Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | V850ES                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 50MHz                                                                                |

| Connectivity               | CSI, EBI/EMI, Ethernet, I <sup>2</sup> C, UART/USART, USB                            |

| Peripherals                | DMA, LVD, PWM, WDT                                                                   |

| Number of I/O              | 100                                                                                  |

| Program Memory Size        | 512KB (512K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                |                                                                                      |

| RAM Size                   | 124К х 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 3.6V                                                                         |

| Data Converters            | A/D 12x10b                                                                           |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 144-LQFP                                                                             |

| Supplier Device Package    |                                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3785gj-gae-ax |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.6.2 Internal units

#### (1) CPU

The CPU uses five-stage pipeline control to enable single-clock execution of address calculations, arithmetic logic operations, data transfers, and almost all other instruction processing.

Other dedicated on-chip hardware, such as a multiplier (16 bits  $\times$  16 bits  $\rightarrow$  32 bits) and a barrel shifter (32 bits) contribute to faster complex processing.

#### (2) Bus control unit (BCU)

The BCU starts a required external bus cycle based on the physical address obtained by the CPU. When an instruction is fetched from external memory space and the CPU does not send a bus cycle start request, the BCU generates a prefetch address and prefetches the instruction code. The prefetched instruction code is stored in an instruction queue.

#### (3) Flash memory (ROM)

This is a 512/384/256 KB flash memory mapped to addresses 0000000H to 007FFFFH/0000000H to 005FFFFH/0000000H to 003FFFFH. It can be accessed from the CPU in one clock during instruction fetch.

#### (4) RAM

This is a 60 KB RAM mapped to addresses 3FF0000H to 3FFEFFFH. It can be accessed from the CPU in one clock during data access. An 16/64 KB data-only RAM is incorporated at addresses 00280000H to 00283FFFH/00280000H to 0028FFFFH.

#### (5) Interrupt controller (INTC)

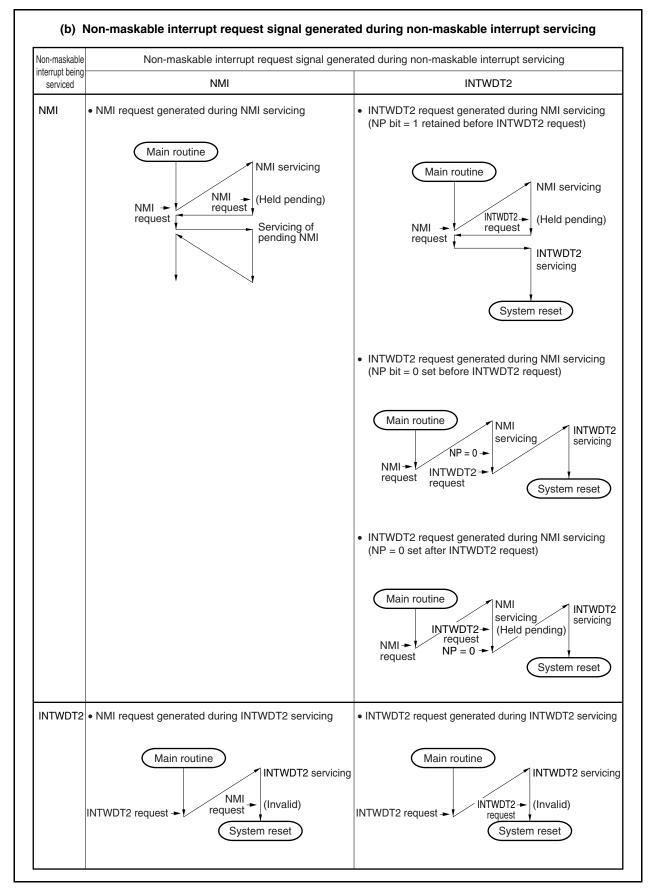

This controller handles hardware interrupt requests (NMI, INTP00 to INTP25) from on-chip peripheral hardware and external hardware. Eight levels of interrupt priorities can be specified for these interrupt requests, and multiplexed servicing control can be performed.

#### (6) Clock generator (CG)

A main clock oscillator and subclock oscillator are provided and generate the main clock oscillation frequency ( $f_{xT}$ ) and subclock frequency ( $f_{xT}$ ), respectively. There are two modes: In the clock-through mode,  $f_x$  is used as the main clock frequency ( $f_{xx}$ ) as is. In the PLL mode,  $f_x$  is used multiplied by 8.

The CPU clock frequency (fcPu) can be selected from among fxx, fxx/2, fxx/4, fxx/8, fxx/16, fxx/32, and fxr.

#### (7) Internal oscillator

An internal oscillator is provided on chip. The oscillation frequency is 220 kHz (TYP). The internal oscillator supplies the clock for watchdog timer 2 and timer M.

#### (8) Timer/counter

Six-channel 16-bit timer/event counter AA (TAA), two-channel 16-bit timer/event counter AB (TAB), one-channel 16-bit timer/event counter T (TMT), and four-channel 16-bit interval timer M (TMM) are provided on chip. The motor control function can be realized using TAB1 and TAA4 in combination.

| /850ES/JJ3 |          |                                         |                                                    |              |             |            |          |       |  |

|------------|----------|-----------------------------------------|----------------------------------------------------|--------------|-------------|------------|----------|-------|--|

| After res  | set: 00H | R/W                                     | Address: F                                         | FFFF444H     | ł           |            |          |       |  |

|            | 7        | 6                                       | 5                                                  | 4            | 3           | 2          | 1        | 0     |  |

| PMC2       | PMC27    | PMC26                                   | PMC25                                              | PMC24        | PMC23       | PMC22      | PMC21    | PMC20 |  |

|            |          | 1                                       |                                                    |              |             |            |          |       |  |

|            | PMC27    |                                         | Spe                                                | cification o | f P27 pin o | peration m | ode      |       |  |

|            | 0        | I/O port                                |                                                    |              |             |            |          |       |  |

|            | 1        | TIAB03 ir                               | put/TOABC                                          | 03 output/IN | NTP21 inpu  | ıt         |          |       |  |

|            | PMC26    |                                         | Spe                                                | cification o | f P26 pin o | peration m | ode      |       |  |

|            | 0        | I/O port                                |                                                    |              |             |            |          |       |  |

|            | 1        | TIAA31 ir                               | put/TOAA3                                          | 31 output/IN | NTP05 inpu  | it/UDMAAk  | 0 output |       |  |

|            | PMC25    |                                         | Spe                                                | cification o | f P25 pin o | peration m | ode      |       |  |

|            | 0        | I/O port                                | I/O port                                           |              |             |            |          |       |  |

|            | 1        | SCKF1 I/                                | SCKF1 I/O/TIAA30 input/TOAA30 output/UDMARQ0 input |              |             |            |          |       |  |

|            | PMC24    | Specification of P24 pin operation mode |                                                    |              |             |            |          |       |  |

|            | 0        | I/O port                                |                                                    |              |             |            |          |       |  |

|            | 1        | SOF1 out                                | SOF1 output/RXDC1 input/SCL00 I/O/INTP04 input     |              |             |            |          |       |  |

|            | PMC23    |                                         | Spe                                                | cification o | f P23 pin o | peration m | ode      |       |  |

|            | 0        | I/O port                                |                                                    |              |             |            |          |       |  |

|            | 1        | SIF1 inpu                               | SIF1 input/TXDC1 output/SDA00 I/O/INTP03 input     |              |             |            |          |       |  |

|            | PMC22    |                                         | Spe                                                | cification o | f P22 pin o | peration m | ode      |       |  |

|            | 0        | I/O port                                |                                                    |              | •           |            |          |       |  |

|            | 1        | TIAB01 ir                               | put/TOABC                                          | )1 output/R  | TC1HZ out   | tput/INTP0 | 2 input  |       |  |

|            | PMC21    |                                         | Spe                                                | cification o | f P21 pin o | peration m | ode      |       |  |

|            | 0        | I/O port                                |                                                    |              |             |            | -        |       |  |

|            | 1        | •                                       | put/TOABC                                          | 0 output/R   | TCDIV out   | put/RTCCL  | output   |       |  |

|            | PMC20    |                                         | Spe                                                | cification o | f P20 pin o | peration m | ode      |       |  |

|            | 0        | I/O port                                |                                                    |              | -           |            |          |       |  |

|            | 1        |                                         | put/TOABC                                          | )2 output/IN |             | +          |          |       |  |

| PFCDH2 | Specification of PDH2 pin alternate function |

|--------|----------------------------------------------|

| 0      | A18 output                                   |

| 1      | SCKE1 I/O                                    |

Caution The SCKE1 function is assigned to the PDH2 pin as well as the P911 pin. When using the PDH2 pin for the SCKE1 function, do not set the P911 pin to be used for this function.

| PFCDH1 | Specification of PDH1 pin alternate function |

|--------|----------------------------------------------|

| 0      | A17 output                                   |

| 1      | SOE1 output                                  |

Caution The SOE1 function is assigned to the PDH1 pin as well as the P910 pin. When using the PDH1 pin for the SOE1 function, do not set the P910 pin to be used for this function.

| PFCDH0 | Specification of PDH0 pin alternate function |

|--------|----------------------------------------------|

| 0      | A16 output                                   |

| 1      | SIE1 input                                   |

Caution The SIE1 function is assigned to the PDH0 pin as well as the P99 pin. When using the PDH0 pin for the SIE1 function, do not set the P99 pin to be used for this function.

|          | •                        |          |                            |                             |               |                | -,            |                                   |

|----------|--------------------------|----------|----------------------------|-----------------------------|---------------|----------------|---------------|-----------------------------------|

| Pin Name | Alternate                | Function | Pnx Bit of                 | PMnx Bit of                 | PMCnx Bit of  | PFCEnx Bit of  | PFCnx Bit of  | Other Bits                        |

|          | Name                     | I/O      | Pn Register                | PMn Register                | PMCn Register | PFCEn Register | PFCn Register | (Registers)                       |

| P93      | TOAB1B2                  | Output   | P93 = Setting not required | PM93 = Setting not required | PMC93 = 1     | PFCE93 = 0     | PFC93 = 0     |                                   |

|          | TRGAB1 Note 1            | Input    | P93 = Setting not required | PM93 = Setting not required | PMC93 = 1     | PFCE93 = 0     | PFC93 = 1     | KRM3 (KRM) = 0                    |

|          | KR3 <sup>Note 1</sup>    | Input    | P93 = Setting not required | PM93 = Setting not required | PMC93 = 1     | PFCE93 = 0     | PFC93 = 1     | TAB1ETS1, TAB1ETS0 (TAB1I0C1) = 0 |

|          | INTP14                   | Input    | P93 = Setting not required | PM93 = Setting not required | PMC93 = 1     | PFCE93 = 1     | PFC93 = 0     |                                   |

|          | A3 <sup>Note 2</sup>     | Output   | P93 = Setting not required | PM93 = Setting not required | PMC93 = 1     | PFCE93 = 1     | PFC93 = 1     |                                   |

| P94      | TOAB1T3                  | Output   | P94 = Setting not required | PM94 = Setting not required | PMC94 = 1     | PFCE94 = 0     | PFC94 = 0     |                                   |

|          | TOAB13                   | Output   | P94 = Setting not required | PM94 = Setting not required | PMC94 = 1     | PFCE94 = 0     | PFC94 = 0     |                                   |

|          | TIAB13 <sup>Note 3</sup> | Input    | P94 = Setting not required | PM94 = Setting not required | PMC94 = 1     | PFCE94 = 0     | PFC94 = 1     | KRM2 (KRM) = 0                    |

|          | KR <sup>4Note 3</sup>    | Input    | P94 = Setting not required | PM94 = Setting not required | PMC94 = 1     | PFCE94 = 0     | PFC94 = 1     | TAB1TIS7, TAB1TIS6 (TAB1I0C1) = 0 |

|          | INTP15                   | Input    | P94 = Setting not required | PM94 = Setting not required | PMC94 = 1     | PFCE94 = 1     | PFC94 = 0     |                                   |

|          | A4 <sup>Note 2</sup>     | Output   | P94 = Setting not required | PM94 = Setting not required | PMC94 = 1     | PFCE94 = 1     | PFC94 = 1     |                                   |

| P95      | TOAB1B3                  | Output   | P95 = Setting not required | PM95 = Setting not required | PMC95 = 1     | PFCE95 = 0     | PFC95 = 0     |                                   |

|          | EVTAB1 <sup>Note 4</sup> | Input    | P95 = Setting not required | PM95 = Setting not required | PMC95 = 1     | PFCE95 = 0     | PFC95 = 1     | KRM5 (KRM) = 0                    |

|          | KR5 <sup>Note 4</sup>    | Input    | P95 = Setting not required | PM95 = Setting not required | PMC95 = 1     | PFCE95 = 0     | PFC95 = 1     | TAB1EES1, TAB1EES0 (TAB1I0C1) = 0 |

|          | INTP16                   | Input    | P95 = Setting not required | PM95 = Setting not required | PMC95 = 1     | PFCE95 = 1     | PFC95 = 0     |                                   |

|          | A5 <sup>Note 2</sup>     | Output   | P95 = Setting not required | PM95 = Setting not required | PMC95 = 1     | PFCE95 = 1     | PFC95 = 1     |                                   |

Table 4-18. Using Port Pin as Alternate-Function Pin (8/13)

Notes 1. KR3 and TRGAB1 are alternate functions. When using the pin for the TRGAB1 function, disable key return detection of KR3, which is the alternate function (set the KRM.KRM3 bit to 0). Also, when using the pin for the KR3 function, disable edge detection of TRGAB1, which is the alternate function (set the TAB1IOC2.TAB1ETS1 and TAB1ETS0 bits to 00).

- 2. When using as the A0 to A15 pins, be sure to set all 16 bits of the PMC9 register to FFFFH at once.

- 3. KR4 and TIAB13 are alternate functions. When using the pin for the TIAB13 function, disable key return detection of KR4, which is the alternate function (set the KRM.KRM4 bit to 0). Also, when using the pin for the KR4 function, disable edge detection of TIAB13, which is the alternate function (set the TAB1IOC1.TAB1IS7 and TAB1IS6 bits to 00).

- 4. KR5 and EVTAB1 are alternate functions. When using the pin for the EVTAB1 function, disable key return detection of KR5, which is the alternate function (set the KRM.KRM5 bit to 0). Also, when using the pin for the KR5 function, disable edge detection of EVTAB1, which is the alternate function (set the TAB1IOC2.TAB1EES1 and TAB1EES0 bits to 00).

# 6.4 Operation

## 6.4.1 Operation of each clock

The following table shows the operation status of each clock.

| Register Setting and                |                 | PCC Register                           |              |                         |              |                  |                     |                  |                     |  |  |  |

|-------------------------------------|-----------------|----------------------------------------|--------------|-------------------------|--------------|------------------|---------------------|------------------|---------------------|--|--|--|

| Operation Status                    |                 | CLK Bi                                 | t = 0, MCK   | Bit = 0                 |              |                  | Bit = 1,<br>Bit = 0 |                  | Bit = 1,<br>Bit = 1 |  |  |  |

|                                     | During<br>Reset | During<br>Oscillation<br>Stabilization | HALT<br>Mode | IDLE1,<br>IDLE2<br>Mode | STOP<br>Mode | Subclock<br>Mode | Sub-IDLE<br>Mode    | Subclock<br>Mode | Sub-IDLE<br>Mode    |  |  |  |

| Target Clock                        |                 | Time Count                             |              |                         |              |                  |                     |                  |                     |  |  |  |

| Main clock oscillator (fx)          | ×               | 0                                      | 0            | 0                       | ×            | 0                | 0                   | ×                | ×                   |  |  |  |

| Subclock oscillator (fxT)           | 0               | 0                                      | 0            | 0                       | 0            | 0                | 0                   | 0                | 0                   |  |  |  |

| CPU clock (fcpu)                    | ×               | ×                                      | ×            | ×                       | ×            | 0                | ×                   | 0                | ×                   |  |  |  |

| Internal system clock (fclk)        | ×               | ×                                      | 0            | ×                       | ×            | 0                | ×                   | 0                | ×                   |  |  |  |

| Main clock (in PLL mode, fxx)       | ×               | O <sup>Note</sup>                      | 0            | ×                       | ×            | 0                | 0                   | ×                | ×                   |  |  |  |

| Peripheral clock (fxx to fxx/1,024) | ×               | ×                                      | 0            | ×                       | ×            | 0                | ×                   | ×                | ×                   |  |  |  |

| WT clock (main)                     | ×               | 0                                      | 0            | 0                       | ×            | 0                | 0                   | ×                | ×                   |  |  |  |

| WT clock (sub)                      | 0               | 0                                      | 0            | 0                       | 0            | 0                | 0                   | 0                | 0                   |  |  |  |

| WDT2 clock (internal oscillation)   | ×               | 0                                      | 0            | 0                       | 0            | 0                | 0                   | 0                | 0                   |  |  |  |

| WDT2 clock (main)                   | ×               | ×                                      | 0            | ×                       | ×            | 0                | ×                   | ×                | ×                   |  |  |  |

| WDT2 clock (sub)                    | 0               | 0                                      | 0            | 0                       | 0            | 0                | 0                   | 0                | 0                   |  |  |  |

## Table 6-1. Operation Status of Each Clock

Note Lockup time

#### Remark O: Operable

×: Stopped

## 6.4.2 Clock output function

The clock output function is used to output the internal system clock (fcLK) from the CLKOUT pin.

The internal system clock (fcLK) is selected by using the PCC.CK3 to PCC.CK0 bits.

The CLKOUT pin functions alternately as the PCM1 pin and functions as a clock output pin if so specified by the control register of port CM.

The status of the CLKOUT pin is the same as the internal system clock in Table 6-1 and the pin can output the clock when it is in the operable status. It outputs a low level in the stopped status. However, the CLKOUT pin is in the port mode (PCM1 pin: input mode) after reset and until it is set in the output mode. Therefore, the status of the pin is Hi-Z.

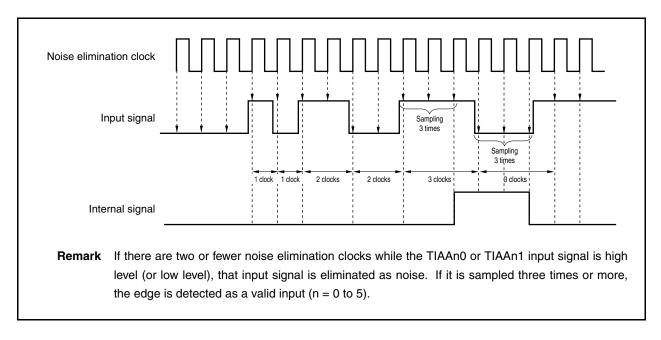

A timing example of noise elimination performed by the timer AA input pin digital filter is shown Figure 7-2.

Figure 7-2. Example of Digital Noise Elimination Timing

# (1) Operation flow in PWM output mode

| FFFH<br>16-bit counter<br>0000H | D00 D00 D01 D01 D01 D01 D00 D00 D00 D00                       |

|---------------------------------|---------------------------------------------------------------|

| TAAnCE bit                      |                                                               |

| TAAnCCR0 register               | D00 D01 D00                                                   |

| CCR0 buffer register            | Doo Do1 Do0                                                   |

| INTTAAnCC0 signal               |                                                               |

| TOAAn0 pin output               |                                                               |

| TAAnCCR1 register               | D10 D10 D11 D10                                               |

| CCR1 buffer register            | D10 D10 D11 D10                                               |

| INTTAAnCC1 signal               |                                                               |

| TOAAn1 pin output               |                                                               |

|                                 | I     I     I     I       <1>     <2>     <3>     <4>     <5> |

| <b>Remark</b> n = 0 m<br>m = 0. |                                                               |

# Figure 7-32. Software Processing Flow in PWM Output Mode (1/2)

| FFFFH                  | D11 D11                                                                         |

|------------------------|---------------------------------------------------------------------------------|

| TAA1<br>16-bit counter | D <sub>10</sub> D <sub>10</sub>                                                 |

| 0000H<br>FFFFH         |                                                                                 |

| TAA0<br>16-bit counter | D <sub>01</sub> D <sub>01</sub> D <sub>01</sub> D <sub>01</sub> D <sub>01</sub> |

| 0000H                  |                                                                                 |

| TAA1CE bit             |                                                                                 |

| TAA1CCR0 register      | D10                                                                             |

| TAA1CCR1 register      | D <sub>11</sub>                                                                 |

| INTTAA1CC0 interrupt   |                                                                                 |

| INTTAA1CC1 interrupt   |                                                                                 |

| TOAA10 pin output      |                                                                                 |

| TOAA11 pin output      |                                                                                 |

| TAA0CCR0 register      | D00                                                                             |

| TAA0CCR1 register      | D01                                                                             |

| INTTAA0CC0 interrupt   |                                                                                 |

| INTTAA0CC1 interrupt   |                                                                                 |

| TOAA00 pin output      |                                                                                 |

| TOAA01 pin output      |                                                                                 |

|                        |                                                                                 |

Figure 7-49. Timing Example of Simultaneous-Start Function (TAA1: Master, TAA0: Slave)

#### (b) 0%/100% output of PWM waveform

To output a 0% waveform, set the TABnCCRk register to 0000H. If the set value of the TABnCCR0 register is FFFFH, the INTTABnCCk signal is generated periodically.

| Count clock<br>16-bit counter |                 | $\frac{1}{2} \frac{1}{2} \frac{1}$ |       | $ \begin{array}{c c}                                    $ |

|-------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------|

| TABnCE bit                    |                 | ζ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | <u>}</u>                                                  |

| TABnCCR0 register             |                 | ۲ <u>ــــــــــــــــــــــــــــــــــــ</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Do    | <u>, D</u> o                                              |

| TABnCCRk register             |                 | ς                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0000H | 0000H                                                     |

| INTTABnCC0 signal             |                 | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       | ,                                                         |

| INTTABnCCk signal             |                 | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | ,                                                         |

| TOABnk pin output             | L               | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | ·                                                         |

| <b>Remark</b> k =<br>n =      | 1 to 3,<br>0, 1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |                                                           |

To output a 100% waveform, set a value of "set value of TABnCCR0 register + 1" to the TABnCCRk register. If the set value of the TABnCCR0 register is FFFFH, 100% output cannot be produced.

| Count clock              |                    | "                           |           | ,                   |      |

|--------------------------|--------------------|-----------------------------|-----------|---------------------|------|

| 16-bit counter           | FFFF 0000          | $D_{0}$ $D_{0} - 1$ $D_{0}$ | 0000 0001 | $D_0 - 1$ $D_0$     | 0000 |

| TABnCE bit               |                    | \$ <del>}</del>             |           | (                   |      |

| TABnCCR0 register        | Do                 | \$}                         | Do        | Do                  |      |

| TABnCCRk register        | D <sub>0</sub> + 1 | ۶ <del>،</del>              | D₀ + 1    | Do + 1              |      |

| INTTABnCC0 signal        |                    | \$ <del>}</del>             |           | ,<br>( <del>,</del> |      |

| INTTABnCCk signal        | (                  | <u> </u>                    |           | <u>}</u>            |      |

| TOABnk pin output        |                    | \$}                         |           | <u>}</u>            |      |

| <b>Remark</b> k =<br>n = | 1 to 3,<br>0, 1    |                             |           |                     |      |

## (2) Operation timing in one-shot pulse output mode

## (a) Notes on rewriting TABnCCRm register

To change the set value of the TABnCCRm register to a smaller value, stop counting once, and then change the set value.

If the value of the TABnCCR0 register is rewritten to a smaller value during counting, the 16-bit counter may overflow.

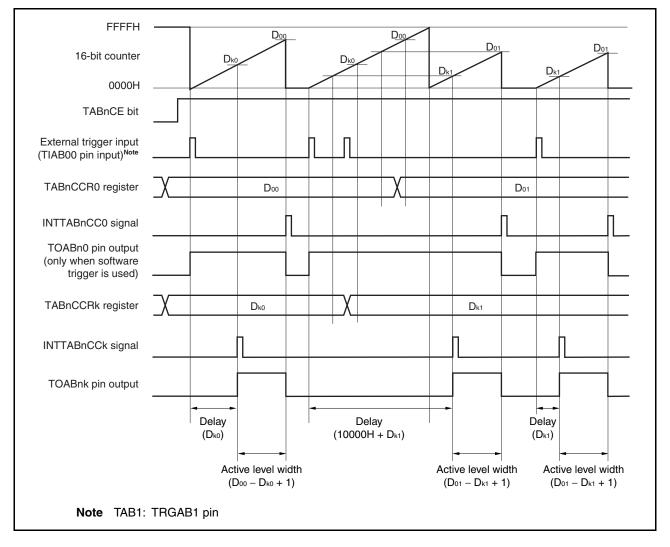

When the TABnCCR0 register is rewritten from  $D_{00}$  to  $D_{01}$  and the TABnCCRk register from  $D_{k0}$  to  $D_{k1}$  where  $D_{00} > D_{01}$  and  $D_{k0} > D_{k1}$ , if the TABnCCRk register is rewritten when the count value of the 16-bit counter is greater than  $D_{k1}$  and less than  $D_{k0}$  and if the TABnCCR0 register is rewritten when the count value is greater than  $D_{01}$  and less than  $D_{00}$ , each set value is reflected as soon as the register has been rewritten and compared with the count value. The counter counts up to FFFFH and then counts up again from 0000H. When the count value matches  $D_{k1}$ , the counter generates the INTTABnCCk signal and asserts the TOABnk pin. When the count value matches  $D_{01}$ , the counter generates the INTTABnCCO signal, deasserts the TOABnk pin, and stops counting.

Therefore, the counter may output a pulse with a delay period or active period different from that of the oneshot pulse that is originally expected.

**Remark** k = 1 to 3, n = 0, 1

## (c) Basic timing 3

## [Register setting condition]

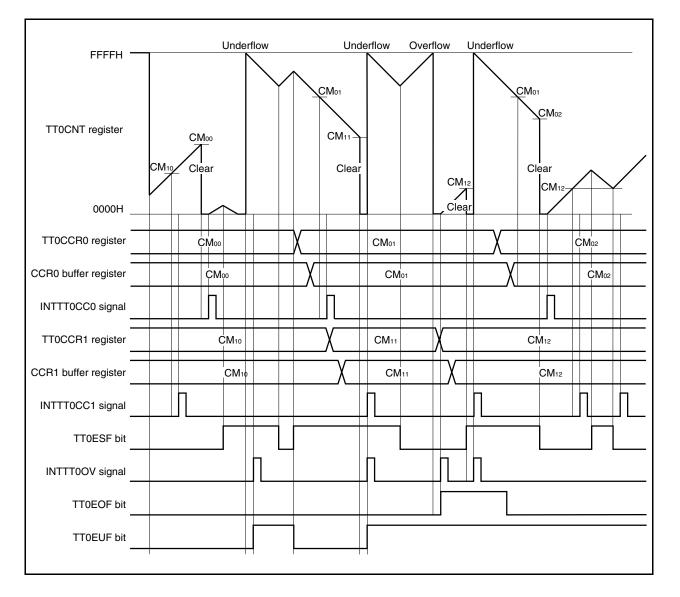

• TT0CTL2.TT0ECM1 and TT0CTL2.TT0ECM0 bits = 11

The count value of the 16-bit counter is cleared to 0000H when its value matches the value of the CCR0 buffer register.

The count value of the 16-bit counter is cleared to 0000H when its value matches the value of the CCR1 buffer register.

- Setting of the TT0CTL2.TT0LDE bit is invalid.

- TT0IOC3.TT0SCE bit = 0, and TT0IOC3.TT0ECS1 and TT0IOC3.TT0ECS0 bits = 00

Specification of clearing the 16-bit counter when the edge of the encoder clear input signal (TECR0 pin) is detected (no edge specified)

## (3) Real-time counter control register 2 (RC1CC2)

The RC1CC2 register is an 8-bit register that controls the alarm interrupt function and waiting of counters. This register can be read or written in 8-bit or 1-bit units.

Reset sets this register to 00H.

| After n | eset: 00H                                                     | R/W                                                                                    | Addres                                                                                                                                                                                                                                                                                                                                                                                                                                          | s: FFFFFA                  | DFH                        |             |                               |                              |  |

|---------|---------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|-------------|-------------------------------|------------------------------|--|

|         | 7                                                             | 6                                                                                      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4                          | 3                          | 2           | 1                             | 0                            |  |

| RC1CC2  | WALE                                                          | 0                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                          | 0                          | 0           | RWST                          | RWAIT                        |  |

|         | <u> </u>                                                      |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |                            |             |                               |                              |  |

|         | WALE                                                          | Description                                                                            | Alarm interrupt (INTRTC1) operation control                                                                                                                                                                                                                                                                                                                                                                                                     |                            |                            |             |                               |                              |  |

|         | 0                                                             |                                                                                        | •                                                                                                                                                                                                                                                                                                                                                                                                                                               | upon alarm                 |                            | atch.       |                               |                              |  |

|         |                                                               | Generated                                                                              | sinterrupt                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            | matori.                    |             |                               |                              |  |

|         | RWST                                                          |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Real-tim                   | e counter v                | vait state  |                               |                              |  |

|         | 0                                                             | Counter o                                                                              | perating                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |                            |             |                               |                              |  |

|         | 1                                                             |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            | counters sto<br>values ena |             |                               |                              |  |

|         |                                                               | status flag<br>write counte                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |                            |             |                               |                              |  |

|         | RWAIT                                                         |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Real-time                  | e counter w                | ait control |                               |                              |  |

|         | 0                                                             | Sets coun                                                                              | ter operati                                                                                                                                                                                                                                                                                                                                                                                                                                     | on.                        |                            |             |                               |                              |  |

|         | 1                                                             |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | on of secon<br>/write mode | d to year co<br>e)         | ounters.    |                               |                              |  |

|         | Be sure to<br>If the RC<br>informatic<br>clocks or<br>However | to write 1 to<br>1SUBC reg<br>on is retained<br>less $(2 \times 3)^2$<br>, if the seco | pontrols the operation of the counters.<br>by write 1 to this bit when reading or writing counter values.<br>ISUBC register overflows while the RWAIT bit is 1, the overflow<br>on is retained internally and the RC1SEC register is counted up after two<br>less ( $2 \times 32.768$ kHz) after 0 is written to the RWAIT bit.<br>if the second counter value is rewritten while the RWAIT bit is 1, the<br>overflow information is discarded. |                            |                            |             |                               |                              |  |

|         |                                                               |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                          | -                          | -           | <b>al-time co</b><br>C1PWR bi | unter operation when t = 1). |  |

| 2. Conf | irm that th                                                   | at the RWST bit is set to 1 when reading or writing each counter value.                |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |                            |             |                               |                              |  |

|         |                                                               | does not l<br>omes 0 wł                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |                            |             |                               | even if the RWAIT bit        |  |

# 16.10 Cautions

Cautions concerning UARTBn are shown below.

## (1) When supply clock to UARTBn is stopped

When the supply of clocks to UARTBn is stopped (for example, IDLE and STOP modes), operation stops with each register retaining the value it had immediately before the supply of clocks was stopped. The TXDBn pin output also holds and outputs the value it had immediately before the supply of clocks was stopped. However, operation is not guaranteed after the supply of clocks is restarted. Therefore, after the supply of clocks is restarted, the circuits should be initialized by setting the UBnPWR bit = 0, UBnRXE bit = 0, and UBnTXE bit = 0.

#### (2) Caution on setting UBnCTL0 register

- When using UARTBn, set the external pins related to the UARTBn function to the alternate function and set the UBnCTL2 register. Then set the UBnCTL0.UBnPWR bit to 1 before setting the other bits.

- Be sure to input a high level to the RXDBn pin when setting the external pins related to the UARTBn function to the alternate function. If a low level is input, it is judged that a falling edge is input after the UBnCTL0.UBnRXE bit has been set to 1, and reception may be started.

## (3) Caution on setting UBnFIC2 register

Be sure to clear the UBnCTL0.UBnTXE bit (to disable transmission) and UBnCTL0.UBnRXE bit (to disable reception) to 0 before writing data to the UBnFIC2 register. If data is written to the UBnFIC2 register with the UBnTXE or UBnRXE bit set to 1, the operation is not guaranteed.

#### (4) Transmission interrupt request signal

In the single mode, the transmission enable interrupt request signal (INTUBnTIT) occurs when the UBnTX register becomes empty (when 1 byte of data is transferred from the UBnTX register to the transmit shift register). In the FIFO mode, the FIFO transmission end interrupt request signal (INTUBnTIF) occurs when data is no longer in transmit FIFO and the transmit shift register (when the FIFO and register are empty). However, the INTUBnTIT signal or INTUBnTIF signal does not occur if the transmit data register becomes empty due to RESET input.

#### (5) Initialization during continuous transmission in single mode

Confirm that the UBnSTR.UBnTSF bit is 0 before executing initialization during transmission processing. If initialization is executed while the UBnTSF bit is 1, the transmit data is not guaranteed.

#### (6) Initialization during continuous transmission (pending mode) in FIFO mode

Confirm that the UBnSTR.UBnTSF bit is 0 before executing initialization during transmission processing (this can also be done by checking the FIFO transmission end interrupt request signal (INTUBnTIF)). If initialization is executed while the UBnTSF bit is 1, the transmit data is not guaranteed.

To write transmit data to transmit FIFO by DMA control, set the number of transmit data specified as the trigger by the UBnFIC2.UBnTT3 to UBnFIC2.UBnTT0 bits to 1 byte; otherwise the operation will not be guaranteed.

## (7) Initialization during continuous transmission (pointer mode) in FIFO mode

Confirm that the UBnSTR.UBnTSF bit is 0 before executing initialization during transmission processing (this can also be done by checking the FIFO transmission end interrupt request signal (INTUBnTIF)). If initialization is executed while the UBnTSF bit is 1, the transmit data is not guaranteed.

## 17.3.2 Mode switching between UARTC1, CSIF1 and $I^2C00$

In the V850ES/JH3-E and V850ES/JJ3-E, UARTC1, CSIF1 and I<sup>2</sup>C00 share the same pin, so these functions cannot be used simultaneously. Set UARTC1 in advance, using the PMC2, PFC2 and PFCE2 registers.

# Caution The transmit/receive operation of UARTC1, CSIF1, and I<sup>2</sup>C00 is not guaranteed if these functions are switched during transmission or reception. Be sure to disable the one that is not used.

| After re  | set: 00H                   | R/W        | Address:   | FFFFF444H             | 4                 |            |         |        |

|-----------|----------------------------|------------|------------|-----------------------|-------------------|------------|---------|--------|

|           | 7                          | 6          | 5          | 4                     | 3                 | 2          | 1       | 0      |

| PMC2      | /<br>PMC27 <sup>Note</sup> |            | PMC25      | PMC24                 | PMC23             | PMC22      | PMC21   | PMC20  |

| TWOZ      | 1 1027                     | 1 1020     | 1 1023     | 1 1024                | 1 1023            | TMOZZ      | 1 10021 | 1 1020 |

| After res | set: 00H                   | R/W        | Address: F | FFFF464H              | I                 |            |         |        |

|           | 7                          | 6          | 5          | 4                     | 3                 | 2          | 1       | 0      |

| PFC2      | PFC27 <sup>Note</sup>      | PFC26      | PFC25      | PFC24                 | PFC23             | PFC22      | PFC21   | PFC20  |

| After res | set: 00H<br>7              | <b>R/W</b> | Address: F | FFFF704H<br>4         | ł<br>3            | 2          | 1       | 0      |

| PFCE2     | PFCE27 <sup>Note</sup>     |            | PFCE25     | PFCE24                | PFCE23            | PFCE22     | PFCE21  | PFCE20 |

|           |                            |            |            |                       |                   |            |         |        |

|           | PMC25                      | PFCE25     | PFC25      |                       | Ор                | eration mo | de      |        |

|           | 0                          | ×          | ×          | Port I/O m            | node              |            |         |        |

|           | 1                          | 0          | 0          | SCKF1 (C              | SIF1)             |            |         |        |

|           |                            |            |            |                       |                   |            |         |        |

|           | PMC24                      | PFCE24     | PFC24      |                       |                   | eration mo | de      |        |

|           | 0                          | ×          | ×          | Port I/O m            |                   |            |         |        |

|           | 1                          | 0          | 0          | SOF1 (CS              |                   |            |         |        |

|           | 1                          | 0          | 1          | RXDC1 (l              |                   |            |         |        |

|           | 1                          | 1          | 0          | SCL00 (I <sup>2</sup> | C00)              |            |         |        |

|           | PMC23                      | PFCE23     | PFC23      |                       | Ор                | eration mo | de      |        |

|           | 0                          | ×          | ×          | Port I/O m            | node              |            |         |        |

|           | 1                          | 0          | 0          | SIF1 (CSI             | F1)               |            |         |        |

|           | 1                          | 0          | 1          | TXDC1 (L              | JARTC1)           |            |         |        |

|           | 1                          | 1          | 0          | SDA00 (l <sup>2</sup> | <sup>2</sup> C00) |            |         |        |

|           | Note V8                    | 50ES/JJ3   | 3-E only   |                       |                   |            |         |        |

Figure 17-3. UARTC1, CSIF1 and I<sup>2</sup>C00 Mode Switch Settings

# 20.4 Registers

I<sup>2</sup>C0n is controlled by the following registers.

- IIC control register n (IICCn)

- IIC status register n (IICSn)

- IIC flag register n (IICFn)

- IIC clock select register n (IICCLn)

- IIC function expansion register n (IICXn)

- IIC division clock select register 0 to 2 (OCKS0 to OCKS2)

The following registers are also used.

- IIC shift registers n (IICn)

- Slave address registers n (SVAn)

- Remark For the alternate-function pin settings, see Table 4-18 Settings When Port Pins Are Used for Alternate Functions.

## (1) IIC control registers n (IICCn)