Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | V850ES                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 50MHz                                                                                |

| Connectivity               | CANbus, CSI, EBI/EMI, Ethernet, I <sup>2</sup> C, UART/USART, USB                    |

| Peripherals                | DMA, LVD, PWM, WDT                                                                   |

| Number of I/O              | 100                                                                                  |

| Program Memory Size        | 512KB (512K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 124K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 3.6V                                                                         |

| Data Converters            | A/D 12x10b                                                                           |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 144-LQFP                                                                             |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3786gj-gae-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| (2/3) |

|-------|

|       |

| Pin Name | I/O | Function                                                                        | Alternate Function                  | Pin   | No.   |

|----------|-----|---------------------------------------------------------------------------------|-------------------------------------|-------|-------|

|          |     |                                                                                 |                                     | JH3-E | JJ3-E |

| P50      | I/O | Port 5                                                                          | INTP07/DDI                          | 23    | 23    |

| P51      |     | 5-bit I/O port (V850ES/JH3-E)                                                   | INTP08/DDO                          | 24    | 24    |

| P52      |     | 10-bit I/O port (V850ES/JJ3-E)<br>Input/output can be specified in 1-bit units  | INTP09/DCK                          | 25    | 25    |

| P53      |     | 5 V tolerant.                                                                   | INTP10/DMS                          | 26    | 26    |

| P54      |     |                                                                                 | INTP11/DRST                         | 27    | 27    |

| P55      |     |                                                                                 | SDA04/INTP23/UDMARQ1                | -     | 42    |

| P56      |     |                                                                                 | SCL04/INTP24/UDMAAK1                | _     | 43    |

| P57      |     |                                                                                 | SIF6/TXDC7                          | -     | 62    |

| P58      |     |                                                                                 | SOF6/RXDC7                          | -     | 63    |

| P59      |     |                                                                                 | SCKF6/INTP25                        | -     | 64    |

| P70      | I/O | Port 7                                                                          | ANIO                                | 128   | 144   |

| P71      |     | 10-bit I/O port (V850ES/JH3-E)                                                  | ANI1                                | 127   | 143   |

| P72      |     | 12-bit I/O port (V850ES/JJ3-E)<br>Input/output can be specified in 1-bit units. | ANI2                                | 126   | 142   |

| P73      |     | inpurouput can be specified in 1-bit diffits.                                   | ANI3                                | 125   | 141   |

| P74      |     |                                                                                 | ANI4                                | 124   | 140   |

| P75      |     |                                                                                 | ANI5                                | 123   | 139   |

| P76      |     |                                                                                 | ANI6                                | 122   | 138   |

| P77      |     |                                                                                 | ANI7                                | 121   | 137   |

| P78      |     |                                                                                 | ANI8                                | 120   | 136   |

| P79      |     |                                                                                 | ANI9                                | 119   | 135   |

| P710     |     |                                                                                 | ANI10                               | -     | 134   |

| P711     |     |                                                                                 | ANI11                               | _     | 133   |

| P90      | I/O | Port 9                                                                          | TOAB1T1/TOAB11/TIAB11/KR0/INTP12/A0 | 65    | 71    |

| P91      |     | 16-bit I/O port                                                                 | TOAB1B1/TIAB10/KR1/TOAB10/A1        | 66    | 72    |

| P92      |     | Input/output can be specified in 1-bit units.<br>5 V tolerant.                  | TOAB1T2/TOAB12/TIAB12/KR2/INTP13/A2 | 67    | 73    |

| P93      |     |                                                                                 | TOAB1B2/TRGAB1/KR3/INTP14/A3        | 68    | 74    |

| P94      |     |                                                                                 | TOAB1T3/TOAB13/TIAB13/KR4/INTP15/A4 | 69    | 75    |

| P95      |     |                                                                                 | TOAB1B3/EVTB1/KR5/INTP16/A5         | 70    | 76    |

| P96      |     |                                                                                 | TECR0/TIT00/KR6/TOT00/A6            | 71    | 77    |

| P97      |     |                                                                                 | TENC00/TIT01/KR7/TOT01/A7           | 72    | 78    |

| P98      |     |                                                                                 | TENC01/INTP17/A8                    | 73    | 79    |

| P99      |     |                                                                                 | SIE1/TXDC5/SDA03/A9                 | 74    | 80    |

| P910     |     |                                                                                 | SOE1/RXDC5/SCL03/A10                | 75    | 81    |

| P911     |     |                                                                                 | SCKE1/TIAA50/TOAA50/A11             | 76    | 82    |

| P912     |     |                                                                                 | TOAB1OFF/INTP18/A12                 | 77    | 83    |

| P913     |     |                                                                                 | SIF3/TXDB1/INTP19/A13               | 78    | 84    |

| P914     |     |                                                                                 | SOF3/RXDB1/INTP20/A14               | 79    | 85    |

| P915     |     |                                                                                 | SCKF3/TIAA51/TOAA51/A15             | 80    | 86    |

Remark JH3-E: V850ES/JH3-E, JJ3-E: V850ES/JJ3-E

### (2) Clock control register (CKC)

The CKC register is a special register. Data can be written to this register only in a combination of specific sequence (see **3.4.8 Special registers**).

The CKC register controls the internal system clock in the PLL mode.

This register can be read or written in 8-bit or 1-bit units.

Reset sets this register to 0AH.

|                                                                                                                                                                                                                                                                                                                                         | After res                                                                                                                                     | set: 0AH | R/W                       | Address:      | FFFFF822  | 2H |   |   |        |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------|---------------|-----------|----|---|---|--------|--|--|

|                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                               | 7        | 6                         | 5             | 4         | 3  | 2 | 1 | 0      |  |  |

|                                                                                                                                                                                                                                                                                                                                         | CKC                                                                                                                                           | 0        | 0                         | 0             | 0         | 1  | 0 | 1 | CKDIV0 |  |  |

|                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                               |          |                           |               |           |    |   |   |        |  |  |

|                                                                                                                                                                                                                                                                                                                                         | CKDIV0 Internal system clock (fxx) in PLL mode                                                                                                |          |                           |               |           |    |   |   |        |  |  |

|                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                               | 0        | Setting pr                | ohibited      |           |    |   |   |        |  |  |

|                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                               | 1        | $f_{xx} = 8 \times f_{x}$ | x (fx = 3.0 t | o 6.25 MH | z) |   |   |        |  |  |

| <ol> <li>Caution 1. Be sure to set the CKC register to 0BH. When setting this register to a value other than 0BH or leaving it set to its initial value without setting it to 0BH, enabling PLL operation (PLLCTL.SELPLL = 1) is prohibited.</li> <li>Be sure to set bits 3 and 1 to "1" and clear bits 7 to 4 and 2 to "0".</li> </ol> |                                                                                                                                               |          |                           |               |           |    |   |   |        |  |  |

| Remark                                                                                                                                                                                                                                                                                                                                  | <b>Remark</b> Both the CPU clock and peripheral clock are divided by the CKC register, but only the CPU clock is divided by the PCC register. |          |                           |               |           |    |   |   |        |  |  |

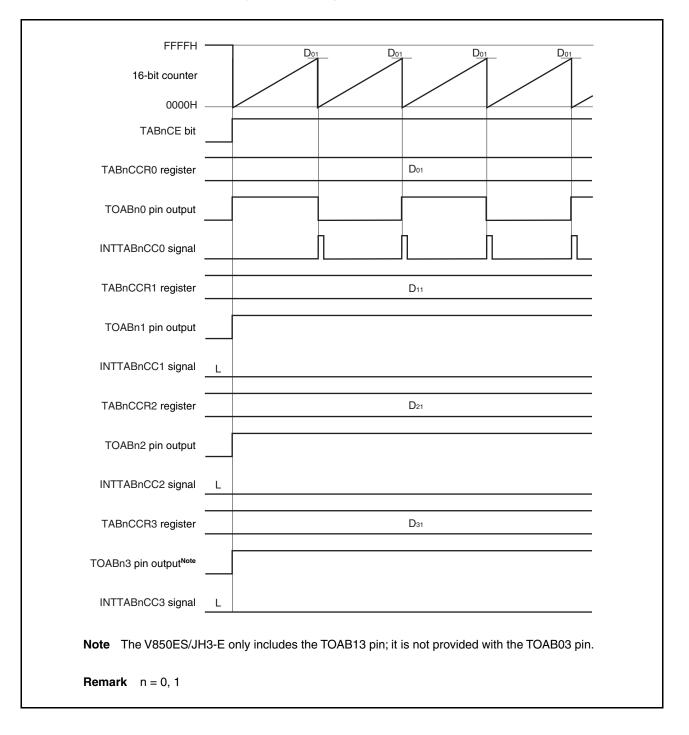

If the set value of the TABnCCRk register is greater than the set value of the TABnCCR0 register, the count value of the 16-bit counter does not match the value of the TABnCCRk register. Consequently, the INTTABnCCk signal is not generated, nor is the output of the TOABnk pin changed.

**Remark** k = 1 to 3, n = 0, 1

Figure 8-8. Timing Chart When Do1 < Dk1

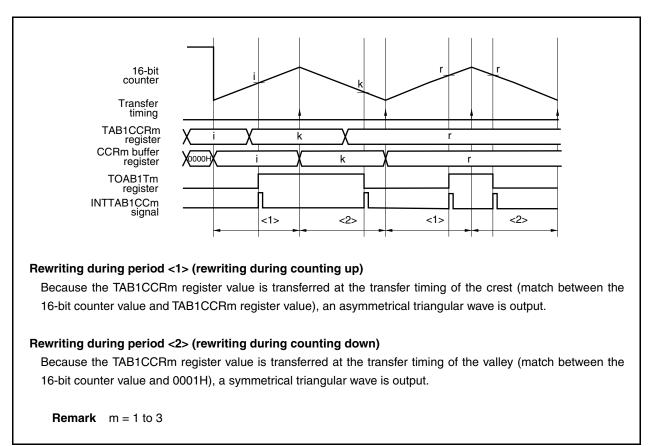

# (c) Rewriting TAB1CCRm register

# Figure 11-30. Example of Rewriting TAB1CCRm Register

### (d) Transferring TAB1OPT1 register value

Do not set the TAB1OPT1.TAB1ID4 to TAB1OPT1.TAB1ID0 bits to other than 00000. When using the interrupt culling function, rewrite the TAB1OPT1 register in the intermittent batch rewrite mode (transfer culling mode). For details of rewriting the TAB1OPT1 register, see **11.4.3 Interrupt culling function**.

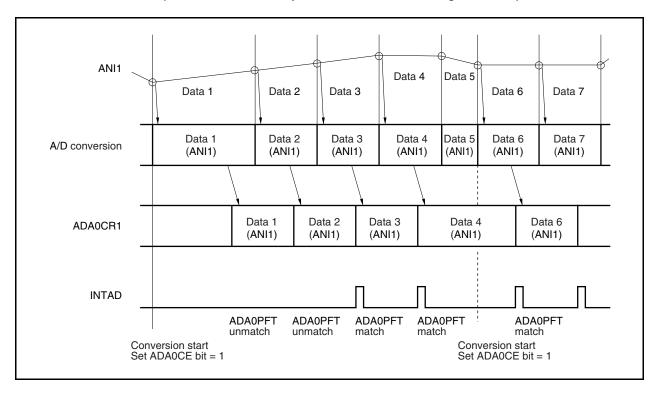

## (1) Continuous select mode

In this mode, the result of converting the voltage of the analog input pin specified by the ADA0S register is compared with the set value of the ADA0PFT register. If the result of power-fail comparison matches the condition set by the ADA0PFC bit, the conversion result is stored in the ADA0CRn register, and the INTAD signal is generated. If it does not match, the conversion result is stored in the ADA0CRn register, and the INTAD signal is not generated. After completion of the first conversion, the next conversion is started, unless the ADA0M0.ADA0CE bit is cleared to 0.

Figure 15-8. Timing Example of Continuous Select Mode Operation (When Power-Fail Comparison Is Made: ADA0S Register = 01H)

### (2) Continuous scan mode

In this mode, the results of converting the voltages of the analog input pins sequentially selected from the ANI0 pin to the pin specified by the ADA0S register are stored, and the set value of the ADA0CR0H register of channel 0 is compared with the value of the ADA0PFT register. If the result of power-fail comparison matches the condition set by the ADA0PFC bit, the conversion result is stored in the ADA0CR0 register, and the INTAD signal is generated. If it does not match, the conversion result is stored in the ADA0CR0 register, and the INTAD signal is not generated. After the result of the first conversion has been stored in the ADA0CR0 register, the results of sequentially converting the voltages on the analog input pins up to the pin specified by the ADA0S register are continuously stored. After completion of conversion, the next conversion is started from the ANI0 pin again, unless the ADA0CE bit is cleared to 0.

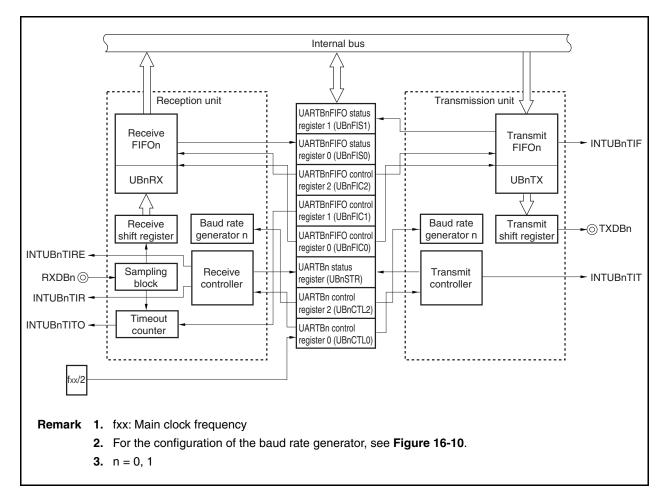

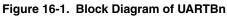

# 16.2 Configuration

The block diagram of the UARTBn is shown below.

UARTBn consists of the following hardware units.

| Table 16-1. | Configuration of UARTBn |

|-------------|-------------------------|

|-------------|-------------------------|

| Item      | Configuration                             |

|-----------|-------------------------------------------|

| Registers | UARTBn control register 0 (UBnCTL0)       |

|           | UARTBn control register 2 (UBnCTL2)       |

|           | UARTBn status register (UBnSTR)           |

|           | UARTBn FIFO control register 0 (UBnFIC0)  |

|           | UARTBn FIFO control register 1 (UBnFIC1)  |

|           | UARTBn FIFO control register 2 (UBnFIC2)  |

|           | UARTBn FIFO status register 0 (UBnFIS0)   |

|           | UARTBn FIFO status register 1 (UBnFIS1)   |

|           | Receive shift register                    |

|           | UARTBn receive data register AP (UBnRXAP) |

|           | UARTBn receive data register (UBnRX)      |

|           | Transmit shift register                   |

|           | UARTBn transmit data register (UBnTX)     |

## (7) UARTBn FIFO control register 1 (UBnFIC1)

The UBnFIC1 register is valid in the FIFO mode (UBnFIC0.UBnMOD bit = 1). It generates a reception timeout interrupt request signal (INTUBnTITO) if data is stored in receive FIFO when the next data does not come (start bit is not detected) after the lapse of the time set by the UBnTC4 to UBnTC0 bits (next data reception wait time), after the stop bit has been received.

This register can be read or written in 8-bit or 1-bit units.

Reset sets this register to 00H.

| Aller le              | set: 00H | R/W        |             |             |             |          | 2                  | FFFFBA         |             |

|-----------------------|----------|------------|-------------|-------------|-------------|----------|--------------------|----------------|-------------|

|                       |          | 6          | 5           | 4           |             | 3        |                    | 1              | 0           |

| UBnFIC1<br>(n = 0, 1) | UBnTCE   | 0          | 0           | UBnT        |             | nTC3     | UBnTC2             | UBnTC1         | UBnTC0      |

|                       | UBnTCE   |            | Specific    | ation of ti | meout co    | unter    | function dis       | able/enabl     | е           |

|                       | 0        | Disable    | use of tim  | neout cou   | nter funct  | tion.    |                    |                |             |

|                       | 1        | Enable     | use of tim  | eout cour   | iter funct  | ion.     |                    |                |             |

|                       |          |            |             |             |             |          |                    |                |             |

|                       | UBnTC4   | UBnTC3     | UBnTC2      | UBnTC1      | UBnTC       | ) Ne     | ext data rec       | ception wai    | t time      |

|                       | 0        | 0          | 0           | 0           | 0           | 32 b     | ytes (32 $	imes$   | 8/baud rate    | e)          |

|                       | 0        | 0          | 0           | 0           | 1           | 31 b     | ytes (31 $	imes$   | 8/baud rate    | e)          |

|                       | 0        | 0          | 0           | 1           | 0           | 30 b     | ytes (30 $	imes$   | 8/baud rate    | e)          |

|                       | 0        | 0          | 0           | 1           | 1           | 29 b     | oytes (29 $	imes$  | 8/baud rate    | e)          |

|                       | •        | •          | •           | ٠           | •           |          |                    | •              |             |

|                       | •        | •          | •           | ٠           | •           |          |                    | •              |             |

|                       | •        | •          | •           | •           | •           |          |                    | •              |             |

|                       | 1        | 1          | 1           | 0           | 0           | 4 by     | tes (4 $	imes$ 8/k | paud rate)     |             |

|                       | 1        | 1          | 1           | 0           | 1           | 3 by     | tes (3 $	imes$ 8/k | paud rate)     |             |

|                       | 1        | 1          | 1           | 1           | 0           | 2 by     | tes (2 $	imes$ 8/k | paud rate)     |             |

|                       | 1        | 1          | 1           | 1           | 1           | 1 by     | te (1 $	imes$ 8/ba | aud rate)      |             |

|                       | When co  | unting up  | of the rec  | ception wa  | ait time, s | et by t  | the UBnTC          | 4 to UBnT      | C0 bits, is |

|                       | complete | , the cou  | nt value o  | f the time  | out count   | ter is c | leared to 0        | , regardles    | s of the    |

|                       |          |            |             |             |             |          |                    | oit is later d | etected,    |

|                       | counting | is started | l again fro | m the sto   | p bit of th | at dat   | a.                 |                |             |

## (2) Function of CSI data buffer registers 0, 1 (CSIBUF0, CSIBUF1)

By consecutively writing the transmit data to the CEnTX0 register from where it is transferred, up to sixteen 16-bit data can be stored in the CSIBUFn register while the CSIBUFn pointer for writing is automatically incremented (n = 0, 1).

The condition under which transfer is to be started (CEnSTR.CEnEMF bit = 0) is satisfied when data is written to the lower 8 bits (CEnTX0L register) of the CEnTX0 register. If a transfer data length of 9 bits or more is specified (CEnCTL2.CEnDLS3 to CEnCTL2.CEnDLS0 bits = 0000 or 1001 to 1111), data must be written to the CEnTX0 register in 16-bit units or to the CEnTX0H and CEnTX0L registers, in that order, in 8-bit units. If the transfer data length is set to 8 bits (CEnCTL2.CEnDLS3 to CEnCTL2.CEnDLS3 to CEnCTL2.CEnDLS0 bits = 1000), data must be written to the CEnTX0L register in 8-bit units or to the CEnTX0 register in 16-bit units. (If data is written to the CEnTX0L register in 16-bit units, however, the higher 8 bits of the data (of the CEnTX0H register) are ignored and not transferred).

The CEnSTR.CEnFLF register is set to 1 when 16 data exist in the CSIBUFn register and outputs a CSIBUFn overflow interrupt (INTCEnTIOF) when the CEnFLF bit = 1 and when the 17th transfer data is written (17th transfer data is not written and ignored).

Sixteen data exist in the CSIBUFn register in the single mode (CEnCTL0.CEnTMS bit = 1) when "CSIBUFn pointer value for writing = CSIBUFn pointer value for SIOn loading, and CEnSTR.CEnFLF bit = 1". When the CSIBUFn pointer for SIOn loading is incremented after completion of transfer while CEnFLF bit = 1, the CEnFLF bit is cleared to 0 and the next transmission data can be written.

In the continuous mode (CEnCTL0.CEnTMS bit = 1), when one data has been transferred, the CEnFLF bit is cleared to 0, but writing the next transmission data is prohibited (if a receive operation is processed, the received data is stored in the CSIBUFn register. Therefore, if the transmission data is written to the register, the received data is overwritten and destroyed).

This register can be read or written in 8-bit or 1-bit units. Reset sets this register to 01H.

| After res | et: 01H                       | R/W Address: CF0CTL0 FFFFFD00H, CF1CTL0 FFFFFD10H,                                                                                                                                                  |  |  |  |  |  |

|-----------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|           |                               | CF2CTL0 FFFFFD20H, CF3CTL0 FFFFFD30H,                                                                                                                                                               |  |  |  |  |  |

|           |                               | CF4CTL0 FFFFFD40H, CF5CTL0 FFFFFD50H,                                                                                                                                                               |  |  |  |  |  |

|           |                               | CF6CTL0 FFFFFD60H                                                                                                                                                                                   |  |  |  |  |  |

|           | -7-                           |                                                                                                                                                                                                     |  |  |  |  |  |

| CFnCTL0   | <7>                           | <6>         <5>         <4>         3         2         1         <0>           CFnTXE <sup>Note</sup> CFnDIR <sup>Note</sup> 0         0         CFnTMS <sup>Note</sup> CFnSCE                     |  |  |  |  |  |

|           |                               |                                                                                                                                                                                                     |  |  |  |  |  |

|           | CFnPWR                        | Specification of CSIFn operation disable/enable                                                                                                                                                     |  |  |  |  |  |

|           | 0                             | Disables CSIFn operation and resets the CFnSTR register                                                                                                                                             |  |  |  |  |  |

|           | 1                             | Enables CSIFn operation                                                                                                                                                                             |  |  |  |  |  |

|           | • The CF                      | nPWR bit controls the CSIFn operation and resets the internal circuit.                                                                                                                              |  |  |  |  |  |

|           |                               |                                                                                                                                                                                                     |  |  |  |  |  |

|           | <b>CFnTXE</b> <sup>Note</sup> | Specification of transmit operation disable/enable                                                                                                                                                  |  |  |  |  |  |

|           | 0                             | Disables transmit operation                                                                                                                                                                         |  |  |  |  |  |

|           | 1 Enables transmit operation  |                                                                                                                                                                                                     |  |  |  |  |  |

|           | • The SO                      | Fn output is low level when the CFnTXE bit is 0.                                                                                                                                                    |  |  |  |  |  |

|           |                               |                                                                                                                                                                                                     |  |  |  |  |  |

|           | CFnRXE <sup>Note</sup>        | Specification of receive operation disable/enable                                                                                                                                                   |  |  |  |  |  |

|           | 0                             | Disables receive operation                                                                                                                                                                          |  |  |  |  |  |

|           | 1                             | Enables receive operation                                                                                                                                                                           |  |  |  |  |  |

|           | transfer                      | ption completion interrupt is output even when the prescribed data is red, and the receive data (CFnRX register) is not updated, because the operation is disabled by clearing the CFnRXE bit to 0. |  |  |  |  |  |

|           | Note Th                       | nese bits can only be rewritten when the CFnPWR bit = $0$ .                                                                                                                                         |  |  |  |  |  |

|           |                               | owever, CFnPWR bit = 1 can also be set at the same time as                                                                                                                                          |  |  |  |  |  |

|           | re                            | writing these bits.                                                                                                                                                                                 |  |  |  |  |  |

|           | Coution                       | To foreibly overend transmission/recention clear the CEnDW/D                                                                                                                                        |  |  |  |  |  |

|           | Caution                       | To forcibly suspend transmission/reception, clear the CFnPWR<br>bit to 0 instead of the CFnRXE and CFnTXE bits.                                                                                     |  |  |  |  |  |

|           |                               | At this time, the clock output is stopped.                                                                                                                                                          |  |  |  |  |  |

|           |                               |                                                                                                                                                                                                     |  |  |  |  |  |

|           |                               | ······································                                                                                                                                                              |  |  |  |  |  |

|           | Remark                        | n = 0 to 4 (V850ES/JH3-E)                                                                                                                                                                           |  |  |  |  |  |

# (4) CSIFn control register 1 (CFnCTL1)

CFnCTL1 is an 8-bit register that controls the CSIFn serial transfer operation. This register can be read or written in 8-bit or 1-bit units. Reset sets this register to 00H.

### Caution The CFnCTL1 register can be rewritten only when the CFnCTL0.CFnPWR bit = 0.

| CFRCTL 1 FFFFFD21H, CFSCTL 1 FFFFFD3H,<br>CFGCTL 1 FFFFFD2H<br>CFGCTL 1 FFFFFD2H<br>CFGCTL 1 FFFFFD2H<br>CFGCTL 1 TFFFFD2H<br>CFGCTL 1 TFFFFD2H<br>CFGCTL 1 TFFFFD2H<br>CFGCTL 1 TFFFFD2H<br>CGGCL 2 FFGCKS CFGCKS CFGCKS<br>CFGCTL 1 TFFFFD2H<br>CGGCL 2 FFGCKS CFGCKS CFGCKS<br>CFGCTL 1 TFFFFD2H<br>CGGCL 2 FFGCKS CFGCKS CFGCKS CFGCKS<br>CFGCKS CFGCKS CGGC 2 CFGCKS CFGC 2 CFGCKS CFGCKS<br>CGGCL 2 CFGCKS CFGCKS CGGC 2 CFGC 2 CFGCKS CFGC<br>CGGCL 2 CFGCKS CFGCKS CGGC 2 CFGC 2 CFGCKS CFGC 2 CFGCKS CFGC 2 CFGCKS CFGCKS CGGC 2 CFGC 2 CFGC 2 CFGCKS CFGC 2 CFGCKS CFGC 2 CFGCKS CFGC 2 CFGCKS CGGC 2 CFGC 2 CFGC 2 CFGCKS CFGC 2 CFGCKS CGGC 2 CFGC 2 CFGC 2 CFGCKS CGGC 2 CFGC 2 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | After res | et: 00H | R/W A       | ddress: CF  | OCTL1 FFFFFD01H, CF1CTL1 FF          | FFFD11H,                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|-------------|-------------|--------------------------------------|-----------------------------------------------|

| CFICLI 1 FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |         |             | CF          | 2CTL1 FFFFFD21H, CF3CTL1 FF          | FFFD31H,                                      |

| CFICKL1 $7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 \\ \hline 0 & 0 & 0 & CFICKP (CFIDAP (CFIDAP (CFICKS2 (CFICKS1 (CFICKS0)))) \\ \hline 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |         |             | CF          | 4CTL1 FFFFFD41H, CF5CTL1 FF          | FFFD51H,                                      |

| CFnCTL1000CFnCKPCFnDAPCFnCKS2CFnCKS2CFnCKS2CFnCKS2CFnCKS2Communication00SCRF (numper)<br>SCRF (numper)<br>COT (SCR (SCR (SCR (SCR (SCR (SCR (SCR (SCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |         |             | CF          | 6CTL1 FFFFFD61H                      |                                               |

| Specification of data transmissionCommunication00SCRF: (UO)Uppe 10SCRF: (UO)0Communication01SCRF: (UO)Uppe 201SCRF: (UO)0Communication01SCRF: (UO)0Uppe 310SCRF: (UO)0SoF: (UD)00COT (SCR (DE) (SCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           | 7       | 6           | 5           | 4 3 2                                | 1 0                                           |

| $\frac{1}{1} \frac{1}{1} \frac{1}$ | CFnCTL1   | 0       | 0           | 0           | CFnCKP CFnDAP CFnCKS2 C              | CFnCKS1 CFnCKS0                               |

| $\frac{1}{1} \frac{1}{1} \frac{1}$ |           |         |             |             |                                      |                                               |

| Sider (db)Sider (db)Sime (db) <td< td=""><th></th><td></td><td>CFnCKF</td><td>P CFnDAP</td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |         | CFnCKF      | P CFnDAP    |                                      |                                               |

| $\frac{Communication}{type 2} \frac{0}{1} \frac{1}{1} \frac{SOFFn}{SOFFn} (ucpu)} \frac{D2'}{D2'} \frac{D2'}{D2'}$                                                                                                                                                                                                                                                                                                                                                             |           |         | ion O       |             | SOFn (output) <u>D7 (D6 (D5 ) D4</u> | <u>↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ </u> |

| $\begin{array}{ c c c c c c } \hline \hline \\ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |         | ion O       | \$          | SOFn (output) <u>D7 D6 D5 D4 C</u>   |                                               |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |         | ion 1       | 0           | SCKFn (I/O)                          |                                               |

| 001fxx/4Master mode001fxx/6Master mode010fxx/8Master mode011fxx/12Master mode100fxx/16Master mode101fxx/32Master mode110fsagamMaster mode111External clock (SCKFn)Slave modeNotes1.If n is 0, 4, or 5, set the communication clock (fccLK) to 8 MHz or lower.2.If n is 1 to 3, or 6, set the communication clock (fccLK) to 5 MHz or lower.Remarks1.n = 0 to 4 (V850ES/JH3-E)n = 0 to 6 (V850ES/JJ3-E)2.When n = 0 or 1, m = 1When n = 2 or 3, m = 2When n = 4, m = 3When n = 5 or 6, m = 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |         | ion 1       | 1           | SCKFn (I/O) D7 \ D6 \ D5 \ D4 \ [    |                                               |

| 0       0       fxx/4       Master mode         0       0       1       fxx/6       Master mode         0       1       0       fxx/12       Master mode         0       1       1       fxx/12       Master mode         1       0       0       fxx/16       Master mode         1       0       1       fxx/32       Master mode         1       1       1       External clock (SCKFn)       Slave mode         Notes 1. If n is 0, 4, or 5, set the communication clock (fccLK) to 8 MHz or lower.         CL If n is 1 to 3, or 6, set the communication clock (fccLK) to 5 MHz or lower.         Set the communication clock (fccLK) to 5 MHz or lower.         Remarks 1. n = 0 to 4 (V850ES/JH3-E)         n = 0 to 6 (V850ES/JH3-E)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           | CENCKS2 | CEnCKS1     | CEnCKSO     | Communication clock (from Note       | Mada                                          |

| 001fixedMaster mode010fixedMaster mode010fixedMaster mode011fixedMaster mode100fixedMaster mode101fixedMaster mode110fisedMaster mode111fisedMaster mode111External clock (SCKFn)Slave mode111External clock (SCKFn)Slave modeNotes 1.If n is 0, 4, or 5, set the communication clock (fccLK) to 8 MHz or lower.2.If n is 1 to 3, or 6, set the communication clock (fccLK) to 5 MHz or lower.Remarks 1. n = 0 to 4 (V850ES/JH3-E)<br>n = 0 to 6 (V850ES/JJ3-E)2.When n = 0 or 1, m = 1<br>When n = 2 or 3, m = 2<br>When n = 4, m = 3<br>When n = 5 or 6, m = 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |         |             |             |                                      |                                               |

| 010fxx/8Master mode011fxx/12Master mode100fxx/16Master mode101fxx/32Master mode110fsmgmMaster mode111External clock (SCKFn)Slave modeNotes1.If n is 0, 4, or 5, set the communication clock (fccLK) to 5 MHz or lower.2.If n is 1 to 3, or 6, set the communication clock (fccLK) to 5 MHz or lower.Remarks1.n = 0 to 4 (V850ES/JJ3-E)2.When n = 0 or 1, m = 1When n = 2 or 3, m = 2When n = 4, m = 3When n = 5 or 6, m = 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |         |             |             |                                      |                                               |

| 011frx/12Master mode100frx/16Master mode101frx/32Master mode111fbRGmMaster mode111External clock (SCKFn)Slave modeNotes 1. If n is 0, 4, or 5, set the communication clock (fccLK) to 8 MHz or lower.2. If n is 1 to 3, or 6, set the communication clock (fccLK) to 5 MHz or lower.Remarks 1. $n = 0$ to 4 (V850ES/JH3-E) $n = 0$ to 6 (V850ES/JJ3-E)2. When $n = 0$ or 1, $m = 1$ When $n = 2$ or 3, $m = 2$ When $n = 4$ , $m = 3$ When $n = 5$ or 6, $m = 4$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |         |             |             |                                      |                                               |