#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 26                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 10x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 35-XFBGA, WLCSP                                                            |

| Supplier Device Package    | 35-WLCSP (2.82x2.53)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd21e15c-uut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 6. Signal Descriptions List

The following table gives details on signal names classified by peripheral.

| Signal Name      | Function                                                       | Туре            | Active Level |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------|-----------------|--------------|--|--|--|--|--|--|

| Analog Compa     | Analog Comparators - AC                                        |                 |              |  |  |  |  |  |  |

| AIN[3:0]         | AC Analog Inputs                                               | Analog          |              |  |  |  |  |  |  |

| CMP[:0]          | AC Comparator Outputs                                          | Digital         |              |  |  |  |  |  |  |

| Analog Digital   | Converter - ADC                                                |                 |              |  |  |  |  |  |  |

| AIN[19:0]        | ADC Analog Inputs                                              | Analog          |              |  |  |  |  |  |  |

| VREFA            | ADC Voltage External Reference A                               | Analog          |              |  |  |  |  |  |  |

| VREFB            | ADC Voltage External Reference B                               | Analog          |              |  |  |  |  |  |  |

| Digital Analog   | Converter - DAC                                                |                 |              |  |  |  |  |  |  |

| VOUT             | DAC Voltage output                                             | Analog          |              |  |  |  |  |  |  |

| VREFA            | DAC Voltage External Reference                                 | Analog          |              |  |  |  |  |  |  |

| External Interru | upt Controller                                                 |                 |              |  |  |  |  |  |  |

| EXTINT[15:0]     | External Interrupts                                            | Input           |              |  |  |  |  |  |  |

| NMI              | External Non-Maskable Interrupt                                | Input           |              |  |  |  |  |  |  |

| Generic Clock    | Generator - GCLK                                               |                 |              |  |  |  |  |  |  |

| GCLK_IO[7:0]     | Generic Clock (source clock or generic clock generator output) | I/O             |              |  |  |  |  |  |  |

| Inter-IC Sound   | Controller - I2S                                               |                 |              |  |  |  |  |  |  |

| MCK[1:0]         | Master Clock                                                   | I/O             |              |  |  |  |  |  |  |

| SCK[1:0]         | Serial Clock                                                   | I/O             |              |  |  |  |  |  |  |

| FS[1:0]          | I2S Word Select or TDM Frame Sync                              | I/O             |              |  |  |  |  |  |  |

| SD[1:0]          | Serial Data Input or Output                                    | I/O             |              |  |  |  |  |  |  |

| Power Manage     | er - PM                                                        |                 |              |  |  |  |  |  |  |

| RESETN           | Reset                                                          | Input           | Low          |  |  |  |  |  |  |

| Serial Commun    | nication Interface - SERCOMx                                   | 1               |              |  |  |  |  |  |  |

| PAD[3:0]         | SERCOM I/O Pads                                                | I/O             |              |  |  |  |  |  |  |

| System Contro    | System Control - SYSCTRL                                       |                 |              |  |  |  |  |  |  |

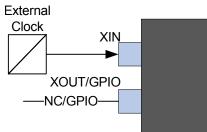

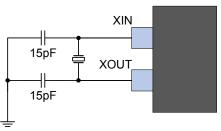

| XIN              | Crystal Input                                                  | Analog/ Digital |              |  |  |  |  |  |  |

| XIN32            | 32kHz Crystal Input                                            | Analog/ Digital |              |  |  |  |  |  |  |

| XOUT             | Crystal Output                                                 | Analog          |              |  |  |  |  |  |  |

| XOUT32           | 32kHz Crystal Output                                           | Analog          |              |  |  |  |  |  |  |

| Periph. | Base       | IRQ  | AHB C | lock     | APB C | lock     | Generic Clock      | PAC   |          | Events                |                            | DMA                     |         |

|---------|------------|------|-------|----------|-------|----------|--------------------|-------|----------|-----------------------|----------------------------|-------------------------|---------|

| Name    | Address    | Line | Index | Enabled  | Index | Enabled  | Index              | Index | Prot.    | User                  | Generator                  | Index                   | Sleep   |

|         |            |      |       | at Reset |       | at Reset |                    |       | at Reset |                       |                            |                         | Walking |

| TC5     | 0x42003400 | 20   |       |          | 13    | N        | 28                 | 13    | N        | 20: EV                | 57: OVF<br>58-59: MC0-1    | 30: OVF<br>31-32: MC0-1 | Y       |

| TC6     | 0x42003800 | 21   |       |          | 14    | N        | 29                 | 14    | N        | 21: EV                | 60: OVF<br>61-62: MC0-1    | 33: OVF<br>34-35: MC0-1 | Y       |

| TC7     | 0x42003C00 | 22   |       |          | 15    | N        | 29                 | 15    | N        | 22: EV                | 63: OVF<br>64-65: MC0-1    | 36: OVF<br>37-38: MC0-1 | Y       |

| ADC     | 0x42004000 | 23   |       |          | 16    | Y        | 30                 | 16    | N        | 23: START<br>24: SYNC | 66: RESRDY<br>67: WINMON   | 39: RESRDY              | Y       |

| AC      | 0x42004400 | 24   |       |          | 17    | N        | 31: DIG<br>32: ANA | 17    | N        | 25-26: SOC0-1         | 68-69: COMP0-1<br>70: WIN0 |                         | Y       |

| DAC     | 0x42004800 | 25   |       |          | 18    | N        | 33                 | 18    | N        | 27: START             | 71: EMPTY                  | 40: EMPTY               | Y       |

| PTC     | 0x42004C00 | 26   |       |          | 19    | N        | 34                 | 19    | N        | 28: STCONV            | 72: EOC<br>73: WCOMP       |                         |         |

| 125     | 0x42005000 | 27   |       |          | 20    | N        | 35-36              | 20    | N        |                       |                            | 41:42: RX<br>43:44: TX  | Y       |

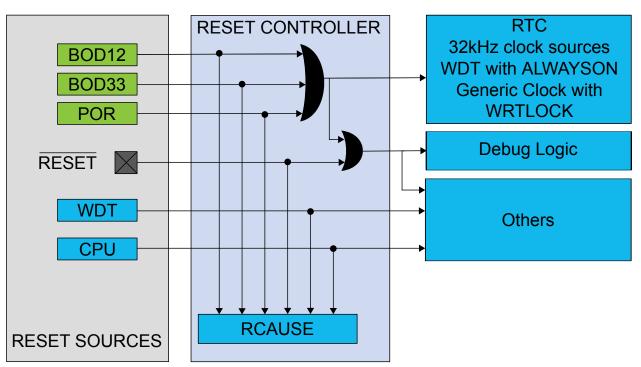

Figure 16-3. Reset Controller

## 16.6.2.8 Sleep Mode Controller

Sleep mode is activated by the Wait For Interrupt instruction (WFI). The Idle bits in the Sleep Mode register (SLEEP.IDLE) and the SLEEPDEEP bit of the System Control register of the CPU should be used as argument to select the level of the sleep mode.

There are two main types of sleep mode:

- IDLE mode: The CPU is stopped. Optionally, some synchronous clock domains are stopped, depending on the IDLE argument. Regulator operates in normal mode.

- STANDBY mode: All clock sources are stopped, except those where the RUNSTDBY bit is set. Regulator operates in low-power mode. Before entering standby mode the user must make sure that a significant amount of clocks and peripherals are disabled, so that the voltage regulator is not overloaded.

| Mode    | Level | Mode Entry                                   | Wake-Up Sources                                                    |

|---------|-------|----------------------------------------------|--------------------------------------------------------------------|

| IDLE    | 0     | SCR.SLEEPDEEP = 0<br>SLEEP.IDLE=Level<br>WFI | Synchronous <sup>(2)</sup> (APB, AHB), asynchronous <sup>(1)</sup> |

|         | 1     |                                              | Synchronous (APB), asynchronous                                    |

|         | 2     |                                              | Asynchronous                                                       |

| STANDBY |       | SCR.SLEEPDEEP = 1<br>WFI                     | Asynchronous                                                       |

| Table 16-3. | Sleep Mode | Entry and | Exit Table |

|-------------|------------|-----------|------------|

|-------------|------------|-----------|------------|

## Note:

- 1. Asynchronous: interrupt generated on generic clock or external clock or external event.

- 2. Synchronous: interrupt generated on the APB clock.

| Value   | Description        |

|---------|--------------------|

| 0xA     | 8192 clock cycles  |

| 0xB     | 16384 clock cycles |

| 0xC-0xF | Reserved           |

## 18.8.3 Early Warning Interrupt Control

| Name:                                       | EWCTRL                                     |  |  |  |  |

|---------------------------------------------|--------------------------------------------|--|--|--|--|

| Offset:                                     | 0x2                                        |  |  |  |  |

| Reset:                                      | N/A - Loaded from NVM User Row at start-up |  |  |  |  |

| Property: Write-Protected, Enable-Protected |                                            |  |  |  |  |

| Bit    | 7 | 6 | 5 | 4 | 3   | 2     | 1        | 0   |

|--------|---|---|---|---|-----|-------|----------|-----|

|        |   |   |   |   |     | EWOFF | SET[3:0] |     |

| Access |   |   |   |   | R/W | R/W   | R/W      | R/W |

| Reset  |   |   |   |   | х   | х     | х        | х   |

### Bits 3:0 – EWOFFSET[3:0]: Early Warning Interrupt Time Offset

These bits determine the number of GCLK\_WDT clocks in the offset from the start of the watchdog timeout period to when the Early Warning interrupt is generated. These bits are loaded from NVM User Row at start-up. Refer to *NVM User Row Mapping* for more details.

| Value   | Description        |

|---------|--------------------|

| 0x0     | 8 clock cycles     |

| 0x1     | 16 clock cycles    |

| 0x2     | 32 clock cycles    |

| 0x3     | 64 clock cycles    |

| 0x4     | 128 clock cycles   |

| 0x5     | 256 clocks cycles  |

| 0x6     | 512 clocks cycles  |

| 0x7     | 1024 clock cycles  |

| 0x8     | 2048 clock cycles  |

| 0x9     | 4096 clock cycles  |

| 0xA     | 8192 clock cycles  |

| 0xB     | 16384 clock cycles |

| 0xC-0xF | Reserved           |

## 18.8.4 Interrupt Enable Clear

| Name:            | INTENCLR        |

|------------------|-----------------|

| Offset:          | 0x4             |

| Reset:           | 0x00            |

| <b>Property:</b> | Write-Protected |

| PRESCALER[3:0] | Name    | Description                 |

|----------------|---------|-----------------------------|

| 0x7            | DIV128  | CLK_RTC_CNT = GCLK_RTC/128  |

| 0x8            | DIV256  | CLK_RTC_CNT = GCLK_RTC/256  |

| 0x9            | DIV512  | CLK_RTC_CNT = GCLK_RTC/512  |

| 0xA            | DIV1024 | CLK_RTC_CNT = GCLK_RTC/1024 |

| 0xB-0xF        |         | Reserved                    |

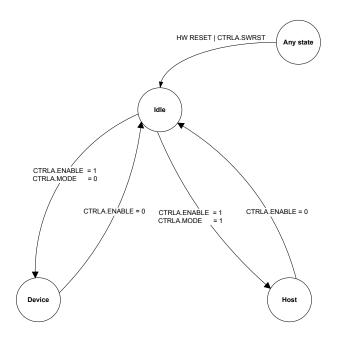

## Bits 3:2 – MODE[1:0]: Operating Mode

These bits define the operating mode of the RTC.

These bits are not synchronized.

| MODE[1:0] | Name    | Description            |

|-----------|---------|------------------------|

| 0x0       | COUNT32 | Mode 0: 32-bit Counter |

| 0x1       | COUNT16 | Mode 1: 16-bit Counter |

| 0x2       | CLOCK   | Mode 2: Clock/Calendar |

| 0x3       |         | Reserved               |

## Bit 1 – ENABLE: Enable

Due to synchronization, there is delay from writing CTRL.ENABLE until the peripheral is enabled/ disabled. The value written to CTRL.ENABLE will read back immediately, and the Synchronization Busy bit in the Status register (STATUS.SYNCBUSY) will be set. STATUS.SYNCBUSY will be cleared when the operation is complete.

This bit is not enable-protected.

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | The peripheral is disabled or being disabled. |

| 1     | The peripheral is enabled or being enabled.   |

## Bit 0 – SWRST: Software Reset

Writing a zero to this bit has no effect.

Writing a one to this bit resets all registers in the RTC, except DBGCTRL, to their initial state, and the RTC will be disabled.

Writing a one to CTRL.SWRST will always take precedence, meaning that all other writes in the same write-operation will be discarded.

Due to synchronization, there is a delay from writing CTRL.SWRST until the reset is complete. CTRL.SWRST and STATUS.SYNCBUSY will both be cleared when the reset is complete.

This bit is not enable-protected.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

## 19.8.3 Control - MODE2

## Bit 0 – CMP0: Compare 0 Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the Compare 0 Interrupt Enable bit and enable the Compare 0 interrupt.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | The compare 0 interrupt is disabled. |

| 1     | The compare 0 interrupt is enabled.  |

#### 19.8.12 Interrupt Enable Set - MODE1

Name: INTENSET Offset: 0x07 Reset: 0x00 Property: Write-Protected

| Bit    | 7   | 6       | 5 | 4 | 3 | 2 | 1    | 0    |

|--------|-----|---------|---|---|---|---|------|------|

|        | OVF | SYNCRDY |   |   |   |   | CMP1 | CMP0 |

| Access | R/W | R/W     |   |   |   |   | R/W  | R/W  |

| Reset  | 0   | 0       |   |   |   |   | 0    | 0    |

## Bit 7 – OVF: Overflow Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the Overflow interrupt bit and enable the Overflow interrupt.

| Va | alue | Description                         |

|----|------|-------------------------------------|

| 0  |      | The overflow interrupt is disabled. |

| 1  |      | The overflow interrupt is enabled.  |

## Bit 6 – SYNCRDY: Synchronization Ready Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the Synchronization Ready Interrupt Enable bit and enable the Synchronization Ready interrupt.

| Value | Description                                      |

|-------|--------------------------------------------------|

| 0     | The synchronization ready interrupt is disabled. |

| 1     | The synchronization ready interrupt is enabled.  |

## Bits 1,0 – CMPx : Compare x Interrupt Enable [x=1:0]

Writing a zero to this bit has no effect.

Writing a one to this bit will set the Compare x Interrupt Enable bit and enable the Compare x interrupt.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | The compare x interrupt is disabled. |

| 1     | The compare x interrupt is enabled.  |

## 19.8.13 Interrupt Enable Set - MODE2

Name: INTENSET Offset: 0x07

## Bit 0 – SWRST: Channel Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit resets the channel registers to their initial state. The bit can be set when the channel is disabled (ENABLE=0). Writing a '1' to this bit will be ignored as long as ENABLE=1. This bit is automatically cleared when the reset is completed.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

#### 20.8.19 Channel Control B

This register affects the DMA channel that is selected in the Channel ID register (CHID.ID).

Name:CHCTRLBOffset:0x44Reset:0x00000000Property:PAC Write-Protection, Enable-Protected

| 31    | 30                                 | 29                                                                                                                                               | 28                                  | 27                                                                                                                                                                                                                                                                  | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25                                                                                                                                                                                                                                                                                                                                                                                      | 24                                                                                                                                                                                                                                    |  |  |

|-------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|       |                                    |                                                                                                                                                  |                                     |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CMD[1:0]                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                       |  |  |

|       |                                    |                                                                                                                                                  |                                     |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                                                                                                                     | R/W                                                                                                                                                                                                                                   |  |  |

|       |                                    |                                                                                                                                                  |                                     |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                                     |  |  |

|       |                                    |                                                                                                                                                  |                                     |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                       |  |  |

| 23    | 22                                 | 21                                                                                                                                               | 20                                  | 19                                                                                                                                                                                                                                                                  | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17                                                                                                                                                                                                                                                                                                                                                                                      | 16                                                                                                                                                                                                                                    |  |  |

| TRIGA | CT[1:0]                            |                                                                                                                                                  |                                     |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                       |  |  |

| R/W   | R/W                                |                                                                                                                                                  |                                     |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                       |  |  |

| 0     | 0                                  |                                                                                                                                                  |                                     |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                       |  |  |

|       |                                    |                                                                                                                                                  |                                     |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                       |  |  |

| 15    | 14                                 | 13                                                                                                                                               | 12                                  | 11                                                                                                                                                                                                                                                                  | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9                                                                                                                                                                                                                                                                                                                                                                                       | 8                                                                                                                                                                                                                                     |  |  |

|       |                                    |                                                                                                                                                  | TRIGSRC[5:0]                        |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                       |  |  |

|       |                                    | R/W                                                                                                                                              | R/W                                 | R/W                                                                                                                                                                                                                                                                 | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W                                                                                                                                                                                                                                                                                                                                                                                     | R/W                                                                                                                                                                                                                                   |  |  |

|       |                                    | 0                                                                                                                                                | 0                                   | 0                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                                     |  |  |

|       |                                    |                                                                                                                                                  |                                     |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                       |  |  |

| 7     | 6                                  | 5                                                                                                                                                | 4                                   | 3                                                                                                                                                                                                                                                                   | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                                     |  |  |

|       | LVL                                | LVL[1:0] EVOE EVIE EVACT[2:0]                                                                                                                    |                                     |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                       |  |  |

|       | R/W                                | R/W                                                                                                                                              | R/W                                 | R/W                                                                                                                                                                                                                                                                 | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W                                                                                                                                                                                                                                                                                                                                                                                     | R/W                                                                                                                                                                                                                                   |  |  |

|       |                                    |                                                                                                                                                  |                                     |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                       |  |  |

|       | 23<br>TRIGA<br>R/W<br>0<br>15<br>7 | 23         22           TRIGACT[1:0]           R/W         R/W           0         0           15         14           7         6           LVL | 23     22     21       TRIGACT[1:0] | 23     22     21     20       TRIGACT[1:0]     20       R/W     R/W       0     0       15     14     13       15     14     13       R/W     R/W       0     0       15     14       15     14       16     5       17     6       5     4       LVL[1:0]     EVOE | 23       22       21       20       19         TRIGACT[1:0]       10       10         R/W       R/W       10       10         15       14       13       12       11         Image: Comparison of the system of the | 23       22       21       20       19       18         TRIGACT[1:0]       1       1       1         R/W       R/W       0       0       1         15       14       13       12       11       10         TRIGSRC[5:0]       TRIGSRC[5:0]       TRIGSRC[5:0]       1       10         7       6       5       4       3       2         LVL[1:0]       EVOE       EVIE       1       1 | CMD         CMD           23         22         21         20         19         18         17           23         22         21         20         19         18         17           TRIGACT[1:0]                  R/W         R/W |  |  |

## Bits 25:24 – CMD[1:0]: Software Command

These bits define the software commands. Refer to Channel Suspend and Channel Resume and Next Suspend Skip.

These bits are not enable-protected.

| CMD[1:0] | Name    | Description               |

|----------|---------|---------------------------|