#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status               | Active                                                                    |  |

|------------------------------|---------------------------------------------------------------------------|--|

| Core Processor               | ARM® Cortex®-M0+                                                          |  |

| Core Size 32-Bit Single-Core |                                                                           |  |

| Speed 48MHz                  |                                                                           |  |

| Connectivity                 | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                            |  |

| Peripherals                  | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |  |

| Number of I/O                | 26                                                                        |  |

| Program Memory Size          | 64KB (64K x 8)                                                            |  |

| Program Memory Type          | FLASH                                                                     |  |

| EEPROM Size                  | -                                                                         |  |

| RAM Size                     | 8K x 8                                                                    |  |

| Voltage - Supply (Vcc/Vdd)   | d) 1.62V ~ 3.6V                                                           |  |

| Data Converters              | A/D 10x12b; D/A 1x10b                                                     |  |

| Oscillator Type              | Internal                                                                  |  |

| Operating Temperature        | -40°C ~ 125°C (TA)                                                        |  |

| Mounting Type                | Surface Mount                                                             |  |

| Package / Case               | 32-TQFP                                                                   |  |

| Supplier Device Package      | 32-TQFP (7x7)                                                             |  |

| Purchase URL                 | https://www.e-xfl.com/product-detail/microchip-technology/atsamd21e16b-af |  |

|                              |                                                                           |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 36. PTC  | - Peripheral Touch Controller         | 781 |

|----------|---------------------------------------|-----|

| 36.1.    | Overview                              |     |

| 36.2.    | Features                              |     |

| 36.3.    | Block Diagram                         |     |

| 36.4.    | Signal Description                    |     |

| 36.5.    | Product Dependencies                  |     |

| 36.6.    | Functional Description                |     |

| 37. Elec | trical Characteristics                | 786 |

| 37.1.    | Disclaimer                            |     |

| 37.2.    | Absolute Maximum Ratings              |     |

| 37.3.    | General Operating Ratings             |     |

| 37.4.    | Supply Characteristics                |     |

| 37.5.    | Maximum Clock Frequencies             |     |

| 37.6.    | Power Consumption                     |     |

| 37.7.    | Peripheral Power Consumption          | 795 |

| 37.8.    | I/O Pin Characteristics               | 798 |

| 37.9.    | Injection Current                     |     |

| 37.10    | . Analog Characteristics              |     |

| 37.11    | . NVM Characteristics                 | 816 |

| 37.12    | . Oscillators Characteristics         | 817 |

| 37.13    | . PTC Typical Characteristics         |     |

| 37.14    | . USB Characteristics                 |     |

| 37.15    | . Timing Characteristics              | 832 |

| 38. Pack | aging Information                     |     |

| 38.1.    | Thermal Considerations                |     |

| 38.2.    | Package Drawings                      | 843 |

| 38.3.    | Soldering Profile                     |     |

| 39. Sche | ematic Checklist                      | 855 |

| 39.1.    | Introduction                          | 855 |

| 39.2.    | Power Supply                          |     |

| 39.3.    | External Analog Reference Connections | 856 |

| 39.4.    | External Reset Circuit                | 858 |

| 39.5.    | Clocks and Crystal Oscillators        | 859 |

| 39.6.    | Unused or Unconnected Pins            | 862 |

| 39.7.    | Programming and Debug Ports           |     |

| 39.8.    | USB Interface                         |     |

| 40. Erra | ta                                    |     |

| 40.1.    | Device Variant A                      |     |

| 40.2.    | Device Variant B                      |     |

| 40.3.    | Device Variant C                      | 908 |

| 41. Con  | ventions                              | 912 |

| 41.1.    | Numerical Notation                    |     |

| 41.2.    | Memory Size and Type                  | 912 |

### 11.2.2 Interrupt Line Mapping

Each of the 28 interrupt lines is connected to one peripheral instance, as shown in the table below. Each peripheral can have one or more interrupt flags, located in the peripheral's Interrupt Flag Status and Clear (INTFLAG) register. The interrupt flag is set when the interrupt condition occurs. Each interrupt in the peripheral can be individually enabled by writing a one to the corresponding bit in the peripheral's Interrupt Enable Set (INTENSET) register, and disabled by writing a one to the corresponding bit in the peripheral's Interrupt Enable Clear (INTENCLR) register. An interrupt request is generated from the peripheral are ORed together on system level, generating one interrupt request for each peripheral. An interrupt request will set the corresponding interrupt pending bit in the NVIC interrupt, it must be enabled in the NVIC interrupt enable register (SETPEND/CLRPEND bits in ISPR/ICPR). For the NVIC to activate the interrupt, it must be enabled in the NVIC interrupt enable register (SETENA/CLRENA bits in ISER/ICER). The NVIC interrupt priority registers IPR0-IPR7 provide a priority field for each interrupt.

| Peripheral Source                          | NVIC Line |

|--------------------------------------------|-----------|

| EIC NMI – External Interrupt Controller    | NMI       |

| PM – Power Manager                         | 0         |

| SYSCTRL – System Control                   | 1         |

| WDT – Watchdog Timer                       | 2         |

| RTC – Real Time Counter                    | 3         |

| EIC – External Interrupt Controller        | 4         |

| NVMCTRL – Non-Volatile Memory Controller   | 5         |

| DMAC - Direct Memory Access Controller     | 6         |

| USB - Universal Serial Bus                 | 7         |

| EVSYS – Event System                       | 8         |

| SERCOM0 – Serial Communication Interface 0 | 9         |

| SERCOM1 – Serial Communication Interface 1 | 10        |

| SERCOM2 – Serial Communication Interface 2 | 11        |

| SERCOM3 – Serial Communication Interface 3 | 12        |

| SERCOM4 – Serial Communication Interface 4 | 13        |

| SERCOM5 – Serial Communication Interface 5 | 14        |

| TCC0 – Timer Counter for Control 0         | 15        |

| TCC1 – Timer Counter for Control 1         | 16        |

| TCC2 – Timer Counter for Control 2         | 17        |

| TC3 – Timer Counter 3                      | 18        |

| TC4 – Timer Counter 4                      | 19        |

| TC5 – Timer Counter 5                      | 20        |

- MASTER: Contains the main trace enable bit and other trace control fields,

- FLOW: Contains the WATERMARK address and the AUTOSTOP and AUTOHALT control bits,

- BASE: Indicates where the SRAM is located in the processor memory map. This register is provided to enable auto discovery of the MTB SRAM location, by a debug agent.

See the CoreSight MTB-M0+ Technical Reference Manual for a detailed description of these registers.

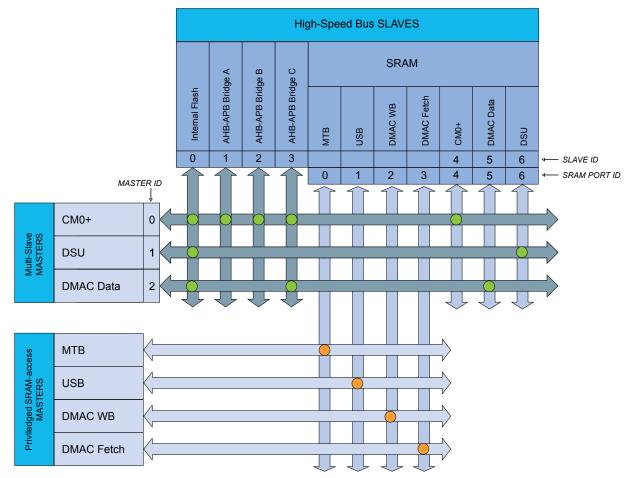

## 11.4 High-Speed Bus System

### 11.4.1 Features

High-Speed Bus Matrix has the following features:

- Symmetric crossbar bus switch implementation

- Allows concurrent accesses from different masters to different slaves

- 32-bit data bus

- Operation at a one-to-one clock frequency with the bus masters

#### 11.4.2 Configuration

| GAIN[2:0] | Recommended Max Frequency |  |

|-----------|---------------------------|--|

| 0x0       | 2MHz                      |  |

| 0x1       | 4MHz                      |  |

| 0x2       | 8MHz                      |  |

| 0x3       | 16MHz                     |  |

| 0x4       | 30MHz                     |  |

| 0x5-0x7   | Reserved                  |  |

#### Bit 7 – ONDEMAND: On Demand Control

The On Demand operation mode allows an oscillator to be enabled or disabled, depending on peripheral clock requests.

In On Demand operation mode, i.e., if the XOSC.ONDEMAND bit has been previously written to one, the oscillator will be running only when requested by a peripheral. If there is no peripheral requesting the oscillator s clock source, the oscillator will be in a disabled state.

If On Demand is disabled, the oscillator will always be running when enabled.

In standby sleep mode, the On Demand operation is still active if the XOSC.RUNSTDBY bit is one. If XOSC.RUNSTDBY is zero, the oscillator is disabled.

| Value | Description                                                                                    |  |

|-------|------------------------------------------------------------------------------------------------|--|

| 0     | The oscillator is always on, if enabled.                                                       |  |

| 1     | The oscillator is enabled when a peripheral is requesting the oscillator to be used as a clock |  |

|       | source. The oscillator is disabled if no peripheral is requesting the clock source.            |  |

#### Bit 6 – RUNSTDBY: Run in Standby

This bit controls how the XOSC behaves during standby sleep mode:

| Value | Description                                                                                                                                                                                                                                        |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0     | The oscillator is disabled in standby sleep mode.                                                                                                                                                                                                  |  |

| 1     | The oscillator is not stopped in standby sleep mode. If XOSC.ONDEMAND is one, the clock source will be running when a peripheral is requesting the clock. If XOSC.ONDEMAND is zero, the clock source will always be running in standby sleep mode. |  |

#### Bit 2 – XTALEN: Crystal Oscillator Enable

This bit controls the connections between the I/O pads and the external clock or crystal oscillator:

| Value | Description                                                               |  |

|-------|---------------------------------------------------------------------------|--|

| 0     | External clock connected on XIN. XOUT can be used as general-purpose I/O. |  |

| 1     | Crystal connected to XIN/XOUT.                                            |  |

#### Bit 1 – ENABLE: Oscillator Enable

| Value | Description                 |

|-------|-----------------------------|

| 0     | The oscillator is disabled. |

| 1     | The oscillator is enabled.  |

17.8.6 32kHz External Crystal Oscillator (XOSC32K) Control

#### Bit 12 – LBYPASS: Lock Bypass

|   | /alue | Description                                                               |  |

|---|-------|---------------------------------------------------------------------------|--|

| ( | )     | Normal Mode: the CLK_FDPLL96M is turned off when lock signal is low.      |  |

| • |       | Lock Bypass Mode: the CLK_FDPLL96M is always running, lock is irrelevant. |  |

#### Bits 10:8 – LTIME[2:0]: Lock Time

These bits select Lock Timeout.

| LTIME[2:0] | Name    | Description                      |

|------------|---------|----------------------------------|

| 0x0        | DEFAULT | No time-out                      |

| 0x1-0x3    |         | Reserved                         |

| 0x4        | 8MS     | Time-out if no lock within 8 ms  |

| 0x5        | 9MS     | Time-out if no lock within 9 ms  |

| 0x6        | 10MS    | Time-out if no lock within 10 ms |

| 0x7        | 11MS    | Time-out if no lock within 11 ms |

# Bits 5:4 – REFCLK[1:0]: Reference Clock Selection

These bits select the CLK\_FDPLL96M\_REF source.

| REFCLK[1:0] | Name      | Description               |

|-------------|-----------|---------------------------|

| 0x0         | XOSC32    | XOSC32 clock reference    |

| 0x1         | XOSC      | XOSC clock reference      |

| 0x2         | GCLK_DPLL | GCLK_DPLL clock reference |

| 0x3         |           | Reserved                  |

#### Bit 3 – WUF: Wake Up Fast

| Value | Description                                                        |

|-------|--------------------------------------------------------------------|

| 0     | DPLL CK output is gated until complete startup time and lock time. |

| 1     | DPLL CK output is gated until startup time only.                   |

#### Bit 2 – LPEN: Low-Power Enable

| Value | Description                                                                                                        |

|-------|--------------------------------------------------------------------------------------------------------------------|

| 0     | The time to digital converter is selected.                                                                         |

| 1     | The time to digital converter is not selected, this will improve power consumption but increase the output jitter. |

#### Bits 1:0 – FILTER[1:0]: Proportional Integral Filter Selection

These bits select the DPLL filter type.

| FILTER[1:0] | Name    | Description          |

|-------------|---------|----------------------|

| 0x0         | DEFAULT | Default filter mode  |

| 0x1         | LBFILT  | Low bandwidth filter |

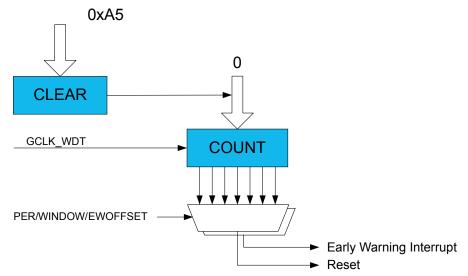

## 18.3 Block Diagram

Figure 18-1. WDT Block Diagram

## 18.4 Signal Description

Not applicable.

## 18.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### 18.5.1 I/O Lines

Not applicable.

#### 18.5.2 Power Management

The WDT can continue to operate in any sleep mode where the selected source clock is running. The WDT interrupts can be used to wake up the device from sleep modes. The events can trigger other operations in the system without exiting sleep modes.

#### **Related Links**

PM - Power Manager

#### 18.5.3 Clocks

The WDT bus clock (CLK\_WDT\_APB) is enabled by default, and can be enabled and disabled in the Power Manager. Refer to *PM* – *Power Manager* for details.

A generic clock (GCLK\_WDT) is required to clock the WDT. This clock must be configured and enabled in the Generic Clock Controller before using the WDT. Refer to *GCLK – Generic Clock Controller* for details. This generic clock is asynchronous to the user interface clock (CLK\_WDT\_APB). Due to this asynchronicity, accessing certain registers will require synchronization between the clock domains. Refer to *Synchronization* for further details.

GCLK\_WDT is intended to be sourced from the clock of the internal ultra-low-power (ULP) oscillator. Due to the ultralow- power design, the oscillator is not very accurate, and so the exact time-out period may vary from device to device. This variation must be kept in mind when designing software that uses the

| Offset | Name     | Bit<br>Pos. |            |           |          |  |  |  |  |  |

|--------|----------|-------------|------------|-----------|----------|--|--|--|--|--|

| 0x0D   |          |             |            |           |          |  |  |  |  |  |

|        | Reserved |             |            |           |          |  |  |  |  |  |

| 0x0F   |          |             |            |           |          |  |  |  |  |  |

| 0x10   | COUNT    | 7:0         |            | COUI      | NT[7:0]  |  |  |  |  |  |

| 0x11   | COUNT    | 15:8        |            | COUN      | IT[15:8] |  |  |  |  |  |

| 0x12   | Reserved |             |            |           |          |  |  |  |  |  |

| 0x13   | Reserved |             |            |           |          |  |  |  |  |  |

| 0x14   | PER      | 7:0         |            | PEF       | R[7:0]   |  |  |  |  |  |

| 0x15   | PER      | 15:8        | PER[15:8]  |           |          |  |  |  |  |  |

| 0x16   | Reserved |             |            |           |          |  |  |  |  |  |

| 0x17   | Reserved |             |            |           |          |  |  |  |  |  |

| 0x18   | COMPO    | 7:0         | ! ! !      | COMP[7:0] |          |  |  |  |  |  |

| 0x19   | COMP0    | 15:8        | COMP[15:8] |           |          |  |  |  |  |  |

| 0x1A   | 001454   | 7:0         |            | CON       | IP[7:0]  |  |  |  |  |  |

| 0x1B   | COMP1    | 15:8        |            | COM       | P[15:8]  |  |  |  |  |  |

## Table 19-3. MODE2 - Mode Register Summary

| Offset           | Name     | Bit<br>Pos. |          |         |        |        |            |         |           |          |

|------------------|----------|-------------|----------|---------|--------|--------|------------|---------|-----------|----------|

| 0x00             | CTRL     | 7:0         | MATCHCLR | CLKREP  |        |        | MOD        | E[1:0]  | ENABLE    | SWRST    |

| 0x01             | UTKE     | 15:8        |          |         |        |        |            | PRESCA  | ALER[3:0] |          |

| 0x02             | READREQ  | 7:0         |          |         |        |        | ADDI       | R[5:0]  |           |          |

| 0x03             | READREQ  | 15:8        | RREQ     | RCONT   |        |        |            |         |           |          |

| 0x04             | EVCTRL   | 7:0         | PEREO7   | PEREO6  | PEREO5 | PEREO4 | PEREO3     | PEREO2  | PEREO1    | PEREO0   |

| 0x05             | EVCIRE   | 15:8        | OVFEO    |         |        |        |            |         |           | ALARMEO0 |

| 0x06             | INTENCLR | 7:0         | OVF      | SYNCRDY |        |        |            |         |           | ALARM0   |

| 0x07             | INTENSET | 7:0         | OVF      | SYNCRDY |        |        |            |         |           | ALARM0   |

| 0x08             | INTFLAG  | 7:0         | OVF      | SYNCRDY |        |        |            |         |           | ALARM0   |

| 0x09             | Reserved |             |          |         |        |        |            |         |           |          |

| 0x0A             | STATUS   | 7:0         | SYNCBUSY |         |        |        |            |         |           |          |

| 0x0B             | DBGCTRL  | 7:0         |          |         |        |        |            |         |           | DBGRUN   |

| 0x0C             | FREQCORR | 7:0         | SIGN     |         |        | :      | VALUE[6:0] | :       | :         |          |

| 0x0D<br><br>0x0F | Reserved |             |          |         |        |        |            |         |           |          |

| 0x10             |          | 7:0         | MINUT    | FE[1:0] |        |        | SECO       | ND[5:0] |           |          |

| 0x11             | CLOCK    | 15:8        |          | HOU     | R[3:0] |        |            | MINU    | TE[5:2]   |          |

| 0x12             | CLUCK    | 23:16       | MONT     | H[1:0]  |        |        | DAY[4:0]   |         |           | HOUR[4]  |

| 0x13             | 31:24    |             |          |         | YEAI   | R[5:0] |            |         | MON       | TH[3:2]  |

| 0x14<br><br>0x17 | Reserved |             |          |         |        |        |            |         |           |          |

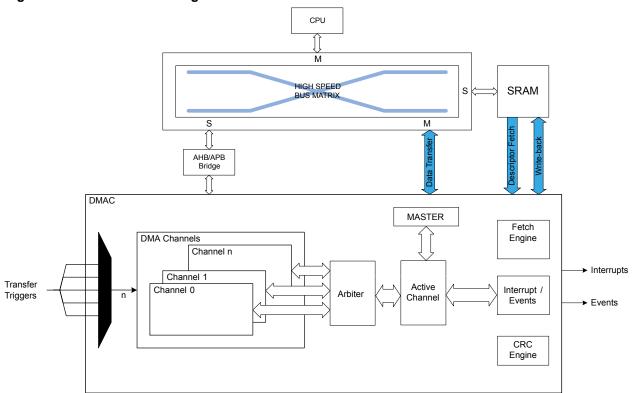

# 20.3 Block Diagram

Figure 20-1. DMAC Block Diagram

## 20.4 Signal Description

Not applicable.

## 20.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### 20.5.1 I/O Lines

Not applicable.

### 20.5.2 Power Management

The DMAC will continue to operate in any sleep mode where the selected source clock is running. The DMAC's interrupts can be used to wake up the device from sleep modes. Events connected to the event system can trigger other operations in the system without exiting sleep modes. On hardware or software reset, all registers are set to their reset value.

#### **Related Links**

PM – Power Manager

#### 20.5.3 Clocks

The DMAC bus clock (CLK\_DMAC\_APB) must be configured and enabled in the Power Manager before using the DMAC.

| Action                         | CHCTRLB.EVACT | CHCTRLB.TRGSRC |

|--------------------------------|---------------|----------------|

| Conditional Transfer on Strobe | TRIG          | any peripheral |

| Conditional Transfer           | CTRIG         | -              |

| Conditional Block Transfer     | CBLOCK        | -              |

| Channel Suspend                | SUSPEND       |                |

| Channel Resume                 | RESUME        | -              |

| Skip Next Block Suspend        | SSKIP         |                |

#### **Normal Transfer**

The event input is used to trigger a beat or burst transfer on peripherals.

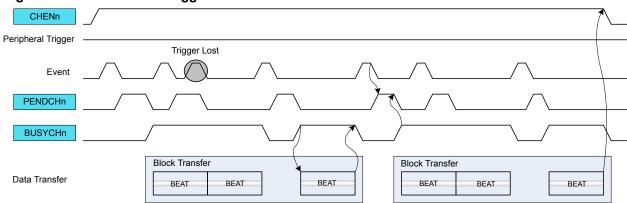

The event is acknowledged as soon as the event is received. When received, both the Channel Pending status bit in the Channel Status register (CHSTATUS.PEND) and the corresponding Channel n bit in the Pending Channels register (PENDCH.PENDCHn) are set. If the event is received while the channel is pending, the event trigger is lost.

The figure below shows an example where beat transfers are enabled by internal events.

Figure 20-11. Beat Event Trigger Action

## **Conditional Transfer on Strobe**

The event input is used to trigger a transfer on peripherals with pending transfer requests. This event action is intended to be used with peripheral triggers, e.g. for timed communication protocols or periodic transfers between peripherals: only when the peripheral trigger coincides with the occurrence of a (possibly cyclic) event the transfer is issued.

The event is acknowledged as soon as the event is received. The peripheral trigger request is stored internally when the previous trigger action is completed (i.e. the channel is not pending) and when an active event is received. If the peripheral trigger is active, the DMA will wait for an event before the peripheral trigger is internally registered. When both event and peripheral transfer trigger are active, both CHSTATUS.PEND and PENDCH.PENDCHn are set. A software trigger will now trigger a transfer.

The figure below shows an example where the peripheral beat transfer is started by a conditional strobe event action.

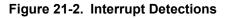

When an external interrupt is configured for level detection and when filtering is disabled, detection is done asynchronously. Asynchronuous detection does not require GCLK\_EIC, but interrupt and events can still be generated. If filtering or edge detection is enabled, the EIC automatically requests GCLK\_EIC to operate. GCLK\_EIC must be enabled in the GCLK module.

The detection delay depends on the detection mode.

#### Table 21-2. Interrupt Latency

| Detection mode       | Latency (worst case)                              |

|----------------------|---------------------------------------------------|

| Level without filter | Three CLK_EIC_APB periods                         |

| Level with filter    | Four GCLK_EIC periods + Three CLK_EIC_APB periods |

| Edge without filter  | Four GCLK_EIC periods + Three CLK_EIC_APB periods |

| Edge with filter     | Six GCLK_EIC periods + Three CLK_EIC_APB periods  |

#### **Related Links**

GCLK - Generic Clock Controller

#### 21.6.4 Additional Features

#### 21.6.4.1 Non-Maskable Interrupt (NMI)

The non-maskable interrupt pin can also generate an interrupt on edge or level detection, but it is configured with the dedicated NMI Control register (NMICTRL). To select the sense for NMI, write to the NMISENSE bit group in the NMI Control register (NMICTRL.NMISENSE). NMI filtering is enabled by writing a '1' to the NMI Filter Enable bit (NMICTRL.NMIFILTEN).

If edge detection or filtering is required, enable GCLK\_EIC or CLK\_ULP32K.

NMI detection is enabled only by the NMICTRL.NMISENSE value, and the EIC is not required to be enabled.

When an NMI is detected, the non-maskable interrupt flag in the NMI Flag Status and Clear register is set (NMIFLAG.NMI). NMI interrupt generation is always enabled, and NMIFLAG.NMI generates an interrupt request when set.

#### 21.6.5 DMA Operation

Not applicable.

| Condition                                                  | Request                                          |           |       |  |  |  |  |  |

|------------------------------------------------------------|--------------------------------------------------|-----------|-------|--|--|--|--|--|

|                                                            | DMA                                              | Interrupt | Event |  |  |  |  |  |

| Data needed for transmit<br>(TX) (Master transmit<br>mode) | Yes<br>(request cleared when<br>data is written) |           | NA    |  |  |  |  |  |

| Data needed for transmit<br>(RX) (Master transmit<br>mode) | Yes<br>(request cleared when<br>data is read)    |           |       |  |  |  |  |  |

| Master on Bus (MB)                                         |                                                  | Yes       |       |  |  |  |  |  |

| Stop received (SB)                                         |                                                  | Yes       |       |  |  |  |  |  |

| Error (ERROR)                                              |                                                  | Yes       |       |  |  |  |  |  |

#### 28.6.4.1 DMA Operation

Smart mode must be enabled for DMA operation in the Control B register by writing CTRLB.SMEN=1.

#### Slave DMA

When using the I<sup>2</sup>C slave with DMA, an address match will cause the address interrupt flag (INTFLAG.ADDRMATCH) to be raised. After the interrupt has been serviced, data transfer will be performed through DMA.

The I<sup>2</sup>C slave generates the following requests:

- Write data received (RX): The request is set when master write data is received. The request is cleared when DATA is read.

- Read data needed for transmit (TX): The request is set when data is needed for a master read operation. The request is cleared when DATA is written.

#### Master DMA

When using the I<sup>2</sup>C master with DMA, the ADDR register must be written with the desired address (ADDR.ADDR), transaction length (ADDR.LEN), and transaction length enable (ADDR.LENEN). When ADDR.LENEN is written to 1 along with ADDR.ADDR, ADDR.LEN determines the number of data bytes in the transaction from 0 to 255. DMA is then used to transfer ADDR.LEN bytes followed by an automatically generated NACK (for master reads) and a STOP.

If a NACK is received by the slave for a master write transaction before ADDR.LEN bytes, a STOP will be automatically generated and the length error (STATUS.LENERR) will be raised along with the INTFLAG.ERROR interrupt.

The I<sup>2</sup>C master generates the following requests:

- Read data received (RX): The request is set when master read data is received. The request is cleared when DATA is read.

- Write data needed for transmit (TX): The request is set when data is needed for a master write operation. The request is cleared when DATA is written.

#### 28.6.4.2 Interrupts

The I<sup>2</sup>C slave has the following interrupt sources. These are asynchronous interrupts. They can wake-up the device from any sleep mode:

Error (ERROR)

Data bits are sent on the falling edge of the Serial Clock and sampled on the rising edge of the Serial Clock. The Word Select line indicates the channel in transmission, a low level for the left channel and a high level for the right channel.

In I<sup>2</sup>S format, typical configurations are described below. These configurations do not list all necessary settings, but only basic ones. Other configuration settings are to be done as per requirement such as clock and DMA configurations.

### Case 1: I<sup>2</sup>S 16-bit compact stereo

- Slot size configured as 16 bits (CLKCTRL0.SLOTSIZE = 0x1)

- Number of slots configured as 2 (CLKCTRL0.NBSLOTS = 0x1)

- Data size configured as 16-bit compact stereo (SERCTRL0.DATASIZE = 0x05)

- Data delay from Frame Sync configured as 1-bit delay (CLKCTRLn.BITDELAY = 0x01)

- Frame Sync Width configured as HALF frame (CLKCTRLn.FSWIDTH = 0x01)

### Case 2: I<sup>2</sup>S 24-bit stereo Transmitterwith 24-bit slot

- Slot size configured as 24 bits (CLKCTRL0.SLOTSIZE = 0x2)

- Number of slots configured as 2 (CLKCTRL0.NBSLOTS = 0x1)

- Data size configured as 24 bits (SERCTRL0.DATASIZE = 0x01)

- Data delay from Frame Sync configured as 1-bit delay (CLKCTRLn.BITDELAY = 0x01)

- Frame Sync Width configured as HALF frame (CLKCTRLn.FSWIDTH = 0x01)

In both cases, it will ensure that Word select signal is 'low level' for the left channel and 'high level' for the right channel.

The length of transmitted words can be chosen among 8, 16, 18, 20, 24, and 32 bits by writing the Data Word Size bit group in the Serializer Control mregister (SERCTRLm.DATASIZE).

If the slot allows for more data bits than the number of bits specified in the respective DATASIZE field, additional bits are appended to the transmitted or received data word as specified in the SERCTRLm.EXTEND field. If the slot allows less data bits than programmed, the extra bits are not transmitted, or received data word is extended based on the EXTEND field value.

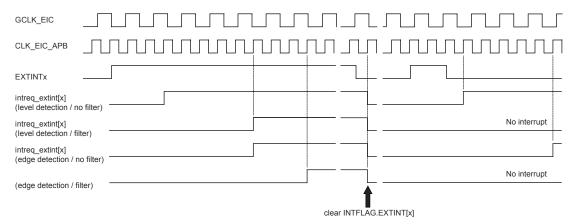

#### 29.6.5 TDM Format - Reception and Transmission Sequence

In Time Division Multiplexed (TDM) format, the number of data slots sent or received within each frame will be (CLKCTRLn.NBSLOTS + 1).

By configuring the CLKCTRLn register (CLKCTRLn.FSWIDTH and CLKCTRLn.FSINV), the Frame Sync pulse width and polarity can be modified.

By configuring SERCTRLm, data bits can be left-adjusted or right-adjusted in the slot. It can also configure the data transmission/reception with either the MSB or the LSB transmitted/received first and starting the transmission/reception either at the transition of the FSn pin or one clock period after.

#### Figure 29-6. TDM Format Reception and Transmission Sequence

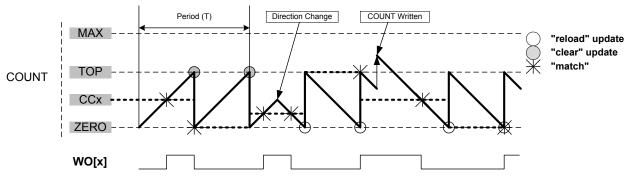

| Name       | Operation            | ТОР | Update                       | Output Waveform               |           | OVFIF/Event |      |  |

|------------|----------------------|-----|------------------------------|-------------------------------|-----------|-------------|------|--|

|            |                      |     |                              | On Match                      | On Update | Up          | Down |  |

| NPWM       | Single-<br>slope PWM | PER | TOP/<br>ZERO                 | See section<br>Polarity' belo | •         | TOP         | ZERO |  |

| DSCRITICAL | Dual-slope<br>PWM    | PER | ZERO                         | -                             |           | -           | ZERO |  |

| DSBOTTOM   | Dual-slope<br>PWM    | PER | ZERO                         |                               |           | -           | ZERO |  |

| DSBOTH     | Dual-slope<br>PWM    | PER | TOP <sup>(1)</sup> &<br>ZERO |                               |           | ТОР         | ZERO |  |

| DSTOP      | Dual-slope<br>PWM    | PER | ZERO                         |                               |           | TOP         | -    |  |

1. The UPDATE condition on TOP only will occur when circular buffer is enabled for the channel.

### **Related Links**

Circular Buffer PORT: IO Pin Controller

### Normal Frequency (NFRQ)

For Normal Frequency generation, the period time (T) is controlled by the period register (PER). The waveform generation output (WO[x]) is toggled on each compare match between COUNT and CCx, and the corresponding Match or Capture Channel x Interrupt Flag (EVCTRL.MCEOx) will be set.

## Figure 31-4. Normal Frequency Operation

#### Match Frequency (MFRQ)

For Match Frequency generation, the period time (T) is controlled by CC0 register instead of PER. WO[0] toggles on each update condition.

# 32.7 Register Summary

The register mapping depends on the Operating Mode field in the Control A register (CTRLA.MODE). The register summary is detailed below.

#### 32.7.1 Common Device Summary

| Offset | Name      | Bit Pos. |                         |                  |  |       |              |         |        |             |  |

|--------|-----------|----------|-------------------------|------------------|--|-------|--------------|---------|--------|-------------|--|

| 0x00   | CTRLA     | 7:0      | MODE                    |                  |  |       |              | RUNSTBY | ENABLE | SWRST       |  |

| 0x01   | Reserved  |          |                         |                  |  |       |              |         |        |             |  |

| 0x02   | SYNCBUSY  | 7:0      |                         |                  |  |       |              |         | ENABLE | SWRST       |  |

| 0x03   | QOSCTRL   | 7:0      |                         | DQOS[1:0] CQOS[1 |  |       |              |         |        | S[1:0]      |  |

| 0x0D   | FSMSTATUS | 7:0      |                         |                  |  |       | FSMSTATE[6:0 | )]      |        |             |  |

| 0x24   |           | 7:0      |                         |                  |  | DESCA | DD[7:0]      |         |        |             |  |

| 0x25   | DESCADD   | 15:8     |                         |                  |  | DESCA | DD[15:8]     |         |        |             |  |

| 0x26   | DESCADD   | 23:16    |                         |                  |  | DESCA | DD[23:16]    |         |        |             |  |

| 0x27   |           | 31:24    |                         | DESCADD[31:24]   |  |       |              |         |        |             |  |

| 0x28   | PADCAL    | 7:0      | TRANSN[1:0] TRANSP[4:0] |                  |  |       |              |         |        |             |  |

| 0x29   | FADCAL    | 15:8     |                         | TRIM[2:0]        |  |       |              |         |        | TRANSN[4:2] |  |

#### 32.7.2 Device Summary

### Table 32-1. General Device Registers

| Offset | Name     | Bit Pos. |         |          |           |        |            |          |         |         |

|--------|----------|----------|---------|----------|-----------|--------|------------|----------|---------|---------|

| 0x04   | Reserved |          |         |          |           |        |            |          |         |         |

| 0x05   | Reserved |          |         |          |           |        |            |          |         |         |

| 0x06   | Reserved |          |         |          |           |        |            |          |         |         |

| 0x07   | Reserved |          |         |          |           |        |            |          |         |         |

| 0x08   | CTRLB    | 7:0      |         |          |           | NREPLY | SPDCC      | DNF[1:0] | UPRSM   | DETACH  |

| 0x09   | CIRLB    | 15:8     |         |          |           |        | LPMHD      | DSK[1:0] | GNAK    |         |

| 0x0A   | DADD     |          | ADDEN   |          |           |        | DADD[6:0]  |          |         |         |

| 0x0B   | Reserved |          |         |          |           |        |            |          |         |         |

| 0x0C   | STATUS   | 7:0      | LINESTA | ATE[1:0] |           |        | SPEE       | D[1:0]   |         |         |

| 0x0E   | Reserved |          |         |          |           |        |            |          |         |         |

| 0x0F   | Reserved |          |         |          |           |        |            |          |         |         |

| 0x10   | FNUM     | 7:0      |         |          | FNUM[4:0] |        |            |          |         |         |

| 0x11   | FINUM    | 15:8     | FNCERR  |          |           |        | FNUM[10:5] |          |         |         |

| 0x12   | Reserved |          |         |          |           |        |            |          |         |         |

| 0x14   | INTENCLR | 7:0      | RAMACER | UPRSM    | EORSM     | WAKEUP | EORST      | SOF      |         | SUSPEND |

| 0x15   | INTENCLR | 15:8     |         |          |           |        |            |          | LPMSUSP | LPMNYET |

| 0x16   | Reserved |          |         |          |           |        |            |          |         |         |

| 0x17   | Reserved |          |         |          |           |        |            |          |         |         |

| 0x18   | INTENOET | 7:0      | RAMACER | UPRSM    | EORSM     | WAKEUP | EORST      | SOF      |         | SUSPEND |

| 0x19   | INTENSET | 15:8     |         |          |           |        |            |          | LPMSUSP | LPMNYET |

| 0x1A   | Reserved |          |         |          |           |        |            |          |         |         |

| 0x1B   | Reserved |          |         |          |           |        |            |          |         |         |

| 0x1C   |          | 7:0      | RAMACER | UPRSM    | EORSM     | WAKEUP | EORST      | SOF      |         | SUSPEND |

| 0x1D   | INTFLAG  | 15:8     |         |          |           |        |            |          | LPMSUSP | LPMNYET |

| Offset | Name       | Bit Pos. |  |      |        |  |  |

|--------|------------|----------|--|------|--------|--|--|

| 0x1E   | Reserved   |          |  |      |        |  |  |

| 0x1F   | Reserved   |          |  |      |        |  |  |

| 0x20   | EPINTSMRY  | 7:0      |  | EPIN | T[7:0] |  |  |

| 0x21   | EPINISWIRT | 15:8     |  | EPIN | [15:8] |  |  |

| 0x22   | Reserved   |          |  |      |        |  |  |

| 0x23   | Reserved   |          |  |      |        |  |  |

#### Table 32-2. Device Endpoint Register n

| Offset | Name         | Bit Pos. |        |        |              |          |         |         |              |         |

|--------|--------------|----------|--------|--------|--------------|----------|---------|---------|--------------|---------|

| 0x1m0  | EPCFGn       | 7:0      |        |        | EPTYPE1[1:0] |          |         |         | EPTYPE0[1:0] | ]       |

| 0x1m1  | Reserved     |          |        |        |              |          |         |         |              |         |

| 0x1m2  | Reserved     |          |        |        |              |          |         |         |              |         |

| 0x1m3  | Reserved     |          |        |        |              |          |         |         |              |         |

| 0x1m4  | EPSTATUSCLRn | 7:0      | BK1RDY | BK0RDY | STALLRQ1     | STALLRQ0 |         | CURBK   | DTGLIN       | DTGLOUT |

| 0x1m5  | EPSTATUSSETn | 7:0      | BK1RDY | BK0RDY | STALLRQ1     | STALLRQ0 |         | CURBK   | DTGLIN       | DTGLOUT |

| 0x1m6  | EPSTATUSn    | 7:0      | BK1RDY | BK0RDY | STALLRQ1     | STALLRQ0 |         | CURBK   | DTGLIN       | DTGLOUT |

| 0x1m7  | EPINTFLAGn   | 7:0      |        | STALL1 | STALL0       | RXSTP    | TRFAIL1 | TRFAIL0 | TRCPT1       | TRCPT0  |

| 0x1m8  | EPINTENCLRn  | 7:0      |        | STALL1 | STALL0       | RXSTP    | TRFAIL1 | TRFAIL0 | TRCPT1       | TRCPT0  |

| 0x1m9  | EPINTENSETn  | 7:0      |        | STALL1 | STALL0       | RXSTP    | TRFAIL1 | TRFAIL0 | TRCPT1       | TRCPT0  |

| 0x1mA  | Reserved     |          |        |        |              |          |         |         |              |         |

| 0x1mB  | Reserved     |          |        |        |              |          |         |         |              |         |

## Table 32-3. Device Endpoint n Descriptor Bank 0

| Offset<br>0x n0 +<br>index | Name      | Bit Pos. |            |              |                        |        |               |            |                |        |  |

|----------------------------|-----------|----------|------------|--------------|------------------------|--------|---------------|------------|----------------|--------|--|

| 0x00                       |           | 7:0      |            |              |                        | ADE    | D[7:0]        |            |                |        |  |

| 0x01                       | ADDR      | 15:8     |            |              |                        | ADD    | [15:8]        |            |                |        |  |

| 0x02                       | ADDR      | 23:16    |            |              |                        | ADD    | 23:16]        |            |                |        |  |

| 0x03                       |           | 31:24    |            |              |                        | ADD    | 31:24]        |            |                |        |  |

| 0x04                       |           | 7:0      |            |              |                        | BYTE_C | OUNT[7:0]     |            |                |        |  |

| 0x05                       | DOVOITE   | 15:8     | MULTI_PACK | ET_SIZE[1:0] | BYTE_COUNT[13:8]       |        |               |            |                |        |  |

| 0x06                       | PCKSIZE   | 23:16    |            |              | MULTI_PACKET_SIZE[9:2] |        |               |            |                |        |  |

| 0x07                       |           | 31:24    | AUTO_ZLP   |              | SIZE[2:0]              |        |               | MULTI_PACK | ET_SIZE[13:10] | 0]     |  |

| 0x08                       | EVTREO    | 7:0      |            | VARIAE       | BLE[3:0]               |        |               | SUBF       | PID[3:0]       |        |  |

| 0x09                       | EXTREG    | 15:8     |            |              |                        |        | VARIABLE[10:4 | 4]         |                |        |  |

| 0x0A                       | STATUS_BK | 7:0      |            |              |                        |        |               |            | ERRORFLOW      | CRCERR |  |

| 0x0B                       | Reserved  | 7:0      |            |              |                        |        |               |            |                |        |  |

| 0x0C                       | Reserved  | 7:0      |            |              |                        |        |               |            |                |        |  |

| 0x0D                       | Reserved  | 7:0      |            |              |                        |        |               |            |                |        |  |

| 0x0E                       | Reserved  | 7:0      |            |              |                        |        |               |            |                |        |  |

| 0x0F                       | Reserved  | 7:0      |            |              |                        |        |               |            |                |        |  |

- Control B (CTRLB)

- Software Trigger (SWTRIG)

- Window Monitor Control (WINCTRL)

- Input Control (INPUTCTRL)

- Window Upper/Lower Threshold (WINUT/WINLT)

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

The following registers are synchronized when read:

- Software Trigger (SWTRIG)

- Input Control (INPUTCTRL)

Required read-synchronization is denoted by the "Read-Synchronized" property in the register description.

#### **Related Links**

Register Synchronization

## 33.7 Register Summary

| Offset | Name      | Bit   |          |        |             |          |         |             |                |          |

|--------|-----------|-------|----------|--------|-------------|----------|---------|-------------|----------------|----------|

|        |           | Pos.  |          |        |             |          |         |             |                |          |

| 0x00   | CTRLA     | 7:0   |          |        |             |          |         | RUNSTDBY    | ENABLE         | SWRST    |

| 0x01   | REFCTRL   | 7:0   | REFCOMP  |        |             |          |         | REFSI       | EL[3:0]        |          |

| 0x02   | AVGCTRL   | 7:0   |          |        | ADJRES[2:0] |          |         | SAMPLE      | NUM[3:0]       |          |

| 0x03   | SAMPCTRL  | 7:0   |          |        |             |          | SAMPL   | EN[5:0]     |                |          |

| 0x04   |           | 7:0   |          |        | RESS        | EL[1:0]  | CORREN  | FREERUN     | LEFTADJ        | DIFFMODE |

| 0x05   | CTRLB     | 15:8  |          |        |             |          |         | Р           | RESCALER[2:    | 0]       |

| 0x06   | Reserved  |       |          |        |             |          |         |             |                |          |

| 0x07   | Reserved  |       |          |        |             |          |         |             |                |          |

| 0x08   | WINCTRL   | 7:0   |          |        |             |          |         |             | WINMODE[2:0]   |          |

| 0x09   |           |       |          |        |             |          |         |             |                |          |

|        | Reserved  |       |          |        |             |          |         |             |                |          |

| 0x0B   |           |       |          |        |             |          |         |             |                |          |

| 0x0C   | SWTRIG    | 7:0   |          |        |             |          |         |             | START          | FLUSH    |

| 0x0D   |           |       |          |        |             |          |         |             |                |          |

|        | Reserved  |       |          |        |             |          |         |             |                |          |

| 0x0F   |           |       |          |        |             |          |         |             |                |          |

| 0x10   |           | 7:0   |          |        |             |          |         | MUXPOS[4:0] |                |          |

| 0x11   | INPUTCTRL | 15:8  |          |        |             |          |         | MUXNEG[4:0] |                |          |

| 0x12   | INFOICINE | 23:16 |          | INPUTO | FFSET[3:0]  |          |         | INPUTS      | CAN[3:0]       |          |

| 0x13   |           | 31:24 |          |        |             |          |         | GAIN        | <b>V</b> [3:0] |          |

| 0x14   | EVCTRL    | 7:0   |          |        | WINMONEO    | RESRDYEO |         |             | SYNCEI         | STARTEI  |

| 0x15   | Reserved  |       |          |        |             |          |         |             |                |          |

| 0x16   | INTENCLR  | 7:0   |          |        |             |          | SYNCRDY | WINMON      | OVERRUN        | RESRDY   |

| 0x17   | INTENSET  | 7:0   |          |        |             |          | SYNCRDY | WINMON      | OVERRUN        | RESRDY   |

| 0x18   | INTFLAG   | 7:0   |          |        |             |          | SYNCRDY | WINMON      | OVERRUN        | RESRDY   |

| 0x19   | STATUS    | 7:0   | SYNCBUSY |        |             |          |         |             |                |          |

| USB Device state | Conditions                                                                         | Тур. | Units |

|------------------|------------------------------------------------------------------------------------|------|-------|

| Wait connection  | GCLK_USB is off, using USB wakeup asynchronous interrupt. USB bus not connected.   | 0.10 | μA    |

| Wait connection  | GCLK_USB is on.<br>USB bus not connected.                                          | 0.19 | mA    |

| Suspend          | GCLK_USB is off, using USB wakeup asynchronous interrupt. USB bus in suspend mode. | 201  | μA    |

| Suspend          | GCLK_USB is on.<br>USB bus in suspend mode.                                        | 0.83 | mA    |

| IDLE             | Start Of Frame is running.<br>No packet transferred.                               | 1.17 | mA    |

| Active OUT       | Start Of Frame is running.<br>Bulk OUT on 100% bandwidth.                          | 2.17 | mA    |

| Active IN        | Start Of Frame is running.<br>Bulk IN on 100% bandwidth.                           | 10.3 | mA    |

| Table 37-13. | . Typical USB Host Full Speed mode Current Consumption |

|--------------|--------------------------------------------------------|

|--------------|--------------------------------------------------------|

# 37.8 I/O Pin Characteristics

## 37.8.1 Normal I/O Pins

#### Table 37-14. Normal I/O Pins Characteristics

| Symbol                          | Parameter                          | Conditions                                   | Min.                 | Тур.                | Max.                 | Units |

|---------------------------------|------------------------------------|----------------------------------------------|----------------------|---------------------|----------------------|-------|

| R <sub>PULL</sub>               | Pull-up - Pull-<br>down resistance | All pins except for PA24 and PA25            | 20                   | 40                  | 60                   | kΩ    |

| V <sub>IL</sub> Input low-level |                                    | V <sub>DD</sub> =1.62V-2.7V                  | -                    | -                   | 0.25*V <sub>DD</sub> | V     |

|                                 | voltage                            | V <sub>DD</sub> =2.7V-3.63V                  | -                    | -                   | 0.3*V <sub>DD</sub>  |       |

| VIH                             | Input high-level voltage           | V <sub>DD</sub> =1.62V-2.7V                  | 0.7*V <sub>DD</sub>  | -                   | -                    |       |

|                                 |                                    | V <sub>DD</sub> =2.7V-3.63V                  | 0.55*V <sub>DD</sub> | -                   | -                    |       |

| V <sub>OL</sub>                 | Output low-level voltage           | V <sub>DD</sub> >1.6V, I <sub>OL</sub> maxl  | -                    | 0.1*V <sub>DD</sub> | 0.2*V <sub>DD</sub>  |       |

| V <sub>OH</sub>                 | Output high-level voltage          | V <sub>DD</sub> >1.6V, I <sub>OH</sub> maxII | 0.8*V <sub>DD</sub>  | 0.9*V <sub>DD</sub> | -                    |       |

| Symbol                | Parameter           | Conditions                                                                                      | Min. | Тур. | Max. | Units |  |

|-----------------------|---------------------|-------------------------------------------------------------------------------------------------|------|------|------|-------|--|

| f <sub>IN</sub>       | Input frequency     |                                                                                                 | 32   | -    | 2000 | KHz   |  |

| f <sub>OUT</sub>      | Output frequency    |                                                                                                 | 48   | -    | 96   | MHz   |  |

| I <sub>FDPLL96M</sub> | Current consumption | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 48 MHz                                             | -    | 500  | 700  | μA    |  |

|                       |                     | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 96 MHz                                             | -    | 900  | 1200 |       |  |

| J <sub>p</sub>        | Period jitter       | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 48 MHz                                             | -    | 1.5  | 2.1  | %     |  |

|                       |                     | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 96 MHz                                             | -    | 4.0  | 10.0 |       |  |

|                       |                     | f <sub>IN</sub> = 2 MHz, f <sub>OUT</sub> = 48 MHz                                              | -    | 1.6  | 2.2  |       |  |

|                       |                     | f <sub>IN</sub> = 2 MHz, f <sub>OUT</sub> = 96 MHz                                              | -    | 4.6  | 10.2 |       |  |

| t <sub>LOCK</sub>     | Lock Time           | After start-up, time to get lock signal.<br>f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 96 MHz | -    | 1.2  | 2    | ms    |  |

|                       |                     | f <sub>IN</sub> = 2 MHz, f <sub>OUT</sub> = 96 MHz                                              | -    | 25   | 50   | μs    |  |

| Duty                  | Duty cycle          |                                                                                                 | 40   | 50   | 60   | %     |  |

| Table 37-57. FDPLL96M Characteristics <sup>(</sup> | <sup>I)</sup> (Device Variant B / Die Revision E) |

|----------------------------------------------------|---------------------------------------------------|

|----------------------------------------------------|---------------------------------------------------|

| Symbol                | Parameter           | Conditions                                                                                      | Min. | Тур. | Max. | Units |  |  |

|-----------------------|---------------------|-------------------------------------------------------------------------------------------------|------|------|------|-------|--|--|

| f <sub>IN</sub>       | Input frequency     |                                                                                                 | 32   | -    | 2000 | KHz   |  |  |

| f <sub>OUT</sub>      | Output frequency    |                                                                                                 | 48   | -    | 96   | MHz   |  |  |

| I <sub>FDPLL96M</sub> | Current consumption | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 48 MHz                                             | -    | 500  | -    | μA    |  |  |

|                       |                     | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 96 MHz                                             | -    | 900  | -    |       |  |  |

| J <sub>p</sub>        | Period jitter       | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 48 MHz                                             | -    | 2.2  | 3.0  | %     |  |  |

|                       |                     | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 96 MHz                                             | -    | 3.7  | 9.0  |       |  |  |

|                       |                     | f <sub>IN</sub> = 2 MHz, f <sub>OUT</sub> = 48 MHz                                              | -    | 2.2  | 3.0  |       |  |  |

|                       |                     | f <sub>IN</sub> = 2 MHz, f <sub>OUT</sub> = 96 MHz                                              | -    | 4.4  | 9.7  |       |  |  |

| t <sub>LOCK</sub>     | Lock Time           | After start-up, time to get lock signal.<br>f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 96 MHz | -    | 1.0  | 2    | ms    |  |  |

|                       |                     | f <sub>IN</sub> = 2 MHz, f <sub>OUT</sub> = 96 MHz                                              | -    | 22   | 50   | μs    |  |  |

| Duty                  | Duty cycle          |                                                                                                 | 40   | 50   | 60   | %     |  |  |

### Note:

1. All values have been characterized with FILTSEL[1/0] as default value.

#### 44.8.2 External 32 kHz Crystal Oscillator (XOSC32K) Characteristics

#### 44.8.2.1 Digital Clock Characteristics

The following table describes the characteristics for the oscillator when a digital clock is applied on XIN32 pin.

### Table 44-35. Digital Clock Characteristics

| Symbol               | Parameter              | Conditions | Min. | Тур.   | Max. | Units |

|----------------------|------------------------|------------|------|--------|------|-------|

| f <sub>CPXIN32</sub> | XIN32 clock frequency  |            | -    | 32.768 | -    | kHz   |

|                      | XIN32 clock duty cycle |            | -    | 50     | -    | %     |

#### 44.8.2.2 Crystal Oscillator Characteristics

Figure 37-6 and the equation in also applies to the 32 kHz oscillator connection. The user must choose a crystal oscillator where the crystal load capacitance  $C_L$  is within the range given in the table. The exact value of  $C_L$  can be found in the crystal datasheet.

#### Table 44-36. 32kHz Crystal Oscillator Characteristics (Device Variant A)

| Symbol               | Parameter                                                                  | Conditions                                        | Min. | Тур.  | Max. | Units  |

|----------------------|----------------------------------------------------------------------------|---------------------------------------------------|------|-------|------|--------|

| f <sub>OUT</sub>     | Crystal oscillator frequency                                               |                                                   | -    | 32768 | -    | Hz     |

| t <sub>startup</sub> | Startup time                                                               | $ ESR_{XTAL} = 39.9  k\Omega,  C_{L} = 12.5  pF $ | -    | 28K   | 31K  | cycles |

| CL                   | Crystal load capacitance                                                   |                                                   | -    | -     | 12.5 | pF     |

| C <sub>SHUNT</sub>   | Crystal shunt capacitance                                                  |                                                   | -    | 0.1   | -    |        |

| C <sub>XIN32</sub>   | Parasitic capacitor load                                                   | TQFP64/48/32 packages                             | -    | 3.1   | -    |        |

| C <sub>XOUT32</sub>  | Parasitic capacitor load                                                   |                                                   | -    | 3.3   | -    |        |

| I <sub>XOSC32K</sub> | Current consumption                                                        |                                                   | -    | 1.22  | 2.44 | μA     |

| ESR                  | Crystal equivalent series resistance<br>f=32.768kHz<br>, Safety Factor = 3 | C <sub>L</sub> =12.5pF                            | -    | -     | 141  | kΩ     |

#### Table 44-37. 32kHz Crystal Oscillator Characteristics (Device Variant B)

| Symbol               | Parameter                    | Conditions                                      | Min. | Тур.  | Max. | Units  |

|----------------------|------------------------------|-------------------------------------------------|------|-------|------|--------|

| f <sub>OUT</sub>     | Crystal oscillator frequency |                                                 | -    | 32768 | -    | Hz     |

| t <sub>startup</sub> | Startup time                 | $ ESR_{XTAL} = 39.9 k\Omega,  C_{L} = 12.5 pF $ | -    | 28K   | 30K  | cycles |

| CL                   | Crystal load capacitance     |                                                 | -    | -     | 12.5 | pF     |

| C <sub>SHUNT</sub>   | Crystal shunt capacitance    |                                                 | -    | 0.1   | -    |        |

| C <sub>XIN32</sub>   | Parasitic capacitor load     | TQFP64/48/32 packages                           | -    | 3.2   | -    |        |

| C <sub>XOUT32</sub>  | Parasitic capacitor load     |                                                 | -    | 3.7   | -    |        |

| Symbol               | Parameter           | Conditions                                                                                      | Min. | Тур. | Max. | Units |

|----------------------|---------------------|-------------------------------------------------------------------------------------------------|------|------|------|-------|

| fout                 | Output frequency    | Calibrated against a 8MHz reference at 25°C, over [-40, +85]°C, over [1.62, 3.63]V              | 7.54 | 8    | 8.19 | MHz   |

|                      |                     | Calibrated against a 8MHz reference at 25°C, at V_{DD}=3.3V                                     | 7.94 | 8    | 8.06 |       |

|                      |                     | Calibrated against a 8MHz reference at 25°C, over [1.62, 3.63]V                                 | 7.92 | 8    | 8.06 |       |

| I <sub>OSC8M</sub>   | Current consumption | IIDLEIDLE2 on OSC32K versus IDLE2 on<br>calibrated OSC8M enabled at 8MHz<br>(FRANGE=1, PRESC=0) |      | 64   | 96   | μA    |

| t <sub>startup</sub> | Startup time        |                                                                                                 | -    | 2.4  | 3.3  | μs    |

| Duty                 | Duty cycle          |                                                                                                 | -    | 50   | -    | %     |

| Table 44-47. Internal 8MHz RC Oscillato | r Characteristics (Device Variant B) |

|-----------------------------------------|--------------------------------------|

|-----------------------------------------|--------------------------------------|

## 44.8.7 Fractional Digital Phase Locked Loop (FDPLL96M) Characteristics Table 44-48. FDPLL96M Characteristics<sup>(1)</sup> (Device Variant A)

| Symbol                | Parameter           | Conditions                                                                                      | Min. | Тур. | Max. | Units |

|-----------------------|---------------------|-------------------------------------------------------------------------------------------------|------|------|------|-------|

| f <sub>IN</sub>       | Input frequency     |                                                                                                 | 32   | -    | 2000 | KHz   |

| f <sub>OUT</sub>      | Output frequency    |                                                                                                 | 48   | -    | 96   | MHz   |

| I <sub>FDPLL96M</sub> | Current consumption | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 48 MHz                                             | -    | 500  | 700  | μA    |

|                       |                     | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 96 MHz                                             | -    | 900  | 1200 |       |

| Jp                    | Period jitter       | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 48 MHz                                             | -    | 1.5  | 2.0  | %     |

|                       |                     | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 96 MHz                                             | -    | 3.0  | 10.0 |       |

|                       |                     | f <sub>IN</sub> = 2 MHz, f <sub>OUT</sub> = 48 MHz                                              | -    | 1.3  | 2.0  |       |

|                       |                     | f <sub>IN</sub> = 2 MHz, f <sub>OUT</sub> = 96 MHz                                              | -    | 3.0  | 7.0  |       |

| t <sub>LOCK</sub>     | Lock Time           | After start-up, time to get lock signal.<br>f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 96 MHz | -    | 1.3  | 2    | ms    |

|                       |                     | f <sub>IN</sub> = 2 MHz, f <sub>OUT</sub> = 96 MHz                                              | -    | 25   | 50   | μs    |

| Duty                  | Duty cycle          |                                                                                                 | 40   | 50   | 60   | %     |

# Table 44-49. FDPLL96M Characteristics<sup>(1)</sup> (Device Variant B, Die Revision E)

| Symbol                | Parameter           | Conditions                                          | Min. | Тур. | Max. | Units |

|-----------------------|---------------------|-----------------------------------------------------|------|------|------|-------|

| f <sub>IN</sub>       | Input frequency     |                                                     | 32   | -    | 2000 | KHz   |

| f <sub>OUT</sub>      | Output frequency    |                                                     | 48   | -    | 96   | MHz   |

| I <sub>FDPLL96M</sub> | Current consumption | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 48 MHz | -    | 500  | 740  | μA    |

|                       |                     | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 96 MHz | -    | 900  | 1262 |       |