# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 26                                                                         |

| Program Memory Size        | 256KB (256K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                               |

| Data Converters            | A/D 10x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 32-VQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd21e18a-mft |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 32-bit ARM-Based Microcontrollers

| Ordering Code    | FLASH (bytes) | SRAM (bytes) | Package | Carrier Type |

|------------------|---------------|--------------|---------|--------------|

| ATSAMD21G18A-AU  | 256K          | 32K          | TQFP48  | Tray         |

| ATSAMD21G18A-AUT | _             |              |         | Tape & Reel  |

| ATSAMD21G18A-AF  |               |              |         | Tray         |

| ATSAMD21G18A-AFT | _             |              |         | Tape & Reel  |

| ATSAMD21G18A-MU  |               |              | QFN48   | Tray         |

| ATSAMD21G18A-MUT | _             |              |         | Tape & Reel  |

| ATSAMD21G18A-MF  |               |              |         | Tray         |

| ATSAMD21G18A-MFT | _             |              |         | Tape & Reel  |

| ATSAMD21G18A-UUT |               |              | WLCSP45 | Tape & Reel  |

# Table 3-5. Device Variant B

| Ordering Code    | FLASH (bytes) | SRAM (bytes) | Package | Carrier Type |

|------------------|---------------|--------------|---------|--------------|

| ATSAMD21G15B-AU  | 32K           | 4K           | TQFP48  | Tray         |

| ATSAMD21G15B-AUT |               |              |         | Tape & Reel  |

| ATSAMD21G15B-AF  |               |              |         | Tray         |

| ATSAMD21G15B-AFT |               |              |         | Tape & Reel  |

| ATSAMD21G15B-MU  |               |              | QFN48   | Tray         |

| ATSAMD21G15B-MUT | -             |              |         | Tape & Reel  |

| ATSAMD21G15B-MF  | -             |              |         | Tray         |

| ATSAMD21G15B-MFT | -             |              |         | Tape & Reel  |

| ATSAMD21G16B-AU  | 64K           | 8K           | TQFP48  | Tray         |

| ATSAMD21G16B-AUT |               |              |         | Tape & Reel  |

| ATSAMD21G16B-AF  |               |              |         | Tray         |

| ATSAMD21G16B-AFT |               |              |         | Tape & Reel  |

| ATSAMD21G16B-MU  |               |              | QFN48   | Tray         |

| ATSAMD21G16B-MUT |               |              |         | Tape & Reel  |

| ATSAMD21G16B-MF  |               |              |         | Tray         |

| ATSAMD21G16B-MFT |               |              |         | Tape & Reel  |

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

#### Bit 4 – WDT:

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

# Bit 3 – GCLK

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

# Bit 2 – SYSCTRL

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Val | ue | Description                   |

|-----|----|-------------------------------|

| 0   |    | Write-protection is disabled. |

| 1   |    | Write-protection is enabled.  |

#### Bit 1 – PM

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

Write Protect Set

| Name:       | WPSET    |  |  |  |  |

|-------------|----------|--|--|--|--|

| Offset:     | 0x04     |  |  |  |  |

| Reset:      | 0x000000 |  |  |  |  |

| Property: – |          |  |  |  |  |

| Bit    | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

|--------|----|----|----|----|----|----|----|----|

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

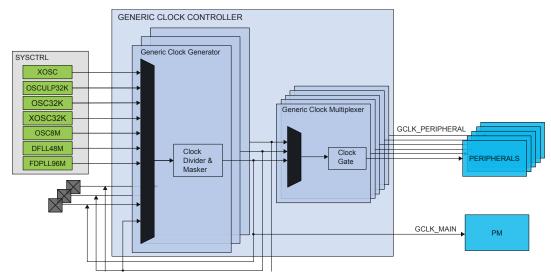

# 15. GCLK - Generic Clock Controller

# 15.1 Overview

Depending on the application, peripherals may require specific clock frequencies to operate correctly. The Generic Clock controller GCLK provides nine Generic Clock Generators that can provide a wide range of clock frequencies.

Generators can be set to use different external and internal oscillators as source. The clock of each Generator can be divided. The outputs from the Generators are used as sources for the Generic Clock Multiplexers, which provide the Generic Clock (GCLK\_PERIPHERAL) to the peripheral modules, as shown in Generic Clock Controller Block Diagram. The number of Peripheral Clocks depends on how many peripherals the device has.

Note: The Generator 0 is always the direct source of the GCLK\_MAIN signal.

# 15.2 Features

- Provides Generic Clocks

- Wide frequency range

- Clock source for the generator can be changed on the fly

# 15.3 Block Diagram

The generation of Peripheral Clock signals (GCLK\_PERIPHERAL) and the Main Clock (GCLK\_MAIN) can be seen in the figure below.

#### Figure 15-1. Device Clocking Diagram

The GCLK block diagram is shown in the next figure.

#### 15.6.5.2 Run in Standby Mode

In standby mode, the GCLK can continuously output the generator output to GCLK\_IO.

When set, the GCLK can continuously output the generator output to GCLK\_IO.

Refer to Generic Clock Output on I/O Pins for details.

#### 15.6.6 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

When executing an operation that requires synchronization, the Synchronization Busy bit in the Status register (STATUS.SYNCBUSY) will be set immediately, and cleared when synchronization is complete.

If an operation that requires synchronization is executed while STATUS.SYNCBUSY=1, the bus will be stalled. All operations will complete successfully, but the CPU will be stalled and interrupts will be pending as long as the bus is stalled.

The following registers are synchronized when written:

- Generic Clock Generator Control register (GENCTRL)

- Generic Clock Generator Division register (GENDIV)

- Control register (CTRL)

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

# Related Links

Register Synchronization

# 15.7 Register Summary

#### Table 15-2. Register Summary

| Offset | Name    | Bit   |          |       |          |          |        |          |       |       |

|--------|---------|-------|----------|-------|----------|----------|--------|----------|-------|-------|

|        |         | Pos.  |          |       |          |          |        |          |       |       |

| 0x0    | CTRL    | 7:0   |          |       |          |          |        |          |       | SWRST |

| 0x1    | STATUS  | 7:0   | SYNCBUSY |       |          |          |        |          |       |       |

| 0x2    | CLKCTRL | 7:0   |          |       |          |          | ID[    | 5:0]     |       |       |

| 0x3    | GLKCTRL | 15:8  | WRTLOCK  | CLKEN |          | GEN[3:0] |        |          |       |       |

| 0x4    | GENCTRL | 7:0   |          |       |          |          |        | ID[      | [3:0] |       |

| 0x5    |         | 15:8  |          |       |          |          |        | SRC[4:0] |       |       |

| 0x6    | GENCIRE | 23:16 |          |       | RUNSTDBY | DIVSEL   | OE     | OOV      | IDC   | GENEN |

| 0x7    |         | 31:24 |          |       |          |          |        |          |       |       |

| 0x8    |         | 7:0   |          |       |          | ID[3:0]  |        |          |       |       |

| 0x9    | GENDIV  | 15:8  |          |       |          | DIV[7:0] |        |          |       |       |

| 0xA    |         | 23:16 |          |       |          | DIV      | [15:8] |          |       |       |

| 0xB    |         | 31:24 |          |       |          |          |        |          |       |       |

#### 16.8.5 APBB Clock Select

Name:APBBSELOffset:0x0AReset:0x00Property:Write-Protected

| Bit    | 7 | 6 | 5 | 4 | 3 | 2   | 1            | 0   |

|--------|---|---|---|---|---|-----|--------------|-----|

|        |   |   |   |   |   |     | APBBDIV[2:0] |     |

| Access |   |   |   |   |   | R/W | R/W          | R/W |

| Reset  |   |   |   |   |   | 0   | 0            | 0   |

# Bits 2:0 – APBBDIV[2:0]: APBB Prescaler Selection

These bits define the division ratio of the APBB clock prescaler (2<sup>n</sup>).

| APBBDIV[2:0] | Name   | Description   |

|--------------|--------|---------------|

| 0x0          | DIV1   | Divide by 1   |

| 0x1          | DIV2   | Divide by 2   |

| 0x2          | DIV4   | Divide by 4   |

| 0x3          | DIV8   | Divide by 8   |

| 0x4          | DIV16  | Divide by 16  |

| 0x5          | DIV32  | Divide by 32  |

| 0x6          | DIV64  | Divide by 64  |

| 0x7          | DIV128 | Divide by 128 |

# 16.8.6 APBC Clock Select

Name:APBCSELOffset:0x0BReset:0x00Property:Write-Protected

| Bit    | 7 | 6 | 5 | 4 | 3 | 2   | 1            | 0   |

|--------|---|---|---|---|---|-----|--------------|-----|

|        |   |   |   |   |   |     | APBCDIV[2:0] |     |

| Access |   |   |   |   |   | R/W | R/W          | R/W |

| Reset  |   |   |   |   |   | 0   | 0            | 0   |

# Bits 2:0 – APBCDIV[2:0]: APBC Prescaler Selection

These bits define the division ratio of the APBC clock prescaler (2<sup>n</sup>).

| APBCDIV[2:0] | Name | Description |

|--------------|------|-------------|

| 0x0          | DIV1 | Divide by 1 |

| 0x1          | DIV2 | Divide by 2 |

XOSC32K.ENABLE bit while writing to other bits may result in unpredictable behavior. The oscillator remains enabled in all sleep modes if it has been enabled beforehand. The start-up time of the 32kHz External Crystal Oscillator is selected by writing to the Oscillator Start-Up Time bit group (XOSC32K.STARTUP) in the in the 32kHz External Crystal Oscillator Control register. The SYSCTRL masks the oscillator output during the start-up time to ensure that no unstable clock propagates to the digital logic. The 32kHz External Crystal Oscillator Ready bit (PCLKSR.XOSC32KRDY) in the Power and Clock Status register is set when the user-selected startup time is over. An interrupt is generated on a zero-to-one transition of PCLKSR.XOSC32KRDY if the 32kHz External Crystal Oscillator Ready bit (INTENSET.XOSC32KRDY) in the Interrupt Enable Set Register is set.

As a crystal oscillator usually requires a very long start-up time (up to one second), the 32kHz External Crystal Oscillator will keep running across resets, except for power-on reset (POR).

XOSC32K can provide two clock outputs when connected to a crystal. The XOSC32K has a 32.768kHz output enabled by writing a one to the 32kHz External Crystal Oscillator 32kHz Output Enable bit (XOSC32K.EN32K) in the 32kHz External Crystal Oscillator Control register. XOSC32K.EN32K is only usable when XIN32 is connected to a crystal, and not when an external digital clock is applied on XIN32.

**Note:** Do not enter standby mode when an oscillator is in start-up: Wait for the OSCxRDY bit in SYSCTRL.PCLKSR register to be set before going into standby mode.

#### **Related Links**

GCLK - Generic Clock Controller

# 17.6.4 32kHz Internal Oscillator (OSC32K) Operation

The OSC32K provides a tunable, low-speed and low-power clock source.

The OSC32K can be used as a source for the generic clock generators, as described in the *GCLK* – *Generic Clock Controller*.

The OSC32K is disabled by default. The OSC32K is enabled by writing a one to the 32kHz Internal Oscillator Enable bit (OSC32K.ENABLE) in the 32kHz Internal Oscillator Control register. It is disabled by writing a zero to OSC32K.ENABLE. The OSC32K has a 32.768kHz output enabled by writing a one to the 32kHz Internal Oscillator 32kHz Output Enable bit (OSC32K.EN32K).

The frequency of the OSC32K oscillator is controlled by the value in the 32kHz Internal Oscillator Calibration bits (OSC32K.CALIB) in the 32kHz Internal Oscillator Control register. The OSC32K.CALIB value must be written by the user. Flash Factory Calibration values are stored in the NVM Software Calibration Area (refer to *NVM Software Calibration Area Mapping*). When writing to the Calibration bits, the user must wait for the PCLKSR.OSC32KRDY bit to go high before the value is committed to the oscillator.

# **Related Links**

GCLK - Generic Clock Controller NVM Software Calibration Area Mapping

# 17.6.5 32kHz Ultra Low Power Internal Oscillator (OSCULP32K) Operation

The OSCULP32K provides a tunable, low-speed and ultra-low-power clock source. The OSCULP32K is factory-calibrated under typical voltage and temperature conditions. The OSCULP32K should be preferred to the OSC32K whenever the power requirements are prevalent over frequency stability and accuracy.

The OSCULP32K can be used as a source for the generic clock generators, as described in the *GCLK* – *Generic Clock Controller*.

# 22.4 Signal Description

Not applicable.

# 22.5 Product Dependencies

In order to use this module, other parts of the system must be configured correctly, as described below.

#### 22.5.1 Power Management

The NVMCTRL will continue to operate in any sleep mode where the selected source clock is running. The NVMCTRL interrupts can be used to wake up the device from sleep modes.

The Power Manager will automatically put the NVM block into a low-power state when entering sleep mode. This is based on the Control B register (CTRLB) SLEEPPRM bit setting. Refer to the CTRLB.SLEEPPRM register description for more details.

#### **Related Links**

PM – Power Manager

#### 22.5.2 Clocks

Two synchronous clocks are used by the NVMCTRL. One is provided by the AHB bus (CLK\_NVMCTRL\_AHB) and the other is provided by the APB bus (CLK\_NVMCTRL\_APB). For higher system frequencies, a programmable number of wait states can be used to optimize performance. When changing the AHB bus frequency, the user must ensure that the NVM Controller is configured with the proper number of wait states. Refer to the Electrical Characteristics for the exact number of wait states to be used for a particular frequency range.

# **Related Links**

**Electrical Characteristics**

#### 22.5.3 Interrupts

The NVM Controller interrupt request line is connected to the interrupt controller. Using the NVMCTRL interrupt requires the interrupt controller to be programmed first.

# 22.5.4 Debug Operation

When an external debugger forces the CPU into debug mode, the peripheral continues normal operation.

Access to the NVM block can be protected by the security bit. In this case, the NVM block will not be accessible. See the section on the NVMCTRL Security Bit for details.

# 22.5.5 Register Access Protection

All registers with write-access are optionally write-protected by the Peripheral Access Controller (PAC), except the following registers:

- Interrupt Flag Status and Clear register (INTFLAG)

- Status register (STATUS)

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

#### **Related Links**

PAC - Peripheral Access Controller

© 2017 Microchip Technology Inc.

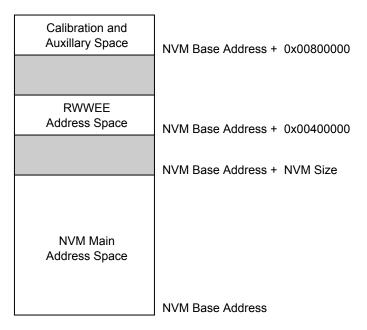

#### Figure 22-3. NVM Memory Organization

The lower rows in the NVM main address space can be allocated as a boot loader section by using the BOOTPROT fuses, and the upper rows can be allocated to EEPROM, as shown in the figure below.

The boot loader section is protected by the lock bit(s) corresponding to this address space and by the BOOTPROT[2:0] fuse. The EEPROM rows can be written regardless of the region lock status.

The number of rows protected by BOOTPROT is given in Boot Loader Size, the number of rows allocated to the EEPROM are given in EEPROM Size.

#### **Related Links**

PORT: IO Pin Controller

#### 26.5.2 Power Management

This peripheral can continue to operate in any sleep mode where its source clock is running. The interrupts can wake up the device from sleep modes.

#### **Related Links**

PM - Power Manager

#### 26.5.3 Clocks

The SERCOM bus clock (CLK\_SERCOMx\_APB) can be enabled and disabled in the Power Manager. Refer to *Perhipharal Clock Masking* for details and default status of this clock.

A generic clock (GCLK\_SERCOMx\_CORE) is required to clock the SERCOMx\_CORE. This clock must be configured and enabled in the Generic Clock Controller before using the SERCOMx\_CORE. Refer to *GCLK - Generic Clock Controller* for details.

This generic clock is asynchronous to the bus clock (CLK\_SERCOMx\_APB). Therefore, writing to certain registers will require synchronization to the clock domains. Refer to *Synchronization* for further details.

#### **Related Links**

Synchronization GCLK - Generic Clock Controller Peripheral Clock Masking

#### 26.5.4 DMA

The DMA request lines are connected to the DMA Controller (DMAC). In order to use DMA requests with this peripheral the DMAC must be configured first. Refer to *DMAC – Direct Memory Access Controller* for details.

# **Related Links**

DMAC – Direct Memory Access Controller

# 26.5.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. In order to use interrupt requests of this peripheral, the Interrupt Controller (NVIC) must be configured first. Refer to *Nested Vector Interrupt Controller* for details.

#### **Related Links**

Nested Vector Interrupt Controller

# 26.5.6 Events

Not applicable.

# 26.5.7 Debug Operation

When the CPU is halted in debug mode, this peripheral will continue normal operation. If the peripheral is configured to require periodical service by the CPU through interrupts or similar, improper operation or data loss may result during debugging. This peripheral can be forced to halt operation during debugging - refer to the Debug Control (DBGCTRL) register for details.

# 26.5.8 Register Access Protection

Registers with write-access can be write-protected optionally by the peripheral access controller (PAC).

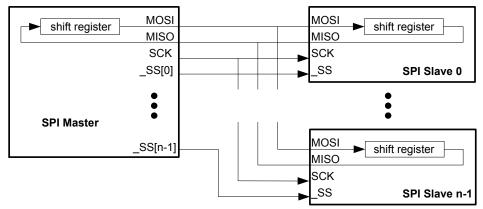

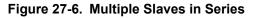

Another configuration is multiple slaves in series, as in Multiple Slaves in Series. In this configuration, all n attached slaves are connected in series. A common  $\overline{SS}$  line is provided to all slaves, enabling them simultaneously. The master must shift n characters for a complete transaction. Depending on the Master Slave Select Enable bit (CTRLB.MSSEN), the  $\overline{SS}$  line can be controlled either by hardware or user software and normal GPIO.

# 27.6.3.4 Loop-Back Mode

For loop-back mode, configure the Data In Pinout (CTRLA.DIPO) and Data Out Pinout (CTRLA.DOPO) to use the same data pins for transmit and receive. The loop-back is through the pad, so the signal is also available externally.

#### 27.6.3.5 Hardware Controlled SS

In master mode, a single  $\overline{SS}$  chip select can be controlled by hardware by writing the Master Slave Select Enable (CTRLB.MSSEN) bit to '1'. In this mode, the  $\overline{SS}$  pin is driven low for a minimum of one baud cycle before transmission begins, and stays low for a minimum of one baud cycle after transmission completes. If back-to-back frames are transmitted, the  $\overline{SS}$  pin will always be driven high for a minimum of one baud cycle between frames.

In Hardware Controlled SS, the time T is between one and two baud cycles depending on the SPI transfer mode.

register (INTFLAG.DRDY), indicating data are needed for transmit. If a NACK is sent, the I<sup>2</sup>C slave will wait for a new start condition and address match.

Typically, software will immediately acknowledge the address packet by sending an ACK/NACK bit. The I<sup>2</sup>C slave Command bit field in the Control B register (CTRLB.CMD) can be written to '0x3' for both read and write operations as the command execution is dependent on the STATUS.DIR bit. Writing '1' to INTFLAG.AMATCH will also cause an ACK/NACK to be sent corresponding to the CTRLB.ACKACT bit.

#### Case 2: Address packet accepted – Write flag set

The STATUS.DIR bit is cleared, indicating an I<sup>2</sup>C master write operation. The SCL line is forced low, stretching the bus clock. If an ACK is sent, the I<sup>2</sup>C slave will wait for data to be received. Data, repeated start or stop can be received.

If a NACK is sent, the  $I^2C$  slave will wait for a new start condition and address match. Typically, software will immediately acknowledge the address packet by sending an ACK/NACK. The  $I^2C$  slave command CTRLB.CMD = 3 can be used for both read and write operation as the command execution is dependent on STATUS.DIR.

Writing '1' to INTFLAG.AMATCH will also cause an ACK/NACK to be sent corresponding to the CTRLB.ACKACT bit.

#### Receiving Address Packets (SCLSM=1)

When SCLSM=1, the I<sup>2</sup>C slave will stretch the SCL line only after an ACK, see Slave Behavioral Diagram (SCLSM=1). When the I<sup>2</sup>C slave is properly configured, it will wait for a start condition to be detected.

When a start condition is detected, the successive address packet will be received and checked by the address match logic.

If the received address is not a match, the packet will be rejected and the I<sup>2</sup>C slave will wait for a new start condition.

If the address matches, the acknowledge action as configured by the Acknowledge Action bit Control B register (CTRLB.ACKACT) will be sent and the Address Match bit in the Interrupt Flag register (INTFLAG.AMATCH) is set. SCL will be stretched until the I<sup>2</sup>C slave clears INTFLAG.AMATCH. As the I<sup>2</sup>C slave holds the clock by forcing SCL low, the software is given unlimited time to respond to the address.

The direction of a transaction is determined by reading the Read/Write Direction bit in the Status register (STATUS.DIR). This bit will be updated only when a valid address packet is received.

If the Transmit Collision bit in the Status register (STATUS.COLL) is set, the last packet addressed to the I<sup>2</sup>C slave had a packet collision. A collision causes the SDA and SCL lines to be released without any notification to software. The next AMATCH interrupt is, therefore, the first indication of the previous packet's collision. Collisions are intended to follow the SMBus Address Resolution Protocol (*ARP*).

After the address packet has been received from the I<sup>2</sup>C master, INTFLAG.AMATCH be set to '1' to clear it.

#### **Receiving and Transmitting Data Packets**

After the I<sup>2</sup>C slave has received an address packet, it will respond according to the direction either by waiting for the data packet to be received or by starting to send a data packet by writing to DATA.DATA. When a data packet is received or sent, INTFLAG.DRDY will be set. After receiving data, the I<sup>2</sup>C slave will send an acknowledge according to CTRLB.ACKACT.

#### Case 1: Data received

INTFLAG.DRDY is set, and SCL is held low, pending for SW interaction.

#### 29.9.4 Interrupt Enable Set

Name:INTENSETOffset:0x10Reset:0x0000Property:PAC Write-Protection

| Bit           | 15 | 14 | 13         | 12         | 11 | 10 | 9                  | 8           |

|---------------|----|----|------------|------------|----|----|--------------------|-------------|

|               |    |    | TXUR1      | TXUR0      |    |    | TXRDY1             | TXRDY0      |

| Access        |    |    | R/W        | R/W        |    |    | R/W                | R/W         |

| Reset         |    |    | 0          | 0          |    |    | 0                  | 0           |

|               |    |    |            |            |    |    |                    |             |

|               |    |    |            |            |    |    |                    |             |

| Bit           | 7  | 6  | 5          | 4          | 3  | 2  | 1                  | 0           |

| Bit           | 7  | 6  | 5<br>RXOR1 | 4<br>RXOR0 | 3  | 2  | 1<br>RXRDY1        | 0<br>RXRDY0 |

| Bit<br>Access | 7  | 6  |            |            | 3  | 2  | 1<br>RXRDY1<br>R/W |             |

#### Bits 13,12 – TXURx : Transmit Underrun x Interrupt Enable [x=1..0]

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Transmit Underrun Interrupt Enable bit, which enables the Transmit Underrun interrupt.

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | The Transmit Underrun interrupt is disabled. |

| 1     | The Transmit Underrun interrupt is enabled.  |

#### Bits 9,8 – TXRDYx : Transmit Ready x Interrupt Enable [x=1..0]

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Transmit Ready Interrupt Enable bit, which enables the Transmit Ready interrupt.

| Value | Description                               |

|-------|-------------------------------------------|

| 0     | The Transmit Ready interrupt is disabled. |

| 1     | The Transmit Ready interrupt is enabled.  |

#### Bits 4,5 – RXORx : Receive Overrun x Interrupt Enable [x=1..0]

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Receive Overrun Interrupt Enable bit, which enables the Receive Overrun interrupt.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The Receive Overrun interrupt is disabled. |

| 1     | The Receive Overrun interrupt is enabled.  |

#### Bits 1,0 – RXRDYx : Receive Ready x Interrupt Enable [x=1..0]

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Receive Ready Interrupt Enable bit, which enables the Receive Ready interrupt.

#### Bit 1 – ENABLE: Enable

Due to synchronization, there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRLA.ENABLE will read back immediately, and the ENABLE Synchronization Busy bit in the SYNCBUSY register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE will be cleared when the operation is complete.

This bit is not enable protected.

| Value | Description                 |

|-------|-----------------------------|

| 0     | The peripheral is disabled. |

| 1     | The peripheral is enabled.  |

# Bit 0 – SWRST: Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit resets all registers in the TC, except DBGCTRL, to their initial state, and the TC will be disabled.

Writing a '1' to CTRLA.SWRST will always take precedence; all other writes in the same write-operation will be discarded.

Due to synchronization there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the reset is complete.

This bit is not enable protected.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

# 30.8.2 Read Request

| Name:<br>Offset:<br>Reset: |      | READREQ<br>0x02<br>0x0000 |       |    |     |     |           |     |     |

|----------------------------|------|---------------------------|-------|----|-----|-----|-----------|-----|-----|

| Bit                        | 15   |                           | 14    | 13 | 12  | 11  | 10        | 9   | 8   |

|                            | RREQ |                           | RCONT |    |     |     |           |     |     |

| Access                     | W    |                           | R/W   |    |     |     |           |     |     |

| Reset                      | 0    |                           | 0     |    |     |     |           |     |     |

|                            |      |                           |       |    |     |     |           |     |     |

| Bit                        | 7    |                           | 6     | 5  | 4   | 3   | 2         | 1   | 0   |

|                            |      |                           |       |    |     |     | ADDR[4:0] |     |     |

| Access                     |      |                           |       |    | R/W | R/W | R/W       | R/W | R/W |

| Reset                      |      |                           |       |    | 0   | 0   | 0         | 0   | 0   |

# Bit 15 – RREQ: Read Request

Writing a zero to this bit has no effect.

This bit will always read as zero.

Writing a one to this bit requests synchronization of the register pointed to by the Address bit group (READREQ. ADDR) and sets the Synchronization Busy bit in the Status register (STATUS.SYNCBUSY).

| Value | Description                                                                       |

|-------|-----------------------------------------------------------------------------------|

| 0     | The TC will wrap around and continue counting on an overflow/underflow condition. |

| 1     | The TC will wrap around and stop on the next underflow/overflow condition.        |

#### Bit 0 – DIR: Counter Direction

This bit is used to change the direction of the counter.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the bit and make the counter count up.

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | The timer/counter is counting up (incrementing).   |

| 1     | The timer/counter is counting down (decrementing). |

#### 30.8.5 Control C

Name:CTRLCOffset:0x06Reset:0x00Property:PAC Write-Protection, Read-synchronized, Write-Synchronized

| Bit    | 7 | 6 | 5      | 4      | 3 | 2 | 1      | 0      |

|--------|---|---|--------|--------|---|---|--------|--------|

|        |   |   | CPTEN1 | CPTEN0 |   |   | INVEN1 | INVEN0 |

| Access |   |   | R/W    | R/W    |   |   | R/W    | R/W    |

| Reset  |   |   | 0      | 0      |   |   | 0      | 0      |

#### Bits 5,4 – CPTENx: Capture Channel x Enable

These bits are used to select the capture or compare operation on channel x.

Writing a '1' to CPTENx enables capture on channel x.

Writing a '0' to CPTENx disables capture on channel x.

#### Bits 1,0 – INVENx: Waveform Output x Inversion Enable

These bits are used to select inversion on the output of channel x.

Writing a '1' to INVENx inverts output from WO[x].

Writing a '0' to INVENx disables inversion of output from WO[x].

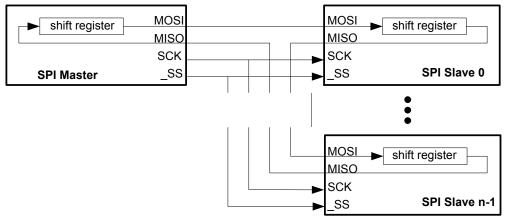

#### 30.8.6 Debug Control

Name:DBGCTRLOffset:0x08Reset:0x00Property:PAC Write-Protection

# 32-bit ARM-Based Microcontrollers

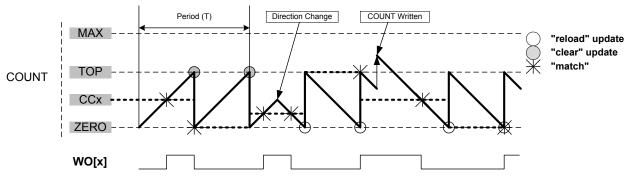

| Name       | Operation            | ТОР | Update                       | Output Wav                    | eform     | OVFIF/Ev | ent  |

|------------|----------------------|-----|------------------------------|-------------------------------|-----------|----------|------|

|            |                      |     |                              | On Match                      | On Update | Up       | Down |

| NPWM       | Single-<br>slope PWM | PER | TOP/<br>ZERO                 | See section<br>Polarity' belo | •         | TOP      | ZERO |

| DSCRITICAL | Dual-slope<br>PWM    | PER | ZERO                         | -                             |           | -        | ZERO |

| DSBOTTOM   | Dual-slope<br>PWM    | PER | ZERO                         |                               |           | -        | ZERO |

| DSBOTH     | Dual-slope<br>PWM    | PER | TOP <sup>(1)</sup> &<br>ZERO |                               |           | TOP      | ZERO |

| DSTOP      | Dual-slope<br>PWM    | PER | ZERO                         |                               |           | TOP      | -    |

1. The UPDATE condition on TOP only will occur when circular buffer is enabled for the channel.

# **Related Links**

Circular Buffer PORT: IO Pin Controller

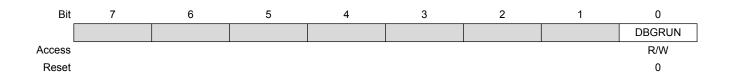

# Normal Frequency (NFRQ)

For Normal Frequency generation, the period time (T) is controlled by the period register (PER). The waveform generation output (WO[x]) is toggled on each compare match between COUNT and CCx, and the corresponding Match or Capture Channel x Interrupt Flag (EVCTRL.MCEOx) will be set.

# Figure 31-4. Normal Frequency Operation

# Match Frequency (MFRQ)

For Match Frequency generation, the period time (T) is controlled by CC0 register instead of PER. WO[0] toggles on each update condition.

# 32-bit ARM-Based Microcontrollers

| Symbol            | Parameter                                    | Conditions                                                                                              | Min. | Тур. | Max. | Units |

|-------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------|------|------|------|-------|

| I <sub>DFLL</sub> | Power<br>consumption on<br>V <sub>DDIN</sub> | f <sub>REF</sub> = XTAL, 32 .768kHz, 100ppm<br>DFLLMUL = 1464                                           | -    | 425  | 482  | μA    |

| t <sub>LOCK</sub> | Lock time                                    | f <sub>REF</sub> = XTAL, 32 .768kHz, 100ppm<br>DFLLMUL = 1464<br>DFLLVAL.COARSE = DFLL48M<br>COARSE CAL | 100  | 200  | 500  | μs    |

|                   |                                              | DFLLVAL.FINE = 512                                                                                      |      |      |      |       |

|                   |                                              | DFLLCTRL.BPLCKC = 1                                                                                     |      |      |      |       |

|                   |                                              | DFLLCTRL.QLDIS = 0                                                                                      |      |      |      |       |

|                   |                                              | DFLLCTRL.CCDIS = 1                                                                                      |      |      |      |       |

|                   |                                              | DFLLMUL.FSTEP = 10                                                                                      |      |      |      |       |

| Symbol            | Parameter                              | Conditions                                                                                    | Min.   | Тур.   | Max.   | Units |

|-------------------|----------------------------------------|-----------------------------------------------------------------------------------------------|--------|--------|--------|-------|

| f <sub>OUT</sub>  | Average Output<br>frequency            | f <sub>REF</sub> = 32 .768kHz                                                                 | 47.963 | 47.972 | 47.981 | MHz   |

| f <sub>REF</sub>  | Reference<br>frequency                 |                                                                                               | 0.732  | 32.768 | 33     | kHz   |

| Jitter            | Cycle to Cycle jitter                  | f <sub>REF</sub> = 32 .768kHz                                                                 | -      | -      | 0.42   | ns    |

| I <sub>DFLL</sub> | Power consumption on $V_{\text{DDIN}}$ | f <sub>REF</sub> =32 .768kHz                                                                  | -      | 403    | 453    | μA    |

| t <sub>LOCK</sub> | Lock time                              | f <sub>REF</sub> = 32 .768kHz<br>DFLLVAL.COARSE = DFLL48M<br>COARSE CAL<br>DFLLVAL.FINE = 512 | -      | 200    | 500    | μs    |

|                   |                                        | DFLLCTRL.BPLCKC = 1                                                                           |        |        |        |       |

|                   |                                        | DFLLCTRL.QLDIS = 0                                                                            |        |        |        |       |

|                   |                                        | DFLLCTRL.CCDIS = 1                                                                            |        |        |        |       |

|                   |                                        | DFLLMUL.FSTEP = 10                                                                            |        |        |        |       |

1. To insure that the device stays within the maximum allowed clock frequency, any reference clock for DFLL in close loop must be within a 2% error accuracy.

# **39.5** Clocks and Crystal Oscillators

The SAM D21 can be run from internal or external clock sources, or a mix of internal and external sources. An example of usage will be to use the internal 8MHz oscillator as source for the system clock, and an external 32.768kHz watch crystal as clock source for the Real-Time counter (RTC).

# 39.5.1 External Clock Source

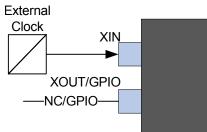

#### Figure 39-5. External Clock Source Example Schematic

# Table 39-4. External Clock Source Connections

| Signal Name | Recommended Pin Connection                        | Description                        |

|-------------|---------------------------------------------------|------------------------------------|

| XIN         | XIN is used as input for an external clock signal | Input for inverting oscillator pin |

| XOUT/GPIO   | Can be left unconnected or used as normal GPIO    |                                    |

# 39.5.2 Crystal Oscillator

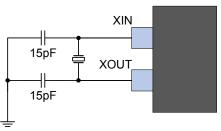

#### Figure 39-6. Crystal Oscillator Example Schematic

The crystal should be located as close to the device as possible. Long signal lines may cause too high load to operate the crystal, and cause crosstalk to other parts of the system.

#### Table 39-5. Crystal Oscillator Checklist

| Signal Name | Recommended Pin Connection            | Description                           |

|-------------|---------------------------------------|---------------------------------------|

| XIN         | Load capacitor 15pF <sup>(1)(2)</sup> | External crystal between 0.4 to 30MHz |

| XOUT        | Load capacitor 15pF <sup>(1)(2)</sup> |                                       |

- 1. These values are given only as typical example.

- 2. Decoupling capacitor should be placed close to the device for each supply pin pair in the signal group.

# 39.5.3 External Real Time Oscillator

The low frequency crystal oscillator is optimized for use with a 32.768kHz watch crystal. When selecting crystals, load capacitance and crystal's Equivalent Series Resistance (ESR) must be taken into consideration. Both values are specified by the crystal vendor.

|                  | <ul> <li>2 – The DFLL status bits in the PCLKSR register during the USB clock recovery mode can be wrong after a USB suspend state.</li> <li>Errata reference: 11938</li> <li>Fix/Workaround:</li> <li>Do not monitor the DFLL status bits in the PCLKSR register during the USB clock recovery mode.</li> </ul>                                                                                                                                                                                                                                                                                                  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | <ul> <li>3 – If the DFLL48M reaches the maximum or minimum COARSE or<br/>FINE calibration values during the locking sequence, an out of bounds<br/>interrupt will be generated. These interrupts will be generated even if<br/>the final calibration values at DFLL48M lock are not at maximum or<br/>minimum, and might therefore be false out of bounds interrupts.<br/>Errata reference: 10669<br/>Fix/Workaround:<br/>Check that the lockbits: DFLLLCKC and DFLLLCKF in the SYSCTRL<br/>Interrupt Flag Status and Clear register (INTFLAG) are both set before<br/>enabling the DFLLOOB interrupt.</li> </ul> |

| 40.1.1.5 XOSC32K |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                  | <ul> <li>1 – The automatic amplitude control of the XOSC32K does not work.</li> <li>Errata reference: 10933</li> <li>Fix/Workaround:</li> <li>Use the XOSC32K with Automatic Amplitude control disabled</li> <li>(XOSC32K.AAMPEN = 0)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                  |

| 40.1.1.6 FDPLL   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                  | 1 – The lock flag (DPLLSTATUS.LOCK) may clear randomly. When the<br>lock flag randomly clears, DPLLLCKR and DPLLLCKF interrupts will<br>also trigger, and the DPLL output is masked.<br>Errata reference: 11791<br>Fix/Workaround:<br>Set DPLLCTRLB.LBYPASS to 1 to disable masking of the DPLL output by<br>the lock status.                                                                                                                                                                                                                                                                                     |

|                  | 2 – FDPLL lock time-out values are different from the parameters in the datasheet.<br>Errata reference: 12145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                  | Fix/Workaround:<br>The time-out values are:<br>- DPLLCTRLB.LTIME[2:0] = 4 : 10ms<br>- DPLLCTRLB.LTIME[2:0] = 5 : 10ms<br>- DPLLCTRLB.LTIME[2:0] = 6 : 11ms<br>- DPLLCTRLB.LTIME[2:0] = 7 : 11ms                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                  | 3 – When changing on-the-fly the FDPLL ratio in DPLLnRATIO register,<br>STATUS.DPLLnLDRTO will not be set when the ratio update will be<br>completed.<br>Errata reference: 15753<br>Fix/Workaround:<br>Wait for the interruption flag INTFLAG.DPLLnLDRTO instead.                                                                                                                                                                                                                                                                                                                                                 |

| 40.1.2.3 | PM      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |         | 1 – In debug mode, if a watchdog reset occurs, the debug session is lost.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          |         | Errata reference: 12196                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |         | Fix/Workaround:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |         | A new debug session must be restart after a watchdog reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 40.1.2.4 | DFLL48M |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |         | <ul> <li>1 – The DFLL clock must be requested before being configured otherwise a write access to a DFLL register can freeze the device.</li> <li>Errata reference: 9905</li> <li>Fix/Workaround:</li> <li>Write a zero to the DFLL ONDEMAND bit in the DFLLCTRL register before</li> </ul>                                                                                                                                                                                                                                                                                             |

|          |         | configuring the DFLL module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|          |         | 2 – The DFLL status bits in the PCLKSR register during the USB clock<br>recovery mode can be wrong after a USB suspend state.<br>Errata reference: 11938<br>Fix/Workaround:                                                                                                                                                                                                                                                                                                                                                                                                             |

|          |         | Do not monitor the DFLL status bits in the PCLKSR register during the USB clock recovery mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |         | <ul> <li>3 – If the DFLL48M reaches the maximum or minimum COARSE or<br/>FINE calibration values during the locking sequence, an out of bounds<br/>interrupt will be generated. These interrupts will be generated even if<br/>the final calibration values at DFLL48M lock are not at maximum or<br/>minimum, and might therefore be false out of bounds interrupts.<br/>Errata reference: 10669</li> <li>Fix/Workaround:</li> <li>Check that the lockbits: DFLLLCKC and DFLLLCKF in the SYSCTRL<br/>Interrupt Flag Status and Clear register (INTFLAG) are both set before</li> </ul> |

|          |         | enabling the DFLLOOB interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 40.1.2.5 | XOSC32K |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |         | <ul> <li>1 – The automatic amplitude control of the XOSC32K does not work.</li> <li>Errata reference: 10933</li> <li>Fix/Workaround:</li> <li>Use the XOSC32K with Automatic Amplitude control disabled</li> <li>(XOSC32K.AAMPEN = 0)</li> </ul>                                                                                                                                                                                                                                                                                                                                        |

|          |         | (XOOOJZIX.AAWII EIN = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 40.1.2.6 | FDPLL   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |         | <ul> <li>1 – When changing on-the-fly the FDPLL ratio in DPLLnRATIO register,<br/>STATUS.DPLLnLDRTO will not be set when the ratio update will be<br/>completed.</li> <li>Errata reference: 15753</li> <li>Fix/Workaround:</li> <li>Wait for the interruption flag INTFLAG.DPLLnLDRTO instead.</li> </ul>                                                                                                                                                                                                                                                                               |

| 40.1.2.7 | DMAC    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |         | 1 – When at least one channel using linked descriptors is already<br>active, enabling another DMA channel (with or without linked<br>descriptors) can result in a channel Fetch Error (FERR) or an incorrect<br>descriptor fetch.                                                                                                                                                                                                                                                                                                                                                       |

|               | To use the Master or Slave SCL low extend time-outs, enable the SCL Low Time-out (CTRLA.LOWTOUT=1).                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | 2 – In USART autobaud mode, missing stop bits are not recognized as<br>inconsistent sync (ISF) or framing (FERR) errors.<br>Errata reference: 13852<br>Fix/Workaround:<br>None                                                                                                                                                                                                                                                                                                                                     |

|               | <ul> <li>3 – If the SERCOM is enabled in SPI mode with SSL detection enabled<br/>(CTRLB.SSDE) and CTRLB.RXEN=1, an erroneous slave select low<br/>interrupt (INTFLAG.SSL) can be generated.</li> <li>Errata reference: 13369</li> <li>Fix/Workaround:</li> <li>Enable the SERCOM first with CTRLB.RXEN=0. In a subsequent write, set<br/>CTRLB.RXEN=1.</li> </ul>                                                                                                                                                  |

|               | 4 – In TWI master mode, an ongoing transaction should be stalled<br>immediately when DBGCTRL.DBGSTOP is set and the CPU enters<br>debug mode. Instead, it is stopped when the current byte transaction is<br>completed and the corresponding interrupt is triggered if enabled.<br>Errata reference: 12499<br>Fix/Workaround:                                                                                                                                                                                      |

|               | In TWI master mode, keep DBGCTRL.DBGSTOP=0 when in debug mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 40.1.3.12 TC  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|               | <ul> <li>1 – Spurious TC overflow and Match/Capture events may occur.</li> <li>Errata reference: 13268</li> <li>Fix/Workaround:</li> <li>Do not use the TC overflow and Match/Capture events. Use the corresponding Interrupts instead.</li> </ul>                                                                                                                                                                                                                                                                 |

| 40.1.3.13 TCC |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|               | <ul> <li>1 – Using TCC in dithering mode with external retrigger events can lead<br/>to unexpected stretch of right aligned pulses, or shrink of left aligned<br/>pulses.</li> <li>Errata reference: 15625</li> <li>Fix/Workaround:</li> <li>Do not use retrigger events/actions when TCC is configured in dithering<br/>mode.</li> </ul>                                                                                                                                                                          |

|               | 2 – Advance capture mode (CAPTMIN CAPTMAX LOCMIN LOCMAX<br>DERIV0) doesn't work if an upper channel is not in one of these mode.<br>Example: when CC[0]=CAPTMIN, CC[1]=CAPTMAX, CC[2]=CAPTEN,<br>and CC[3]=CAPTEN, CAPTMIN and CAPTMAX won't work.<br>Errata reference: 14817<br>Fix/Workaround:<br>Basic capture mode must be set in lower channel and advance capture<br>mode in upper channel.<br>Example: CC[0]=CAPTEN, CC[1]=CAPTEN, CC[2]=CAPTMIN,<br>CC[3]=CAPTMAX<br>All capture will be done as expected. |

|               | 3 – In RAMP 2 mode with Fault keep, qualified and restart:                                                                                                                                                                                                                                                                                                                                                                                                                                                         |