#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ĿХF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 38                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                               |

| Data Converters            | A/D 14x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-TQFP                                                                    |

| Supplier Device Package    | 48-TQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd21g15b-aft |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Up to four compare channels with optional complementary output

- · Generation of synchronized pulse width modulation (PWM) pattern across port pins

- Deterministic fault protection, fast decay and configurable dead-time between complementary output

- Dithering that increase resolution with up to 5 bit and reduce quantization error

- 32-bit Real Time Counter (RTC) with clock/calendar function

- Watchdog Timer (WDT)

- CRC-32 generator

- One full-speed (12Mbps) Universal Serial Bus (USB) 2.0 interface

- Embedded host and device function

- Eight endpoints

- Up to six Serial Communication Interfaces (SERCOM), each configurable to operate as either:

- USART with full-duplex and single-wire half-duplex configuration

- I2C up to 3.4MHz

- SPI

- LIN slave

- One two-channel Inter-IC Sound (I<sup>2</sup>S) interface

- One 12-bit, 350ksps Analog-to-Digital Converter (ADC) with up to 20 channels

- Differential and single-ended input

- 1/2x to 16x programmable gain stage

- Automatic offset and gain error compensation

- Oversampling and decimation in hardware to support 13-, 14-, 15- or 16-bit resolution

- 10-bit, 350ksps Digital-to-Analog Converter (DAC)

- Two Analog Comparators (AC) with window compare function

- Peripheral Touch Controller (PTC)

- 256-Channel capacitive touch and proximity sensing

- I/O

- Up to 52 programmable I/O pins

- Drop in compatible with SAM D20

- Packages

- 64-pin TQFP, QFN, UFBGA

- 48-pin TQFP, QFN, WLCSP

- 32-pin TQFP, QFN, WLCSP

- Operating Voltage

- 1.62V 3.63V

- 4. Note that TC6 and TC7 are not supported on the SAM D21E and G devices. Refer to Configuration Summary for details.

- 5. This function is only activated in the presence of a debugger.

- If the PA24 and PA25 pins are not connected, it is recommended to enable a pull-up on PA24 and PA25 through input GPIO mode. The aim is to avoid an eventually extract power consumption (<1mA) due to a not stable level on pad. The port PA24 and PA25 doesn't have Drive Strength option.

## **Related Links**

**Electrical Characteristics**

# 7.2 Other Functions

# 7.2.1 Oscillator Pinout

The oscillators are not mapped to the normal PORT functions and their multiplexing are controlled by registers in the System Controller (SYSCTRL).

# Table 7-2. Oscillator Pinout

| Oscillator | Supply | Signal | I/O pin |

|------------|--------|--------|---------|

| XOSC       | VDDIO  | XIN    | PA14    |

|            |        | XOUT   | PA15    |

| XOSC32K    | VDDANA | XIN32  | PA00    |

|            |        | XOUT32 | PA01    |

# 7.2.2 Serial Wire Debug Interface Pinout

Only the SWCLK pin is mapped to the normal PORT functions. A debugger cold-plugging or hot-plugging detection will automatically switch the SWDIO port to the SWDIO function.

# Table 7-3. Serial Wire Debug Interface Pinout

| Signal | Supply | I/O pin |

|--------|--------|---------|

| SWCLK  | VDDIO  | PA30    |

| SWDIO  | VDDIO  | PA31    |

# 7.2.3 SERCOM I<sup>2</sup>C Pins

# Table 7-4. SERCOM Pins Supporting I<sup>2</sup>C

| Device   | Pins Supporting I <sup>2</sup> C Hs mode                               |

|----------|------------------------------------------------------------------------|

| SAM D21E | PA08, PA09, PA16, PA17, PA22, PA23                                     |

| SAM D21G | PA08, PA09, PA12, PA13, PA16, PA17, PA22, PA23                         |

| SAM D21J | PA08, PA09, PA12, PA13, PA16, PA17, PA22, PA23, PB12, PB13, PB16, PB17 |

stall. APB registers can also be read while the synchronization is ongoing without causing the peripheral bus to stall.

# 14.3.1.3 Read-Synchronization

Reading a read-synchronized peripheral core register will cause the peripheral bus to stall immediately until the read-synchronization is complete. STATUS.SYNCBUSY will not be set. Refer to Synchronization Delay for details on the synchronization delay. Note that reading a read-synchronized peripheral core register while STATUS.SYNCBUSY is one will cause the peripheral bus to stall twice; first because of the ongoing synchronization, and then again because reading a read-synchronized core register will cause the peripheral bus to stall immediately.

#### 14.3.1.4 Completion of synchronization

The user can either poll STATUS.SYNCBUSY or use the Synchronisation Ready interrupt (if available) to check when the synchronization is complete. It is also possible to perform the next read/write operation and wait, as this next operation will be started once the previous write/read operation is synchronized and/or complete.

#### 14.3.1.5 Read Request

The read request functionality is only available to peripherals that have the Read Request register (READREQ) implemented. Refer to the register description of individual peripheral chapters for details.

To avoid forcing the peripheral bus to stall when reading read-synchronized peripheral core registers, the read request mechanism can be used.

#### **Basic Read Request**

Writing a '1' to the Read Request bit in the Read Request register (READREQ.RREQ) will request readsynchronization of the register specified in the Address bits in READREQ (READREQ.ADDR) and set STATUS.SYNCBUSY. When read-synchronization is complete, STATUS.SYNCBUSY is cleared. The read-synchronized value is then available for reading without delay until READREQ.RREQ is written to '1' again.

The address to use is the offset to the peripheral's base address of the register that should be synchronized.

#### **Continuous Read Request**

Writing a '1' to the Read Continuously bit in READREQ (READREQ.RCONT) will force continuous readsynchronization of the register specified in READREQ.ADDR. The latest value is always available for reading without stalling the bus, as the synchronization mechanism is continuously synchronizing the given value.

SYNCBUSY is set for the first synchronization, but not for the subsequent synchronizations. If another synchronization is attempted, i.e. by executing a write-operation of a write-synchronized register, the read request will be stopped, and will have to be manually restarted.

#### Note:

The continuous read-synchronization is paused in sleep modes where the generic clock is not running. This means that a new read request is required if the value is needed immediately after exiting sleep.

#### 14.3.1.6 Enable Write-Synchronization

Writing to the Enable bit in the Control register (CTRL.ENABLE) will also trigger write-synchronization and set STATUS.SYNCBUSY. CTRL.ENABLE will read its new value immediately after being written. The Synchronisation Ready interrupt (if available) cannot be used for Enable write-synchronization.

When the enable write-synchronization is ongoing (STATUS.SYNCBUSY is one), attempt to do any of the following will cause the peripheral bus to stall until the enable synchronization is complete:

# 17. SYSCTRL – System Controller

# 17.1 Overview

The System Controller (SYSCTRL) provides a user interface to the clock sources, brown out detectors, on-chip voltage regulator and voltage reference of the device.

Through the interface registers, it is possible to enable, disable, calibrate and monitor the SYSCTRL subperipherals.

All sub-peripheral statuses are collected in the Power and Clocks Status register (PCLKSR). They can additionally trigger interrupts upon status changes via the INTENSET (INTENSET), INTENCLR (INTENCLR) and INTFLAG (INTFLAG) registers.

Additionally, BOD33 and BOD12 interrupts can be used to wake up the device from standby mode upon a programmed brown-out detection.

# 17.2 Features

- 0.4-32MHz Crystal Oscillator (XOSC)

- Tunable gain control

- Programmable start-up time

- Crystal or external input clock on XIN I/O

- 32.768kHz Crystal Oscillator (XOSC32K)

- Automatic or manual gain control

- Programmable start-up time

- Crystal or external input clock on XIN32 I/O

- 32.768kHz High Accuracy Internal Oscillator (OSC32K)

- Frequency fine tuning

- Programmable start-up time

- 32.768kHz Ultra Low Power Internal Oscillator (OSCULP32K)

- Ultra low power, always-on oscillator

- Frequency fine tuning

- Calibration value loaded from Flash Factory Calibration at reset

- 8MHz Internal Oscillator (OSC8M)

- Fast startup

- Output frequency fine tuning

- 4/2/1MHz divided output frequencies available

- Calibration value loaded from Flash Factory Calibration at reset

- Digital Frequency Locked Loop (DFLL48M)

- Internal oscillator with no external components

- 48MHz output frequency

- Operates standalone as a high-frequency programmable oscillator in open loop mode

- Operates as an accurate frequency multiplier against a known frequency in closed loop mode

- Fractional Digital Phase Locked Loop (FDPLL96M)

- 48MHz to 96MHz output clock frequency

Writing a zero to this bit has no effect.

Writing a one to this bit clears the Synchronization Ready interrupt flag.

# Bits 1,0 – CMPx : Compare x [x=1:0]

This flag is cleared by writing a one to the flag.

This flag is set on the next CLK\_RTC\_CNT cycle after a match with the compare condition and an interrupt request will be generated if INTENCLR/SET.CMPx is one.

Writing a zero to this bit has no effect.

Writing a one to this bit clears the Compare x interrupt flag.

## 19.8.16 Interrupt Flag Status and Clear - MODE2

Name: INTFLAG Offset: 0x08 Reset: 0x00 Property: -

| Bit    | 7   | 6       | 5 | 4 | 3 | 2 | 1 | 0      |

|--------|-----|---------|---|---|---|---|---|--------|

|        | OVF | SYNCRDY |   |   |   |   |   | ALARM0 |

| Access | R/W | R/W     |   |   |   |   |   | R/W    |

| Reset  | 0   | 0       |   |   |   |   |   | 0      |

## Bit 7 – OVF: Overflow

This flag is cleared by writing a one to the flag.

This flag is set on the next CLK\_RTC\_CNT cycle after an overflow condition occurs, and an interrupt request will be generated if INTENCLR/SET.OVF is one.

Writing a zero to this bit has no effect.

Writing a one to this bit clears the Overflow interrupt flag.

#### Bit 6 – SYNCRDY: Synchronization Ready

This flag is cleared by writing a one to the flag.

This flag is set on a 1-to-0 transition of the Synchronization Busy bit in the Status register (STATUS.SYNCBUSY), except when caused by enable or software reset, and an interrupt request will be generated if INTENCLR/SET.SYNCRDY is one.

Writing a zero to this bit has no effect.

Writing a one to this bit clears the Synchronization Ready interrupt flag.

#### Bit 0 – ALARM0: Alarm 0

This flag is cleared by writing a one to the flag.

This flag is set on the next CLK\_RTC\_CNT cycle after a match with ALARM0 condition occurs, and an interrupt request will be generated if INTENCLR/SET.ALARM0 is also one.

Writing a zero to this bit has no effect.

Writing a one to this bit clears the Alarm 0 interrupt flag.

• Issue an Erase Row command.

Note: The NVM Address bit field in the Address register (ADDR.ADDR) uses 16-bit addressing.

## 22.6.4.6 Lock and Unlock Region

These commands are used to lock and unlock regions as detailed in section Region Lock Bits.

# 22.6.4.7 Set and Clear Power Reduction Mode

The NVM Controller and block can be taken in and out of power reduction mode through the Set and Clear Power Reduction Mode commands. When the NVM Controller and block are in power reduction mode, the Power Reduction Mode bit in the Status register (STATUS.PRM) is set.

## 22.6.5 NVM User Configuration

The NVM user configuration resides in the auxiliary space. Refer to the Physical Memory Map of the device for calibration and auxiliary space address mapping.

The bootloader resides in the main array starting at offset zero. The allocated boot loader section is writeprotected.

| BOOTPROT [2:0]     | Rows Protected by BOOTPROT | Boot Loader Size in Bytes |

|--------------------|----------------------------|---------------------------|

| 0x7 <sup>(1)</sup> | None                       | 0                         |

| 0x6                | 2                          | 512                       |

| 0x5                | 4                          | 1024                      |

| 0x4                | 8                          | 2048                      |

| 0x3                | 16                         | 4096                      |

| 0x2                | 32                         | 8192                      |

| 0x1                | 64                         | 16384                     |

| 0x0                | 128                        | 32768                     |

#### Table 22-2. Boot Loader Size

**Note:** 1) Default value is 0x7.

The EEPROM[2:0] bits indicate the EEPROM size, see the table below. The EEPROM resides in the upper rows of the NVM main address space and is writable, regardless of the region lock status.

Table 22-3. EEPROM Size

| EEPROM[2:0] | Rows Allocated to EEPROM | EEPROM Size in Bytes |

|-------------|--------------------------|----------------------|

| 7           | None                     | 0                    |

| 6           | 1                        | 256                  |

| 5           | 2                        | 512                  |

| 4           | 4                        | 1024                 |

| 3           | 8                        | 2048                 |

| 2           | 16                       | 4096                 |

| 1           | 32                       | 8192                 |

| 0           | 64                       | 16384                |

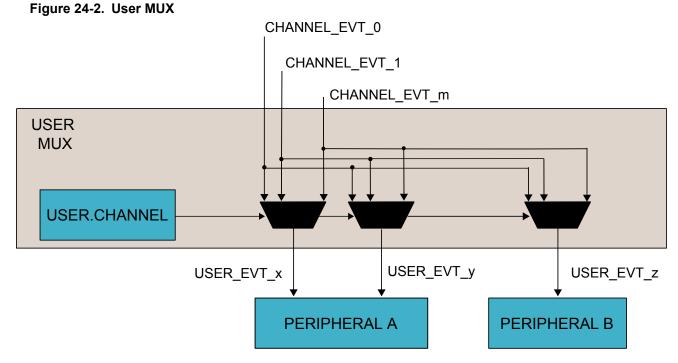

To configure a user multiplexer, the USER register must be written in a single 16-bit write. It is possible to read out the configuration of a user by first selecting the user by writing to USER.USER using an 8-bit write and then performing a read of the 16-bit USER register.

# 24.6.2.4 Channel Setup

An event channel can select one event from a list of event generators. Depending on configuration, the selected event could be synchronized, resynchronized or asynchronously sent to the users. When synchronization or resynchronization is required, the channel includes an internal edge detector, allowing the Event System to generate internal events when rising, falling or both edges are detected on the selected event generator. An event channel is able to generate internal events for the specific software commands. All these configurations are available in the Channel register (CHANNEL).

To configure a channel, the Channel register must be written in a single 32-bit write. It is possible to read out the configuration of a channel by first selecting the channel by writing to CHANNEL.CHANNEL using a, 8-bit write, and then performing a read of the CHANNEL register.

# 24.6.2.5 Channel Path

There are three different ways to propagate the event provided by an event generator:

- Asynchronous path

- Synchronous path

- Resynchronized path

# 26. SERCOM USART – SERCOM Universal Synchronous and Asynchronous Receiver and Transmitter

# 26.1 Overview

The Universal Synchronous and Asynchronous Receiver and Transmitter (USART) is one of the available modes in the Serial Communication Interface (SERCOM).

The USART uses the SERCOM transmitter and receiver, see Block Diagram. Labels in uppercase letters are synchronous to CLK\_SERCOMx\_APB and accessible for CPU. Labels in lowercase letters can be programmed to run on the internal generic clock or an external clock.

The transmitter consists of a single write buffer, a shift register, and control logic for different frame formats. The write buffer support data transmission without any delay between frames. The receiver consists of a two-level receive buffer and a shift register. Status information of the received data is available for error checking. Data and clock recovery units ensure robust synchronization and noise filtering during asynchronous data reception.

#### **Related Links**

SERCOM - Serial Communication Interface

# 26.2 USART Features

- Full-duplex operation

- Asynchronous (with clock reconstruction) or synchronous operation

- Internal or external clock source for asynchronous and synchronous operation

- Baud-rate generator

- Supports serial frames with 5, 6, 7, 8 or 9 data bits and 1 or 2 stop bits

- Odd or even parity generation and parity check

- Selectable LSB- or MSB-first data transfer

- Buffer overflow and frame error detection

- Noise filtering, including false start-bit detection and digital low-pass filter

- Collision detection

- Can operate in all sleep modes

- Operation at speeds up to half the system clock for internally generated clocks

- Operation at speeds up to the system clock for externally generated clocks

- RTS and CTS flow control

- IrDA modulation and demodulation up to 115.2kbps

- Start-of-frame detection

- Can work with DMA

#### **Related Links**

Features

- 4. Set the Collision Detected bit (STATUS.COLL) along with the Error interrupt flag (INTFLAG.ERROR).

- 5. Set the Transmit Complete interrupt flag (INTFLAG.TXC), since the transmit buffer no longer contains data.

After a collision, software must manually enable the transmitter again before continuing, after assuring that the CTRLB Synchronization Busy bit (SYNCBUSY.CTRLB) is not set.

#### 26.6.3.6 Loop-Back Mode

For loop-back mode, configure the Receive Data Pinout (CTRLA.RXPO) and Transmit Data Pinout (CTRLA.TXPO) to use the same data pins for transmit and receive. The loop-back is through the pad, so the signal is also available externally.

## 26.6.3.7 Start-of-Frame Detection

The USART start-of-frame detector can wake up the CPU when it detects a start bit. In standby sleep mode, the internal fast startup oscillator must be selected as the GCLK\_SERCOMx\_CORE source.

When a 1-to-0 transition is detected on RxD, the 8MHz Internal Oscillator is powered up and the USART clock is enabled. After startup, the rest of the data frame can be received, provided that the baud rate is slow enough in relation to the fast startup internal oscillator start-up time. Refer to *Electrical Characteristics* for details. The start-up time of this oscillator varies with supply voltage and temperature.

The USART start-of-frame detection works both in asynchronous and synchronous modes. It is enabled by writing '1' to the Start of Frame Detection Enable bit in the Control B register (CTRLB.SFDE).

If the Receive Start Interrupt Enable bit in the Interrupt Enable Set register (INTENSET.RXS) is set, the Receive Start interrupt is generated immediately when a start is detected.

When using start-of-frame detection without the Receive Start interrupt, start detection will force the 8MHz Internal Oscillator and USART clock active while the frame is being received. In this case, the CPU will not wake up until the Receive Complete interrupt is generated.

#### **Related Links**

**Electrical Characteristics**

#### 26.6.3.8 Sample Adjustment

In asynchronous mode (CTRLA.CMODE=0), three samples in the middle are used to determine the value based on majority voting. The three samples used for voting can be selected using the Sample Adjustment bit field in Control A register (CTRLA.SAMPA). When CTRLA.SAMPA=0, samples 7-8-9 are used for 16x oversampling, and samples 3-4-5 are used for 8x oversampling.

Name:CCxOffset:0x18+i\*0x2 [i=0..1]Reset:0x0000Property:Write-Synchronized

| Bit    | 15  | 14  | 13  | 12  | 11    | 10  | 9   | 8   |

|--------|-----|-----|-----|-----|-------|-----|-----|-----|

|        |     |     |     | CC[ | 15:8] |     |     |     |

| Access | R/W | R/W | R/W | R/W | R/W   | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0   | 0     | 0   | 0   | 0   |

|        |     |     |     |     |       |     |     |     |

| Bit    | 7   | 6   | 5   | 4   | 3     | 2   | 1   | 0   |

|        |     |     |     | CC[ | 7:0]  |     |     |     |

| Access | R/W | R/W | R/W | R/W | R/W   | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0   | 0     | 0   | 0   | 0   |

# Bits 15:0 – CC[15:0]: Channel x Compare/Capture Value

These bits contain the compare/capture value in 16-bit TC mode. In Match frequency (MFRQ) or Match PWM (MPWM) waveform operation (CTRLA.WAVEGEN), the CC0 register is used as a period register.

#### 30.8.14.3 Channel x Compare/Capture Value, 32-bit Mode

Name:CCxOffset:0x18+i\*0x4 [i=0..1]Reset:0x00000000Property:Write-Synchronized

| Bit    | 31  | 30  | 29  | 28   | 27    | 26  | 25  | 24  |

|--------|-----|-----|-----|------|-------|-----|-----|-----|

|        |     |     |     | CC[3 | 1:24] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W   | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0     | 0   | 0   | 0   |

|        |     |     |     |      |       |     |     |     |

| Bit    | 23  | 22  | 21  | 20   | 19    | 18  | 17  | 16  |

|        |     |     |     | CC[2 | 3:16] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W   | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0     | 0   | 0   | 0   |

|        |     |     |     |      |       |     |     |     |

| Bit    | 15  | 14  | 13  | 12   | 11    | 10  | 9   | 8   |

|        |     |     |     | CC[  | 15:8] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W   | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0     | 0   | 0   | 0   |

|        |     |     |     |      |       |     |     |     |

| Bit    | 7   | 6   | 5   | 4    | 3     | 2   | 1   | 0   |

|        |     |     |     | CC   | 7:0]  |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W   | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0     | 0   | 0   | 0   |

# Bits 31:0 – CC[31:0]: Channel x Compare/Capture Value

These bits contain the compare/capture value in 32-bit TC mode. In Match frequency (MFRQ) or Match PWM (MPWM) waveform operation (CTRLA.WAVEGEN), the CC0 register is used as a period register.

# 32-bit ARM-Based Microcontrollers

| Value | Name  | Description                                               |

|-------|-------|-----------------------------------------------------------|

| 0x0   | START | Blanking applied from start of the Ramp period            |

| 0x1   | RISE  | Blanking applied from rising edge of the waveform output  |

| 0x2   | FALL  | Blanking applied from falling edge of the waveform output |

| 0x3   | BOTH  | Blanking applied from each toggle of the waveform output  |

# Bit 4 – QUAL: Recoverable Fault n Qualification

Setting this bit enables the recoverable Fault n input qualification.

|   | Value | Description                                                                                    |

|---|-------|------------------------------------------------------------------------------------------------|

| ſ | 0     | The recoverable Fault n input is not disabled on CMPx value condition.                         |

|   | 1     | The recoverable Fault n input is disabled when output signal is at inactive level (CMPx == 0). |

## Bit 3 – KEEP: Recoverable Fault n Keep

Setting this bit enables the Fault n keep action.

| Value | Description                                                                   |

|-------|-------------------------------------------------------------------------------|

| 0     | The Fault n state is released as soon as the recoverable Fault n is released. |

| 1     | The Fault n state is released at the end of TCC cycle.                        |

## Bits 1:0 – SRC[1:0]: Recoverable Fault n Source

These bits select the TCC event input for recoverable Fault n.

Event system channel connected to MCEx event input, must be configured to route the event asynchronously, when used as a recoverable Fault n input.

| Value | Name     | Description                                                       |

|-------|----------|-------------------------------------------------------------------|

| 0x0   | DISABLE  | Fault input disabled                                              |

| 0x1   | ENABLE   | MCEx (x=0,1) event input                                          |

| 0x2   | INVERT   | Inverted MCEx (x=0,1) event input                                 |

| 0x3   | ALTFAULT | Alternate fault (A or B) state at the end of the previous period. |

# 31.8.6 Waveform Extension Control

Name: WEXCTRL Offset: 0x14 Reset: 0x00000000 Property: PAC Write-Protection, Enable-Protected

| Bit    | 31        | 30  | 29  | 28  | 27  | 26  | 25  | 24  |  |  |  |

|--------|-----------|-----|-----|-----|-----|-----|-----|-----|--|--|--|

|        | DTHS[7:0] |     |     |     |     |     |     |     |  |  |  |

| Access | R/W       | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Reset  | 0         | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

|        |           |     |     |     |     |     |     |     |  |  |  |

| Bit    | 23        | 22  | 21  | 20  | 19  | 18  | 17  | 16  |  |  |  |

|        | DTLS[7:0] |     |     |     |     |     |     |     |  |  |  |

| Access | R/W       | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Reset  | 0         | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

# 32-bit ARM-Based Microcontrollers

| Bit    | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |

|--------|------|------|------|------|------|------|------|------|

|        | NRV7 | NRV6 | NRV5 | NRV4 | NRV3 | NRV2 | NRV1 | NRV0 |

| Access | R/W  |

| Reset  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

|        |      |      |      |      |      |      |      |      |

| Bit    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|        | NRE7 | NRE6 | NRE5 | NRE4 | NRE3 | NRE2 | NRE1 | NRE0 |

| Access | R/W  |

| Reset  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

# Bits 31:28 – FILTERVAL1[3:0]: Non-Recoverable Fault Input 1 Filter Value

These bits define the filter value applied on TCE1 event input line. When the TCE1 event input line is configured as a synchronous event, this value must be 0x0.

# Bits 27:24 – FILTERVAL0[3:0]: Non-Recoverable Fault Input 0 Filter Value

These bits define the filter value applied on TCE0 event input line. When the TCE0 event input line is configured as a synchronous event, this value must be 0x0.

# Bits 23,22,21,20,19,18,17,16 – INVENx: Waveform Output x Inversion

These bits are used to select inversion on the output of channel x.

Writing a '1' to INVENx inverts output from WO[x].

Writing a '0' to INVENx disables inversion of output from WO[x].

## Bits 15,14,13,12,11,10,9,8 - NRVx: NRVx Non-Recoverable State x Output Value

These bits define the value of the enabled override outputs, under non-recoverable fault condition.

#### Bits 7,6,5,4,3,2,1,0 – NREx: Non-Recoverable State x Output Enable

These bits enable the override of individual outputs by NRVx value, under non-recoverable fault condition.

| Value | Description                                          |

|-------|------------------------------------------------------|

| 0     | Non-recoverable fault tri-state the output.          |

| 1     | Non-recoverable faults set the output to NRVx level. |

#### 31.8.8 Debug control

Name:DBGCTRLOffset:0x1EReset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2     | 1 | 0      |

|--------|---|---|---|---|---|-------|---|--------|

|        |   |   |   |   |   | FDDBD |   | DBGRUN |

| Access |   |   |   |   |   | R/W   |   | R/W    |

| Reset  |   |   |   |   |   | 0     |   | 0      |

# Bit 2 – FDDBD: Fault Detection on Debug Break Detection

This bit is not affected by software reset and should not be changed by software while the TCC is enabled.

# 32.8.6.8 Host Interrupt Pipe Set Register

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Pipe Interrupt Enable Set (PINTENCLR) register.

This register is cleared by USB reset or when PEN[n] is zero.

Name:PINTENSETOffset:0x109 + (n x 0x20)Reset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5     | 4     | 3    | 2      | 1 | 0     |

|--------|---|---|-------|-------|------|--------|---|-------|

|        |   |   | STALL | TXSTP | PERR | TRFAIL |   | TRCPT |

| Access |   |   | R/W   | R/W   | R/W  | R/W    |   | R/W   |

| Reset  |   |   | 0     | 0     | 0    | 0      |   | 0     |

#### Bit 5 – STALL: Stall Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will enable the Stall interrupt.

| Value | Description                      |

|-------|----------------------------------|

| 0     | The Stall interrupt is disabled. |

| 1     | The Stall interrupt is enabled.  |

#### Bit 4 – TXSTP: Transmitted Setup Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will enable the Transmitted Setup interrupt.

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | The Transmitted Setup interrupt is disabled. |

| 1     | The Transmitted Setup interrupt is enabled.  |

## Bit 3 – PERR: Pipe Error Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will enable the Pipe Error interrupt.

| Value | Description                           |

|-------|---------------------------------------|

| 0     | The Pipe Error interrupt is disabled. |

| 1     | The Pipe Error interrupt is enabled.  |

#### Bit 2 – TRFAIL: Transfer Fail Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will enable the Transfer Fail interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The Transfer Fail interrupt is disabled. |

| 1     | The Transfer Fail interrupt is enabled.  |

#### Bit 0 – TRCPT: Transfer Complete x interrupt Enable

Writing a zero to this bit has no effect.

Refer to *Nested Vector Interrupt Controller* for details. The user must read the INTFLAG register to determine which interrupt condition is present.

#### **Related Links**

Nested Vector Interrupt Controller

# 33.6.13 Events

The ADC can generate the following output events:

- Result Ready (RESRDY): Generated when the conversion is complete and the result is available.

- Window Monitor (WINMON): Generated when the window monitor condition match.

Setting an Event Output bit in the Event Control Register (EVCTRL.xxEO=1) enables the corresponding output event. Clearing this bit disables the corresponding output event. Refer to the *Event System* chapter for details on configuring the event system.

The peripheral can take the following actions on an input event:

- Start conversion (START): Start a conversion.

- Conversion flush (FLUSH): Flush the conversion.

Setting an Event Input bit in the Event Control register (EVCTRL.xxEI=1) enables the corresponding action on input event. Clearing this bit disables the corresponding action on input event.

**Note:** If several events are connected to the ADC, the enabled action will be taken on any of the incoming events. The events must be correctly routed in the Event System.

#### **Related Links**

EVSYS – Event System

#### 33.6.14 Sleep Mode Operation

The Run in Standby bit in the Control A register (CTRLA.RUNSTDBY) controls the behavior of the ADC during standby sleep mode. When CTRLA.RUNSTDBY=0, the ADC is disabled during sleep, but maintains its current configuration. When CTRLA.RUNSTDBY=1, the ADC continues to operate during sleep. Note that when CTRLA.RUNSTDBY=0, the analog blocks are powered off for the lowest power consumption. This necessitates a start-up time delay when the system returns from sleep.

When CTRLA.RUNSTDBY=1, any enabled ADC interrupt source can wake up the CPU. While the CPU is sleeping, ADC conversion can only be triggered by events.

#### 33.6.15 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

When executing an operation that requires synchronization, the Synchronization Busy bit in the Status register (STATUS.SYNCBUSY) will be set immediately, and cleared when synchronization is complete. The Synchronization Ready interrupt can be used to signal when synchronization is complete.

If an operation that requires synchronization is executed while STATUS.SYNCBUSY=1, the bus will be stalled. All operations will complete successfully, but the CPU will be stalled and interrupts will be pending as long as the bus is stalled.

The following bits are synchronized when written:

- Software Reset bit in the Control A register (CTRLA.SWRST)

- Enable bit in the Control A register (CTRLA.ENABLE)

The following registers are synchronized when written:

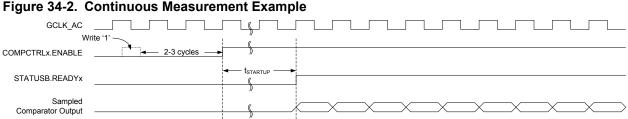

In continuous operation, edge detection of the comparator output for interrupts is done by comparing the current and previous sample. The sampling rate is the CLK\_AC\_DIG frequency. An example of continuous measurement is shown in the next figure.

For low-power operation, comparisons can be performed during sleep modes without a clock. The comparator is enabled continuously, and changes of the comparator state are detected asynchronously. When a toggle occurs, the Power Manager will start CLK\_AC\_DIG to register the appropriate peripheral events and interrupts. The CLK\_AC\_DIG clock is then disabled again automatically, unless configured to wake up the system from sleep.

## **Related Links**

**Electrical Characteristics**

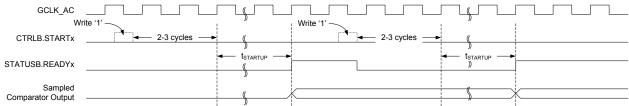

#### Single-Shot

Single-shot operation is selected by writing COMPCTRLx.SINGLE to '1'. During single-shot operation, the comparator is normally idle. The user starts a single comparison by writing '1' to the respective Start Comparison bit in the write-only Control B register (CTRLB.STARTx). The comparator is enabled, and after the start-up time has passed, a single comparison is done and STATUSA is updated. Appropriate peripheral events and interrupts are also generated. No new comparisons will be performed.

Writing '1' to CTRLB.STARTx also clears the Comparator x Ready bit in the Status B register (STATUSB.READYx). STATUSB.READYx is set automatically by hardware when the single comparison has completed.

To remove the need for polling, an additional means of starting the comparison is also available. A read of the Status C register (STATUSC) will start a comparison on all comparators currently configured for single-shot operation. The read will stall the bus until all enabled comparators are ready. If a comparator is already busy with a comparison, the read will stall until the current comparison is compete, and a new comparison will not be started.

A single-shot measurement can also be triggered by the Event System. Setting the Comparator x Event Input bit in the Event Control Register (EVCTRL.COMPEIx) enables triggering on incoming peripheral events. Each comparator can be triggered independently by separate events. Event-triggered operation is similar to user-triggered operation; the difference is that a peripheral event from another hardware module causes the hardware to automatically start the comparison and clear STATUSB.READYx.

To detect an edge of the comparator output in single-shot operation for the purpose of interrupts, the result of the current measurement is compared with the result of the previous measurement (one sampling period earlier). An example of single-shot operation is shown in the figure below.

#### Figure 34-3. Single-Shot Example

# 35.7 Register Summary

| Offset | Name        | Bit Pos. |              |         |  |       |          |          |         |          |  |

|--------|-------------|----------|--------------|---------|--|-------|----------|----------|---------|----------|--|

| 0x00   | CTRLA       | 7:0      |              |         |  |       |          | RUNSTDBY | ENABLE  | SWRST    |  |

| 0x01   | CTRLB       | 7:0      | REFSI        | EL[1:0] |  | BDWP  | VPD      | LEFTADJ  | IOEN    | EOEN     |  |

| 0x02   | EVCTRL      | 7:0      |              |         |  |       |          |          | EMPTYEO | STARTEI  |  |

| 0x03   | Reserved    |          |              |         |  |       |          |          |         |          |  |

| 0x04   | INTENCLR    | 7:0      |              |         |  |       |          | SYNCRDY  | EMPTY   | UNDERRUN |  |

| 0x05   | INTENSET    | 7:0      |              |         |  |       |          | SYNCRDY  | EMPTY   | UNDERRUN |  |

| 0x06   | INTFLAG     | 7:0      |              |         |  |       |          | SYNCRDY  | EMPTY   | UNDERRUN |  |

| 0x07   | STATUS      | 7:0      | SYNCBUSY     |         |  |       |          |          |         |          |  |

| 0x08   | DATA        | 7:0      |              |         |  | DAT   | A[7:0]   |          |         |          |  |

| 0x09   | DATA        | 15:8     |              |         |  | DATA  | [15:8]   |          |         |          |  |

| 0x0A   |             |          |              |         |  |       |          |          |         |          |  |

|        | Reserved    |          |              |         |  |       |          |          |         |          |  |

| 0x0B   |             |          |              |         |  |       |          |          |         |          |  |

| 0x0C   | DATABUF 7:0 |          | DATABUF[7:0] |         |  |       |          |          |         |          |  |

| 0x0D   | DAIADOI     | 15:8     |              |         |  | DATAB | UF[15:8] |          |         |          |  |

# 35.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to Register Access Protection.

Some registers are synchronized when read and/or written. Synchronization is denoted by the "Write-Synchronized" or the "Read-Synchronized" property in each individual register description. For details, refer to Synchronization.

Some registers are enable-protected, meaning they can only be written when the peripheral is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

# 35.8.1 Control A

Name:CTRLAOffset:0x00Reset:0x00Property:PAC Write-Protection, Write-Synchronized

| Bit    | 7 | 6 | 5 | 4 | 3 | 2        | 1      | 0     |

|--------|---|---|---|---|---|----------|--------|-------|

|        |   |   |   |   |   | RUNSTDBY | ENABLE | SWRST |

| Access |   |   |   |   |   | R/W      | R/W    | R/W   |

| Reset  |   |   |   |   |   | 0        | 0      | 0     |

Name:DATAOffset:0x08Reset:0x0000Property:PAC Write-Protection, Write-Synchronized

| Bit    | 15         | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

|--------|------------|----|----|----|----|----|---|---|

|        | DATA[15:8] |    |    |    |    |    |   |   |

| Access | W          | W  | W  | W  | W  | W  | W | W |

| Reset  | 0          | 0  | 0  | 0  | 0  | 0  | 0 | 0 |

|        |            |    |    |    |    |    |   |   |

| Bit    | 7          | 6  | 5  | 4  | 3  | 2  | 1 | 0 |

|        | DATA[7:0]  |    |    |    |    |    |   |   |

| Access | W          | W  | W  | W  | W  | W  | W | W |

| Reset  | 0          | 0  | 0  | 0  | 0  | 0  | 0 | 0 |

# Bits 15:0 – DATA[15:0]: Data value to be converted

DATA register contains the 10-bit value that is converted to a voltage by the DAC. The adjustment of these 10 bits within the 16-bit register is controlled by CTRLB.LEFTADJ.

| Table 35-1. Valid Data | 35-1. | Valid | Data | Bits |

|------------------------|-------|-------|------|------|

|------------------------|-------|-------|------|------|

| CTRLB.LEFTADJ | DATA       | Description             |

|---------------|------------|-------------------------|

| 0             | DATA[9:0]  | Right adjusted, 10-bits |

| 1             | DATA[15:6] | Left adjusted, 10-bits  |

# 35.8.9 Data Buffer

Name:DATABUFOffset:0x0CReset:0x0000Property:Write-Synchronized

| Bit    | 15            | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

|--------|---------------|----|----|----|----|----|---|---|

|        | DATABUF[15:8] |    |    |    |    |    |   |   |

| Access | W             | W  | W  | W  | W  | W  | W | W |

| Reset  | 0             | 0  | 0  | 0  | 0  | 0  | 0 | 0 |

|        |               |    |    |    |    |    |   |   |

| Bit    | 7             | 6  | 5  | 4  | 3  | 2  | 1 | 0 |

|        | DATABUF[7:0]  |    |    |    |    |    |   |   |

| Access | W             | W  | W  | W  | W  | W  | W | W |

| Reset  | 0             | 0  | 0  | 0  | 0  | 0  | 0 | 0 |

# Bits 15:0 – DATABUF[15:0]: Data Buffer

DATABUF contains the value to be transferred into DATA register.

# 32-bit ARM-Based Microcontrollers

| Name                | Description            | Mode                      | VDD=1.8V |      |      | VDD=3.3V |      |      | Units |

|---------------------|------------------------|---------------------------|----------|------|------|----------|------|------|-------|

|                     |                        |                           | Min.     | Тур. | Max. | Min.     | Тур. | Max. |       |

| t <sub>M_SDIH</sub> | Data input hold time   | Master mode               | -8.2     |      |      | -8.2     |      |      | ns    |

| t <sub>S_SDIS</sub> | Data input setup time  | Slave mode                | 9.1      |      |      | 8.3      |      |      | ns    |

| t <sub>S_SDIH</sub> | Data input hold time   | Slave mode                | 3.8      |      |      | 3.7      |      |      | ns    |

| t <sub>M_SDOV</sub> | Data output valid time | Master transmitter        |          |      | 2.5  |          |      | 1.9  | ns    |

| t <sub>M_SDOH</sub> | Data output hold time  | Master transmitter        | -0.1     |      |      | -0.1     |      |      | ns    |

| t <sub>S_SDOV</sub> | Data output valid time | Slave transmitter         |          |      | 29.8 |          |      | 19.7 | ns    |

| t <sub>S_SDOH</sub> | Data output hold time  | Slave transmitter         | 29.1     |      |      | 18.9     |      |      | ns    |

| t <sub>PDM2LS</sub> | Data input setup time  | Master mode PDM2<br>Left  | 35.5     |      |      | 25.3     |      |      | ns    |

| t <sub>PDM2LH</sub> | Data input hold time   | Master mode PDM2<br>Left  | -8.2     |      |      | -8.2     |      |      | ns    |

| t <sub>PDM2RS</sub> | Data input setup time  | Master mode PDM2<br>Right | 30.6     |      |      | 21.1     |      |      | ns    |

| t <sub>PDM2RH</sub> | Data input hold time   | Master mode PDM2<br>Right | -7       |      |      | -7       |      |      | ns    |

1. All timing characteristics given for 15pF capacitive load.

2. These values are based on simulations and not covered by test limits in production.

3. See I/O Pin Characteristics

| Table 38-11. Device and Package Maximum Weight |        |  |  |  |  |

|------------------------------------------------|--------|--|--|--|--|

| 140                                            | mg     |  |  |  |  |

| Table 38-12. Package Characteristics           |        |  |  |  |  |

| Moisture Sensitivity Level                     | MSL3   |  |  |  |  |

| Table 38-13. Package Reference                 |        |  |  |  |  |

| JEDEC Drawing Reference                        | MS-026 |  |  |  |  |

| JESD97 Classification                          | E3     |  |  |  |  |

Register Description:

REFCTRL bit selection names updated from AREFA / AREFB to VREFA / VREFB in Table 33-5

DAC – Digital-to-Analog Converter

Updated block diagram and signal description: VREFP replaced with VREFB.

**Electrical Characteristics**