Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 38                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                               |

| Data Converters            | A/D 14x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 48-QFN (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd21g16b-mft |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

characteristics). The system continues to be held in this static state until the internally regulated supplies have reached a safe operating state.

- 2. The PM starts, clocks are switched to the slow clock (Core Clock, System Clock, Flash Clock and any Bus Clocks that do not have clock gate control). Internal resets are maintained due to the external reset.

- 3. The debugger maintains a low level on SWCLK. RESET is released, resulting in a debugger Cold-Plugging procedure.

- 4. The debugger generates a clock signal on the SWCLK pin, the Debug Access Port (DAP) receives a clock.

- 5. The CPU remains in Reset due to the Cold-Plugging procedure; meanwhile, the rest of the system is released.

- 6. A Chip-Erase is issued to ensure that the Flash is fully erased prior to programming.

- 7. Programming is available through the AHB-AP.

- 8. After the operation is completed, the chip can be restarted either by asserting RESET, toggling power, or writing a '1' to the Status A register CPU Reset Phase Extension bit (STATUSA.CRSTEXT). Make sure that the SWCLK pin is high when releasing RESET to prevent extending the CPU reset.

# Related Links

Electrical Characteristics NVMCTRL – Non-Volatile Memory Controller Security Bit

# 13.9 Intellectual Property Protection

Intellectual property protection consists of restricting access to internal memories from external tools when the device is protected, and this is accomplished by setting the NVMCTRL security bit. This protected state can be removed by issuing a Chip-Erase (refer to Chip Erase). When the device is protected, read/write accesses using the AHB-AP are limited to the DSU address range and DSU commands are restricted. When issuing a Chip-Erase, sensitive information is erased from volatile memory and Flash.

The DSU implements a security filter that monitors the AHB transactions generated by the ARM AHB-AP inside the DAP. If the device is protected, then AHB-AP read/write accesses outside the DSU external address range are discarded, causing an error response that sets the ARM AHB-AP sticky error bits (refer to the ARM Debug Interface v5 Architecture Specification on http://www.arm.com).

The DSU is intended to be accessed either:

- Internally from the CPU, without any limitation, even when the device is protected

- Externally from a debug adapter, with some restrictions when the device is protected

For security reasons, DSU features have limitations when used from a debug adapter. To differentiate external accesses from internal ones, the first 0x100 bytes of the DSU register map have been mirrored at offset 0x100:

- The first 0x100 bytes form the internal address range

- The next 0x100 bytes form the external address range

When the device is protected, the DAP can only issue MEM-AP accesses in the DSU address range limited to the 0x100- 0x2000 offset range.

| GCLK<br>Generator ID | Reset Value after a User Reset                                                                                                                                                                 |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x02                 | 0x00010302 if the generator is not used by the RTC and not a source of a 'locked' generic clock<br>No change if the generator is used by the RTC or used by a GCLK with a WRTLOCK as one       |

| 0x03                 | 0x0000003 if the generator is not used by the RTC and not a source of a 'locked'<br>generic clock<br>No change if the generator is used by the RTC or used by a GCLK with a WRTLOCK as<br>one  |

| 0x04                 | 0x00000004 if the generator is not used by the RTC and not a source of a 'locked' generic clock<br>No change if the generator is used by the RTC or used by a GCLK with a WRTLOCK as one       |

| 0x05                 | 0x00000005 if the generator is not used by the RTC and not a source of a 'locked'<br>generic clock<br>No change if the generator is used by the RTC or used by a GCLK with a WRTLOCK as<br>one |

| 0x06                 | 0x0000006 if the generator is not used by the RTC and not a source of a 'locked'<br>generic clock<br>No change if the generator is used by the RTC or used by a GCLK with a WRTLOCK as<br>one  |

| 0x07                 | 0x00000007 if the generator is not used by the RTC and not a source of a 'locked'<br>generic clock<br>No change if the generator is used by the RTC or used by a GCLK with a WRTLOCK as<br>one |

| 0x08                 | 0x0000008 if the generator is not used by the RTC and not a source of a 'locked'<br>generic clock<br>No change if the generator is used by the RTC or used by a GCLK with a WRTLOCK as<br>one  |

| Value   | Name     | Description               |

|---------|----------|---------------------------|

| 0x0     | GCLKGEN0 | Generic clock generator 0 |

| 0x1     | GCLKGEN1 | Generic clock generator 1 |

| 0x2     | GCLKGEN2 | Generic clock generator 2 |

| 0x3     | GCLKGEN3 | Generic clock generator 3 |

| 0x4     | GCLKGEN4 | Generic clock generator 4 |

| 0x5     | GCLKGEN5 | Generic clock generator 5 |

| 0x6     | GCLKGEN6 | Generic clock generator 6 |

| 0x7     | GCLKGEN7 | Generic clock generator 7 |

| 0x8     | GCLKGEN8 | Generic clock generator 8 |

| 0x9-0xF | Reserved |                           |

# 15.8.5 Generic Clock Generator Division

Name: GENDIV

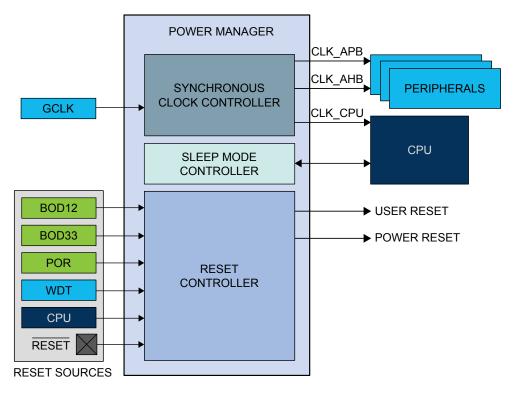

# 16.3 Block Diagram

Figure 16-1. PM Block Diagram

# 16.4 Signal Description

| Signal Name | Туре          | Description    |

|-------------|---------------|----------------|

| RESET       | Digital input | External reset |

Refer to *I/O Multiplexing and Considerations* for details on the pin mapping for this peripheral. One signal can be mapped on several pins.

# **Related Links**

I/O Multiplexing and Considerations

# 16.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

# 16.5.1 I/O Lines

Not applicable.

# 16.5.2 Power Management

Not applicable.

| Bit    | 7   | 6       | 5 | 4 | 3 | 2 | 1 | 0    |

|--------|-----|---------|---|---|---|---|---|------|

|        | OVF | SYNCRDY |   |   |   |   |   | CMP0 |

| Access | R/W | R/W     |   |   |   |   |   | R/W  |

| Reset  | 0   | 0       |   |   |   |   |   | 0    |

# Bit 7 – OVF: Overflow Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Overflow Interrupt Enable bit and disable the corresponding interrupt.

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | The Overflow interrupt is disabled.                                                    |

| 1     | The Overflow interrupt is enabled, and an interrupt request will be generated when the |

|       | Overflow interrupt flag is set.                                                        |

# Bit 6 – SYNCRDY: Synchronization Ready Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Synchronization Ready Interrupt Enable bit and disable the corresponding interrupt.

| Value | Description                                                                                                                                      |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The Synchronization Ready interrupt is disabled.                                                                                                 |

| 1     | The Synchronization Ready interrupt is enabled, and an interrupt request will be generated when the Synchronization Ready interrupt flag is set. |

## Bit 0 – CMP0: Compare 0 Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Compare 0 Interrupt Enable bit and disable the corresponding interrupt.

| Value | Description                                                                             |

|-------|-----------------------------------------------------------------------------------------|

| 0     | The Compare 0 interrupt is disabled.                                                    |

| 1     | The Compare 0 interrupt is enabled, and an interrupt request will be generated when the |

|       | Compare x interrupt flag is set.                                                        |

## 19.8.9 Interrupt Enable Clear - MODE1

Name:INTENCLROffset:0x06Reset:0x00Property:Write-Protected

| Bit    | 7   | 6       | 5 | 4 | 3 | 2 | 1    | 0    |

|--------|-----|---------|---|---|---|---|------|------|

|        | OVF | SYNCRDY |   |   |   |   | CMP1 | CMP0 |

| Access | R/W | R/W     |   |   |   |   | R/W  | R/W  |

| Reset  | 0   | 0       |   |   |   |   | 0    | 0    |

# Bit 7 – OVF: Overflow Interrupt Enable

Writing a zero to this bit has no effect.

# **Reset:** 0x00X0 **Property:** PAC Write-Protection, Enable-Protected

| 15 | 14      | 13 | 12 | 11     | 10                 | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----|---------|----|----|--------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |         |    |    | LVLEN3 | LVLEN2             | LVLEN1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LVLEN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|    |         |    |    | R/W    | R/W                | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|    |         |    |    | 0      | 0                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|    |         |    |    |        |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7  | 6       | 5  | 4  | 3      | 2                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|    |         |    |    |        | CRCENABLE          | DMAENABLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SWRST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    |         |    |    |        | R/W                | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|    |         |    |    |        | 0                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|    | 15<br>7 |    |    |        | LVLEN3<br>R/W<br>0 | Image: Constraint of the system         Image: Constand of the system         Image: Constando | Image: constraint of the state of the sta |

# Bits 8, 9, 10, 11 – LVLENx: Priority Level x Enable

When this bit is set, all requests with the corresponding level will be fed into the arbiter block. When cleared, all requests with the corresponding level will be ignored.

For details on arbitration schemes, refer to the Arbitration section.

These bits are not enable-protected.

| Value | Description                                                 |

|-------|-------------------------------------------------------------|

| 0     | Transfer requests for Priority level x will not be handled. |

| 1     | Transfer requests for Priority level x will be handled.     |

#### Bit 2 – CRCENABLE: CRC Enable

Writing a '0' to this bit will disable the CRC calculation when the CRC Status Busy flag is cleared (CRCSTATUS. CRCBUSY). The bit is zero when the CRC is disabled.

Writing a '1' to this bit will enable the CRC calculation.

| Value | Description                      |

|-------|----------------------------------|

| 0     | The CRC calculation is disabled. |

| 1     | The CRC calculation is enabled.  |

#### Bit 1 – DMAENABLE: DMA Enable

Setting this bit will enable the DMA module.

Writing a '0' to this bit will disable the DMA module. When writing a '0' during an ongoing transfer, the bit will not be cleared until the internal data transfer buffer is empty and the DMA transfer is aborted. The internal data transfer buffer will be empty once the ongoing burst transfer is completed.

This bit is not enable-protected.

| Value | Description                 |

|-------|-----------------------------|

| 0     | The peripheral is disabled. |

| 1     | The peripheral is enabled.  |

#### Bit 0 – SWRST: Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit when both the DMAC and the CRC module are disabled (DMAENABLE and CRCENABLE are '0') resets all registers in the DMAC (except DBGCTRL) to their initial state. If either the

| Bit    | 7            | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|--------------|-----|-----|-----|-----|-----|-----|-----|

|        | WRBADDR[7:0] |     |     |     |     |     |     |     |

| Access | R/W          | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset  | 0            | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

#### Bits 31:0 - WRBADDR[31:0]: Write-Back Memory Base Address

These bits store the Write-Back memory base address. The value must be 128-bit aligned.

#### 20.8.17 Channel ID

Name: CHID Offset: 0x3F Reset: 0x00 Property: -

| Bit    | 7 | 6 | 5 | 4 | 3   | 2   | 1    | 0   |

|--------|---|---|---|---|-----|-----|------|-----|

|        |   |   |   |   |     | ID[ | 3:0] |     |

| Access |   |   |   |   | R/W | R/W | R/W  | R/W |

| Reset  |   |   |   |   | 0   | 0   | 0    | 0   |

# Bits 3:0 – ID[3:0]: Channel ID

These bits define the channel number that will be affected by the channel registers (CH\*). Before reading or writing a channel register, the channel ID bit group must be written first.

## 20.8.18 Channel Control A

This register affects the DMA channel that is selected in the Channel ID register (CHID.ID).

Name:CHCTRLAOffset:0x40Reset:0x00Property:PAC Write-Protection, Enable-Protected

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0     |

|--------|---|---|---|---|---|---|--------|-------|

|        |   |   |   |   |   |   | ENABLE | SWRST |

| Access | R |   | R | R | R | R | R/W    | R/W   |

| Reset  | 0 |   | 0 | 0 | 0 | 0 | 0      | 0     |

#### Bit 1 – ENABLE: Channel Enable

Writing a '0' to this bit during an ongoing transfer, the bit will not be cleared until the internal data transfer buffer is empty and the DMA transfer is aborted. The internal data transfer buffer will be empty once the ongoing burst transfer is completed.

Writing a '1' to this bit will enable the DMA channel.

This bit is not enable-protected.

| Value | Description              |

|-------|--------------------------|

| 0     | DMA channel is disabled. |

| 1     | DMA channel is enabled.  |

| Value | Description                           |

|-------|---------------------------------------|

| 0     | The external interrupt x is disabled. |

| 1     | The external interrupt x is enabled.  |

#### 21.8.8 Interrupt Flag Status and Clear

| Name:     | INTFLAG    |

|-----------|------------|

| Offset:   | 0x10       |

| Reset:    | 0x00000000 |

| Property: | -          |

| Bit    | 31       | 30       | 29       | 28       | 27       | 26       | 25       | 24       |

|--------|----------|----------|----------|----------|----------|----------|----------|----------|

|        |          |          |          |          |          |          |          |          |

| Access |          |          |          |          |          |          |          |          |

| Reset  |          |          |          |          |          |          |          |          |

|        |          |          |          |          |          |          |          |          |

| Bit    | 23       | 22       | 21       | 20       | 19       | 18       | 17       | 16       |

|        |          |          |          |          |          |          | EXTINT17 | EXTINT16 |

| Access |          |          |          |          |          |          | R/W      | R/W      |

| Reset  |          |          |          |          |          |          | 0        | 0        |

|        |          |          |          |          |          |          |          |          |

| Bit    | 15       | 14       | 13       | 12       | 11       | 10       | 9        | 8        |

|        | EXTINT15 | EXTINT14 | EXTINT13 | EXTINT12 | EXTINT11 | EXTINT10 | EXTINT9  | EXTINT8  |

| Access | R/W      |

| Reset  | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |

|        |          |          |          |          |          |          |          |          |

| Bit    | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|        | EXTINT7  | EXTINT6  | EXTINT5  | EXTINT4  | EXTINT3  | EXTINT2  | EXTINT1  | EXTINT0  |

| Access | R/W      |

| Reset  | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |

Bits 17,16,15,14,13,12,11,10,9,8,7,6,5,4,3,2,1,0 – EXTINTx : External Interrupt x [x=17..0] This flag is cleared by writing a one to it.

This flag is set when EXTINTx pin matches the external interrupt sense configuration and will generate an interrupt request if INTENCLR/SET.EXTINT[x] is one.

Writing a zero to this bit has no effect.

Writing a one to this bit clears the External Interrupt x flag.

## 21.8.9 Wake-Up Enable

Name:WAKEUPOffset:0x14Reset:0x00000000Property:Write-Protected

# 24.4 Signal Description

Not applicable.

# 24.5 **Product Dependencies**

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

## 24.5.1 I/O Lines

Not applicable.

## 24.5.2 Power Management

The EVSYS can be used to wake up the CPU from all sleep modes, even if the clock used by the EVSYS channel and the EVSYS bus clock are disabled. Refer to the *PM* – *Power Manager* for details on the different sleep modes.

In all sleep modes, although the clock for the EVSYS is stopped, the device still can wake up the EVSYS clock. Some event generators can generate an event when their clocks are stopped.

#### **Related Links**

PM – Power Manager

## 24.5.3 Clocks

The EVSYS bus clock (CLK\_EVSYS\_APB) can be enabled and disabled in the Main Clock module, and the default state of CLK\_EVSYS\_APB can be found in *Peripheral Clock Masking*.

Each EVSYS channel has a dedicated generic clock (GCLK\_EVSYS\_CHANNEL\_n). These are used for event detection and propagation for each channel. These clocks must be configured and enabled in the generic clock controller before using the EVSYS. Refer to *GCLK* - *Generic Clock Controller* for details.

#### **Related Links**

Peripheral Clock Masking GCLK - Generic Clock Controller

# 24.5.4 DMA

Not applicable.

#### 24.5.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. Using the EVSYS interrupts requires the interrupt controller to be configured first. Refer to *Nested Vector Interrupt Controller* for details.

# **Related Links**

Nested Vector Interrupt Controller

#### 24.5.6 Events

Not applicable.

# 24.5.7 Debug Operation

When the CPU is halted in debug mode, this peripheral will continue normal operation. If the peripheral is configured to require periodical service by the CPU through interrupts or similar, improper operation or data loss may result during debugging. This peripheral can be forced to halt operation during debugging.

## **Related Links**

PORT: IO Pin Controller

## 27.5.2 Power Management

This peripheral can continue to operate in any sleep mode where its source clock is running. The interrupts can wake up the device from sleep modes.

#### **Related Links**

PM - Power Manager

## 27.5.3 Clocks

The SERCOM bus clock (CLK\_SERCOMx\_APB) can be enabled and disabled in the Power Manager. Refer to *Perhipharal Clock Masking* for details and default status of this clock.

A generic clock (GCLK\_SERCOMx\_CORE) is required to clock the SPI. This clock must be configured and enabled in the Generic Clock Controller before using the SPI.

This generic clock is asynchronous to the bus clock (CLK\_SERCOMx\_APB). Therefore, writes to certain registers will require synchronization to the clock domains.

#### **Related Links**

GCLK - Generic Clock Controller Peripheral Clock Masking Synchronization

# 27.5.4 DMA

The DMA request lines are connected to the DMA Controller (DMAC). In order to use DMA requests with this peripheral the DMAC must be configured first. Refer to *DMAC – Direct Memory Access Controller* for details.

## **Related Links**

DMAC - Direct Memory Access Controller

# 27.5.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. In order to use interrupt requests of this peripheral, the Interrupt Controller (NVIC) must be configured first. Refer to *Nested Vector Interrupt Controller* for details.

#### **Related Links**

Nested Vector Interrupt Controller

#### 27.5.6 Events

Not applicable.

# 27.5.7 Debug Operation

When the CPU is halted in debug mode, this peripheral will continue normal operation. If the peripheral is configured to require periodical service by the CPU through interrupts or similar, improper operation or data loss may result during debugging. This peripheral can be forced to halt operation during debugging - refer to the Debug Control (DBGCTRL) register for details.

#### 27.5.8 Register Access Protection

Registers with write-access can be write-protected optionally by the peripheral access controller (PAC).

PAC Write-Protection is not available for the following registers:

| Value | Description                                                       |

|-------|-------------------------------------------------------------------|

| 0x0   | Standard-mode (Sm) up to 100 kHz and Fast-mode (Fm) up to 400 kHz |

| 0x1   | Fast-mode Plus (Fm+) up to 1 MHz                                  |

| 0x2   | High-speed mode (Hs-mode) up to 3.4 MHz                           |

| 0x3   | Reserved                                                          |

## Bit 23 – SEXTTOEN: Slave SCL Low Extend Time-Out

This bit enables the slave SCL low extend time-out. If SCL is cumulatively held low for greater than 25ms from the initial START to a STOP, the slave will release its clock hold if enabled and reset the internal state machine. Any interrupt flags set at the time of time-out will remain set. If the address was recognized, PREC will be set when a STOP is received.

This bit is not synchronized.

| Value | Description       |

|-------|-------------------|

| 0     | Time-out disabled |

| 1     | Time-out enabled  |

# Bits 21:20 - SDAHOLD[1:0]: SDA Hold Time

These bits define the SDA hold time with respect to the negative edge of SCL.

These bits are not synchronized.

| Value | Name | Description         |

|-------|------|---------------------|

| 0x0   | DIS  | Disabled            |

| 0x1   | 75   | 50-100ns hold time  |

| 0x2   | 450  | 300-600ns hold time |

| 0x3   | 600  | 400-800ns hold time |

# Bit 16 – PINOUT: Pin Usage

This bit sets the pin usage to either two- or four-wire operation:

This bit is not synchronized.

| Value | Description               |

|-------|---------------------------|

| 0     | 4-wire operation disabled |

| 1     | 4-wire operation enabled  |

# Bit 7 – RUNSTDBY: Run in Standby

This bit defines the functionality in standby sleep mode.

This bit is not synchronized.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | Disabled – All reception is dropped. |

| 1     | Wake on address match, if enabled.   |

# Bits 4:2 – MODE[2:0]: Operating Mode

These bits must be written to 0x04 to select the I<sup>2</sup>C slave serial communication interface of the SERCOM.

These bits are not synchronized.

# Bit 1 – ENABLE: Enable

Due to synchronization, there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRL.ENABLE will read back immediately and the Enable Synchronization Writing a '0' to this bit has no effect.

| Value | Description            |

|-------|------------------------|

| 0     | No bus error detected. |

| 1     | Bus error detected.    |

## 28.8.7 Synchronization Busy

|        | Name:<br>Offset:<br>Reset: | SYNCBUSY<br>0x1C<br>0x00000000 |    |    |    |    |        |       |

|--------|----------------------------|--------------------------------|----|----|----|----|--------|-------|

| Bit    | 31                         | 30                             | 29 | 28 | 27 | 26 | 25     | 24    |

|        |                            |                                |    |    |    |    |        |       |

| Access |                            |                                |    |    |    |    |        |       |

| Reset  |                            |                                |    |    |    |    |        |       |

|        |                            |                                |    |    |    |    |        |       |

| Bit    | 23                         | 22                             | 21 | 20 | 19 | 18 | 17     | 16    |

|        |                            |                                |    |    |    |    |        |       |

| Access |                            |                                |    |    |    |    |        |       |

| Reset  |                            |                                |    |    |    |    |        |       |

|        |                            |                                |    |    |    |    |        |       |

| Bit    | 15                         | 14                             | 13 | 12 | 11 | 10 | 9      | 8     |

|        |                            |                                |    |    |    |    |        |       |

| Access |                            |                                |    |    |    |    |        |       |

| Reset  |                            |                                |    |    |    |    |        |       |

|        |                            |                                |    |    |    |    |        |       |

| Bit    | 7                          | 6                              | 5  | 4  | 3  | 2  | 1      | 0     |

|        |                            |                                |    |    |    |    | ENABLE | SWRST |

| Access |                            |                                |    |    |    |    | R      | R     |

| Reset  |                            |                                |    |    |    |    | 0      | 0     |

#### Bit 1 – ENABLE: SERCOM Enable Synchronization Busy

Enabling and disabling the SERCOM (CTRLA.ENABLE) requires synchronization. When written, the SYNCBUSY.ENABLE bit will be set until synchronization is complete.

Writes to any register (except for CTRLA.SWRST) while enable synchronization is on-going will be discarded and an APB error will be generated.

| Value | Description                         |  |  |

|-------|-------------------------------------|--|--|

| 0     | Enable synchronization is not busy. |  |  |

| 1     | Enable synchronization is busy.     |  |  |

#### Bit 0 – SWRST: Software Reset Synchronization Busy

Resetting the SERCOM (CTRLA.SWRST) requires synchronization. When written, the SYNCBUSY.SWRST bit will be set until synchronization is complete.

Writes to any register while synchronization is on-going will be discarded and an APB error will be generated.

| Value | Description                        |

|-------|------------------------------------|

| 0     | SWRST synchronization is not busy. |

| 1     | SWRST synchronization is busy.     |

| Value | Description        |

|-------|--------------------|

| 0     | Time-out disabled. |

| 1     | Time-out enabled.  |

#### Bits 29:28 – INACTOUT[1:0]: Inactive Time-Out

If the inactive bus time-out is enabled and the bus is inactive for longer than the time-out setting, the bus state logic will be set to idle. An inactive bus arise when either an  $I^2C$  master or slave is holding the SCL low.

Enabling this option is necessary for SMBus compatibility, but can also be used in a non-SMBus set-up.

Calculated time-out periods are based on a 100kHz baud rate.

These bits are not synchronized.

| Value | Name  | Description                          |  |  |

|-------|-------|--------------------------------------|--|--|

| 0x0   | DIS   | isabled                              |  |  |

| 0x1   | 55US  | 5-6 SCL cycle time-out (50-60µs)     |  |  |

| 0x2   | 105US | 10-11 SCL cycle time-out (100-110µs) |  |  |

| 0x3   | 205US | 20-21 SCL cycle time-out (200-210µs) |  |  |

## Bit 27 – SCLSM: SCL Clock Stretch Mode

This bit controls when SCL will be stretched for software interaction.

This bit is not synchronized.

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | SCL stretch according to Figure 28-4.        |

| 1     | SCL stretch only after ACK bit, Figure 28-5. |

#### Bits 25:24 – SPEED[1:0]: Transfer Speed

These bits define bus speed.

These bits are not synchronized.

| Value | Description                                                       |

|-------|-------------------------------------------------------------------|

| 0x0   | Standard-mode (Sm) up to 100 kHz and Fast-mode (Fm) up to 400 kHz |

| 0x1   | Fast-mode Plus (Fm+) up to 1 MHz                                  |

| 0x2   | High-speed mode (Hs-mode) up to 3.4 MHz                           |

| 0x3   | Reserved                                                          |

## Bit 23 – SEXTTOEN: Slave SCL Low Extend Time-Out

This bit enables the slave SCL low extend time-out. If SCL is cumulatively held low for greater than 25ms from the initial START to a STOP, the master will release its clock hold if enabled, and complete the current transaction. A STOP will automatically be transmitted.

SB or MB will be set as normal, but CLKHOLD will be release. The MEXTTOUT and BUSERR status bits will be set.

This bit is not synchronized.

| Value | Description       |

|-------|-------------------|

| 0     | Time-out disabled |

| 1     | Time-out enabled  |

# Bit 8 – FSSEL: Frame Sync Select

This field selects the source of the Frame Sync n.

| FSSEL | Name   | Description                                           |  |

|-------|--------|-------------------------------------------------------|--|

| 0x0   | SCKDIV | Divided Serial Clock n is used as Frame Sync n source |  |

| 0x1   | FSPIN  | FSn input pin is used as Frame Sync n source          |  |

# Bit 7 – BITDELAY: Data Delay from Frame Sync

| BITDELAY | Name | Description                  |

|----------|------|------------------------------|

| 0x0      | LJ   | Left Justified (0 Bit Delay) |

| 0x1      | I2S  | I2S (1 Bit Delay)            |

## Bits 6:5 – FSWIDTH[1:0]: Frame Sync Width

This field selects the duration of the Frame Sync output pulses.

When not in Burst mode, the Clock unit n operates in continuous mode when enabled, with periodic Frame Sync pulses and Data samples.

In Burst mode, a single Data transfer starts at each Frame Sync pulse; these pulses are 1-bit wide and occur only when a Data transfer is requested. Note that the compact stereo modes (16C and 8C) are not supported in the Burst mode.

| FSWIDTH[1:0] | Name  | Description                                                                                                                   |

|--------------|-------|-------------------------------------------------------------------------------------------------------------------------------|

| 0x0          | SLOT  | Frame Sync Pulse is 1 Slot wide (default for I2S protocol)                                                                    |

| 0x1          | HALF  | Frame Sync Pulse is half a Frame wide                                                                                         |

| 0x2          | BIT   | Frame Sync Pulse is 1 Bit wide                                                                                                |

| 0x3          | BURST | Clock Unit n operates in Burst mode, with a 1-bit wide Frame Sync pulse per Data sample, only when Data transfer is requested |

# Bits 4:2 – NBSLOTS[2:0]: Number of Slots in Frame

Each Frame for Clock Unit n is composed of (NBSLOTS + 1) Slots.

#### Bits 1:0 – SLOTSIZE[1:0]: Slot Size

Each Slot for Clock Unit n is composed of a number of bits specified by SLOTSIZE.

| SLOTSIZE[1:0] | Name | Description                  |

|---------------|------|------------------------------|

| 0x0           | 8    | 8-bit Slot for Clock Unit n  |

| 0x1           | 16   | 16-bit Slot for Clock Unit n |

| 0x2           | 24   | 24-bit Slot for Clock Unit n |

| 0x3           | 32   | 32-bit Slot for Clock Unit n |

#### 29.9.3 Interrupt Enable Clear

| Name:   | INTENCLR |

|---------|----------|

| Offset: | 0x0C     |

# 30.5.6 Events

The events of this peripheral are connected to the Event System.

#### **Related Links**

EVSYS – Event System

## 30.5.7 Debug Operation

When the CPU is halted in debug mode, this peripheral will halt normal operation. This peripheral can be forced to continue operation during debugging - refer to the Debug Control (DBGCTRL) register for details.

# 30.5.8 Register Access Protection

Registers with write-access can be optionally write-protected by the Peripheral Access Controller (PAC), except the following:

- Interrupt Flag register (INTFLAG)

- Status register (STATUS)

- Read Request register (READREQ)

- Count register (COUNT)

- Period register (PER)

- Compare/Capture Value registers (CCx)

**Note:** Optional write-protection is indicated by the "PAC Write-Protection" property in the register description.

When the CPU is halted in debug mode, all write-protection is automatically disabled. Write-protection does not apply for accesses through an external debugger.

#### 30.5.9 Analog Connections

Not applicable.

# 30.6 Functional Description

## 30.6.1 Principle of Operation

The following definitions are used throughout the documentation:

#### Table 30-1. Timer/Counter Definitions

| Name   | Description                                                                                                                                                                                                                                                   |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TOP    | The counter reaches TOP when it becomes equal to the highest value in the count sequence. The TOP value can be the same as Period (PER) or the Compare Channel 0 (CC0) register value depending on the waveform generator mode in Waveform Output Operations. |

| ZERO   | The counter is ZERO when it contains all zeroes                                                                                                                                                                                                               |

| MAX    | The counter reaches MAX when it contains all ones                                                                                                                                                                                                             |

| UPDATE | The timer/counter signals an update when it reaches ZERO or TOP, depending on the direction settings.                                                                                                                                                         |

| Timer  | The timer/counter clock control is handled by an internal source                                                                                                                                                                                              |

| Bit    | 31      | 30         | 29           | 28    | 27             | 26      | 25   | 24    |

|--------|---------|------------|--------------|-------|----------------|---------|------|-------|

|        |         |            |              |       | FILTERVAL[3:0] |         |      |       |

| Access |         |            |              |       | R/W            | R/W     | R/W  | R/W   |

| Reset  |         |            |              |       | 0              | 0       | 0    | 0     |

|        |         |            |              |       |                |         |      |       |

| Bit    | 23      | 22         | 21           | 20    | 19             | 18      | 17   | 16    |

|        |         |            |              | BLANK | VAL[7:0]       |         |      |       |

| Access | R/W     | R/W        | R/W          | R/W   | R/W            | R/W     | R/W  | R/W   |

| Reset  | 0       | 0          | 0            | 0     | 0              | 0       | 0    | 0     |

|        |         |            |              |       |                |         |      |       |

| Bit    | 15      | 14         | 13           | 12    | 11             | 10      | 9    | 8     |

|        |         |            | CAPTURE[2:0] |       | CHSE           | EL[1:0] | HALT | [1:0] |

| Access |         | R/W        | R/W          | R/W   | R/W            | R/W     | R/W  | R/W   |

| Reset  |         | 0          | 0            | 0     | 0              | 0       | 0    | 0     |

|        |         |            |              |       |                |         |      |       |

| Bit    | 7       | 6          | 5            | 4     | 3              | 2       | 1    | 0     |

|        | RESTART | BLANK[1:0] |              | QUAL  | KEEP           |         | SRC  | [1:0] |

| Access | R/W     | R/W        | R/W          | R/W   | R/W            |         | R/W  | R/W   |

| Reset  | 0       | 0          | 0            | 0     | 0              |         | 0    | 0     |

# Bits 27:24 – FILTERVAL[3:0]: Recoverable Fault n Filter Value