#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                               |

| Data Converters            | A/D 20x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-QFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd21j15b-mft |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 17. | SYSCTRL – System Controller            | 150 |

|-----|----------------------------------------|-----|

|     | 17.1. Overview                         |     |

|     | 17.2. Features                         |     |

|     | 17.3. Block Diagram                    |     |

|     | 17.4. Signal Description               |     |

|     | 17.5. Product Dependencies             |     |

|     | 17.6. Functional Description           |     |

|     | 17.7. Register Summary                 | 170 |

|     | 17.8. Register Description             |     |

| 18. | WDT – Watchdog Timer                   |     |

|     | 18.1. Overview                         |     |

|     | 18.2. Features                         |     |

|     | 18.3. Block Diagram                    |     |

|     | 18.4. Signal Description               |     |

|     | 18.5. Product Dependencies             |     |

|     | 18.6. Functional Description           | 207 |

|     | 18.7. Register Summary                 | 212 |

|     | 18.8. Register Description             | 212 |

| 19. | RTC – Real-Time Counter                | 218 |

|     | 19.1. Overview                         |     |

|     | 19.2. Features                         |     |

|     | 19.3. Block Diagram                    | 219 |

|     | 19.4. Signal Description               |     |

|     | 19.5. Product Dependencies             |     |

|     | 19.6. Functional Description           | 221 |

|     | 19.7. Register Summary                 |     |

|     | 19.8. Register Description             |     |

| 20. | DMAC – Direct Memory Access Controller |     |

|     | 20.1. Overview                         | 252 |

|     | 20.2. Features                         |     |

|     | 20.3. Block Diagram                    |     |

|     | 20.4. Signal Description               |     |

|     | 20.5. Product Dependencies             |     |

|     | 20.6. Functional Description           |     |

|     | 20.7. Register Summary                 |     |

|     | 20.8. Register Description             |     |

|     | 20.9. Register Summary - SRAM          |     |

|     | 20.10. Register Description - SRAM     |     |

| 21. | EIC – External Interrupt Controller    |     |

|     | 21.1. Overview                         |     |

|     | 21.2. Features                         |     |

|     | 21.3. Block Diagram                    |     |

|     | 21.4. Signal Description               |     |

|     | 21.5. Product Dependencies             |     |

- Writing a peripheral core register

- Writing an APB register

- Reading a read-synchronized peripheral core register

APB registers can be read while the enable write-synchronization is ongoing without causing the peripheral bus to stall.

#### 14.3.1.7 Software Reset Write-Synchronization

Writing a '1' to the Software Reset bit in CTRL (CTRL.SWRST) will also trigger write-synchronization and set STATUS.SYNCBUSY. When writing a '1' to the CTRL.SWRST bit it will immediately read as '1'. CTRL.SWRST and STATUS.SYNCBUSY will be cleared by hardware when the peripheral has been reset. Writing a zero to the CTRL.SWRST bit has no effect. The Synchronisation Ready interrupt (if available) cannot be used for Software Reset write-synchronization.

When the software reset is in progress (STATUS.SYNCBUSY and CTRL.SWRST are '1'), attempt to do any of the following will cause the peripheral bus to stall until the Software Reset synchronization and the reset is complete:

- Writing a peripheral core register

- Writing an APB register

- Reading a read-synchronized register

APB registers can be read while the software reset is being write-synchronized without causing the peripheral bus to stall.

#### 14.3.1.8 Synchronization Delay

The synchronization will delay write and read accesses by a certain amount. This delay *D* is within the range of:

$$5 \times P_{\text{GCLK}} + 2 \times P_{\text{APB}} < D < 6 \times P_{\text{GCLK}} + 3 \times P_{\text{APB}}$$

Where  $P_{\text{GCLK}}$  is the period of the generic clock and  $P_{\text{APB}}$  is the period of the peripheral bus clock. A normal peripheral bus register access duration is  $2 \times P_{\text{APB}}$ .

#### 14.3.2 Distributed Synchronizer Register Synchronization

#### 14.3.2.1 Overview

All peripherals are composed of one digital bus interface connected to the APB or AHB bus and running from a corresponding clock in the Main Clock domain, and one peripheral core running from the peripheral Generic Clock (GCLK).

Communication between these clock domains must be synchronized. This mechanism is implemented in hardware, so the synchronization process takes place even if the peripheral generic clock is running from the same clock source and on the same frequency as the bus interface.

All registers in the bus interface are accessible without synchronization. All registers in the peripheral core are synchronized when written. Some registers in the peripheral core are synchronized when read. Registers that need synchronization has this denoted in each individual register description.

#### 14.3.2.2 General Write synchronization

Write-Synchronization is triggered by writing to a register in the peripheral clock domain. The respective bit in the Synchronization Busy register (SYNCBUSY) will be set when the write-synchronization starts and cleared when the write-synchronization is complete. Refer to Synchronization Delay for details on the synchronization delay.

### 17.8.7 32kHz Internal Oscillator (OSC32K) Control

OSC32K

Name:

| Offset: 0x18<br>Reset: 0x003F0080<br>Property: Write-Protected |          |          |     |         |            |       |              |     |

|----------------------------------------------------------------|----------|----------|-----|---------|------------|-------|--------------|-----|

|                                                                |          |          |     |         |            |       |              |     |

| Bit                                                            | 31       | 30       | 29  | 28      | 27         | 26    | 25           | 24  |

|                                                                |          |          |     |         |            |       |              |     |

| Access                                                         |          |          |     |         |            |       |              |     |

| Reset                                                          |          |          |     |         |            |       |              |     |

|                                                                |          |          |     |         |            |       |              |     |

| Bit                                                            | 23       | 22       | 21  | 20      | 19         | 18    | 17           | 16  |

|                                                                |          |          |     |         | CALIB[6:0] |       |              |     |

| Access                                                         |          | R/W      | R/W | R/W     | R/W        | R/W   | R/W          | R/W |

| Reset                                                          |          | 0        | 1   | 1       | 1          | 1     | 1            | 1   |

|                                                                |          |          |     |         |            |       |              |     |

| Bit                                                            | 15       | 14       | 13  | 12      | 11         | 10    | 9            | 8   |

|                                                                |          |          |     | WRTLOCK |            |       | STARTUP[2:0] |     |

| Access                                                         |          |          |     | R/W     |            | R/W   | R/W          | R/W |

| Reset                                                          |          |          |     | 0       |            | 0     | 0            | 0   |

|                                                                |          |          |     |         |            |       |              |     |

| Bit                                                            | 7        | 6        | 5   | 4       | 3          | 2     | 1            | 0   |

|                                                                | ONDEMAND | RUNSTDBY |     |         |            | EN32K | ENABLE       |     |

| Access                                                         | R/W      | R/W      |     |         |            | R/W   | R/W          |     |

| Reset                                                          | 1        | 0        |     |         |            | 0     | 0            |     |

|                                                                |          |          |     |         |            |       |              |     |

## Bits 22:16 – CALIB[6:0]: Oscillator Calibration

These bits control the oscillator calibration.

This value must be written by the user.

Factory calibration values can be loaded from the non-volatile memory.

#### Bit 12 – WRTLOCK: Write Lock

This bit locks the OSC32K register for future writes to fix the OSC32K configuration.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | The OSC32K configuration is not locked. |

| 1     | The OSC32K configuration is locked.     |

#### Bits 10:8 – STARTUP[2:0]: Oscillator Start-Up Time

These bits select start-up time for the oscillator.

The OSCULP32K oscillator is used as input clock to the startup counter.

## 32-bit ARM-Based Microcontrollers

| Value | Description                                                       |

|-------|-------------------------------------------------------------------|

| 0     | Temperature sensor is disabled.                                   |

| 1     | Temperature sensor is enabled and routed to an ADC input channel. |

#### 17.8.17 DPLL Control A

Name:DPLLCTRLAOffset:0x44Reset:0x80Property:Write-Protected

| Bit    | 7        | 6        | 5 | 4 | 3 | 2 | 1      | 0 |

|--------|----------|----------|---|---|---|---|--------|---|

|        | ONDEMAND | RUNSTDBY |   |   |   |   | ENABLE |   |

| Access | R/W      | R/W      |   |   |   |   | R/W    |   |

| Reset  | 1        | 0        |   |   |   |   | 0      |   |

#### Bit 7 – ONDEMAND: On Demand Clock Activation

| Value | Description                                                                                                                                                                                       |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The DPLL is always on when enabled.                                                                                                                                                               |

| 1     | The DPLL is activated only when a peripheral request the DPLL as a source clock. The DPLLCTRLA.ENABLE bit must be one to validate that operation, otherwise the peripheral request has no effect. |

#### Bit 6 – RUNSTDBY: Run in Standby

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | The DPLL is disabled in standby sleep mode.    |

| 1     | The DPLL is not stopped in standby sleep mode. |

#### Bit 1 – ENABLE: DPLL Enable

The software operation of enabling or disabling the DPLL takes a few clock cycles, so check the DPLLSTATUS.ENABLE status bit to identify when the DPLL is successfully activated or disabled.

| Value | Description           |

|-------|-----------------------|

| 0     | The DPLL is disabled. |

| 1     | The DPLL is enabled.  |

#### 17.8.18 DPLL Ratio Control

| Name:     | DPLLRATIO       |

|-----------|-----------------|

| Offset:   | 0x48            |

| Reset:    | 0x00000000      |

| Property: | Write-Protected |

| Bit    | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

|--------|----|----|----|----|----|----|----|----|

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

WDT to ensure that the time-out periods used are valid for all devices. For more information on ULP oscillator accuracy, consult the *Ultra Low Power Internal 32kHz RC Oscillator (OSCULP32K) Characteristics*.

GCLK\_WDT can also be clocked from other sources if a more accurate clock is needed, but at the cost of higher power consumption.

#### **Related Links**

PM – Power ManagerGCLK - Generic Clock Controller32kHz Ultra Low Power Internal Oscillator (OSCULP32K) Operation

#### 18.5.4 DMA

Not applicable.

#### 18.5.5 Interrupts

The interrupt request line is connected to the interrupt controller. Using the WDT interrupt(s) requires the interrupt controller to be configured first.

#### **Related Links**

Nested Vector Interrupt Controller

#### 18.5.6 Events

Not applicable.

#### 18.5.7 Debug Operation

When the CPU is halted in debug mode the WDT will halt normal operation.

#### 18.5.8 Register Access Protection

Registers with write-access can be optionally write-protected by the Peripheral Access Controller (PAC), except the following:

Interrupt Flag Status and Clear register (INTFLAG)

**Note:** Optional write-protection is indicated by the "PAC Write-Protection" property in the register description.

#### 18.5.9 Analog Connections

Not applicable.

## 18.6 Functional Description

#### 18.6.1 Principle of Operation

The Watchdog Timer (WDT) is a system for monitoring correct program operation, making it possible to recover from error situations such as runaway code, by issuing a Reset. When enabled, the WDT is a constantly running timer that is configured to a predefined time-out period. Before the end of the time-out period, the WDT should be set back, or else, a system Reset is issued.

The WDT has two modes of operation, Normal mode and Window mode. Both modes offer the option of Early Warning interrupt generation. The description for each of the basic modes is given below. The settings in the Control register (CTRL) and the Interrupt Enable register (handled by INTENCLR/SET) determine the mode of operation:

| Offset:          | 0x7  |

|------------------|------|

| Reset:           | 0x00 |

| <b>Property:</b> | _    |

| Bit    | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|----------|---|---|---|---|---|---|---|

|        | SYNCBUSY |   |   |   |   |   |   |   |

| Access | R        |   |   |   |   |   |   |   |

| Reset  | 0        |   |   |   |   |   |   |   |

#### Bit 7 – SYNCBUSY: Synchronization Busy

This bit is cleared when the synchronization of registers between clock domains is complete.

This bit is set when the synchronization of registers between clock domains is started.

#### 18.8.8 Clear

Name:CLEAROffset:0x8Reset:0x00Property:Write-Protected, Write-Synchronized

| Bit    | 7 | 6 | 5 | 4    | 3      | 2 | 1 | 0 |

|--------|---|---|---|------|--------|---|---|---|

|        |   |   |   | CLEA | R[7:0] |   |   |   |

| Access | W | W | W | W    | W      | W | W | W |

| Reset  | 0 | 0 | 0 | 0    | 0      | 0 | 0 | 0 |

#### Bits 7:0 – CLEAR[7:0]: Watchdog Clear

Writing 0xA5 to this register will clear the Watchdog Timer and the watchdog time-out period is restarted. Writing any other value will issue an immediate system reset.

#### Bit 6 – CLKREP: Clock Representation

This bit is valid only in Mode 2 and determines how the hours are represented in the Clock Value (CLOCK) register. This bit can be written only when the peripheral is disabled.

This bit is not synchronized.

| Value | Description     |

|-------|-----------------|

| 0     | 24 Hour         |

| 1     | 12 Hour (AM/PM) |

#### Bits 3:2 - MODE[1:0]: Operating Mode

These bits define the operating mode of the RTC.

These bits are not synchronized.

| MODE[1:0] | Name    | Description            |

|-----------|---------|------------------------|

| 0x0       | COUNT32 | Mode 0: 32-bit Counter |

| 0x1       | COUNT16 | Mode 1: 16-bit Counter |

| 0x2       | CLOCK   | Mode 2: Clock/Calendar |

| 0x3       |         | Reserved               |

#### Bit 1 – ENABLE: Enable

Due to synchronization, there is delay from writing CTRL.ENABLE until the peripheral is enabled/ disabled. The value written to CTRL.ENABLE will read back immediately, and the Synchronization Busy bit in the Status register (STATUS.SYNCBUSY) will be set. STATUS.SYNCBUSY will be cleared when the operation is complete.

This bit is not enable-protected.

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | The peripheral is disabled or being disabled. |

| 1     | The peripheral is enabled or being enabled.   |

#### Bit 0 – SWRST: Software Reset

Writing a zero to this bit has no effect.

Writing a one to this bit resets all registers in the RTC, except DBGCTRL, to their initial state, and the RTC will be disabled.

Writing a one to CTRL.SWRST will always take precedence, meaning that all other writes in the same write-operation will be discarded.

Due to synchronization, there is a delay from writing CTRL.SWRST until the reset is complete. CTRL.SWRST and STATUS.SYNCBUSY will both be cleared when the reset is complete.

This bit is not enable-protected.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

#### 19.8.4 Read Request

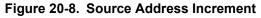

Increment Step Size bit group in the Block Transfer Control register (BTCTRL.STEPSIZE). If BTCTRL.STEPSEL=0, the step size for the source incrementation will be the size of one beat.

When source address incrementation is configured (BTCTRL.SRCINC=1), SRCADDR is calculated as follows:

If **BTCTRL**.STEPSEL=1:

$SRCADDR = SRCADDR_{START} + BTCNT \cdot (BEATSIZE + 1) \cdot 2^{STEPSIZE}$

If **BTCTRL**.STEPSEL=0:

$SRCADDR = SRCADDR_{START} + BTCNT \cdot (BEATSIZE + 1)$

- SRCADDR<sub>START</sub> is the source address of the first beat transfer in the block transfer

- BTCNT is the initial number of beats remaining in the block transfer

- BEATSIZE is the configured number of bytes in a beat

- STEPSIZE is the configured number of beats for each incrementation

The following figure shows an example where DMA channel 0 is configured to increment the source address by one beat after each beat transfer (BTCTRL.SRCINC=1), and DMA channel 1 is configured to increment the source address by two beats (BTCTRL.SRCINC=1, BTCTRL.STEPSEL=1, and BTCTRL.STEPSIZE=0x1). As the destination address for both channels are peripherals, destination incrementation is disabled (BTCTRL.DSTINC=0).

Incrementation for the destination address of a block transfer is enabled by setting the Destination Address Incrementation Enable bit in the Block Transfer Control register (BTCTRL.DSTINC=1). The step size of the incrementation is configurable by clearing BTCTRL.STEPSEL=0 and writing BTCTRL.STEPSIZE to the desired step size. If BTCTRL.STEPSEL=1, the step size for the destination incrementation will be the size of one beat.

When the destination address incrementation is configured (BTCTRL.DSTINC=1), SRCADDR must be set and calculated as follows:

| $DSTADDR = DSTADDR_{START} + BTCNT \bullet (BEATSIZE + 1) \bullet 2^{STEPSIZE}$ | where BTCTRL.STEPSEL is zero |

|---------------------------------------------------------------------------------|------------------------------|

| $DSTADDR = DSTADDR_{START} + BTCNT \bullet (BEATSIZE + 1)$                      | where BTCTRL.STEPSEL is one  |

- DSTADDR<sub>START</sub> is the destination address of the first beat transfer in the block transfer

- BTCNT is the initial number of beats remaining in the block transfer

**CRC on** CRC-16 or CRC-32 calculations can be performed on data passing through any DMA

DMA channel. Once a DMA channel is selected as the source, the CRC engine will continuously generate the CRC on the data passing through the DMA channel. The checksum is available for readout once the DMA transaction is completed or aborted. A CRC can also be generated on SRAM, Flash, or I/O memory by passing these data through a DMA channel. If the latter is done, the destination register for the DMA data can be the data input (CRCDATAIN) register in the CRC engine.

**CRC using the I/O** Before using the CRC engine with the I/O interface, the application must set the CRC Beat Size bits in the CRC Control register (CRCCTRL.CRCBEATSIZE). 8/16/32-bit bus transfer type can be selected.

CRC can be performed on any data by loading them into the CRC engine using the CPU and writing the data to the CRCDATAIN register. Using this method, an arbitrary number of bytes can be written to the register by the CPU, and CRC is done continuously for each byte. This means if a 32-bit data is written to the CRCDATAIN register the CRC engine takes four cycles to calculate the CRC. The CRC complete is signaled by a set CRCBUSY bit in the CRCSTATUS register. New data can be written only when CRCBUSY flag is not set.

#### 20.6.4 DMA Operation

Not applicable.

## 20.6.5 Interrupts

The DMAC channels have the following interrupt sources:

- Transfer Complete (TCMPL): Indicates that a block transfer is completed on the corresponding channel. Refer to Data Transmission for details.

- Transfer Error (TERR): Indicates that a bus error has occurred during a burst transfer, or that an invalid descriptor has been fetched. Refer to Error Handling for details.

- Channel Suspend (SUSP): Indicates that the corresponding channel has been suspended. Refer to Channel Suspend and Data Transmission for details.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Channel Interrupt Flag Status and Clear (CHINTFLAG) register is set when the interrupt condition occurs. Each interrupt can be individually enabled by setting the corresponding bit in the Channel Interrupt Enable Set register (CHINTENSET=1), and disabled by setting the corresponding bit in the Channel Interrupt Enable Clear register (CHINTENCLR=1).

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, the DMAC is reset or the corresponding DMA channel is reset. See CHINTFLAG for details on how to clear interrupt flags. All interrupt requests are ORed together on system level to generate one combined interrupt request to the NVIC.

The user must read the Channel Interrupt Status (INTSTATUS) register to identify the channels with pending interrupts and must read the Channel Interrupt Flag Status and Clear (CHINTFLAG) register to determine which interrupt condition is present for the corresponding channel. It is also possible to read the Interrupt Pending register (INTPEND), which provides the lowest channel number with pending interrupt and the respective interrupt flags.

Note: Interrupts must be globally enabled for interrupt requests to be generated.

#### **Related Links**

Nested Vector Interrupt Controller

- 1. Enable CLK\_EIC\_APB

- 2. If edge detection or filtering is required, GCLK\_EIC must be enabled

- 3. Write the EIC configuration registers (EVCTRL, WAKEUP, CONFIGy)

- 4. Enable the EIC

To use NMI, GCLK\_EIC must be enabled after EIC configuration (NMICTRL).

#### 21.6.2.2 Enabling, Disabling and Resetting

The EIC is enabled by writing a '1' the Enable bit in the Control register (CTRL.ENABLE). The EIC is disabled by writing CTRL.ENABLE to '0'.

The EIC is reset by setting the Software Reset bit in the Control register (CTRL.SWRST). All registers in the EIC will be reset to their initial state, and the EIC will be disabled.

Refer to the CTRL register description for details.

#### 21.6.3 External Pin Processing

Each external pin can be configured to generate an interrupt/event on edge detection (rising, falling or both edges) or level detection (high or low). The sense of external interrupt pins is configured by writing the Input Sense x bits in the Config n register (CONFIGn.SENSEx). The corresponding interrupt flag (INTFLAG.EXTINT[x]) in the Interrupt Flag Status and Clear register (INTFLAG) is set when the interrupt condition is met.

When the interrupt flag has been cleared in edge-sensitive mode, INTFLAG.EXTINT[x] will only be set if a new interrupt condition is met. In level-sensitive mode, when interrupt has been cleared, INTFLAG.EXTINT[x] will be set immediately if the EXTINTx pin still matches the interrupt condition.

Each external pin can be filtered by a majority vote filtering, clocked by GCLK\_EIC. Filtering is enabled if bit Filter Enable x in the Configuration n register (CONFIGn.FILTENx) is written to '1'. The majority vote filter samples the external pin three times with GCLK\_EIC and outputs the value when two or more samples are equal.

| Samples [0, 1, 2] | Filter Output |

|-------------------|---------------|

| [0,0,0]           | 0             |

| [0,0,1]           | 0             |

| [0,1,0]           | 0             |

| [0,1,1]           | 1             |

| [1,0,0]           | 0             |

| [1,0,1]           | 1             |

| [1,1,0]           | 1             |

| [1,1,1]           | 1             |

### Table 21-1. Majority Vote Filter

When an external interrupt is configured for level detection, or if filtering is disabled, detection is made asynchronously, and GCLK\_EIC is not required.

If filtering or edge detection is enabled, the EIC automatically requests the GCLK\_EIC to operate (GCLK\_EIC must be enabled in the GCLK module, see *GCLK – Generic Clock Controller* for details). If level detection is enabled, GCLK\_EIC is not required, but interrupt and events can still be generated.

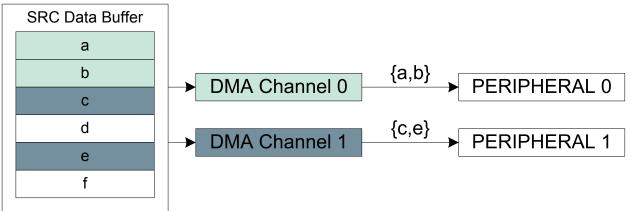

#### 23.6.1 Principle of Operation

Each PORT group of up to 32 pins is controlled by the registers in PORT, as described in the figure. These registers in PORT are duplicated for each PORT group, with increasing base addresses. The number of PORT groups may depend on the package/number of pins.

#### Figure 23-3. Overview of the peripheral functions multiplexing

The I/O pins of the device are controlled by PORT peripheral registers. Each port pin has a corresponding bit in the Data Direction (DIR) and Data Output Value (OUT) registers to enable that pin as an output and to define the output state.

The direction of each pin in a PORT group is configured by the DIR register. If a bit in DIR is set to '1', the corresponding pin is configured as an output pin. If a bit in DIR is set to '0', the corresponding pin is configured as an input pin.

When the direction is set as output, the corresponding bit in the OUT register will set the level of the pin. If bit y in OUT is written to '1', pin y is driven HIGH. If bit y in OUT is written to '0', pin y is driven LOW. Pin configuration can be set by Pin Configuration (PINCFGy) registers, with y=00, 01, ...31 representing the bit position.

The Data Input Value (IN) is set as the input value of a port pin with resynchronization to the PORT clock. To reduce power consumption, these input synchronizers are clocked only when system requires reading the input value. The value of the pin can always be read, whether the pin is configured as input or output. If the Input Enable bit in the Pin Configuration registers (PINCFGy.INEN) is '0', the input value will not be sampled.

In PORT, the Peripheral Multiplexer Enable bit in the PINCFGy register (PINCFGy.PMUXEN) can be written to '1' to enable the connection between peripheral functions and individual I/O pins. The Peripheral Multiplexing n (PMUXn) registers select the peripheral function for the corresponding pin. This will override the connection between the PORT and that I/O pin, and connect the selected peripheral signal to the particular I/O pin instead of the PORT line bundle.

#### Bit 2 – PULLEN: Pull Enable

This bit enables the internal pull-up or pull-down resistor of an I/O pin configured as an input.

| Value | Description                                                                                                           |

|-------|-----------------------------------------------------------------------------------------------------------------------|

| 0     | Internal pull resistor is disabled, and the input is in a high-impedance configuration.                               |

| 1     | Internal pull resistor is enabled, and the input is driven to a defined logic level in the absence of external input. |

#### Bit 1 – INEN: Input Enable

This bit controls the input buffer of an I/O pin configured as either an input or output.

Writing a zero to this bit disables the input buffer completely, preventing read-back of the physical pin state when the pin is configured as either an input or output.

| Value | Description                                                                                 |

|-------|---------------------------------------------------------------------------------------------|

| 0     | Input buffer for the I/O pin is disabled, and the input value will not be sampled.          |

| 1     | Input buffer for the I/O pin is enabled, and the input value will be sampled when required. |

#### Bit 0 – PMUXEN: Peripheral Multiplexer Enable

This bit enables or disables the peripheral multiplexer selection set in the Peripheral Multiplexing register (PMUXn) to enable or disable alternative peripheral control over an I/O pin direction and output drive value.

Writing a zero to this bit allows the PORT to control the pad direction via the Data Direction register (DIR) and output drive value via the Data Output Value register (OUT). The peripheral multiplexer value in PMUXn is ignored. Writing '1' to this bit enables the peripheral selection in PMUXn to control the pad. In this configuration, the physical pin state may still be read from the Data Input Value register (IN) if PINCFGn.INEN is set.

| Value | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| 0     | The peripheral multiplexer selection is disabled, and the PORT registers control the direction |

|       | and output drive value.                                                                        |

| 1     | The peripheral multiplexer selection is enabled, and the selected peripheral function controls |

|       | the direction and output drive value.                                                          |

## 25. SERCOM – Serial Communication Interface

### 25.1 Overview

There are up to six instances of the serial communication interface (SERCOM) peripheral.

A SERCOM can be configured to support a number of modes: I<sup>2</sup>C, SPI, and USART. When SERCOM is configured and enabled, all SERCOM resources will be dedicated to the selected mode.

The SERCOM serial engine consists of a transmitter and receiver, baud-rate generator and address matching functionality. It can use the internal generic clock or an external clock to operate in all sleep modes.

#### **Related Links**

SERCOM USART – SERCOM Universal Synchronous and Asynchronous Receiver and Transmitter SERCOM SPI – SERCOM Serial Peripheral Interface SERCOM I2C – SERCOM Inter-Integrated Circuit

## 25.2 Features

- Interface for configuring into one of the following:

- I<sup>2</sup>C Two-wire serial interface SMBus<sup>™</sup> compatible

- SPI Serial peripheral interface

- USART Universal synchronous and asynchronous serial receiver and transmitter

- · Single transmit buffer and double receive buffer

- Baud-rate generator

- Address match/mask logic

- Operational in all sleep modes

- Can be used with DMA

See the Related Links for full feature lists of the interface configurations.

#### **Related Links**

SERCOM USART – SERCOM Universal Synchronous and Asynchronous Receiver and Transmitter SERCOM SPI – SERCOM Serial Peripheral Interface SERCOM I2C – SERCOM Inter-Integrated Circuit 0x2: SPI slave operation

0x3: SPI master operation

These bits are not synchronized.

#### Bit 1 – ENABLE: Enable

Due to synchronization, there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRL.ENABLE will read back immediately and the Synchronization Enable Busy bit in the Synchronization Busy register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE is cleared when the operation is complete.

This bit is not enable-protected.

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | The peripheral is disabled or being disabled. |

| 1     | The peripheral is enabled or being enabled.   |

#### Bit 0 – SWRST: Software Reset

Writing '0' to this bit has no effect.

Writing '1' to this bit resets all registers in the SERCOM, except DBGCTRL, to their initial state, and the SERCOM will be disabled.

Writing "1' to CTRL.SWRST will always take precedence, meaning that all other writes in the same writeoperation will be discarded. Any register write access during the ongoing reset will result in an APB error. Reading any register will return the reset value of the register.

Due to synchronization, there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY. SWRST will both be cleared when the reset is complete.

This bit is not enable-protected.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

#### 27.8.2 Control B

Name:CTRLBOffset:0x04Reset:0x00000000Property:PAC Write-Protection, Enable-Protected

| Bit    | 31 | 30 | 29 | 28 | 27 | 26 | 25   | 24 |

|--------|----|----|----|----|----|----|------|----|

|        |    |    |    |    |    |    |      |    |

| Access |    |    |    |    |    |    |      |    |

| Reset  |    |    |    |    |    |    |      |    |

|        |    |    |    |    |    |    |      |    |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18 | 17   | 16 |

|        |    |    |    |    |    |    | RXEN |    |

| Access |    |    |    |    |    |    | R/W  |    |

| Reset  |    |    |    |    |    |    | 0    |    |

|        |    |    |    |    |    |    |      |    |

# 32-bit ARM-Based Microcontrollers

| Offset | Name     | Bit Pos. |             |

|--------|----------|----------|-------------|

| 0x30   |          | 7:0      | DATA[7:0]   |

| 0x31   | DATAm0   | 15:8     | DATA[15:8]  |

| 0x32   | DATAMU   | 23:16    | DATA[23:16] |

| 0x33   |          | 31:24    | DATA[31:24] |

| 0x34   | - DATAm1 | 7:0      | DATA[7:0]   |

| 0x35   |          | 15:8     | DATA[15:8]  |

| 0x36   |          | 23:16    | DATA[23:16] |

| 0x37   |          | 31:24    | DATA[31:24] |

## 29.9 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

#### 29.9.1 Control A

Name: CTRLA Offset: 0x00 Reset: 0x00 Property: PAC Write-Protection

| Bit    | 7 | 6 | 5      | 4      | 3     | 2     | 1      | 0     |

|--------|---|---|--------|--------|-------|-------|--------|-------|

|        |   |   | SEREN1 | SEREN0 | CKEN1 | CKEN0 | ENABLE | SWRST |

| Access |   |   | R/W    | R/W    | R/W   | R/W   | R/W    | R/W   |

| Reset  |   |   | 0      | 0      | 0     | 0     | 0      | 0     |

#### Bits 5,4 – SERENx : Serializer x Enable [x=1..0]

Writing a '0' to this bit will disable the Serializer x.

Writing a '1' to this bit will enable the Serializer x.

| Value | Description                   |

|-------|-------------------------------|

| 0     | The Serializer x is disabled. |

| 1     | The Serializer x is enabled.  |

## Bits 3,2 – CKENx : Clock Unit x Enable [x=1..0]

Writing a '0' to this bit will disable the Clock Unit x.

Writing a '1' to this bit will enable the Clock Unit x.

#### Bit 1 – ERR: Error Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Error Interrupt Enable bit, which enables the Error interrupt.

| Value | Description                      |

|-------|----------------------------------|

| 0     | The Error interrupt is disabled. |

| 1     | The Error interrupt is enabled.  |

#### Bit 0 – OVF: Overflow Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Overflow Interrupt Enable bit, which enables the Overflow interrupt request.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The Overflow interrupt is disabled. |

| 1     | The Overflow interrupt is enabled.  |

#### 30.8.10 Interrupt Flag Status and Clear

| Name:            | INTFLAG |

|------------------|---------|

| Offset:          | 0x0E    |

| Reset:           | 0x00    |

| <b>Property:</b> | -       |

| Bit    | 7 | 6 | 5   | 4   | 3       | 2 | 1   | 0   |

|--------|---|---|-----|-----|---------|---|-----|-----|

|        |   |   | MC1 | MC0 | SYNCRDY |   | ERR | OVF |

| Access |   |   | R/W | R/W | R/W     |   | R/W | R/W |

| Reset  |   |   | 0   | 0   | 0       |   | 0   | 0   |

#### Bits 5,4 – MCx: Match or Capture Channel x [x = 1..0]

This flag is set on a comparison match, or when the corresponding CCx register contains a valid capture value. This flag is set on the next CLK\_TC\_CNT cycle, and will generate an interrupt request if the corresponding Match or Capture Channel x Interrupt Enable bit in the Interrupt Enable Set register (INTENSET.MCx) is '1'.

Writing a '0' to one of these bits has no effect.

Writing a '1' to one of these bits will clear the corresponding Match or Capture Channel x interrupt flag

In capture operation, this flag is automatically cleared when CCx register is read.

#### Bit 3 – SYNCRDY: Synchronization Ready Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a one to this bit will clear the Synchronization Ready Interrupt Disable/Enable bit, which disables the Synchronization Ready interrupt.

| Value | Description                                      |

|-------|--------------------------------------------------|

| 0     | The Synchronization Ready interrupt is disabled. |

| 1     | The Synchronization Ready interrupt is enabled.  |

| Value | Description                         |

|-------|-------------------------------------|

| 0     | No Data PID Error detected.         |

| 1     | A Data PID error has been detected. |

## Bit 0 – DTGLER: Data Toggle Error

This bit defines the Data Toggle Error Status.

This bit is set when a Data Toggle Error has been detected.

| Va | lue | Description                 |

|----|-----|-----------------------------|

| 0  |     | No Data Toggle Error.       |

| 1  |     | Data Toggle Error detected. |

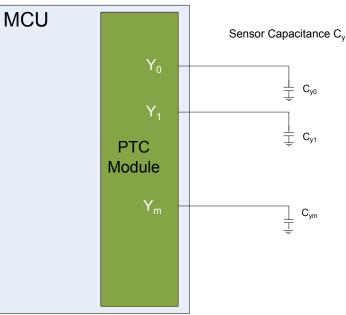

#### 36.5.1.2 Self-capacitance Sensor Arrangement

The self-capacitance sensor is connected to a single pin on the Peripheral Touch Controller through the Y electrode for receiving the signal. The sense electrode capacitance is measured by the Peripheral Touch Controller.

#### Figure 36-4. Self-capacitance Sensor Arrangement

For more information about designing the touch sensor, refer to Buttons, Sliders and Wheels Touch Sensor Design Guide on http://www.atmel.com.

#### 36.5.2 Clocks

The PTC is clocked by the GCLK\_PTC clock. The PTC operates from an asynchronous clock source and the operation is independent of the main system clock and its derivative clocks, such as the peripheral bus clock (CLK\_APB). A number of clock sources can be selected as the source for the asynchronous GCLK\_PTC. The clock source is selected by configuring the Generic Clock Selection ID in the Generic Clock Control register. For more information about selecting the clock sources, refer to *GCLK* - *Generic Clock Controller*.

The selected clock must be enabled in the Power Manager, before it can be used by the PTC. By default these clocks are disabled. The frequency range of GCLK\_PTC is 400kHz to 4MHz.

#### **Related Links**

GCLK - Generic Clock Controller PM – Power Manager

## 36.6 Functional Description

In order to access the PTC, the user must use the QTouch Composer tool to configure and link the QTouch Library firmware with the application code. QTouch Library can be used to implement buttons, sliders, wheels in a variety of combinations on a single interface.

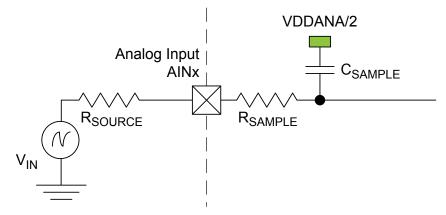

capacitor ( $C_{\text{SAMPLE}}$ ). In addition, the source resistance ( $R_{\text{SOURCE}}$ ) must be taken into account when calculating the required sample and hold time. The next figure shows the ADC input channel equivalent circuit.

## Figure 44-3. ADC Input

To achieve n bits of accuracy, the  $C_{\text{SAMPLE}}$  capacitor must be charged at least to a voltage of

$$V_{\text{CSAMPLE}} \ge V_{\text{IN}} \times (1 + -2^{-(n+1)})$$

The minimum sampling time  $t_{\text{SAMPLEHOLD}}$  for a given  $R_{\text{SOURCE}}$  can be found using this formula:

$$t_{\text{SAMPLEHOLD}} \ge \left(R_{\text{SAMPLE}} + R_{\text{SOURCE}}\right) \times \left(C_{\text{SAMPLE}}\right) \times (n+1) \times \ln(2)$$

for a 12 bits accuracy:  $t_{\text{SAMPLEHOLD}} \ge \left(R_{\text{SAMPLE}} + R_{\text{SOURCE}}\right) \times \left(C_{\text{SAMPLE}}\right) \times 9.02$

where

$$t_{\text{SAMPLEHOLD}} = \frac{1}{2 \times f_{\text{ADC}}}$$

## 44.6.5 Digital to Analog Converter (DAC) Characteristics Table 44-19. Operating Conditions<sup>(1)</sup>(Device Variant A)

| Symbol             | Parameter                        | Conditions            | Min. | Тур.               | Max.                     | Units |

|--------------------|----------------------------------|-----------------------|------|--------------------|--------------------------|-------|

| V <sub>DDANA</sub> | Analog supply voltage            |                       | 1.62 | -                  | 3.63                     | V     |

| AV <sub>REF</sub>  | External reference voltage       |                       | 1.0  | -                  | V <sub>DDANA</sub> -0.6  | V     |

|                    | Internal reference voltage 1     |                       | -    | 1                  | -                        | V     |

|                    | Internal reference voltage 2     |                       | -    | V <sub>DDANA</sub> | -                        | V     |

|                    | Linear output voltage range      |                       | 0.05 | -                  | V <sub>DDANA</sub> -0.05 | V     |

|                    | Minimum resistive load           |                       | 5    | -                  | -                        | kΩ    |

|                    | Maximum capacitance load         |                       | -    | -                  | 100                      | pF    |

| I <sub>DD</sub>    | DC supply current <sup>(2)</sup> | Voltage pump disabled | -    | 160                | 242                      | μA    |

# 32-bit ARM-Based Microcontrollers

| Symbol              | Description           | Mode                      | VDD=1.8V |      | VDD=3.3V |      |      | Units |    |

|---------------------|-----------------------|---------------------------|----------|------|----------|------|------|-------|----|

|                     |                       |                           | Min.     | Тур. | Max.     | Min. | Тур. | Мах   |    |

| t <sub>PDM2RS</sub> | Data input setup time | Master mode PDM2<br>Right | 31.9     |      |          | 20.9 |      |       | ns |

| t <sub>PDM2RH</sub> | Data input hold time  | Master mode PDM2<br>Right | -6.7     |      |          | -6.7 |      |       | ns |

- 1. All timing characteristics given for 15pF capacitive load.

- 2. These values are based on simulations and not covered by test limits in production.

- 3. See I/O Pin Characteristics.

## Table 44-52. I2S Timing Characteristics and Requirements (Device Variant B)

| Name                                            | Description                         | Mode                                                                      | VDD=1.8V |      |      | VDD=3.3V |      |      | Units |

|-------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------|----------|------|------|----------|------|------|-------|

|                                                 |                                     |                                                                           | Min.     | Тур. | Max. | Min.     | Тур. | Max. |       |

| t <sub>M_MCKOR</sub>                            | I2S MCK rise<br>time <sup>(3)</sup> | Master mode /<br>Capacitive load<br>CL = 15 pF                            |          |      | 9.9  |          |      | 4.7  | ns    |

| t <sub>M_MCKOF</sub>                            | I2S MCK fall time <sup>(3)</sup>    | Master mode /<br>Capacitive load<br>CL = 15 pF                            |          |      | 12.3 |          |      | 5.4  | ns    |

| d <sub>M_MCKO</sub>                             | I2S MCK duty cycle                  | Master mode                                                               | 46.9     |      | 50   | 47.3     |      | 50   | %     |

| d <sub>M_MCKI</sub>                             | I2S MCK duty cycle                  | Master mode,<br>pin is input (1b)                                         |          | 50   |      |          | 50   |      | %     |

| t <sub>M_SCKOR</sub>                            | I2S SCK rise time <sup>(3)</sup>    | Master mode /<br>Capacitive load<br>CL = 15 pF                            |          |      | 9.7  |          |      | 4.6  | ns    |

| t <sub>M_SCKOF</sub>                            | I2S SCK fall time <sup>(3)</sup>    | Master mode /<br>Capacitive load<br>CL = 15 pF                            |          |      | 10.3 |          |      | 4.6  | ns    |

| d <sub>M_SCKO</sub>                             | I2S SCK duty cycle                  | Master mode                                                               | 46.9     |      | 50   | 47.2     |      | 50   | %     |

| f <sub>M_SCKO</sub> , 1/<br>t <sub>M_SCKO</sub> | I2S SCK<br>frequency                | Master mode,<br>Supposing<br>external device<br>response delay<br>is 30ns |          |      | 7.7  |          |      | 9.2  | MHz   |

| f <sub>S_SCKI</sub> , 1/<br>ts_scкi             | I2S SCK<br>frequency                | Slave mode,<br>Supposing<br>external device<br>response delay<br>is 30ns  |          |      | 12.7 |          |      | 13   | MHz   |