Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | ARM® Cortex®-M0+                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 48MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 52                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                              |

| Data Converters            | A/D 20x12b; D/A 1x10b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-UFBGA                                                                  |

| Supplier Device Package    | 64-UFBGA (5x5)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd21j16a-cu |

### Bit 20 - I2S

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

### **Bit 19 - PTC**

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| 1 | Value | Description                   |

|---|-------|-------------------------------|

|   | 0     | Write-protection is disabled. |

|   | 1     | Write-protection is enabled.  |

### Bit 18 - DAC:

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

|   | Value | Description                   |

|---|-------|-------------------------------|

| ( | )     | Write-protection is disabled. |

|   | 1     | Write-protection is enabled.  |

### Bit 17 - AC

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

|   | Value | Description                   |

|---|-------|-------------------------------|

| ĺ | 0     | Write-protection is disabled. |

|   | 1     | Write-protection is enabled.  |

### Bit 16 - ADC

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

### Bits 11, 12, 13, 14, 15 - TC3, TC4, TC5, TC6, TC7

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

### Bits 8, 9, 10 - TCCn

Writing a zero to these bits has no effect.

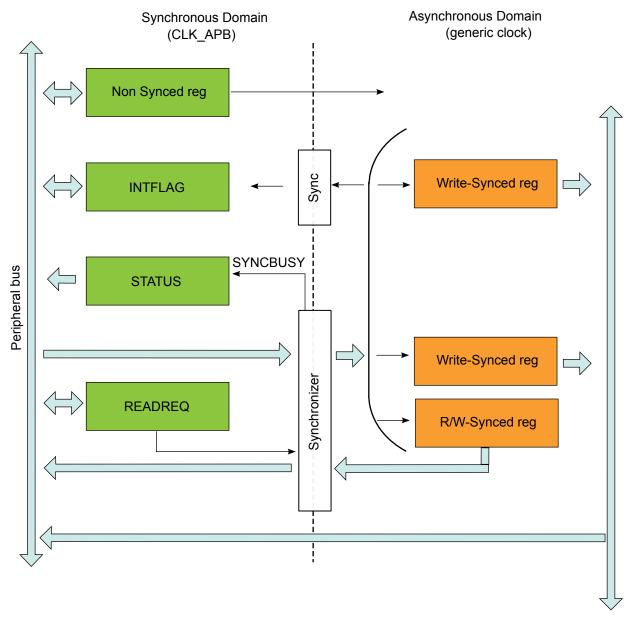

Figure 14-3. Synchronization

### 14.3.1.2 Write-Synchronization

Write-Synchronization is triggered by writing to a register in the peripheral clock domain. The Synchronization Busy bit in the Status register (STATUS.SYNCBUSY) will be set when the write-synchronization starts and cleared when the write-synchronization is complete. Refer to Synchronization Delay for details on the synchronization delay.

When the write-synchronization is ongoing (STATUS.SYNCBUSY is one), any of the following actions will cause the peripheral bus to stall until the synchronization is complete:

- Writing a generic clock peripheral core register

- Reading a read-synchronized peripheral core register

- Reading the register that is being written (and thus triggered the synchronization)

Peripheral core registers without read-synchronization will remain static once they have been written and synchronized, and can be read while the synchronization is ongoing without causing the peripheral bus to

### 16.5.8 Register Access Protection

Registers with write-access can be optionally write-protected by the Peripheral Access Controller (PAC), except the following:

- Interrupt Flag register (INTFLAG).

- Reset Cause register (RCAUSE).

**Note:** Optional write-protection is indicated by the "PAC Write-Protection" property in the register description.

Write-protection does not apply for accesses through an external debugger. Refer to *PAC – Peripheral Access Controller* for details.

#### **Related Links**

PAC - Peripheral Access Controller

## 16.5.9 Analog Connections

Not applicable.

## 16.6 Functional Description

### 16.6.1 Principle of Operation

### 16.6.1.1 Synchronous Clocks

The GCLK\_MAIN clock from GCLK module provides the source for the main clock, which is the common root for the synchronous clocks for the CPU and APBx modules. The main clock is divided by an 8-bit prescaler, and each of the derived clocks can run from any tapping off this prescaler or the undivided main clock, as long as  $f_{CPU} \ge f_{APBx}$ . The synchronous clock source can be changed on the fly to respond to varying load in the application. The clocks for each module in each synchronous clock domain can be individually masked to avoid power consumption in inactive modules. Depending on the sleep mode, some clock domains can be turned off (see Table 16-4).

#### 16.6.1.2 Reset Controller

The Reset Controller collects the various reset sources and generates reset for the device. The device contains a power-on-reset (POR) detector, which keeps the system reset until power is stable. This eliminates the need for external reset circuitry to guarantee stable operation when powering up the device.

### 16.6.1.3 Sleep Mode Controller

In ACTIVE mode, all clock domains are active, allowing software execution and peripheral operation. The PM Sleep Mode Controller allows the user to choose between different sleep modes depending on application requirements, to save power (see Table 16-4).

#### 16.6.2 Basic Operation

#### 16.6.2.1 Initialization

After a power-on reset, the PM is enabled and the Reset Cause register indicates the POR source (RCAUSE.POR). The default clock source of the GCLK\_MAIN clock is started and calibrated before the CPU starts running. The GCLK\_MAIN clock is selected as the main clock without any division on the prescaler. The device is in the ACTIVE mode.

By default, only the necessary clocks are enabled (see Table 16-1).

## 16.6.2.2 Enabling, Disabling and Resetting

The PM module is always enabled and can not be reset.

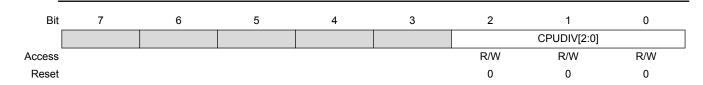

# Bits 2:0 - CPUDIV[2:0]: CPU Prescaler Selection

These bits define the division ratio of the main clock prescaler (2<sup>n</sup>).

| CPUDIV[2:0] | Name   | Description   |

|-------------|--------|---------------|

| 0x0         | DIV1   | Divide by 1   |

| 0x1         | DIV2   | Divide by 2   |

| 0x2         | DIV4   | Divide by 4   |

| 0x3         | DIV8   | Divide by 8   |

| 0x4         | DIV16  | Divide by 16  |

| 0x5         | DIV32  | Divide by 32  |

| 0x6         | DIV64  | Divide by 64  |

| 0x7         | DIV128 | Divide by 128 |

### 16.8.4 APBA Clock Select

Name: APBASEL Offset: 0x09 Reset: 0x00

Property: Write-Protected

| Bit    | 7 | 6 | 5 | 4 | 3 | 2   | 1            | 0   |  |

|--------|---|---|---|---|---|-----|--------------|-----|--|

|        |   |   |   |   |   |     | APBADIV[2:0] |     |  |

| Access |   |   |   |   |   | R/W | R/W          | R/W |  |

| Reset  |   |   |   |   |   | 0   | 0            | 0   |  |

## Bits 2:0 - APBADIV[2:0]: APBA Prescaler Selection

These bits define the division ratio of the APBA clock prescaler (2<sup>n</sup>).

| APBADIV[2:0] | Name   | Description   |

|--------------|--------|---------------|

| 0x0          | DIV1   | Divide by 1   |

| 0x1          | DIV2   | Divide by 2   |

| 0x2          | DIV4   | Divide by 4   |

| 0x3          | DIV8   | Divide by 8   |

| 0x4          | DIV16  | Divide by 16  |

| 0x5          | DIV32  | Divide by 32  |

| 0x6          | DIV64  | Divide by 64  |

| 0x7          | DIV128 | Divide by 128 |

is set when a falling edge has been detected. The flag is cleared when the software write a one to the interrupt flag bit location.

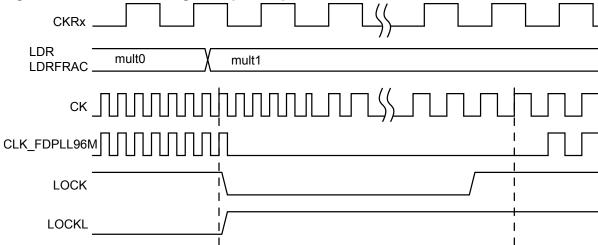

## 17.6.8.7 Digital Filter Selection

The PLL digital filter (PI controller) is automatically adjusted in order to provide a good compromise between stability and jitter. Nevertheless a software operation can override the filter setting using the DPLLCTRLB.FILTER field. The DPLLCTRLB.LPEN field can be use to bypass the TDC module.

### 17.6.9 3.3V Brown-Out Detector Operation

The 3.3V BOD monitors the 3.3V VDDANA supply (BOD33). It supports continuous or sampling modes.

The threshold value action (reset the device or generate an interrupt), the Hysteresis configuration, as well as the enable/disable settings are loaded from Flash User Calibration at startup, and can be overridden by writing to the corresponding BOD33 register bit groups.

### 17.6.9.1 3.3V Brown-Out Detector (BOD33)

The 3.3V Brown-Out Detector (BOD33) monitors the VDDANA supply and compares the voltage with the brown-out threshold level set in the BOD33 Level bit group (BOD33.LEVEL) in the BOD33 register. The BOD33 can generate either an interrupt or a reset when VDDANA crosses below the brown-out threshold level. The BOD33 detection status can be read from the BOD33 Detection bit (PCLKSR.BOD33DET) in the Power and Clocks Status register.

At start-up or at power-on reset (POR), the BOD33 register values are loaded from the Flash User Row. Refer to *NVM User Row Mapping* for more details.

### Related Links

**NVM User Row Mapping**

#### 17.6.9.2 Continuous Mode

When the BOD33 Mode bit (BOD33.MODE) in the BOD33 register is written to zero and the BOD33 is enabled, the BOD33 operates in continuous mode. In this mode, the BOD33 is continuously monitoring the VDDANA supply voltage.

When the BOD12 Mode bit (BOD12.MODE) in the BOD12 register is written to zero and the BOD12 is enabled(BOD12.ENABLE is written to one), the BOD12 operates in continuous mode. In this mode, the BOD12 is continuously monitoring the VDDCORE supply voltage. Continues mode is not available for BOD12 when running in standby sleep mode.

Continuous mode is the default mode for both BOD12 and BOD33.

Table 19-1. MODE0 - Mode Register Summary

| Offset | Name     | Bit   |             |         |                |        |            |        |        |        |  |

|--------|----------|-------|-------------|---------|----------------|--------|------------|--------|--------|--------|--|

|        |          | Pos.  |             |         |                |        |            |        |        |        |  |

| 0x00   | CTRL     | 7:0   | MATCHCLR    |         |                |        | MOD        | E[1:0] | ENABLE | SWRST  |  |

| 0x01   |          | 15:8  |             |         | PRESCALER[3:0] |        |            |        |        |        |  |

| 0x02   | READREQ  | 7:0   |             |         |                |        | ADD        | R[5:0] |        |        |  |

| 0x03   | TETETE S | 15:8  | RREQ        | RCONT   |                |        |            |        |        |        |  |

| 0x04   | EVCTRL   | 7:0   | PEREO7      | PEREO6  | PEREO5         | PEREO4 | PEREO3     | PEREO2 | PEREO1 | PEREO0 |  |

| 0x05   | EVOTRE   | 15:8  | OVFEO       |         |                |        |            |        |        | CMPEO0 |  |

| 0x06   | INTENCLR | 7:0   | OVF         | SYNCRDY |                |        |            |        |        | CMP0   |  |

| 0x07   | INTENSET | 7:0   | OVF         | SYNCRDY |                |        |            |        |        | CMP0   |  |

| 0x08   | INTFLAG  | 7:0   | OVF         | SYNCRDY |                |        |            |        |        | CMP0   |  |

| 0x09   | Reserved |       |             |         |                |        |            |        |        |        |  |

| 0x0A   | STATUS   | 7:0   | SYNCBUSY    |         |                |        |            |        |        |        |  |

| 0x0B   | DBGCTRL  | 7:0   |             |         |                |        |            |        |        | DBGRUN |  |

| 0x0C   | FREQCORR | 7:0   | SIGN        |         |                |        | VALUE[6:0] |        |        |        |  |

| 0x0D   |          |       |             |         |                |        |            |        |        |        |  |

|        | Reserved |       |             |         |                |        |            |        |        |        |  |

| 0x0F   |          |       |             |         |                |        |            |        |        |        |  |

| 0x10   |          | 7:0   |             |         |                | COUN   | NT[7:0]    |        |        |        |  |

| 0x11   | COLINT   | 15:8  | COUNT[15:8] |         |                |        |            |        |        |        |  |

| 0x12   | COUNT    | 23:16 |             |         | COUNT[23:16]   |        |            |        |        |        |  |

| 0x13   |          | 31:24 |             |         |                | COUNT  | Γ[31:24]   |        |        |        |  |

| 0x14   |          |       |             |         |                |        |            |        |        |        |  |

|        | Reserved |       |             |         |                |        |            |        |        |        |  |

| 0x17   |          |       |             |         |                |        |            |        |        |        |  |

| 0x18   |          | 7:0   |             |         |                | COM    | P[7:0]     |        |        |        |  |

| 0x19   | COMP0    | 15:8  |             |         |                | COMF   | P[15:8]    |        |        |        |  |

| 0x1A   |          | 23:16 |             |         |                | COMP   | [23:16]    |        |        |        |  |

| 0x1B   |          | 31:24 |             |         |                | COMP   | [31:24]    |        |        |        |  |

Table 19-2. MODE1 - Mode Register Summary

| Offset | Name     | Bit  |          |         |            |        |        |        |          |        |

|--------|----------|------|----------|---------|------------|--------|--------|--------|----------|--------|

|        |          | Pos. |          |         |            |        |        |        |          |        |

| 0x00   | CTRL     | 7:0  |          |         |            |        | MOD    | E[1:0] | ENABLE   | SWRST  |

| 0x01   | CIRL     | 15:8 |          |         |            |        |        | PRESCA | LER[3:0] |        |

| 0x02   | 0x02     |      |          |         |            |        | ADDI   | R[5:0] |          |        |

| 0x03   | READREQ  | 15:8 | RREQ     | RCONT   |            |        |        |        |          |        |

| 0x04   | EVOTEL   | 7:0  | PEREO7   | PEREO6  | PEREO5     | PEREO4 | PEREO3 | PEREO2 | PEREO1   | PEREO0 |

| 0x05   | EVCTRL   | 15:8 | OVFEO    |         |            |        |        |        | CMPEO1   | CMPEO0 |

| 0x06   | INTENCLR | 7:0  | OVF      | SYNCRDY |            |        |        |        | CMP1     | CMP0   |

| 0x07   | INTENSET | 7:0  | OVF      | SYNCRDY |            |        |        |        | CMP1     | CMP0   |

| 0x08   | INTFLAG  | 7:0  | OVF      | SYNCRDY |            |        |        |        | CMP1     | CMP0   |

| 0x09   | Reserved |      |          |         |            |        |        |        |          |        |

| 0x0A   | STATUS   | 7:0  | SYNCBUSY |         |            |        |        |        |          |        |

| 0x0B   | DBGCTRL  | 7:0  |          |         |            |        |        |        |          | DBGRUN |

| 0x0C   | FREQCORR | 7:0  | SIGN     |         | VALUE[6:0] |        |        |        |          |        |

| Offset | Name    | Bit<br>Pos. |                |                |              |                |                |                |              |                |

|--------|---------|-------------|----------------|----------------|--------------|----------------|----------------|----------------|--------------|----------------|

|        |         | F 03.       |                |                |              |                |                |                |              |                |

| 0x10   |         | 7:0         | EXTINT7        | EXTINT6        | EXTINT5      | EXTINT4        | EXTINT3        | EXTINT2        | EXTINT1      | EXTINT0        |

| 0x11   | INTFLAG | 15:8        | EXTINT15       | EXTINT14       | EXTINT13     | EXTINT12       | EXTINT11       | EXTINT10       | EXTINT9      | EXTINT8        |

| 0x12   | INTILAG | 23:16       |                |                |              |                |                |                | EXTINT17     | EXTINT16       |

| 0x13   |         | 31:24       |                |                |              |                |                |                |              |                |

| 0x14   |         | 7:0         | WAKEUPEN7      | WAKEUPEN6      | WAKEUPEN5    | WAKEUPEN4      | WAKEUPEN3      | WAKEUPEN2      | WAKEUPEN1    | WAKEUPEN0      |

| 0x15   | WAKELID | 15:8        | WAKEUPEN1<br>5 | WAKEUPEN1<br>4 | WAKEUPEN1    | WAKEUPEN1<br>2 | WAKEUPEN1<br>1 | WAKEUPEN1<br>0 | WAKEUPEN9    | WAKEUPEN8      |

| 0x16   | WAKEUP  | 23:16       |                |                |              |                |                |                | WAKEUPEN1    | WAKEUPEN1<br>6 |

| 0x17   | -       | 31:24       |                |                |              |                |                |                |              |                |

| 0x18   |         | 7:0         | FILTEN1        |                | SENSE1[2:0]  |                | FILTEN0        |                | SENSE0[2:0]  |                |

| 0x19   | CONTION | 15:8        | FILTEN3        |                | SENSE3[2:0]  |                | FILTEN2        |                | SENSE2[2:0]  |                |

| 0x1A   | CONFIG0 | 23:16       | FILTEN5        |                | SENSE5[2:0]  |                | FILTEN4        |                | SENSE4[2:0]  |                |

| 0x1B   |         | 31:24       | FILTEN7        |                | SENSE7[2:0]  |                | FILTEN6        |                | SENSE6[2:0]  |                |

| 0x1C   |         | 7:0         | FILTEN9        |                | SENSE9[2:0]  |                | FILTEN8        |                | SENSE8[2:0]  |                |

| 0x1D   | CONFICA | 15:8        | FILTEN11       |                | SENSE11[2:0] |                | FILTEN10       |                | SENSE10[2:0] |                |

| 0x1E   | CONFIG1 | 23:16       | FILTEN13       |                | SENSE13[2:0] |                | FILTEN12       |                | SENSE12[2:0] |                |

| 0x1F   |         | 31:24       | FILTEN15       |                | SENSE15[2:0] |                | FILTEN14       |                | SENSE14[2:0] |                |

| 0x20   | CONFIG2 | 7:0         | FILTEN25       |                | SENSE25[2:0] |                | FILTEN24       |                | SENSE24[2:0] |                |

| 0x21   |         | 15:8        | FILTEN27       |                | SENSE27[2:0] |                | FILTEN26       |                | SENSE26[2:0] |                |

| 0x22   |         | 23:16       | FILTEN29       |                | SENSE29[2:0] |                | FILTEN28       |                | SENSE28[2:0] |                |

| 0x23   |         | 31:24       | FILTEN31       |                | SENSE31[2:0] |                | FILTEN30       |                | SENSE30[2:0] |                |

# 21.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

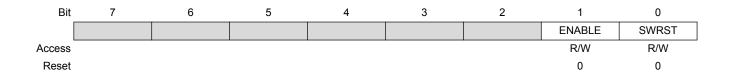

### 21.8.1 Control

Name: CTRL Offset: 0x00 Reset: 0x00

Property: Write-Protected, Write-Synchronized

Name:

STATUS

Offset:

0x18

Reset:

0x0X00

Property:

| Bit    | 15 | 14 | 13 | 12   | 11    | 10    | 9    | 8   |

|--------|----|----|----|------|-------|-------|------|-----|

|        |    |    |    |      |       |       |      | SB  |

| Access |    |    |    |      |       |       |      | R   |

| Reset  |    |    |    |      |       |       |      | x   |

|        |    |    |    |      |       |       |      |     |

| Bit    | 7  | 6  | 5  | 4    | 3     | 2     | 1    | 0   |

|        |    |    |    | NVME | LOCKE | PROGE | LOAD | PRM |

| Access |    |    |    | R/W  | R/W   | R/W   | R/W  | R   |

| Reset  |    |    |    | 0    | 0     | 0     | 0    | 0   |

### Bit 8 - SB: Security Bit Status

| Value | Description                   |

|-------|-------------------------------|

| 0     | The Security bit is inactive. |

| 1     | The Security bit is active.   |

### Bit 4 - NVME: NVM Error

This bit can be cleared by writing a '1' to its bit location.

| Value | Description                                                                                                |

|-------|------------------------------------------------------------------------------------------------------------|

| 0     | No programming or erase errors have been received from the NVM controller since this bit was last cleared. |

| 1     | At least one error has been registered from the NVM Controller since this bit was last cleared.            |

### Bit 3 - LOCKE: Lock Error Status

This bit can be cleared by writing a '1' to its bit location.

| Value | Description                                                                                  |

|-------|----------------------------------------------------------------------------------------------|

| 0     | No programming of any locked lock region has happened since this bit was last cleared.       |

| 1     | Programming of at least one locked lock region has happened since this bit was last cleared. |

## Bit 2 - PROGE: Programming Error Status

This bit can be cleared by writing a '1' to its bit location.

| Value | Description                                                                             |  |

|-------|-----------------------------------------------------------------------------------------|--|

| 0     | No invalid commands or bad keywords were written in the NVM Command register since this |  |

|       | bit was last cleared.                                                                   |  |

| 1     | An invalid command and/or a bad keyword was/were written in the NVM Command register    |  |

|       | since this bit was last cleared.                                                        |  |

### Bit 1 - LOAD: NVM Page Buffer Active Loading

This bit indicates that the NVM page buffer has been loaded with one or more words. Immediately after an NVM load has been performed, this flag is set. It remains set until a page write or a page buffer clear (PBCLR) command is given.

This bit can be cleared by writing a '1' to its bit location.

#### **Related Links**

PM – Power Manager

#### 25.5.3 Clocks

The SERCOM bus clock (CLK\_SERCOMx\_APB) can be enabled and disabled in the Power Manager. Refer to *Perhipharal Clock Masking* for details and default status of this clock.

The SERCOM uses two generic clocks: GCLK\_SERCOMx\_CORE and GCLK\_SERCOMx\_SLOW. The core clock (GCLK\_SERCOMx\_CORE) is required to clock the SERCOM while working as a master. The slow clock (GCLK\_SERCOMx\_SLOW) is only required for certain functions. See specific mode chapters for details.

These clocks must be configured and enabled in the Generic Clock Controller (GCLK) before using the SERCOM.

The generic clocks are asynchronous to the user interface clock (CLK\_SERCOMx\_APB). Due to this asynchronicity, writing to certain registers will require synchronization between the clock domains. Refer to Synchronization for details.

#### **Related Links**

GCLK - Generic Clock Controller

Peripheral Clock Masking

### 25.5.4 DMA

The DMA request lines are connected to the DMA Controller (DMAC). The DMAC must be configured before the SERCOM DMA requests are used.

#### **Related Links**

DMAC - Direct Memory Access Controller

### 25.5.5 Interrupts

The interrupt request line is connected to the Interrupt Controller (NVIC). The NVIC must be configured before the SERCOM interrupts are used.

#### **Related Links**

Nested Vector Interrupt Controller

### 25.5.6 Events

Not applicable.

### 25.5.7 Debug Operation

When the CPU is halted in debug mode, this peripheral will continue normal operation. If the peripheral is configured to require periodical service by the CPU through interrupts or similar, improper operation or data loss may result during debugging. This peripheral can be forced to halt operation during debugging - refer to the Debug Control (DBGCTRL) register for details.

### 25.5.8 Register Access Protection

All registers with write-access can be write-protected optionally by the Peripheral Access Controller (PAC), except the following registers:

- Interrupt Flag Clear and Status register (INTFLAG)

- Status register (STATUS)

- Data register (DATA)

© 2017 Microchip Technology Inc. Datasheet Complete

APPLICATION MB INTERRUPT + SCL HOLD (M1 (M2 (M3 (M4) ADDRESS R/W Р s BUSY -(M1 Wait for (M2 R/W Ā IDLE  $\overline{\textbf{W}}$ Sr DATA  $A/\bar{A}$ SB INTERRUPT + SCL HOLD ►(M4) Software interaction The master provides data on the bus A/Ā (M2 Addressed slave provides data on the bus A/Ā (M3 A/Ā DATA

Figure 28-4. I<sup>2</sup>C Master Behavioral Diagram (SCLSM=0)

In the second strategy (CTRLA.SCLSM=1), interrupts only occur after the ACK bit, as in Master Behavioral Diagram (SCLSM=1). This strategy can be used when it is not necessary to check DATA before acknowledging.

**Note:** I<sup>2</sup>C High-speed (*Hs*) mode requires CTRLA.SCLSM=1.

**Datasheet Complete** 40001882A-page 456 © 2017 Microchip Technology Inc.

### Bit 18 - ACKACT: Acknowledge Action

This bit defines the I<sup>2</sup>C master's acknowledge behavior after a data byte is received from the I<sup>2</sup>C slave. The acknowledge action is executed when a command is written to CTRLB.CMD, or if smart mode is enabled (CTRLB.SMEN is written to one), when DATA.DATA is read.

This bit is not enable-protected.

This bit is not write-synchronized.

| Value | Description |

|-------|-------------|

| 0     | Send ACK.   |

| 1     | Send NACK.  |

### Bits 17:16 - CMD[1:0]: Command

Writing these bits triggers a master operation as described below. The CMD bits are strobe bits, and always read as zero. The acknowledge action is only valid in master read mode. In master write mode, a command will only result in a repeated start or stop condition. The CTRLB.ACKACT bit and the CMD bits can be written at the same time, and then the acknowledge action will be updated before the command is triggered.

Commands can only be issued when either the Slave on Bus interrupt flag (INTFLAG.SB) or Master on Bus interrupt flag (INTFLAG.MB) is '1'.

If CMD 0x1 is issued, a repeated start will be issued followed by the transmission of the current address in ADDR.ADDR. If another address is desired, ADDR.ADDR must be written instead of the CMD bits. This will trigger a repeated start followed by transmission of the new address.

Issuing a command will set the System Operation bit in the Synchronization Busy register (SYNCBUSY.SYSOP).

Table 28-4. Command Description

| CMD[1:0]                   | Direction | Action                                                           |  |

|----------------------------|-----------|------------------------------------------------------------------|--|

| 0x0                        | X         | (No action)                                                      |  |

| 0x1                        | X         | Execute acknowledge action succeeded by repeated Start           |  |

| 0x2 0 (Write) No operation |           | No operation                                                     |  |

|                            | 1 (Read)  | Execute acknowledge action succeeded by a byte read operation    |  |

| 0x3                        | X         | Execute acknowledge action succeeded by issuing a stop condition |  |

These bits are not enable-protected.

### Bit 9 - QCEN: Quick Command Enable

This bit is not write-synchronized.

| Value | Description                |

|-------|----------------------------|

| 0     | Quick Command is disabled. |

| 1     | Quick Command is enabled.  |

#### Bit 8 - SMEN: Smart Mode Enable

When smart mode is enabled, acknowledge action is sent when DATA.DATA is read.

This bit is not write-synchronized.

| Value | Description                                                                       |

|-------|-----------------------------------------------------------------------------------|

| 0     | The TC will wrap around and continue counting on an overflow/underflow condition. |

| 1     | The TC will wrap around and stop on the next underflow/overflow condition.        |

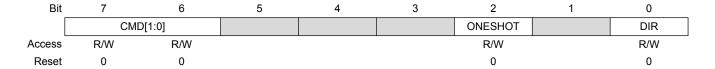

### Bit 0 - DIR: Counter Direction

This bit is used to change the direction of the counter.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the bit and make the counter count up.

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | The timer/counter is counting up (incrementing).   |

| 1     | The timer/counter is counting down (decrementing). |

### 30.8.4 Control B Set

This register allows the user to set bits in the CTRLB register without doing a read-modify-write operation. Changes in this register will also be reflected in the Control B Clear register (CTRLBCLR).

Name: CTRLBSET Offset: 0x05

Reset: 0x00

Property: PAC Write-Protection, Read-synchronized, Write-Synchronized

### Bits 7:6 - CMD[1:0]: Command

These bits are used for software control of the TC. The commands are executed on the next prescaled GCLK\_TC clock cycle. When a command has been executed, the CMD bit group will be read back as zero.

Writing 0x0 to these bits has no effect.

Writing a '1' to any of these bits will clear the pending command.

Table 30-9. Command

| Value | Name      | Description                         |

|-------|-----------|-------------------------------------|

| 0x0   | NONE      | No action                           |

| 0x1   | RETRIGGER | Force a start, restart or retrigger |

| 0x2   | STOP      | Force a stop                        |

| 0x3   | -         | Reserved                            |

### Bit 2 - ONESHOT: One-Shot on Counter

This bit controls one-shot operation of the TC.

Writing a '0' to this bit has no effect

Writing a '1' to this bit will disable one-shot operation.

| Pin Name          | Туре           | Description                       |

|-------------------|----------------|-----------------------------------|

|                   |                |                                   |

| TCCx/WO[WO_NUM-1] | Digital output | Compare channel n waveform output |

Refer to *I/O Multiplexing and Considerations* for details on the pin mapping for this peripheral. One signal can be mapped on several pins.

#### **Related Links**

I/O Multiplexing and Considerations

# 31.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### 31.5.1 I/O Lines

In order to use the I/O lines of this peripheral, the I/O pins must be configured using the I/O Pin Controller (PORT).

### **Related Links**

PORT: IO Pin Controller

### 31.5.2 Power Management

This peripheral can continue to operate in any sleep mode where its source clock is running. The interrupts can wake up the device from sleep modes. Events connected to the event system can trigger other operations in the system without exiting sleep modes.

#### 31.5.3 Clocks

The TCC bus clock (CLK\_TCCx\_APB, with x instance number of the TCCx) is enabled by default, and can be enabled and disabled in the Power Manager.

A generic clock (GCLK\_TCCx) is required to clock the TCC. This clock must be configured and enabled in the generic clock controller before using the TCC. Note that TCC0 and TCC1 share a peripheral clock generator.

The generic clocks (GCLK\_TCCx) are asynchronous to the bus clock (CLK\_TCCx\_APB). Due to this asynchronicity, writing certain registers will require synchronization between the clock domains. Refer to Synchronization for further details.

#### **Related Links**

GCLK - Generic Clock Controller

Peripheral Clock Masking

### 31.5.4 DMA

The DMA request lines are connected to the DMA Controller (DMAC). In order to use DMA requests with this peripheral the DMAC must be configured first. Refer to *DMAC – Direct Memory Access Controller* for details.

#### **Related Links**

DMAC - Direct Memory Access Controller

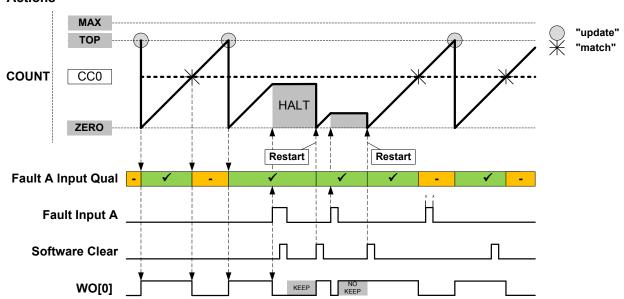

Figure 31-30. Waveform Generation with Software Halt, Fault Qualification, Keep and Restart Actions

#### 31.6.3.6 Non-Recoverable Faults

The non-recoverable fault action will force all the compare outputs to a pre-defined level programmed into the Driver Control register (DRVCTRL.NRE and DRVCTRL.NRV). The non-recoverable fault input (EV0 and EV1) actions are enabled in Event Control register (EVCTRL.EVACT0 and EVCTRL.EVACT1).

To avoid false fault detection on external events (e.g. a glitch on an I/O port) a digital filter can be enabled using Non-Recoverable Fault Input x Filter Value bits in the Driver Control register (DRVCTRL.FILTERVALn). Therefore, the event detection is synchronous, and event action is delayed by the selected digital filter value clock cycles.

When the Fault Detection on Debug Break Detection bit in Debug Control register (DGBCTRL.FDDBD) is written to '1', a non-recoverable Debug Faults State and an interrupt (DFS) is generated when the system goes in debug operation.

### 31.6.3.7 Waveform Extension

Figure 31-31 shows a schematic diagram of actions of the four optional units that follow the recoverable fault stage on a port pin pair: Output Matrix (OTMX), Dead-Time Insertion (DTI), SWAP and Pattern Generation. The DTI and SWAP units can be seen as a four port pair slices:

- Slice 0 DTI0 / SWAP0 acting on port pins (WO[0], WO[WO\_NUM/2 +0])

- Slice 1 DTI1 / SWAP1 acting on port pins (WO[1], WO[WO\_NUM/2 +1])

And more generally:

Slice n DTIx / SWAPx acting on port pins (WO[x], WO[WO\_NUM/2 +x])

| Bit    | 31      | 30                | 29           | 28    | 27       | 26      | 25       | 24     |

|--------|---------|-------------------|--------------|-------|----------|---------|----------|--------|

|        |         |                   |              |       |          | FILTER  | VAL[3:0] |        |

| Access |         |                   |              |       | R/W      | R/W     | R/W      | R/W    |

| Reset  |         |                   |              |       | 0        | 0       | 0        | 0      |

|        |         |                   |              |       |          |         |          |        |

| Bit    | 23      | 22                | 21           | 20    | 19       | 18      | 17       | 16     |

|        |         |                   |              | BLANK | VAL[7:0] |         |          |        |

| Access | R/W     | R/W               | R/W          | R/W   | R/W      | R/W     | R/W      | R/W    |

| Reset  | 0       | 0                 | 0            | 0     | 0        | 0       | 0        | 0      |

|        |         |                   |              |       |          |         |          |        |

| Bit    | 15      | 14                | 13           | 12    | 11       | 10      | 9        | 8      |

|        |         |                   | CAPTURE[2:0] |       | CHSE     | EL[1:0] | HAL      | Γ[1:0] |

| Access |         | R/W               | R/W          | R/W   | R/W      | R/W     | R/W      | R/W    |

| Reset  |         | 0                 | 0            | 0     | 0        | 0       | 0        | 0      |

|        |         |                   |              |       |          |         |          |        |

| Bit    | 7       | 6                 | 5            | 4     | 3        | 2       | 1        | 0      |

|        | RESTART | ESTART BLANK[1:0] |              | QUAL  | KEEP     |         | SRC      | [1:0]  |

| Access | R/W     | R/W               | R/W          | R/W   | R/W      |         | R/W      | R/W    |

| Reset  | 0       | 0                 | 0            | 0     | 0        |         | 0        | 0      |

### Bits 27:24 - FILTERVAL[3:0]: Recoverable Fault n Filter Value

These bits define the filter value applied on MCEx (x=0,1) event input line. The value must be set to zero when MCEx event is used as synchronous event.

### Bits 23:16 - BLANKVAL[7:0]: Recoverable Fault n Blanking Value

These bits determine the duration of the blanking of the fault input source. Activation and edge selection of the blank filtering are done by the BLANK bits (FCTRLn.BLANK).

When enabled, the fault input source is internally disabled for BLANKVAL\* prescaled GCLK\_TCC periods after the detection of the waveform edge.

### Bits 14:12 - CAPTURE[2:0]: Recoverable Fault n Capture Action

These bits select the capture and Fault n interrupt/event conditions.

Table 31-8. Fault n Capture Action

| Value | Name    | Description                                                                                                                                                                                                                          |

|-------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0   | DISABLE | Capture on valid recoverable Fault n is disabled                                                                                                                                                                                     |

| 0x1   | CAPT    | On rising edge of a valid recoverable Fault n, capture counter value on channel selected by CHSEL[1:0].  INTFLAG.FAULTn flag rises on each new captured value.                                                                       |

| 0x2   | CAPTMIN | On rising edge of a valid recoverable Fault n, capture counter value on channel selected by CHSEL[1:0], if COUNT value is lower than the last stored capture value (CC).  INTFLAG.FAULTn flag rises on each local minimum detection. |

Writing this bit to zero will have no effect.

| Value | Description                                                                                                                                                                                                                                      |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | No flush action.                                                                                                                                                                                                                                 |

| 1     | "Writing a '1' to this bit will flush the ADC pipeline. A flush will restart the ADC clock on the next peripheral clock edge, and all conversions in progress will be aborted and lost. This bit will be cleared after the ADC has been flushed. |

|       | After the flush, the ADC will resume where it left off; i.e., if a conversion was pending, the ADC will start a new conversion.                                                                                                                  |

# 33.8.8 Input Control

Name: INPUTCTRL

Offset: 0x10

**Reset:** 0x00000000

Property: Write-Protected, Write-Synchronized

| Bit    | 31  | 30      | 29        | 28  | 27  | 26          | 25             | 24  |

|--------|-----|---------|-----------|-----|-----|-------------|----------------|-----|

|        |     |         |           |     |     | GAIN        | <b>\</b> [3:0] |     |

| Access |     |         |           |     | R/W | R/W         | R/W            | R/W |

| Reset  |     |         |           |     | 0   | 0           | 0              | 0   |

|        |     |         |           |     |     |             |                |     |

| Bit    | 23  | 22      | 21        | 20  | 19  | 18          | 17             | 16  |

|        |     | INPUTOF | FSET[3:0] |     |     | INPUTS      | CAN[3:0]       |     |

| Access | R/W | R/W     | R/W       | R/W | R/W | R/W         | R/W            | R/W |

| Reset  | 0   | 0       | 0         | 0   | 0   | 0           | 0              | 0   |

|        |     |         |           |     |     |             |                |     |

| Bit    | 15  | 14      | 13        | 12  | 11  | 10          | 9              | 8   |

|        |     |         |           |     |     | MUXNEG[4:0] |                |     |

| Access |     |         |           | R/W | R/W | R/W         | R/W            | R/W |

| Reset  |     |         |           | 0   | 0   | 0           | 0              | 0   |

|        |     |         |           |     |     |             |                |     |

| Bit    | 7   | 6       | 5         | 4   | 3   | 2           | 1              | 0   |

|        |     |         |           |     |     | MUXPOS[4:0] |                |     |

| Access |     |         |           | R/W | R/W | R/W         | R/W            | R/W |

| Reset  |     |         |           | 0   | 0   | 0           | 0              | 0   |

# Bits 27:24 - GAIN[3:0]: Gain Factor Selection

These bits set the gain factor of the ADC gain stage.

| GAIN[3:0] | Name | Description |

|-----------|------|-------------|

| 0x0       | 1X   | 1x          |

| 0x1       | 2X   | 2x          |

| 0x2       | 4X   | 4x          |

| 0x3       | 8X   | 8x          |

| 0x4       | 16X  | 16x         |

When RUNSTDBY is one, any enabled AC interrupt source can wake up the CPU. While the CPU is sleeping, single-shot comparisons are only triggerable by events. The AC can also be used during sleep modes where the clock used by the AC is disabled, provided that the AC is still powered (not in shutdown). In this case, the behavior is slightly different and depends on the measurement mode.

Table 34-1. Sleep Mode Operation

| COMPCTRLx.MODE  | RUNSTDBY=0     | RUNSTDBY=1                                                               |

|-----------------|----------------|--------------------------------------------------------------------------|

| 0 (Continuous)  | COMPx disabled | GCLK_AC_DIG stopped, COMPx enabled                                       |

| 1 (Single-shot) | COMPx disabled | GCLK_AC_DIG stopped, COMPx enabled only when triggered by an input event |

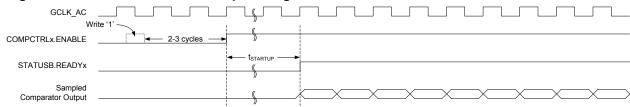

### 34.6.14.1 Continuous Measurement during Sleep

When a comparator is enabled in continuous measurement mode and GCLK\_AC\_DIG is disabled during sleep, the comparator will remain continuously enabled and will function asynchronously. The current state of the comparator is asynchronously monitored for changes. If an edge matching the interrupt condition is found, GCLK\_AC\_DIG is started to register the interrupt condition and generate events. If the interrupt is enabled in the Interrupt Enable registers (INTENCLR/SET), the AC can wake up the device; otherwise GCLK\_AC\_DIG is disabled until the next edge detection. Filtering is not possible with this configuration.

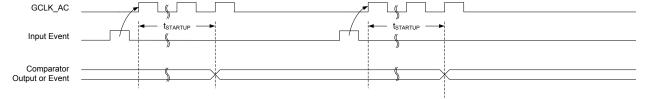

Figure 34-9. Continuous Mode SleepWalking

#### 34.6.14.2 Single-Shot Measurement during Sleep

For low-power operation, event-triggered measurements can be performed during sleep modes. When the event occurs, the Power Manager will start GCLK\_AC\_DIG. The comparator is enabled, and after the start-up time has passed, a comparison is done, with filtering if desired, and the appropriate peripheral events and interrupts are also generated, as the figure below. The comparator and GCLK\_AC\_DIG are then disabled again automatically, unless configured to wake the system from sleep. Filtering is allowed with this configuration.

Figure 34-10. Single-Shot SleepWalking

### 34.6.15 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

The following bits are synchronized when written:

Software Reset bit in control register (CTRLA.SWRST)

### Bit 19 - HYST: Hysteresis Enable

This bit indicates the hysteresis mode of comparator n. Hysteresis is available only for continuous mode (COMPCTRLn. SINGLE=0). COMPCTRLn.HYST can be written only while COMPCTRLn.ENABLE is zero.

This bit is not synchronized.

These bits are not synchronized.

| ı | Value | Name                    |

|---|-------|-------------------------|

|   | 0     | Hysteresis is disabled. |

|   | 1     | Hysteresis is enabled.  |

### Bits 17:16 - OUT[1:0]: Output

These bits configure the output selection for comparator n. COMPCTRLn.OUT can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value | Name  | Description                                                                           |

|-------|-------|---------------------------------------------------------------------------------------|

| 0x0   | OFF   | The output of COMPn is not routed to the COMPn I/O port                               |

| 0x1   | ASYNC | The asynchronous output of COMPn is routed to the COMPn I/O port                      |

| 0x2   | SYNC  | The synchronous output (including filtering) of COMPn is routed to the COMPn I/O port |

| 0x3   | N/A   | Reserved                                                                              |

### Bit 15 - SWAP: Swap Inputs and Invert

This bit swaps the positive and negative inputs to COMPn and inverts the output. This function can be used for offset cancellation. COMPCTRLn.SWAP can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | The output of MUXPOS connects to the positive input, and the output of MUXNEG connects |

|       | to the negative input.                                                                 |

| 1     | The output of MUXNEG connects to the positive input, and the output of MUXPOS connects |

|       | to the negative input.                                                                 |

### Bits 13:12 - MUXPOS[1:0]: Positive Input Mux Selection

These bits select which input will be connected to the positive input of comparator n. COMPCTRLn.MUXPOS can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value | Name | Description |

|-------|------|-------------|

| 0x0   | PIN0 | I/O pin 0   |

| 0x1   | PIN1 | I/O pin 1   |

| 0x2   | PIN2 | I/O pin 2   |

| 0x3   | PIN3 | I/O pin 3   |

### Bits 10:8 - MUXNEG[2:0]: Negative Input Mux Selection

These bits select which input will be connected to the negative input of comparator n. COMPCTRLn.MUXNEG can only be written while COMPCTRLn.ENABLE is zero.

# 36. PTC - Peripheral Touch Controller

### 36.1 Overview

The Peripheral Touch Controller (PTC) acquires signals in order to detect touch on capacitive sensors. The external capacitive touch sensor is typically formed on a PCB, and the sensor electrodes are connected to the analog front end of the PTC through the I/O pins in the device. The PTC supports both self- and mutual-capacitance sensors.

In mutual-capacitance mode, sensing is done using capacitive touch matrices in various X-Y configurations, including indium tin oxide (ITO) sensor grids. The PTC requires one pin per X-line and one pin per Y-line.

In self-capacitance mode, the PTC requires only one pin (Y-line) for each touch sensor.

The number of available pins and the assignment of X- and Y-lines is depending on both package type and device configuration. Refer to the Configuration Summary and I/O Multiplexing table for details.

#### **Related Links**

I/O Multiplexing and Considerations Configuration Summary

### 36.2 Features

- · Low-power, high-sensitivity, environmentally robust capacitive touch buttons, sliders, wheels

- Supports wake-up on touch from Standby sleep mode

- Supports mutual capacitance and self-capacitance sensing

- 6/10/16 buttons in self-capacitance mode, for 32-/48-/64- pins respectively

- 60/120/256 buttons in mutual-capacitance mode, for 32-/48-/64- pins respectively

- Mix-and-match mutual-and self-capacitance sensors

- One pin per electrode no external components

- · Load compensating charge sensing

- Parasitic capacitance compensation and adjustable gain for superior sensitivity

- Zero drift over the temperature and V<sub>DD</sub> range

- Auto calibration and re-calibration of sensors

- Single-shot and free-running charge measurement

- Hardware noise filtering and noise signal de-synchronization for high conducted immunity

- Selectable channel change delay allows choosing the settling time on a new channel, as required

- Acquisition-start triggered by command or through auto-triggering feature

- Low CPU utilization through interrupt on acquisition-complete

- Supported by the Atmel® QTouch® Composer development tools. See also Atmel|Start and Atmel Studio documentation.

#### **Related Links**

I/O Multiplexing and Considerations Configuration Summary

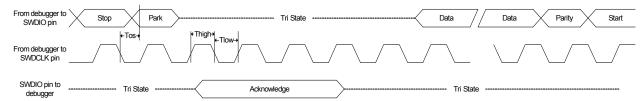

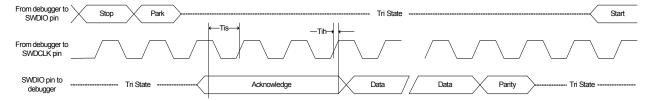

## 37.15.4 SWD Timing

## Figure 37-23. SWD Interface Signals

#### Read Cycle

### Write Cycle

Table 37-64. SWD Timings<sup>(1)</sup>

| Symbol            | Parameter                                                     | Conditions                 | Min. | Max.   | Units |

|-------------------|---------------------------------------------------------------|----------------------------|------|--------|-------|

| T <sub>high</sub> | SWDCLK High period                                            | external capacitor = 40 pF | 10   | 500000 | ns    |

| T <sub>low</sub>  | SWDCLK Low period                                             |                            | 10   | 500000 |       |

| T <sub>os</sub>   | SWDIO output skew to falling edge SWDCLK                      |                            | -5   | 5      |       |

| T <sub>is</sub>   | Input Setup time required between SWDIO                       |                            | 4    | -      |       |

| T <sub>ih</sub>   | Input Hold time required between SWDIO and rising edge SWDCLK |                            | 1    | -      |       |

Note: 1. These values are based on simulation. These values are not covered by test limits in production or characterization.