Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                               |

| Data Converters            | A/D 20x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd21j16b-aut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

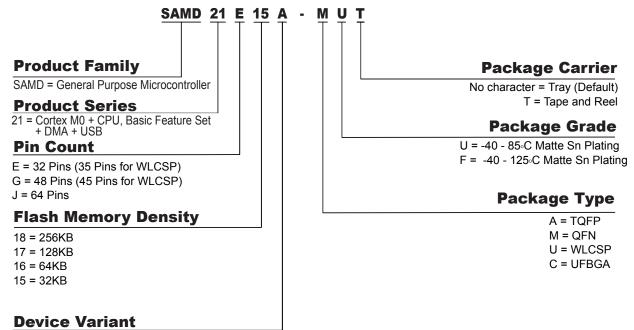

## 3. Ordering Information

A = Default Variant

B = Added RWW support for 32KB and 64KB memory options

C = Silicon revision F for WLCSP35 package option.

## 3.1 SAM D21E

## Table 3-1. Device Variant A

| Ordering Code    | FLASH (bytes) | SRAM (bytes) | Package | Carrier Type |

|------------------|---------------|--------------|---------|--------------|

| ATSAMD21E15A-AU  | 32K           | 4K           | TQFP32  | Tray         |

| ATSAMD21E15A-AUT |               |              |         | Tape & Reel  |

| ATSAMD21E15A-AF  |               |              |         | Tray         |

| ATSAMD21E15A-AFT |               |              |         | Tape & Reel  |

| ATSAMD21E15A-MU  |               |              | QFN32   | Tray         |

| ATSAMD21E15A-MUT |               |              |         | Tape & Reel  |

| ATSAMD21E15A-MF  |               |              |         | Tray         |

| ATSAMD21E15A-MFT |               |              |         | Tape & Reel  |

## 3.3 SAM D21J

Table 3-6. Device Variant A

| Ordering Code    | FLASH (bytes) | SRAM (bytes) | Package | Carrier Type |

|------------------|---------------|--------------|---------|--------------|

| ATSAMD21J15A-AU  | 32K           | 4K           | TQFP64  | Tray         |

| ATSAMD21J15A-AUT |               |              |         | Tape & Reel  |

| ATSAMD21J15A-AF  |               |              |         | Tray         |

| ATSAMD21J15A-AFT |               |              |         | Tape & Reel  |

| ATSAMD21J15A-MU  |               |              | QFN64   | Tray         |

| ATSAMD21J15A-MUT |               |              |         | Tape & Reel  |

| ATSAMD21J15A-MF  |               |              |         | Tray         |

| ATSAMD21J15A-MFT |               |              |         | Tape & Reel  |

| ATSAMD21J16A-AU  | 64K           | 8K           | TQFP64  | Tray         |

| ATSAMD21J16A-AUT |               |              |         | Tape & Reel  |

| ATSAMD21J16A-AF  |               |              |         | Tray         |

| ATSAMD21J16A-AFT |               |              |         | Tape & Reel  |

| ATSAMD21J16A-MU  |               |              | QFN64   | Tray         |

| ATSAMD21J16A-MUT |               |              |         | Tape & Reel  |

| ATSAMD21J16A-MF  |               |              |         | Tray         |

| ATSAMD21J16A-MFT |               |              |         | Tape & Reel  |

| ATSAMD21J16A-CU  |               |              | UFBGA64 | Tray         |

| ATSAMD21J16A-CUT |               |              |         | Tape & Reel  |

| ATSAMD21J17A-AU  | 128K          | 16K          | TQFP64  | Tray         |

| ATSAMD21J17A-AUT |               |              |         | Tape & Reel  |

| ATSAMD21J17A-AF  |               |              |         | Tray         |

| ATSAMD21J17A-AFT |               |              |         | Tape & Reel  |

| ATSAMD21J17A-MU  |               |              | QFN64   | Tray         |

| ATSAMD21J17A-MUT |               |              |         | Tape & Reel  |

| ATSAMD21J17A-MF  |               |              |         | Tray         |

| ATSAMD21J17A-MFT |               |              |         | Tape & Reel  |

| ATSAMD21J17A-CU  |               |              | UFBGA64 | Tray         |

| ATSAMD21J17A-CUT |               |              |         | Tape & Reel  |

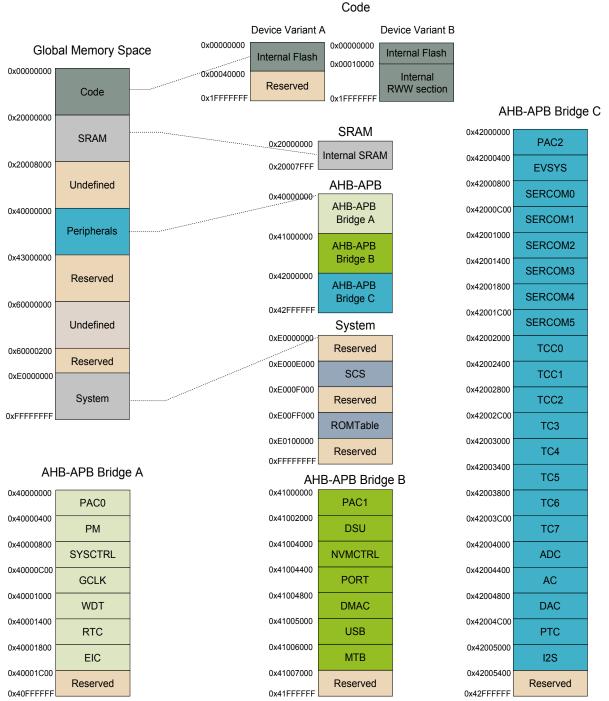

# 9. Product Mapping

Figure 9-1. SAM D21 Product Mapping

This figure represents the full configuration of the SAM D21 with maximum flash and SRAM capabilities and a full set of peripherals. Refer to the Configuration Summary for details.

## 13.13 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to Register Access Protection.

## 13.13.1 Control

Name: CTRL Offset: 0x0000 Reset: 0x00 Property: PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4  | 3     | 2   | 1 | 0     |

|--------|---|---|---|----|-------|-----|---|-------|

|        |   |   |   | CE | MBIST | CRC |   | SWRST |

| Access |   |   |   | W  | W     | W   |   | W     |

| Reset  |   |   |   | 0  | 0     | 0   |   | 0     |

## Bit 4 – CE: Chip-Erase

Writing a '0' to this bit has no effect.

Writing a '1' to this bit starts the Chip-Erase operation.

### Bit 3 – MBIST: Memory Built-In Self-Test

Writing a '0' to this bit has no effect.

Writing a '1' to this bit starts the memory BIST algorithm.

### Bit 2 – CRC: 32-bit Cyclic Redundancy Check

Writing a '0' to this bit has no effect.

Writing a '1' to this bit starts the cyclic redundancy check algorithm.

### Bit 0 – SWRST: Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit resets the module.

### 13.13.2 Status A

Name:STATUSAOffset:0x0001Reset:0x00Property:PAC Write-Protection

**Note:** Optional write-protection is indicated by the "PAC Write-Protection" property in the register description.

When the CPU is halted in debug mode, all write-protection is automatically disabled. Write-protection does not apply for accesses through an external debugger.

## 17.5.7 Analog Connections

When used, the 32.768kHz crystal must be connected between the XIN32 and XOUT32 pins, and the 0.4-32MHz crystal must be connected between the XIN and XOUT pins, along with any required load capacitors. For details on recommended oscillator characteristics and capacitor load, refer to the *Electrical Characteristics* for details.

## **Related Links**

**Electrical Characteristics**

## 17.6 Functional Description

## 17.6.1 Principle of Operation

XOSC, XOSC32K, OSC32K, OSCULP32K, OSC8M, DFLL48M, FDPLL96M, BOD33, BOD12, and VREF are configured via SYSCTRL control registers. Through this interface, the sub-peripherals are enabled, disabled or have their calibration values updated.

The Power and Clocks Status register gathers different status signals coming from the sub-peripherals controlled by the SYSCTRL. The status signals can be used to generate system interrupts, and in some cases wake up the system from standby mode, provided the corresponding interrupt is enabled.

The oscillator must be enabled to run. The oscillator is enabled by writing a one to the ENABLE bit in the respective oscillator control register, and disabled by writing a zero to the oscillator control register. In idle mode, the default operation of the oscillator is to run only when requested by a peripheral. In standby mode, the default operation of the oscillator is to stop. This behavior can be changed by the user, see below for details.

The behavior of the oscillators in the different sleep modes is shown in the table below.

| Oscillator | ldle 0, 1, 2   | Standby |

|------------|----------------|---------|

| XOSC       | Run on request | Stop    |

| XOSC32K    | Run on request | Stop    |

| OSC32K     | Run on request | Stop    |

| OSCULP32K  | Run            | Run     |

| OSC8M      | Run on request | Stop    |

| DFLL48M    | Run on request | Stop    |

| FDPLL96M   | Run on request | Stop    |

| Table 17-1. Benavior of the Oscillators | Table 17-1. | Behavior of the Oscillators |

|-----------------------------------------|-------------|-----------------------------|

|-----------------------------------------|-------------|-----------------------------|

To force an oscillator to always run in idle mode, and not only when requested by a peripheral, the oscillator ONDEMAND bit must be written to zero. The default value of this bit is one, and thus the default operation in idle mode is to run only when requested by a peripheral.

| Value | Description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| 0     | The DFLL Lock Fine interrupt is disabled.                                                |

| 1     | The DFLL Lock Fine interrupt is enabled, and an interrupt request will be generated when |

|       | the DFLL Lock Fine Interrupt flag is set.                                                |

## Bit 5 – DFLLOOB: DFLL Out Of Bounds Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the DFLL Out Of Bounds Interrupt Enable bit, which enables the DFLL Out Of Bounds interrupt.

| Value | Description                                                                             |

|-------|-----------------------------------------------------------------------------------------|

| 0     | The DFLL Out Of Bounds interrupt is disabled.                                           |

| 1     | The DFLL Out Of Bounds interrupt is enabled, and an interrupt request will be generated |

|       | when the DFLL Out Of Bounds Interrupt flag is set.                                      |

## Bit 4 – DFLLRDY: DFLL Ready Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the DFLL Ready Interrupt Enable bit, which enables the DFLL Ready interrupt and set the corresponding interrupt request.

| Value | Description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| 0     | The DFLL Ready interrupt is disabled.                                                    |

| 1     | The DFLL Ready interrupt is enabled, and an interrupt request will be generated when the |

|       | DFLL Ready Interrupt flag is set.                                                        |

## Bit 3 – OSC8MRDY: OSC8M Ready Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the OSC8M Ready Interrupt Enable bit, which enables the OSC8M Ready interrupt.

| Value | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| 0     | The OSC8M Ready interrupt is disabled.                                                    |

| 1     | The OSC8M Ready interrupt is enabled, and an interrupt request will be generated when the |

|       | OSC8M Ready Interrupt flag is set.                                                        |

### Bit 2 – OSC32KRDY: OSC32K Ready Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the OSC32K Ready Interrupt Enable bit, which enables the OSC32K Ready interrupt.

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | The OSC32K Ready interrupt is disabled.                                                |

| 1     | The OSC32K Ready interrupt is enabled, and an interrupt request will be generated when |

|       | the OSC32K Ready Interrupt flag is set.                                                |

### Bit 1 – XOSC32KRDY: XOSC32K Ready Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the XOSC32K Ready Interrupt Enable bit, which enables the XOSC32K Ready interrupt.

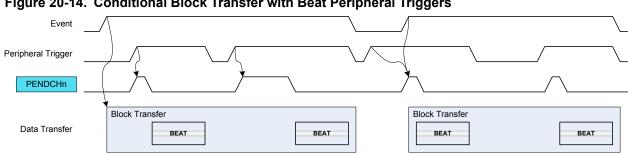

## Figure 20-14. Conditional Block Transfer with Beat Peripheral Triggers

## **Channel Suspend**

The event input is used to suspend an ongoing channel operation. The event is acknowledged when the current AHB access is completed. For further details on Channel Suspend, refer to Channel Suspend.

## **Channel Resume**

The event input is used to resume a suspended channel operation. The event is acknowledged as soon as the event is received and the Channel Suspend Interrupt Flag (CHINTFLAG.SUSP) is cleared. For further details refer to Channel Suspend.

## Skip Next Block Suspend

This event can be used to skip the next block suspend action. If the channel is suspended before the event rises, the channel operation is resumed and the event is acknowledged. If the event rises before a suspend block action is detected, the event is kept until the next block suspend detection. When the block transfer is completed, the channel continues the operation (not suspended) and the event is acknowledged.

**Related Links**

**USER**

### 20.6.3.5 Event Output Selection

Event output selection is available only for the least significant DMA channels. The pulse width of an event output from a channel is one AHB clock cycle.

The output of channel events is enabled by writing a '1' to the Channel Event Output Enable bit in the Control B register (CHCTRLB.EVOE). The event output cause is selected by writing to the Event Output Selection bits in the Block Transfer Control register (BTCTRL.EVOSEL). It is possible to generate events after each block transfer (BTCTRL.EVOSEL=0x1) or beat transfer (BTCTRL.EVOSEL=0x3). To enable an event being generated when a transaction is complete, the block event selection must be set in the last transfer descriptor only.

The figure Figure 20-15 shows an example where the event output generation is enabled in the first block transfer, and disabled in the second block.

# 32-bit ARM-Based Microcontrollers

| Offset | Name      | Bit<br>Pos. |                |                |                |                |                |                |                |                |

|--------|-----------|-------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

|        |           | F05.        |                |                |                |                |                |                |                |                |

| 0x10   |           | 7:0         | EXTINT7        | EXTINT6        | EXTINT5        | EXTINT4        | EXTINT3        | EXTINT2        | EXTINT1        | EXTINT0        |

| 0x11   | INTFLAG   | 15:8        | EXTINT15       | EXTINT14       | EXTINT13       | EXTINT12       | EXTINT11       | EXTINT10       | EXTINT9        | EXTINT8        |

| 0x12   | INTLAG    | 23:16       |                |                |                |                |                |                | EXTINT17       | EXTINT16       |

| 0x13   |           | 31:24       |                |                |                |                |                |                |                |                |

| 0x14   |           | 7:0         | WAKEUPEN7      | WAKEUPEN6      | WAKEUPEN5      | WAKEUPEN4      | WAKEUPEN3      | WAKEUPEN2      | WAKEUPEN1      | WAKEUPEN0      |

| 0x15   |           | 15:8        | WAKEUPEN1<br>5 | WAKEUPEN1<br>4 | WAKEUPEN1<br>3 | WAKEUPEN1<br>2 | WAKEUPEN1<br>1 | WAKEUPEN1<br>0 | WAKEUPEN9      | WAKEUPEN8      |

| 0x16   | WAKEUP    | 23:16       |                |                |                |                |                |                | WAKEUPEN1<br>7 | WAKEUPEN1<br>6 |

| 0x17   |           | 31:24       |                |                |                |                |                |                |                |                |

| 0x18   |           | 7:0         | FILTEN1        |                | SENSE1[2:0]    |                | FILTEN0        |                | SENSE0[2:0]    | 1              |

| 0x19   |           | 15:8        | FILTEN3        |                | SENSE3[2:0]    |                | FILTEN2        |                | SENSE2[2:0]    |                |

| 0x1A   | CONFIG0   | 23:16       | FILTEN5        |                | SENSE5[2:0]    |                | FILTEN4        |                | SENSE4[2:0]    |                |

| 0x1B   |           | 31:24       | FILTEN7        |                | SENSE7[2:0]    |                | FILTEN6        |                | SENSE6[2:0]    |                |

| 0x1C   |           | 7:0         | FILTEN9        |                | SENSE9[2:0]    |                | FILTEN8        |                | SENSE8[2:0]    |                |

| 0x1D   |           | 15:8        | FILTEN11       |                | SENSE11[2:0]   |                | FILTEN10       |                | SENSE10[2:0]   |                |

| 0x1E   | CONFIG1   | 23:16       | FILTEN13       |                | SENSE13[2:0]   |                | FILTEN12       |                | SENSE12[2:0]   |                |

| 0x1F   |           | 31:24       | FILTEN15       |                | SENSE15[2:0]   |                | FILTEN14       |                | SENSE14[2:0]   |                |

| 0x20   |           | 7:0         | FILTEN25       |                | SENSE25[2:0]   |                | FILTEN24       |                | SENSE24[2:0]   |                |

| 0x21   | - CONFIG2 | 15:8        | FILTEN27       |                | SENSE27[2:0]   |                | FILTEN26       |                | SENSE26[2:0]   |                |

| 0x22   |           | 23:16       | FILTEN29       |                | SENSE29[2:0]   |                | FILTEN28       |                | SENSE28[2:0]   |                |

| 0x23   |           | 31:24       | FILTEN31       |                | SENSE31[2:0]   |                | FILTEN30       |                | SENSE30[2:0]   |                |

## 21.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

## 21.8.1 Control

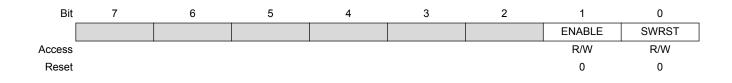

Name: CTRL Offset: 0x00 Reset: 0x00 Property: Write-Protected, Write-Synchronized

This bit will always read as zero.

## Bit 16 – PMUXEN: Peripheral Multiplexer Enable

This bit determines the new value written to PINCFGy.PMUXEN for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits, when the WRCONFIG.WRPINCFG bit is set.

This bit will always read as zero.

## Bits 15:0 – PINMASK[15:0]: Pin Mask for Multiple Pin Configuration

These bits select the pins to be configured within the half-word group selected by the WRCONFIG.HWSEL bit.

These bits will always read as zero.

| Value | Description                                                                                   |

|-------|-----------------------------------------------------------------------------------------------|

| 0     | The configuration of the corresponding I/O pin in the half-word group will be left unchanged. |

| 1     | The configuration of the corresponding I/O pin in the half-word PORT group will be updated.   |

## 23.8.12 Peripheral Multiplexing n

There are up to 16 Peripheral Multiplexing registers in each group, one for every set of two subsequent I/O lines. The n denotes the number of the set of I/O lines.

Name: PMUXn Offset: 0x30 + n\*0x01 [n=0..15] Reset: 0x00 Property: PAC Write-Protection

| Bit    | 7          | 6   | 5   | 4   | 3          | 2   | 1   | 0   |

|--------|------------|-----|-----|-----|------------|-----|-----|-----|

|        | PMUXO[3:0] |     |     |     | PMUXE[3:0] |     |     |     |

| Access | R/W        | R/W | R/W | R/W | R/W        | R/W | R/W | R/W |

| Reset  | 0          | 0   | 0   | 0   | 0          | 0   | 0   | 0   |

## Bits 7:4 – PMUXO[3:0]: Peripheral Multiplexing for Odd-Numbered Pin

These bits select the peripheral function for odd-numbered pins  $(2^n + 1)$  of a PORT group, if the corresponding PINCFGy.PMUXEN bit is '1'.

Not all possible values for this selection may be valid. For more details, refer to the *I/O Multiplexing and Considerations*.

| PMUXO[3:0] | Name | Description                    |

|------------|------|--------------------------------|

| 0x0        | А    | Peripheral function A selected |

| 0x1        | В    | Peripheral function B selected |

| 0x2        | С    | Peripheral function C selected |

| 0x3        | D    | Peripheral function D selected |

| 0x4        | E    | Peripheral function E selected |

| 0x5        | F    | Peripheral function F selected |

| 0x6        | G    | Peripheral function G selected |

| 0x7        | Н    | Peripheral function H selected |

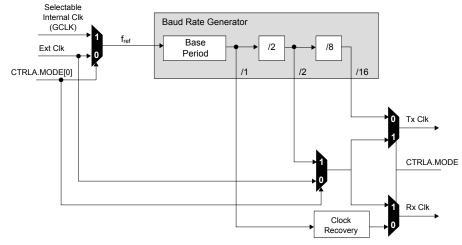

## Figure 25-3. Baud Rate Generator

Table 25-2 contains equations for the baud rate (in bits per second) and the BAUD register value for each operating mode.

For asynchronous operation, there are two different modes: In *arithmetic mode*, the BAUD register value is 16 bits (0 to 65,535). In *fractional mode*, the BAUD register is 13 bits, while the fractional adjustment is 3 bits. In this mode the BAUD setting must be greater than or equal to 1.

For synchronous operation, the BAUD register value is 8 bits (0 to 255).

| Operating Mode             | Condition                         | Baud Rate (Bits Per Second)                                           | BAUD Register Value Calculation                                        |

|----------------------------|-----------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------|

| Asynchronous<br>Arithmetic | $f_{BAUD} \leq \frac{f_{ref}}{S}$ | $f_{BAUD} = \frac{f_{ref}}{S} \left( 1 - \frac{BAUD}{65536} \right)$  | $BAUD = 65536 \cdot \left(1 - S \cdot \frac{f_{BAUD}}{f_{ref}}\right)$ |

| Asynchronous<br>Fractional | $f_{BAUD} \le \frac{f_{ref}}{S}$  | $f_{BAUD} = \frac{f_{ref}}{S \cdot \left(BAUD + \frac{FP}{8}\right)}$ | $BAUD = \frac{f_{ref}}{S \cdot f_{BAUD}} - \frac{FP}{8}$               |

| Synchronous                | $f_{BAUD} \leq \frac{f_{ref}}{2}$ | $f_{BAUD} = \frac{f_{ref}}{2 \cdot (BAUD + 1)}$                       | $BAUD = \frac{f_{ref}}{2 \cdot f_{BAUD}} - 1$                          |

## Table 25-2. Baud Rate Equations

S - Number of samples per bit. Can be 16, 8, or 3.

The Asynchronous Fractional option is used for auto-baud detection.

The baud rate error is represented by the following formula:

$$Error = 1 - \left(\frac{ExpectedBaudRate}{ActualBaudRate}\right)$$

## Asynchronous Arithmetic Mode BAUD Value Selection

The formula given for  $f_{BAUD}$  calculates the average frequency over 65536  $f_{ref}$  cycles. Although the BAUD register can be set to any value between 0 and 65536, the actual average frequency of  $f_{BAUD}$  over a single frame is more granular. The BAUD register values that will affect the average frequency over a single frame lead to an integer increase in the cycles per frame (CPF)

$$CPF = \frac{f_{ref}}{f_{BAUD}}(D+S)$$

where

# 32-bit ARM-Based Microcontrollers

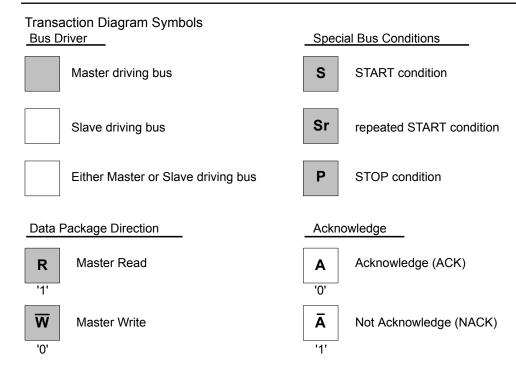

## 28.6.2 Basic Operation

## 28.6.2.1 Initialization

The following registers are enable-protected, meaning they can be written only when the I<sup>2</sup>C interface is disabled (CTRLA.ENABLE is '0'):

- Control A register (CTRLA), except Enable (CTRLA.ENABLE) and Software Reset (CTRLA.SWRST) bits

- Control B register (CTRLB), except Acknowledge Action (CTRLB.ACKACT) and Command (CTRLB.CMD) bits

- Baud register (BAUD)

- Address register (ADDR) in slave operation.

When the I<sup>2</sup>C is enabled or is being enabled (CTRLA.ENABLE=1), writing to these registers will be discarded. If the I<sup>2</sup>C is being disabled, writing to these registers will be completed after the disabling.

Enable-protection is denoted by the "Enable-Protection" property in the register description.

Before the I<sup>2</sup>C is enabled it must be configured as outlined by the following steps:

- 1. Select I<sup>2</sup>C Master or Slave mode by writing 0x4 or 0x5 to the Operating Mode bits in the CTRLA register (CTRLA.MODE).

- 2. If desired, select the SDA Hold Time value in the CTRLA register (CTRLA.SDAHOLD).

- 3. If desired, enable smart operation by setting the Smart Mode Enable bit in the CTRLB register (CTRLB.SMEN).

- 4. If desired, enable SCL low time-out by setting the SCL Low Time-Out bit in the Control A register (CTRLA.LOWTOUT).

- 5. In Master mode:

- 5.1. Select the inactive bus time-out in the Inactive Time-Out bit group in the CTRLA register (CTRLA.INACTOUT).

- 5.2. Write the Baud Rate register (BAUD) to generate the desired baud rate.

In Slave mode:

# 32-bit ARM-Based Microcontrollers

| Bit    | 15        | 14  | 13  | 12   | 11     | 10  | 9   | 8   |

|--------|-----------|-----|-----|------|--------|-----|-----|-----|

|        |           |     |     | DATA | [15:8] |     |     |     |

| Access | R/W       | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0         | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

|        |           |     |     |      |        |     |     |     |

| Bit    | 7         | 6   | 5   | 4    | 3      | 2   | 1   | 0   |

|        | DATA[7:0] |     |     |      |        |     |     |     |

| Access | R/W       | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0         | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

## Bits 31:0 - DATA[31:0]: Sample Data

This register is used to transfer data from the Rx Serializer.

Data samples received by Rx Serializer will be available for reading from RXDATA register, through the Receive Formatting Unit, according to formatting information for Rx Serializer in the RXCTRL register.

## Offset: 0x28 Reset: 0x00000000 Property: PAC Write-Protection

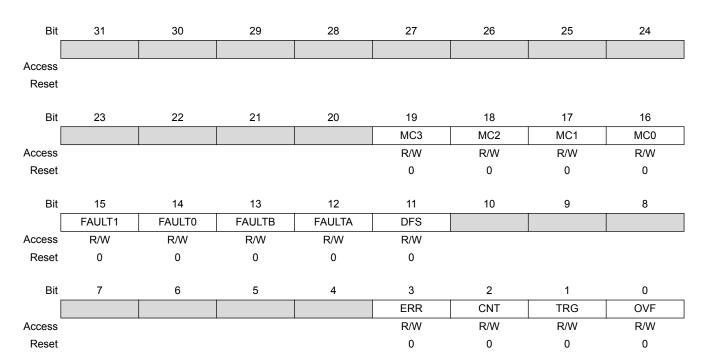

## Bits 19,18,17,16 – MCx: Match or Capture Channel x Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the corresponding Match or Capture Channel x Interrupt Disable/Enable bit, which enables the Match or Capture Channel x interrupt.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | The Match or Capture Channel x interrupt is disabled. |

| 1     | The Match or Capture Channel x interrupt is enabled.  |

## Bits 15,14 – FAULTx: Non-Recoverable Fault x Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Non-Recoverable Fault x Interrupt Disable/Enable bit, which enables the Non-Recoverable Fault x interrupt.

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | The Non-Recoverable Fault x interrupt is disabled. |

| 1     | The Non-Recoverable Fault x interrupt is enabled.  |

## Bit 13 – FAULTB: Recoverable Fault B Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Recoverable Fault B Interrupt Disable/Enable bit, which enables the Recoverable Fault B interrupt.

| Value | Description                                      |

|-------|--------------------------------------------------|

| 0     | Comparison will not start on any incoming event. |

| 1     | Comparison will start on any incoming event.     |

## Bit 4 – WINEO0: Window 0 Event Output Enable

These bits indicate whether the window 0 function can generate a peripheral event or not.

| Value | Description                 |

|-------|-----------------------------|

| 0     | Window 0 Event is disabled. |

| 1     | Window 0 Event is enabled.  |

### Bits 1,0 – COMPEOx: Comparator x Event Output Enable

These bits indicate whether the comparator x output can generate a peripheral event or not.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | COMPx event generation is disabled. |

| 1     | COMPx event generation is enabled.  |

## 34.8.4 Interrupt Enable Clear

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

Name:INTENCLROffset:0x04Reset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4    | 3 | 2 | 1     | 0     |

|--------|---|---|---|------|---|---|-------|-------|

|        |   |   |   | WIN0 |   |   | COMP1 | COMP0 |

| Access |   |   |   | R/W  |   |   | R/W   | R/W   |

| Reset  |   |   |   | 0    |   |   | 0     | 0     |

### Bit 4 – WIN0: Window 0 Interrupt Enable

Reading this bit returns the state of the Window 0 interrupt enable.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit disables the Window 0 interrupt.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The Window 0 interrupt is disabled. |

| 1     | The Window 0 interrupt is enabled.  |

### Bits 1,0 – COMPx: Comparator x Interrupt Enable

Reading this bit returns the state of the Comparator x interrupt enable.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit disables the Comparator x interrupt.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | The Comparator x interrupt is disabled. |

| 1     | The Comparator x interrupt is enabled.  |

## Bit 7 – SYNCBUSY: Synchronization Busy

This bit is cleared when the synchronization of registers between the clock domains is complete.

This bit is set when the synchronization of registers between clock domains is started.

## Bits 1,0 – READYx: Comparator x Ready

This bit is cleared when the comparator x output is not ready. This bit is set when the comparator x output is ready.

## 34.8.9 Status A

| Name:            | STATUSC |

|------------------|---------|

| Offset:          | 0x0A    |

| Reset:           | 0x00    |

| <b>Property:</b> | -       |

| Bit    | 7 | 6 | 5            | 4 | 3 | 2 | 1      | 0      |

|--------|---|---|--------------|---|---|---|--------|--------|

|        |   |   | WSTATE0[1:0] |   |   |   | STATE1 | STATE0 |

| Access |   |   | R            | R |   |   | R      | R      |

| Reset  |   |   | 0            | 0 |   |   | 0      | 0      |

## Bits 5:4 – WSTATE0[1:0]: Window 0 Current State

These bits show the current state of the signal if the window 0 mode is enabled.

| Value | Name   | Description             |

|-------|--------|-------------------------|

| 0x0   | ABOVE  | Signal is above window  |

| 0x1   | INSIDE | Signal is inside window |

| 0x2   | BELOW  | Signal is below window  |

| 0x3   |        | Reserved                |

### Bits 1,0 – STATEx: Comparator x Current State

This bit shows the current state of the output signal from COMPx. STATEx is valid only when STATUSB.READYx is one.

### 34.8.10 Window Control

Name:WINCTRLOffset:0x0CReset:0x00Property:PAC Write-Protection, Write-Synchronized

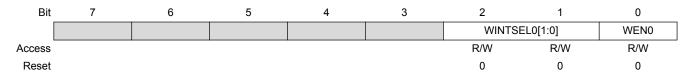

## Bits 2:1 – WINTSEL0[1:0]: Window 0 Interrupt Selection

These bits configure the interrupt mode for the comparator window 0 mode.

## 36. PTC - Peripheral Touch Controller

## 36.1 Overview

The Peripheral Touch Controller (PTC) acquires signals in order to detect touch on capacitive sensors. The external capacitive touch sensor is typically formed on a PCB, and the sensor electrodes are connected to the analog front end of the PTC through the I/O pins in the device. The PTC supports both self- and mutual-capacitance sensors.

In mutual-capacitance mode, sensing is done using capacitive touch matrices in various X-Y configurations, including indium tin oxide (ITO) sensor grids. The PTC requires one pin per X-line and one pin per Y-line.

In self-capacitance mode, the PTC requires only one pin (Y-line) for each touch sensor.

The number of available pins and the assignment of X- and Y-lines is depending on both package type and device configuration. Refer to the Configuration Summary and I/O Multiplexing table for details.

## **Related Links**

I/O Multiplexing and Considerations Configuration Summary

## 36.2 Features

- Low-power, high-sensitivity, environmentally robust capacitive touch buttons, sliders, wheels

- Supports wake-up on touch from Standby sleep mode

- Supports mutual capacitance and self-capacitance sensing

- 6/10/16 buttons in self-capacitance mode, for 32-/48-/64- pins respectively

- 60/120/256 buttons in mutual-capacitance mode, for 32-/48-/64- pins respectively

- Mix-and-match mutual-and self-capacitance sensors

- One pin per electrode no external components

- Load compensating charge sensing

- Parasitic capacitance compensation and adjustable gain for superior sensitivity

- Zero drift over the temperature and V<sub>DD</sub> range

- Auto calibration and re-calibration of sensors

- Single-shot and free-running charge measurement

- Hardware noise filtering and noise signal de-synchronization for high conducted immunity

- Selectable channel change delay allows choosing the settling time on a new channel, as required

- Acquisition-start triggered by command or through auto-triggering feature

- Low CPU utilization through interrupt on acquisition-complete

- Supported by the Atmel<sup>®</sup> QTouch<sup>®</sup> Composer development tools. See also Atmel|Start and Atmel Studio documentation.

### **Related Links**

I/O Multiplexing and Considerations Configuration Summary

# 32-bit ARM-Based Microcontrollers

| Name                                           | Description                      | Mode                                                               | V    | )D=1.8 | 8V   | VI   | DD=3. | 3V   | Units |

|------------------------------------------------|----------------------------------|--------------------------------------------------------------------|------|--------|------|------|-------|------|-------|

|                                                |                                  |                                                                    | Min. | Тур.   | Мах  | Min. | Тур.  | Max. |       |

| d <sub>M_MCKI</sub>                            | I2S MCK duty cycle               | Master mode, pin is<br>input (1b)                                  |      | 50     |      |      | 50    |      | %     |

| t <sub>M_SCKOR</sub>                           | I2S SCK rise time <sup>(3)</sup> | Master mode /<br>Capacitive load CL = 15<br>pF                     |      |        | 9    |      |       | 4.6  | ns    |

| t <sub>M_SCKOF</sub>                           | I2S SCK fall time <sup>(3)</sup> | Master mode /<br>Capacitive load CL = 15<br>pF                     |      |        | 9.7  |      |       | 4.5  | ns    |

| d <sub>M_SCKO</sub>                            | I2S SCK duty cycle               | Master mode                                                        | 45.6 |        | 50   | 45.6 |       | 50   | %     |

| f <sub>M_SCKO</sub> ,1/<br>t <sub>M_SCKO</sub> | I2S SCK frequency                | Master mode,Supposing<br>external device<br>response delay is 30ns |      |        | 8    |      |       | 9.5  | MHz   |

| f <sub>S_SCKI</sub> ,1/<br>t <sub>S_SCKI</sub> | I2S SCK frequency                | Slave mode,Supposing<br>external device<br>response delay is 30ns  |      |        | 14.4 |      |       | 14.8 | MHz   |

| d <sub>S_SCKO</sub>                            | I2S SCK duty cycle               | Slave mode                                                         |      | 50     |      |      | 50    |      | %     |

| t <sub>M_FSOV</sub>                            | FS valid time                    | Master mode                                                        |      |        | 4.1  |      |       | 4    | ns    |

| t <sub>M_FSOH</sub>                            | FS hold time                     | Master mode                                                        | -0.9 |        |      | -0.9 |       |      | ns    |

| t <sub>S_FSIS</sub>                            | FS setup time                    | Slave mode                                                         | 2.3  |        |      | 1.5  |       |      | ns    |

| t <sub>S_FSIH</sub>                            | FS hold time                     | Slave mode                                                         | 0    |        |      | 0    |       |      | ns    |

| t <sub>M_SDIS</sub>                            | Data input setup<br>time         | Master mode                                                        | 34.7 |        |      | 24.5 |       |      | ns    |

| t <sub>M_SDIH</sub>                            | Data input hold time             | Master mode                                                        | -8.2 |        |      | -8.2 |       |      | ns    |

| ts_sdis                                        | Data input setup<br>time         | Slave mode                                                         | 4.6  |        |      | 3.9  |       |      | ns    |

| t <sub>S_SDIH</sub>                            | Data input hold time             | Slave mode                                                         | 1.2  |        |      | 1.2  |       |      | ns    |

| t <sub>M_SDOV</sub>                            | Data output valid<br>time        | Master transmitter                                                 |      |        | 5.6  |      |       | 4.8  | ns    |

| t <sub>M_SDOH</sub>                            | Data output hold time            | Master transmitter                                                 | -0.5 |        |      | -0.5 |       |      | ns    |

| t <sub>S_SDOV</sub>                            | Data output valid time           | Slave transmitter                                                  |      |        | 36.2 |      |       | 25.9 | ns    |

| t <sub>S_SDOH</sub>                            | Data output hold time            | Slave transmitter                                                  | 36   |        |      | 25.7 |       |      | ns    |

| t <sub>PDM2LS</sub>                            | Data input setup<br>time         | Master mode PDM2 Left                                              | 34.7 |        |      | 24.5 |       |      | ns    |

| t <sub>PDM2LH</sub>                            | Data input hold time             | Master mode PDM2 Left                                              | -8.2 |        |      | -8.2 |       |      | ns    |

| Table 38-27. Package Characteristics |        |  |  |  |  |  |

|--------------------------------------|--------|--|--|--|--|--|

| Moisture Sensitivity Level           | MSL1   |  |  |  |  |  |

|                                      |        |  |  |  |  |  |

| Table 38-28. Package Reference       |        |  |  |  |  |  |

| JEDEC Drawing Reference              | MO-220 |  |  |  |  |  |

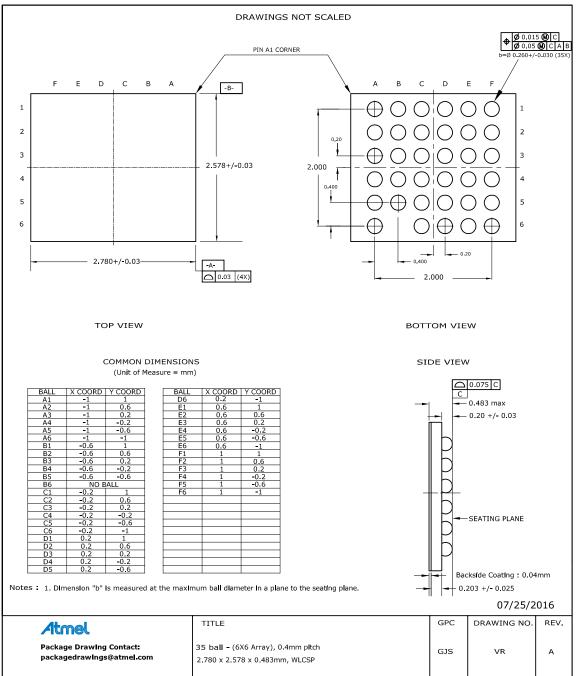

## 38.2.10 35 ball WLCSP (Device Variant C)

6 – In two ramp mode, two events will be generated per cycle, one on each ramp's end. EVCTRL.CNTSEL.END cannot be used to identify the end of a double ramp cycle. Errata reference: 12224

Errata reference: 1222

Fix/Workaround:

None

7 – If an input event triggered STOP action is performed at the same time as the counter overflows, the first pulse width of the subsequent counter start can be altered with one prescaled clock cycle. Errata reference: 12107

Fix/Workaround:

None

8 – When the RUNSTDBY bit is written after the TCC is enabled, the respective TCC APB bus is stalled and the RUNDSTBY bit in the TCC CTRLA register is not enabled-protected.

Errata reference: 12477

Fix/Workaround:

None.

9 – TCC fault filtering on inverted fault is not working. Errata reference: 12512

Fix/Workaround:

Use only non-inverted faults.

10 – When waking up from the STANDBY power save mode, the SYNCBUSY.CTRLB, SYNCBUSY.STATUS, SYNCBUSY.COUNT, SYNCBUSY.PATT, SYNCBUSY.WAVE, SYNCBUSY.PER and SYNCBUSY.CCx bits may be locked to 1.

Errata reference: 12227

### Fix/Workaround:

After waking up from STANDBY power save mode, perform a software reset of the TCC if you are using the SYNCBUSY.CTRLB, SYNCBUSY.STATUS, SYNCBUSY.COUNT, SYNCBUSY.PATT, SYNCBUSY.WAVE, SYNCBUSY.PER or SYNCBUSY.CCx bits

11 – When the Peripheral Access Controller (PAC) protection is enabled, writing to WAVE or WAVEB registers will not cause a hardware exception. Errata reference: 11468 Fix/Workaround: None

12 – If the MCx flag in the INTFLAG register is set when enabling the DMA, this will trigger an immediate DMA transfer and overwrite the current buffered value in the TCC register. Errata reference: 12155

Fix/Workaround:

None

#### 40.1.4.14 PTC

1 – WCOMP interrupt flag is not stable. The WCOMP interrupt flag will not always be set as described in the datasheet. Errata reference: 12860

| Symbol               | Parameter           | Conditions                                                                                      | Min. | Тур. | Max. | Units |

|----------------------|---------------------|-------------------------------------------------------------------------------------------------|------|------|------|-------|

| f <sub>OUT</sub>     | Output frequency    | Calibrated against a 8MHz reference at 25°C, over [-40, +85]°C, over [1.62, 3.63]V              | 7.54 | 8    | 8.19 | MHz   |

|                      |                     | Calibrated against a 8MHz reference at 25°C, at V_{DD}=3.3V                                     | 7.94 | 8    | 8.06 |       |

|                      |                     | Calibrated against a 8MHz reference at 25°C, over [1.62, 3.63]V                                 | 7.92 | 8    | 8.06 |       |

| I <sub>OSC8M</sub>   | Current consumption | IIDLEIDLE2 on OSC32K versus IDLE2 on<br>calibrated OSC8M enabled at 8MHz<br>(FRANGE=1, PRESC=0) |      | 64   | 96   | μA    |

| t <sub>startup</sub> | Startup time        |                                                                                                 | -    | 2.4  | 3.3  | μs    |

| Duty                 | Duty cycle          |                                                                                                 | -    | 50   | -    | %     |

| Table 44-47. Internal 8MHz RC Oscillato | r Characteristics (Device Variant B) |

|-----------------------------------------|--------------------------------------|

|-----------------------------------------|--------------------------------------|

## 44.8.7 Fractional Digital Phase Locked Loop (FDPLL96M) Characteristics Table 44-48. FDPLL96M Characteristics<sup>(1)</sup> (Device Variant A)

| Symbol                | Parameter           | Conditions                                                                                      | Min. | Тур. | Max. | Units |

|-----------------------|---------------------|-------------------------------------------------------------------------------------------------|------|------|------|-------|

| f <sub>IN</sub>       | Input frequency     |                                                                                                 | 32   | -    | 2000 | KHz   |

| f <sub>OUT</sub>      | Output frequency    |                                                                                                 | 48   | -    | 96   | MHz   |

| I <sub>FDPLL96M</sub> | Current consumption | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 48 MHz                                             | -    | 500  | 700  | μA    |

|                       |                     | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 96 MHz                                             | -    | 900  | 1200 |       |

| J <sub>p</sub>        | Period jitter       | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 48 MHz                                             | -    | 1.5  | 2.0  | %     |

|                       |                     | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 96 MHz                                             | -    | 3.0  | 10.0 |       |

|                       |                     | f <sub>IN</sub> = 2 MHz, f <sub>OUT</sub> = 48 MHz                                              | -    | 1.3  | 2.0  |       |

|                       |                     | f <sub>IN</sub> = 2 MHz, f <sub>OUT</sub> = 96 MHz                                              | -    | 3.0  | 7.0  |       |

| t <sub>LOCK</sub>     | Lock Time           | After start-up, time to get lock signal.<br>f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 96 MHz | -    | 1.3  | 2    | ms    |

|                       |                     | f <sub>IN</sub> = 2 MHz, f <sub>OUT</sub> = 96 MHz                                              | -    | 25   | 50   | μs    |

| Duty                  | Duty cycle          |                                                                                                 | 40   | 50   | 60   | %     |

## Table 44-49. FDPLL96M Characteristics<sup>(1)</sup> (Device Variant B, Die Revision E)

| Symbol                | Parameter           | Conditions                                          | Min. | Тур. | Max. | Units |

|-----------------------|---------------------|-----------------------------------------------------|------|------|------|-------|

| f <sub>IN</sub>       | Input frequency     |                                                     | 32   | -    | 2000 | KHz   |

| f <sub>OUT</sub>      | Output frequency    |                                                     | 48   | -    | 96   | MHz   |

| I <sub>FDPLL96M</sub> | Current consumption | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 48 MHz | -    | 500  | 740  | μA    |

|                       |                     | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 96 MHz | -    | 900  | 1262 |       |