Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 48MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 52                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                              |

| Data Converters            | A/D 20x12b; D/A 1x10b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 64-QFN (9x9)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd21j16b-mf |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Worldwide Sales and Service972 |

|--------------------------------|

|--------------------------------|

# 6. Signal Descriptions List

The following table gives details on signal names classified by peripheral.

| Signal Name                    | Function                                                       | Туре            | Active Level |  |  |  |  |  |  |

|--------------------------------|----------------------------------------------------------------|-----------------|--------------|--|--|--|--|--|--|

| Analog Compa                   | rators - AC                                                    |                 |              |  |  |  |  |  |  |

| AIN[3:0]                       | AC Analog Inputs                                               | Analog          |              |  |  |  |  |  |  |

| CMP[:0]                        | AC Comparator Outputs                                          | Digital         |              |  |  |  |  |  |  |

| Analog Digital Converter - ADC |                                                                |                 |              |  |  |  |  |  |  |

| AIN[19:0]                      | ADC Analog Inputs                                              | Analog          |              |  |  |  |  |  |  |

| VREFA                          | ADC Voltage External Reference A                               | Analog          |              |  |  |  |  |  |  |

| VREFB                          | ADC Voltage External Reference B                               | Analog          |              |  |  |  |  |  |  |

| Digital Analog                 | Converter - DAC                                                |                 |              |  |  |  |  |  |  |

| VOUT                           | DAC Voltage output                                             | Analog          |              |  |  |  |  |  |  |

| VREFA                          | DAC Voltage External Reference                                 | Analog          |              |  |  |  |  |  |  |

| External Interru               | upt Controller                                                 |                 |              |  |  |  |  |  |  |

| EXTINT[15:0]                   | External Interrupts                                            | Input           |              |  |  |  |  |  |  |

| NMI                            | External Non-Maskable Interrupt                                | Input           |              |  |  |  |  |  |  |

| Generic Clock                  | Generator - GCLK                                               |                 |              |  |  |  |  |  |  |

| GCLK_IO[7:0]                   | Generic Clock (source clock or generic clock generator output) | I/O             |              |  |  |  |  |  |  |

| Inter-IC Sound                 | Controller - I2S                                               |                 |              |  |  |  |  |  |  |

| MCK[1:0]                       | Master Clock                                                   | I/O             |              |  |  |  |  |  |  |

| SCK[1:0]                       | Serial Clock                                                   | I/O             |              |  |  |  |  |  |  |

| FS[1:0]                        | I2S Word Select or TDM Frame Sync                              | I/O             |              |  |  |  |  |  |  |

| SD[1:0]                        | Serial Data Input or Output                                    | I/O             |              |  |  |  |  |  |  |

| Power Manage                   | er - PM                                                        |                 |              |  |  |  |  |  |  |

| RESETN                         | Reset                                                          | Input           | Low          |  |  |  |  |  |  |

| Serial Commun                  | nication Interface - SERCOMx                                   | 1               |              |  |  |  |  |  |  |

| PAD[3:0]                       | SERCOM I/O Pads                                                | I/O             |              |  |  |  |  |  |  |

| System Control - SYSCTRL       |                                                                |                 |              |  |  |  |  |  |  |

| XIN                            | Crystal Input                                                  | Analog/ Digital |              |  |  |  |  |  |  |

| XIN32                          | 32kHz Crystal Input                                            | Analog/ Digital |              |  |  |  |  |  |  |

| XOUT                           | Crystal Output                                                 | Analog          |              |  |  |  |  |  |  |

| XOUT32                         | 32kHz Crystal Output                                           | Analog          |              |  |  |  |  |  |  |

# 7.2.4 GPIO Clusters

# Table 7-5. GPIO Clusters

| PACKAGE | CLUSTER |      |      |      |      |      |      |      | GP   | 10   |      |      |      |      |      |      |      | SUPPLIES<br>PINS<br>CONNECTED<br>TO THE<br>CLUSTER             |

|---------|---------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|----------------------------------------------------------------|

| 64pins  | 1       | PB31 | PB30 | PA31 | PA30 |      |      |      |      |      |      |      |      |      |      |      |      | VDDIN<br>pin56/GND<br>pin54                                    |

|         | 2       | PA28 | PA27 | PB23 | PB22 |      |      |      |      |      |      |      |      |      |      |      |      | VDDIN<br>pin56/GND<br>pin54 and<br>VDDIO pin<br>48/GND pin47   |

|         | 3       | PA25 | PA24 | PA23 | PA22 | PA21 | PA20 | PB17 | PB16 | PA19 | PA18 | PA17 | PA16 |      |      |      |      | VDDIO pin<br>48/GND pin47<br>and VDDIO<br>pin34/GND<br>pin33   |

|         | 4       | PA15 | PA14 | PA13 | PA12 | PB15 | PB14 | PB13 | PB12 | PB11 | PB10 |      |      |      |      |      |      | VDDIO pin<br>34/GND pin33<br>and VDDIO<br>pin21/GND<br>pin22   |

|         | 5       | PA11 | PA10 | PA09 | PA08 |      |      |      |      |      |      |      |      |      |      |      |      | VDDIO<br>pin21/GND<br>pin22                                    |

|         | 6       | PA07 | PA06 | PA05 | PA04 | PB09 | PB08 | PB07 | PB06 |      |      |      |      |      |      |      |      | VDDANA pin<br>8/GNDANA<br>pin7                                 |

|         | 7       | PB05 | PB04 | PA03 | PA02 | PA01 | PA00 | PB03 | PB02 | PB01 | PB00 |      |      |      |      |      |      | VDDANA pin<br>8/GNDANA<br>pin7                                 |

| 48pins  | 1       | PA31 | PA30 |      |      |      |      |      |      |      |      |      |      |      |      |      |      | VDDIN<br>pin44/GND<br>pin42                                    |

|         | 2       | PA28 | PA27 | PB23 | PB22 |      |      |      |      |      |      |      |      |      |      |      |      | VDDIN<br>pin44/GND<br>pin42 and<br>VDDIO<br>pin36/GND<br>pin35 |

|         | 3       | PA25 | PA24 | PA23 | PA22 | PA21 | PA20 | PA19 | PA18 | PA17 | PA16 | PA15 | PA14 | PA13 | PA12 | PB11 | PB10 | VDDIO<br>pin36/GND<br>pin35 and<br>VDDIO<br>pin17/GND<br>pin18 |

|         | 4       | PA11 | PA10 | PA09 | PA08 |      |      |      |      |      |      |      |      |      |      |      |      | VDDIO<br>pin17/GND<br>pin18                                    |

|         | 5       | PA07 | PA06 | PA05 | PA04 | PB09 | PB08 |      |      |      |      |      |      |      |      |      |      | VDDANA pin6/<br>GNDANA pin5                                    |

|         | 6       | PA03 | PA02 | PA01 | PA00 | PB03 | PB02 |      |      |      |      |      |      |      |      |      |      | VDDANA pin6/<br>GNDANA pin5                                    |

# Table 13-6. Available Features when Operated From The External Address Range and Device is Protected

| Features                                  | Availability From The External Address Range and Device is Protected |

|-------------------------------------------|----------------------------------------------------------------------|

| Chip-Erase command and status             | Yes                                                                  |

| CRC32                                     | Yes, only full array or full EEPROM                                  |

| CoreSight Compliant Device identification | Yes                                                                  |

| Debug communication channels              | Yes                                                                  |

| Testing of onboard memories (MBIST)       | No                                                                   |

| STATUSA.CRSTEXT clearing                  | No (STATUSA.PERR is set when attempting to do so)                    |

# 32-bit ARM-Based Microcontrollers

| Value         | Name            | Description                      |

|---------------|-----------------|----------------------------------|

| 0x00          | XOSC            | XOSC oscillator output           |

| 0x01          | GCLKIN          | Generator input pad              |

| 0x02          | GCLKGEN1        | Generic clock generator 1 output |

| 0x03          | OSCULP32K       | OSCULP32K oscillator output      |

| 0x04          | OSC32K          | OSC32K oscillator output         |

| 0x05          | XOSC32KReserved | XOSC32K oscillator output        |

| 0x06          | OSC8M           | OSC8M oscillator output          |

| 0x07          | DFLL48M         | DFLL48M output                   |

| 0x08          | FDPLL96M        | FDPLL96M output                  |

| 0x09-0x1<br>F | Reserved        | Reserved for future use          |

#### Bits 3:0 – ID[3:0]: Generic Clock Generator Selection

These bits select the generic clock generator that will be configured or read. The value of the ID bit group versus which generic clock generator is configured is shown in the next table.

A power reset will reset the GENCTRL register for all IDs, including the generic clock generator used by the RTC. If a generic clock generator ID other than generic clock generator 0 is not a source of a "locked" generic clock or a source of the RTC generic clock, a user reset will reset the GENCTRL for this ID.

After a power reset, the reset value of the GENCTRL register is as shown in the next table.

| GCLK Generator ID | Reset Value after a Power Reset |

|-------------------|---------------------------------|

| 0x00              | 0x00010600                      |

| 0x01              | 0x0000001                       |

| 0x02              | 0x00010302                      |

| 0x03              | 0x0000003                       |

| 0x04              | 0x0000004                       |

| 0x05              | 0x0000005                       |

| 0x06              | 0x0000006                       |

| 0x07              | 0x0000007                       |

| 0x08              | 0x0000008                       |

After a user reset, the reset value of the GENCTRL register is as shown in the table below.

| GCLK<br>Generator ID | Reset Value after a User Reset                                                                                                                                                                 |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00                 | 0x00010600                                                                                                                                                                                     |

| 0x01                 | 0x00000001 if the generator is not used by the RTC and not a source of a 'locked'<br>generic clock<br>No change if the generator is used by the RTC or used by a GCLK with a WRTLOCK as<br>one |

#### Bit 0 – SWRST: Software Reset

Writing a zero to this bit has no effect.

Writing a one to this bit resets all registers in the RTC, except DBGCTRL, to their initial state, and the RTC will be disabled.

Writing a one to CTRL.SWRST will always take precedence, meaning that all other writes in the same write-operation will be discarded.

Due to synchronization, there is a delay from writing CTRL.SWRST until the reset is complete. CTRL.SWRST and STATUS.SYNCBUSY will both be cleared when the reset is complete.

This bit is not enable-protected.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

#### 19.8.2 Control - MODE1

Name: CTRL Offset: 0x00 Reset: 0x0000 Property: Enable-Protected, Write-Protected, Write-Synchronized

| Bit    | 15 | 14 | 13 | 12 | 11             | 10     | 9      | 8     |  |  |

|--------|----|----|----|----|----------------|--------|--------|-------|--|--|

|        |    |    |    |    | PRESCALER[3:0] |        |        |       |  |  |

| Access |    |    |    |    | R/W            | R/W    | R/W    | R/W   |  |  |

| Reset  |    |    |    |    | 0              | 0      | 0      | 0     |  |  |

|        |    |    |    |    |                |        |        |       |  |  |

| Bit    | 7  | 6  | 5  | 4  | 3              | 2      | 1      | 0     |  |  |

|        |    |    |    |    | MOD            | E[1:0] | ENABLE | SWRST |  |  |

| Access |    |    |    |    | R/W            | R/W    | R/W    | W     |  |  |

| Reset  |    |    |    |    | 0              | 0      | 0      | 0     |  |  |

#### Bits 11:8 - PRESCALER[3:0]: Prescaler

These bits define the prescaling factor for the RTC clock source (GCLK\_RTC) to generate the counter clock (CLK\_RTC\_CNT).

These bits are not synchronized.

| PRESCALER[3:0] | Name  | Description               |

|----------------|-------|---------------------------|

| 0x0            | DIV1  | CLK_RTC_CNT = GCLK_RTC/1  |

| 0x1            | DIV2  | CLK_RTC_CNT = GCLK_RTC/2  |

| 0x2            | DIV4  | CLK_RTC_CNT = GCLK_RTC/4  |

| 0x3            | DIV8  | CLK_RTC_CNT = GCLK_RTC/8  |

| 0x4            | DIV16 | CLK_RTC_CNT = GCLK_RTC/16 |

| 0x5            | DIV32 | CLK_RTC_CNT = GCLK_RTC/32 |

| 0x6            | DIV64 | CLK_RTC_CNT = GCLK_RTC/64 |

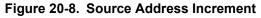

Increment Step Size bit group in the Block Transfer Control register (BTCTRL.STEPSIZE). If BTCTRL.STEPSEL=0, the step size for the source incrementation will be the size of one beat.

When source address incrementation is configured (BTCTRL.SRCINC=1), SRCADDR is calculated as follows:

If **BTCTRL**.STEPSEL=1:

$SRCADDR = SRCADDR_{START} + BTCNT \cdot (BEATSIZE + 1) \cdot 2^{STEPSIZE}$

If **BTCTRL**.STEPSEL=0:

$SRCADDR = SRCADDR_{START} + BTCNT \cdot (BEATSIZE + 1)$

- SRCADDR<sub>START</sub> is the source address of the first beat transfer in the block transfer

- BTCNT is the initial number of beats remaining in the block transfer

- BEATSIZE is the configured number of bytes in a beat

- STEPSIZE is the configured number of beats for each incrementation

The following figure shows an example where DMA channel 0 is configured to increment the source address by one beat after each beat transfer (BTCTRL.SRCINC=1), and DMA channel 1 is configured to increment the source address by two beats (BTCTRL.SRCINC=1, BTCTRL.STEPSEL=1, and BTCTRL.STEPSIZE=0x1). As the destination address for both channels are peripherals, destination incrementation is disabled (BTCTRL.DSTINC=0).

Incrementation for the destination address of a block transfer is enabled by setting the Destination Address Incrementation Enable bit in the Block Transfer Control register (BTCTRL.DSTINC=1). The step size of the incrementation is configurable by clearing BTCTRL.STEPSEL=0 and writing BTCTRL.STEPSIZE to the desired step size. If BTCTRL.STEPSEL=1, the step size for the destination incrementation will be the size of one beat.

When the destination address incrementation is configured (BTCTRL.DSTINC=1), SRCADDR must be set and calculated as follows:

| $DSTADDR = DSTADDR_{START} + BTCNT \bullet (BEATSIZE + 1) \bullet 2^{STEPSIZE}$ | where BTCTRL.STEPSEL is zero |

|---------------------------------------------------------------------------------|------------------------------|

| $DSTADDR = DSTADDR_{START} + BTCNT \bullet (BEATSIZE + 1)$                      | where BTCTRL.STEPSEL is one  |

- DSTADDR<sub>START</sub> is the destination address of the first beat transfer in the block transfer

- BTCNT is the initial number of beats remaining in the block transfer

DMAC or CRC module is enabled, the Reset request will be ignored and the DMAC will return an access error.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no Reset operation ongoing. |

| 1     | A Reset operation is ongoing.        |

#### 20.8.2 CRC Control

Name:CRCCTRLOffset:0x02Reset:0x0000Property:PAC Write-Protection, Enable-Protected

| Bit    | 15 | 14 | 13  | 12          | 11    | 10       | 9      | 8          |  |  |

|--------|----|----|-----|-------------|-------|----------|--------|------------|--|--|

|        |    |    |     | CRCSRC[5:0] |       |          |        |            |  |  |

| Access |    |    | R/W | R/W         | R/W   | R/W      | R/W    | R/W        |  |  |

| Reset  |    |    | 0   | 0           | 0     | 0        | 0      | 0          |  |  |

|        |    |    |     |             |       |          |        |            |  |  |

| Bit    | 7  | 6  | 5   | 4           | 3     | 2        | 1      | 0          |  |  |

|        |    |    |     |             | CRCPC | DLY[1:0] | CRCBEA | TSIZE[1:0] |  |  |

| Access |    |    |     |             | R/W   | R/W      | R/W    | R/W        |  |  |

| Reset  |    |    |     |             | 0     | 0        | 0      | 0          |  |  |

| Reset  |    |    |     |             | 0     | 0        | 0      | 0          |  |  |

#### Bits 13:8 – CRCSRC[5:0]: CRC Input Source

These bits select the input source for generating the CRC, as shown in the table below. The selected source is locked until either the CRC generation is completed or the CRC module is disabled. This means the CRCSRC cannot be modified when the CRC operation is ongoing. The lock is signaled by the CRCBUSY status bit. CRC generation complete is generated and signaled from the selected source when used with the DMA channel.

| Value         | Name  | Description    |

|---------------|-------|----------------|

| 0x00          | NOACT | No action      |

| 0x01          | IO    | I/O interface  |

| 0x02-0x1<br>F | -     | Reserved       |

| 0x20          | CHN   | DMA channel 0  |

| 0x21          | CHN   | DMA channel 1  |

| 0x22          | CHN   | DMA channel 2  |

| 0x23          | CHN   | DMA channel 3  |

| 0x24          | CHN   | DMA channel 4  |

| 0x25          | CHN   | DMA channel 5  |

| 0x26          | CHN   | DMA channel 6  |

| 0x27          | CHN   | DMA channel 7  |

| 0x28          | CHN   | DMA channel 8  |

| 0x29          | CHN   | DMA channel 9  |

| 0x2A          | CHN   | DMA channel 10 |

| 0x2B          | CHN   | DMA channel 11 |

| 0x2C          | CHN   | DMA channel 12 |

| 0x2D          | CHN   | DMA channel 13 |

# 20.9 Register Summary - SRAM

| Offset | Name              | Bit Pos. |                |                 |               |           |             |       |          |  |  |

|--------|-------------------|----------|----------------|-----------------|---------------|-----------|-------------|-------|----------|--|--|

| 0x00   | BTCTRL            | 7:0      |                |                 | BLOCKACT[1:0] |           | EVOSEL[1:0] |       | VALID    |  |  |

| 0x01   | BICIRL            | 15:8     | STEPSIZE[2:0]  |                 | STEPSEL       | DSTINC    | SRCINC      | BEATS | IZE[1:0] |  |  |

| 0x02   | BTCNT             | 7:0      |                |                 | BTCN          | T[7:0]    |             |       |          |  |  |

| 0x03   | BICNI             | 15:8     |                |                 | BTCN          | T[15:8]   |             |       |          |  |  |

| 0x04   |                   | 7:0      |                |                 | SRCAD         | DR[7:0]   |             |       |          |  |  |

| 0x05   | SRCADDR           | 15:8     | SRCADDR[15:8]  |                 |               |           |             |       |          |  |  |

| 0x06   | SRCADDR           | 23:16    | SRCADDR[23:16] |                 |               |           |             |       |          |  |  |

| 0x07   |                   | 31:24    |                | SRCADDR[31:24]  |               |           |             |       |          |  |  |

| 0x08   |                   | 7:0      |                |                 | DSTAD         | DR[7:0]   |             |       |          |  |  |

| 0x09   | DSTADDR           | 15:8     |                | DSTADDR[15:8]   |               |           |             |       |          |  |  |

| 0x0A   | DSTADDR           | 23:16    |                |                 | DSTADD        | R[23:16]  |             |       |          |  |  |

| 0x0B   |                   | 31:24    |                | DSTADDR[31:24]  |               |           |             |       |          |  |  |

| 0x0C   | 7:0 DESCADDR[7:0] |          |                |                 |               |           |             |       |          |  |  |

| 0x0D   | DESCADDR          | 15:8     |                | DESCADDR[15:8]  |               |           |             |       |          |  |  |

| 0x0E   | DESCADDR          | 23:16    |                |                 | DESCADI       | DR[23:16] |             |       |          |  |  |

| 0x0F   |                   | 31:24    |                | DESCADDR[31:24] |               |           |             |       |          |  |  |

# 20.10 Register Description - SRAM

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to Register Access Protection.

Some registers are enable-protected, meaning they can only be written when the peripheral is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

#### 20.10.1 Block Transfer Control

The BTCTRL register offset is relative to (BASEADDR or WRBADDR) + Channel Number \* 0x10

Name: BTCTRL Offset: 0x00 Reset: -Property: -

| Bit    | 15            | 14 | 13 | 12      | 11     | 10     | 9      | 8       |

|--------|---------------|----|----|---------|--------|--------|--------|---------|

|        | STEPSIZE[2:0] |    |    | STEPSEL | DSTINC | SRCINC | BEATSI | ZE[1:0] |

| Access |               |    |    |         |        |        |        |         |

|        |               |    |    |         |        |        |        |         |

Reset

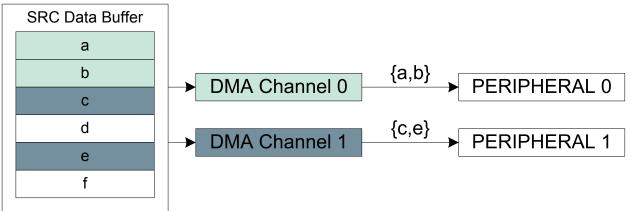

# 24. EVSYS – Event System

### 24.1 Overview

The Event System (EVSYS) allows autonomous, low-latency and configurable communication between peripherals.

Several peripherals can be configured to generate and/or respond to signals known as events. The exact condition to generate an event, or the action taken upon receiving an event, is specific to each peripheral. Peripherals that respond to events are called event users. Peripherals that generate events are called event generators. A peripheral can have one or more event generators and can have one or more event users.

Communication is made without CPU intervention and without consuming system resources such as bus or RAM bandwidth. This reduces the load on the CPU and other system resources, compared to a traditional interrupt-based system.

# 24.2 Features

- 12 configurable event channels, where each channel can:

- Be connected to any event generator.

- Provide a pure asynchronous, resynchronized or synchronous path

- 74 event generators.

- 29 event users.

- Configurable edge detector.

- Peripherals can be event generators, event users, or both.

- SleepWalking and interrupt for operation in sleep modes.

- Software event generation.

- Each event user can choose which channel to respond to.

## 24.3 Block Diagram

#### Figure 24-1. Event System Block Diagram

#### Bit 7 – ERROR: Error Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Error Interrupt Enable bit, which enables the Error interrupt.

| Value | Description                  |

|-------|------------------------------|

| 0     | Error interrupt is disabled. |

| 1     | Error interrupt is enabled.  |

#### Bit 3 – SSL: Slave Select Low Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Slave Select Low Interrupt Enable bit, which enables the Slave Select Low interrupt.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | Slave Select Low interrupt is disabled. |

| 1     | Slave Select Low interrupt is enabled.  |

#### **Bit 2 – RXC: Receive Complete Interrupt Enable**

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Receive Complete Interrupt Enable bit, which enables the Receive Complete interrupt.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | Receive Complete interrupt is disabled. |

| 1     | Receive Complete interrupt is enabled.  |

#### **Bit 1 – TXC: Transmit Complete Interrupt Enable**

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Transmit Complete Interrupt Enable bit, which enables the Transmit Complete interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | Transmit Complete interrupt is disabled. |

| 1     | Transmit Complete interrupt is enabled.  |

#### Bit 0 – DRE: Data Register Empty Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Data Register Empty Interrupt Enable bit, which enables the Data Register Empty interrupt.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | Data Register Empty interrupt is disabled. |

| 1     | Data Register Empty interrupt is enabled.  |

#### 27.8.6 Interrupt Flag Status and Clear

| Name:   | INTFLAG |

|---------|---------|

| Offset: | 0x18    |

| Reset:  | 0x00    |

- Data register (DATA)

- Address register (ADDR)

Optional PAC Write-Protection is denoted by the "PAC Write-Protection" property in each individual register description.

Write-protection does not apply to accesses through an external debugger.

#### Related Links

PAC - Peripheral Access Controller

#### 28.5.9 Analog Connections

Not applicable.

#### 28.6 Functional Description

#### 28.6.1 Principle of Operation

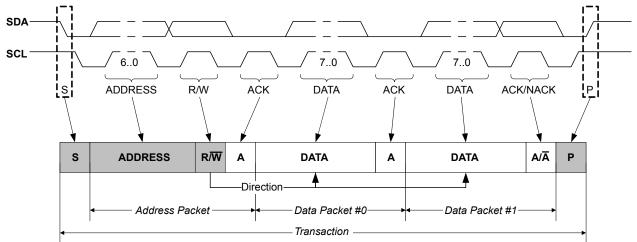

The I<sup>2</sup>C interface uses two physical lines for communication:

- Serial Data Line (SDA) for packet transfer

- Serial Clock Line (SCL) for the bus clock

A transaction starts with the I<sup>2</sup>C master sending the start condition, followed by a 7-bit address and a direction bit (read or write to/from the slave).

The addressed I<sup>2</sup>C slave will then acknowledge (ACK) the address, and data packet transactions can begin. Every 9-bit data packet consists of 8 data bits followed by a one-bit reply indicating whether the data was acknowledged or not.

If a data packet is not acknowledged (NACK), whether by the I<sup>2</sup>C slave or master, the I<sup>2</sup>C master takes action by either terminating the transaction by sending the stop condition, or by sending a repeated start to transfer more data.

The figure below illustrates the possible transaction formats and Transaction Diagram Symbols explains the transaction symbols. These symbols will be used in the following descriptions.

#### Figure 28-2. Basic I<sup>2</sup>C Transaction Diagram

Reset: 0x0000 Property: PAC Write-Protection

| Bit    | 15 | 14 | 13    | 12    | 11 | 10 | 9      | 8      |

|--------|----|----|-------|-------|----|----|--------|--------|

|        |    |    | TXUR1 | TXUR0 |    |    | TXRDY1 | TXRDY0 |

| Access |    |    | R/W   | R/W   |    |    | R/W    | R/W    |

| Reset  |    |    | 0     | 0     |    |    | 0      | 0      |

|        |    |    |       |       |    |    |        |        |

| Bit    | 7  | 6  | 5     | 4     | 3  | 2  | 1      | 0      |

|        |    |    | RXOR1 | RXOR0 |    |    | RXRDY1 | RXRDY0 |

| Access |    |    | R/W   | R/W   |    |    | R/W    | R/W    |

| Reset  |    |    | 0     | 0     |    |    | 0      | 0      |

| Reset  |    |    | 0     | 0     |    |    | 0      | 0      |

#### Bits 13,12 – TXURx : Transmit Underrun x Interrupt Enable [x=1..0]

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Transmit Underrun x Interrupt Enable bit, which disables the Transmit Underrun x interrupt.

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | The Transmit Underrun x interrupt is disabled. |

| 1     | The Transmit Underrun x interrupt is enabled.  |

#### Bits 9,8 – TXRDYx : Transmit Ready x Interrupt Enable [x=1..0]

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Transmit Ready x Interrupt Enable bit, which disables the Transmit Ready x interrupt.

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | The Transmit Ready x interrupt is disabled. |

| 1     | The Transmit Ready x interrupt is enabled.  |

#### Bits 4,5 – RXORx : Receive Overrun x Interrupt Enable [x=1..0]

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Receive Overrun x Interrupt Enable bit, which disables the Receive Overrun x interrupt.

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | The Receive Overrun x interrupt is disabled. |

| 1     | The Receive Overrun x interrupt is enabled.  |

#### Bits 1,0 – RXRDYx : Receive Ready x Interrupt Enable [x=1..0]

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Receive Ready x Interrupt Enable bit, which disables the Receive Ready x interrupt.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The Receive Ready x interrupt is disabled. |

| 1     | The Receive Ready x interrupt is enabled.  |

inverted high side (HS) of the waveform output with optional dead-time insertion between LS and HS switching. The SWAP unit can swap the LS and HS pin outputs, and can be used for fast decay motor control.

The pattern generation unit can be used to generate synchronized waveforms with constant logic level on TCC UPDATE conditions. This is useful for easy stepper motor and full bridge control.

The non-recoverable fault module enables event controlled fault protection by acting directly on the generated waveforms of the timer/counter compare channel outputs. When a non-recoverable fault condition is detected, the output waveforms are forced to a safe and pre-configured value that is safe for the application. This is typically used for instant and predictable shut down and disabling high current or voltage drives.

The count event sources (TCE0 and TCE1) are shared with the non-recoverable fault extension. The events can be optionally filtered. If the filter options are not used, the non-recoverable faults provide an immediate asynchronous action on waveform output, even for cases where the clock is not present. For further details on how to configure asynchronous events routing, refer to section *EVSYS – Event System*.

#### **Related Links**

EVSYS – Event System

#### 31.6.2 Basic Operation

#### 31.6.2.1 Initialization

The following registers are enable-protected, meaning that they can only be written when the TCC is disabled(CTRLA.ENABLE=0):

- Control A (CTRLA) register, except Run Standby (RUNSTDBY), Enable (ENABLE) and Software Reset (SWRST) bits

- Recoverable Fault n Control registers (FCTRLA and FCTRLB)

- Waveform Extension Control register (WEXCTRL)

- Drive Control register (DRVCTRL)

- Event Control register (EVCTRL)

Enable-protected bits in the CTRLA register can be written at the same time as CTRLA.ENABLE is written to '1', but not at the same time as CTRLA.ENABLE is written to '0'. Enable-protection is denoted by the "Enable-Protected" property in the register description.

Before the TCC is enabled, it must be configured as outlined by the following steps:

- 1. Enable the TCC bus clock (CLK\_TCCx\_APB).

- 2. If Capture mode is required, enable the channel in capture mode by writing a '1' to the Capture Enable bit in the Control A register (CTRLA.CPTEN).

Optionally, the following configurations can be set before enabling TCC:

- 1. Select PRESCALER setting in the Control A register (CTRLA.PRESCALER).

- 2. Select Prescaler Synchronization setting in Control A register (CTRLA.PRESCSYNC).

- 3. If down-counting operation is desired, write the Counter Direction bit in the Control B Set register (CTRLBSET.DIR) to '1'.

- 4. Select the Waveform Generation operation in the WAVE register (WAVE.WAVEGEN).

- 5. Select the Waveform Output Polarity in the WAVE register (WAVE.POL).

- 6. The waveform output can be inverted for the individual channels using the Waveform Output Invert Enable bit group in the Driver register (DRVCTRL.INVEN).

#### Bits 7:5 – CMD[2:0]: TCC Command

These bits can be used for software control of re-triggering and stop commands of the TCC. When a command has been executed, the CMD bit field will read back zero. The commands are executed on the next prescaled GCLK\_TCC clock cycle.

Writing zero to this bit group has no effect.

Writing a '1' to any of these bits will clear the pending command.

| Value | Name      | Description                               |

|-------|-----------|-------------------------------------------|

| 0x0   | NONE      | No action                                 |

| 0x1   | RETRIGGER | Clear start, restart or retrigger         |

| 0x2   | STOP      | Force stop                                |

| 0x3   | UPDATE    | Force update of double buffered registers |

| 0x4   | READSYNC  | Force COUNT read synchronization          |

#### Bits 4:3 – IDXCMD[1:0]: Ramp Index Command

These bits can be used to force cycle A and cycle B changes in RAMP2 and RAMP2A operation. On timer/counter update condition, the command is executed, the IDX flag in STATUS register is updated and the IDXCMD command is cleared.

Writing zero to these bits has no effect.

Writing a '1' to any of these bits will clear the pending command.

| Value | Name    | Description                                                     |

|-------|---------|-----------------------------------------------------------------|

| 0x0   | DISABLE | DISABLE Command disabled: IDX toggles between cycles A and B    |

| 0x1   | SET     | Set IDX: cycle B will be forced in the next cycle               |

| 0x2   | CLEAR   | Clear IDX: cycle A will be forced in next cycle                 |

| 0x3   | HOLD    | Hold IDX: the next cycle will be the same as the current cycle. |

#### Bit 2 – ONESHOT: One-Shot

This bit controls one-shot operation of the TCC. When one-shot operation is enabled, the TCC will stop counting on the next overflow/underflow condition or on a stop command.

Writing a '0' to this bit has no effect

Writing a '1' to this bit will disable the one-shot operation.

| Value | Description                                                                        |

|-------|------------------------------------------------------------------------------------|

| 0     | The TCC will update the counter value on overflow/underflow condition and continue |

|       | operation.                                                                         |

| 1     | The TCC will stop counting on the next underflow/overflow condition.               |

#### Bit 1 – LUPD: Lock Update

This bit controls the update operation of the TCC buffered registers.

When CTRLB.LUPD is set, no any update of the registers with value of its buffered register is performed on hardware UPDATE condition. Locking the update ensures that all buffer registers are valid before an hardware update is performed. After all the buffer registers are loaded correctly, the buffered registers can be unlocked.

This bit has no effect when input capture operation is enabled.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will enable updating.

| Symbol | Parameter                  | Conditions                            |                        | Min.   | Тур.   | Max.   | Units |

|--------|----------------------------|---------------------------------------|------------------------|--------|--------|--------|-------|

| RES    | Input resolution           |                                       |                        | -      | -      | 10     | Bits  |

| INL    | Integral non-linearity     | V <sub>REF</sub> = Ext 1.0V           | V <sub>DD</sub> = 1.6V | 0.75   | 1.1    | 2.5    | LSB   |

|        |                            |                                       | V <sub>DD</sub> = 3.6V | 0.6    | 1.2    | 1.5    |       |

|        |                            | $V_{REF} = V_{DDANA}$                 | V <sub>DD</sub> = 1.6V | 1.4    | 2.2    | 2.5    |       |

|        |                            |                                       | V <sub>DD</sub> = 3.6V | 0.9    | 1.4    | 1.5    |       |

|        |                            | V <sub>REF</sub> = INT1V              | V <sub>DD</sub> = 1.6V | 0.75   | 1.3    | 1.5    |       |

|        |                            |                                       | V <sub>DD</sub> = 3.6V | 0.8    | 1.2    | 1.5    |       |

| DNL    | Differential non-linearity | V <sub>REF</sub> = Ext 1.0V           | V <sub>DD</sub> = 1.6V | +/-0.9 | +/-1.2 | +/-1.5 | LSB   |

|        |                            |                                       | V <sub>DD</sub> = 3.6V | +/-0.9 | +/-1.1 | +/-1.2 |       |

|        |                            | V <sub>REF</sub> = V <sub>DDANA</sub> | V <sub>DD</sub> = 1.6V | +/-1.1 | +/-1.5 | +/-1.7 |       |

|        |                            |                                       | V <sub>DD</sub> = 3.6V | +/-1.0 | +/-1.1 | +/-1.2 |       |

|        |                            | V <sub>REF</sub> = INT1V              | V <sub>DD</sub> = 1.6V | +/-1.1 | +/-1.4 | +/-1.5 |       |

|        |                            |                                       | V <sub>DD</sub> = 3.6V | +/-1.0 | +/-1.5 | +/-1.6 |       |

|        | Gain error                 | Ext. V <sub>REF</sub>                 |                        | +/-1.5 | +/-5   | +/-10  | mV    |

|        | Offset error               | Ext. V <sub>REF</sub>                 |                        | +/-2   | +/-3   | +/-6   | mV    |

# Table 37-33. Accuracy Characteristics<sup>(1)</sup> (Device Variant B and C)

| Symbol | Parameter                  | Conditions                            |                        | Min.    | Тур.    | Max.    | Units |

|--------|----------------------------|---------------------------------------|------------------------|---------|---------|---------|-------|

| RES    | Input resolution           |                                       |                        | -       | -       | 10      | Bits  |

| INL    | Integral non-linearity     | V <sub>REF</sub> = Ext 1.0V           | V <sub>DD</sub> = 1.6V | 0.7     | 0.75    | 2       | LSB   |

|        |                            |                                       | V <sub>DD</sub> = 3.6V | 0.6     | 0.65    | 1.5     |       |

|        |                            | $V_{REF} = V_{DDANA}$                 | V <sub>DD</sub> = 1.6V | 0.6     | 0.85    | 2       |       |

|        |                            |                                       | V <sub>DD</sub> = 3.6V | 0.5     | 0.8     | 1.5     |       |

|        |                            | V <sub>REF</sub> = INT1V              | V <sub>DD</sub> = 1.6V | 0.5     | 0.75    | 1.5     |       |

|        |                            |                                       | V <sub>DD</sub> = 3.6V | 0.7     | 0.8     | 1.5     |       |

| DNL    | Differential non-linearity | V <sub>REF</sub> = Ext 1.0V           | V <sub>DD</sub> = 1.6V | +/-0.3  | +/-0.4  | +/-1.0  | LSB   |

|        |                            |                                       | V <sub>DD</sub> = 3.6V | +/-0.25 | +/-0.4  | +/-0.75 |       |

|        |                            | V <sub>REF</sub> = V <sub>DDANA</sub> | V <sub>DD</sub> = 1.6V | +/-0.4  | +/-0.55 | +/-1.5  |       |

|        |                            |                                       | V <sub>DD</sub> = 3.6V | +/-0.2  | +/-0.3  | +/-0.75 |       |

|        |                            | V <sub>REF</sub> = INT1V              | V <sub>DD</sub> = 1.6V | +/-0.5  | +/-0.7  | +/-1.5  |       |

|        |                            |                                       | V <sub>DD</sub> = 3.6V | +/-0.4  | +/-0.7  | +/-1.5  |       |

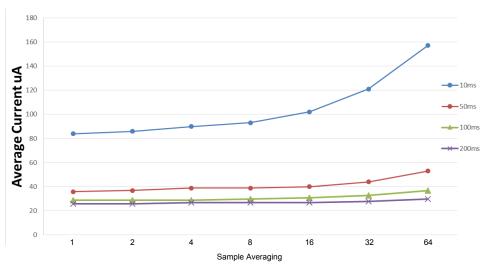

Figure 37-15. 1 Sensor / PTC\_GCLK = 2MHz / FREQ\_MODE\_HOP

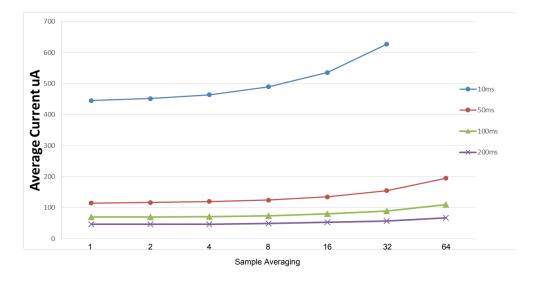

Figure 37-16. 10 Sensor / PTC\_GCLK = 4MHz / FREQ\_MODE\_NONE

|                  | Errata reference: 12164<br>Fix/Workaround:<br>Do a power cycle to reset the GCLK generators after an external XOSC32K<br>failure.                                                                                                                                                                                                                                                                                                                                                                              |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40.1.4.2 DSU     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                  | <ul> <li>1 – If a debugger has issued a DSU Cold-Plugging procedure and then released the CPU from the resulting ""CPU Reset Extension"", the CPU will be held in ""CPU Reset Extension"" after any upcoming reset event.</li> <li>Errata reference: 12015</li> <li>Fix/workaround:</li> <li>The CPU must be released from the ""CPU Reset Extension"" either by writing a one in the DSU STATUSA.CRSTEXT register or by applying an external reset with SWCLK high or by power cycling the device.</li> </ul> |

|                  | 2 – The MBIST ""Pause-on-Error"" feature is not functional on this device.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                  | Errata reference: 14324<br>Fix/Workaround:<br>Do not use the ""Pause-on-Error"" feature.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 40.1.4.3 PM      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                  | <ul> <li>1 – In debug mode, if a watchdog reset occurs, the debug session is lost.</li> <li>Errata reference: 12196</li> <li>Fix/Workaround:</li> <li>A new debug session must be restart after a watchdog reset.</li> </ul>                                                                                                                                                                                                                                                                                   |

| 40.1.4.4 DFLL48M |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                  | <ul> <li>1 – The DFLL clock must be requested before being configured otherwise a write access to a DFLL register can freeze the device.</li> <li>Errata reference: 9905</li> <li>Fix/Workaround:</li> <li>Write a zero to the DFLL ONDEMAND bit in the DFLLCTRL register before configuring the DFLL module.</li> </ul>                                                                                                                                                                                       |

|                  | <ul> <li>2 – The DFLL status bits in the PCLKSR register during the USB clock recovery mode can be wrong after a USB suspend state.</li> <li>Errata reference: 11938</li> <li>Fix/Workaround:</li> <li>Do not monitor the DFLL status bits in the PCLKSR register during the USB clock recovery mode.</li> </ul>                                                                                                                                                                                               |

|                  | 3 – If the DFLL48M reaches the maximum or minimum COARSE or<br>FINE calibration values during the locking sequence, an out of bounds<br>interrupt will be generated. These interrupts will be generated even if<br>the final calibration values at DFLL48M lock are not at maximum or<br>minimum, and might therefore be false out of bounds interrupts.<br>Errata reference: 10669<br>Fix/Workaround:                                                                                                         |

3 – Advance capture mode (CAPTMIN CAPTMAX LOCMIN LOCMAX DERIV0) doesn't work if an upper channel is not in one of these mode. Example: when CC[0]=CAPTMIN, CC[1]=CAPTMAX, CC[2]=CAPTEN, and CC[3]=CAPTEN, CAPTMIN and CAPTMAX won't work. Errata reference: 14817 Fix/Workaround: Basic capture mode must be set in lower channel and advance capture mode in upper channel. Example: CC[0]=CAPTEN, CC[1]=CAPTEN, CC[2]=CAPTMIN, CC[3]=CAPTMAX All capture will be done as expected.

# 40.3 Device Variant C

The device variant (last letter of the ordering number) is independent of the die revision (DSU.DID.REVISION): The device variant denotes functional differences, whereas the die revision marks evolution of the die.

#### 40.3.1 Die Revision F

40.3.1.1 Device

#### 1 – The SYSTICK calibration value is incorrect. Errata reference: 14155 Fix/Workaround:

The correct SYSTICK calibration value is 0x4000000. This value should not be used to initialize the Systick RELOAD value register, which should be initialized instead with a value depending on the main clock frequency and on the tick period required by the application. For a detailed description of the SYSTICK module, refer to the official ARM Cortex-M0+ documentation.

2 – On pin PA24 and PA25 the pull-up and pull-down configuration is not disabled automatically when alternative pin function is enabled except for USB.

#### Errata reference: 12368

#### Fix/Workaround:

For pin PA24 and PA25, the GPIO pull-up and pull-down must be disabled before enabling alternative functions on them.

3 – If APB clock is stopped and GCLK clock is running, APB read access to read-synchronized registers will freeze the system. The CPU and the DAP AHB-AP are stalled, as a consequence debug operation is impossible.

#### Errata reference: 10416

#### Fix/Workaround:

Do not make read access to read-synchronized registers when APB clock is stopped and GCLK is running. To recover from this situation, power cycle the device or reset the device using the RESETN pin.

4 – If the external XOSC32K is broken, neither the external pin RST nor the GCLK software reset can reset the GCLK generators using XOSC32K as source clock. Errata reference: 12164 Fix/Workaround:

# 32-bit ARM-Based Microcontrollers

| Symbol            | Parameter                              | Conditions                                                              | Min. | Тур. | Max. | Units |

|-------------------|----------------------------------------|-------------------------------------------------------------------------|------|------|------|-------|

| I <sub>DFLL</sub> | Power consumption on $V_{\text{DDIN}}$ | f <sub>REF</sub> = 32 .768kHz                                           | -    | 425  | 482  | μA    |

| t <sub>LOCK</sub> | Lock time                              | f <sub>REF</sub> = 32 .768kHz<br>DFLLVAL.COARSE = DFLL48M<br>COARSE CAL | 100  | 200  | 500  | μs    |

|                   |                                        | DFLLVAL.FINE = 512                                                      |      |      |      |       |

|                   |                                        | DFLLCTRL.BPLCKC = 1                                                     |      |      |      |       |

|                   |                                        | DFLLCTRL.QLDIS = 0                                                      |      |      |      |       |

|                   |                                        | DFLLCTRL.CCDIS = 1                                                      |      |      |      |       |

|                   |                                        | DFLLMUL.FSTEP = 10                                                      |      |      |      |       |

|                   |                                        |                                                                         |      |      |      |       |

# Table 44-41. DFLL48M Characteristics - Closed Loop Mode<sup>(1)</sup>, Device Variant B

| Symbol            | Parameter                              | Conditions                                                              | Min.  | Тур.   | Max.  | Units |

|-------------------|----------------------------------------|-------------------------------------------------------------------------|-------|--------|-------|-------|

| f <sub>OUT</sub>  | Average Output<br>frequency            | f <sub>REF</sub> = 32 .768kHz                                           | 47.76 | 48     | 48.24 | MHz   |

| f <sub>REF</sub>  | Reference frequency                    |                                                                         | 0.732 | 32.768 | 33    | kHz   |

| Jitter            | Cycle to Cycle jitter                  | f <sub>REF</sub> = 32 .768kHz                                           | -     | -      | 0.42  | ns    |

| I <sub>DFLL</sub> | Power consumption on $V_{\text{DDIN}}$ | f <sub>REF</sub> = 32 .768kHz                                           | -     | 403    | 453   | μA    |

| t <sub>LOCK</sub> | Lock time                              | f <sub>REF</sub> = 32 .768kHz<br>DFLLVAL.COARSE = DFLL48M<br>COARSE CAL | -     | 200    | 500   | μs    |

|                   |                                        | DFLLVAL.FINE = 512                                                      |       |        |       |       |

|                   |                                        | DFLLCTRL.BPLCKC = 1                                                     |       |        |       |       |

|                   |                                        | DFLLCTRL.QLDIS = 0                                                      |       |        |       |       |

|                   |                                        | DFLLCTRL.CCDIS = 1                                                      |       |        |       |       |

|                   |                                        | DFLLMUL.FSTEP = 10                                                      |       |        |       |       |