Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                               |

| Data Converters            | A/D 20x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-QFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd21j16b-mft |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2. Configuration Summary

|                                                         | SAM D21J            | SAM D21G            | SAM D21E            |  |

|---------------------------------------------------------|---------------------|---------------------|---------------------|--|

| Pins                                                    | 64                  | 48 (45 for WLCSP)   | 32 (35 for WLCSP)   |  |

| General Purpose I/O-pins<br>(GPIOs)                     | 52                  | 38                  | 26                  |  |

| Flash                                                   | 256/128/64/32KB     | 256/128/64/32KB     | 256/128/64/32KB     |  |

| SRAM                                                    | 32/16/8/4KB         | 32/16/8/4KB         | 32/16/8/4KB         |  |

| Timer Counter (TC) instances                            | 5                   | 3 (5 for WLCSP)     | 3                   |  |

| Waveform output channels per TC instance                | 2                   | 2                   | 2                   |  |

| Timer Counter for Control (TCC) instances               | 3                   | 3                   | 3                   |  |

| Waveform output channels per TCC                        | 8/4/2               | 8/4/2               | 6/4/2               |  |

| DMA channels                                            | 12                  | 12                  | 12                  |  |

| USB interface                                           | 1                   | 1                   | 1                   |  |

| Serial Communication<br>Interface (SERCOM)<br>instances | 6                   | 6                   | 4                   |  |

| Inter-IC Sound (I <sup>2</sup> S) interface             | 1                   | 1                   | 1                   |  |

| Analog-to-Digital Converter<br>(ADC) channels           | 20                  | 14                  | 10                  |  |

| Analog Comparators (AC)                                 | 2                   | 2                   | 2                   |  |

| Digital-to-Analog Converter<br>(DAC) channels           | 1                   | 1                   | 1                   |  |

| Real-Time Counter (RTC)                                 | Yes                 | Yes                 | Yes                 |  |

| RTC alarms                                              | 1                   | 1                   | 1                   |  |

| RTC compare values                                      | One 32-bit value or | One 32-bit value or | One 32-bit value or |  |

|                                                         | two 16-bit values   | two 16-bit values   | two 16-bit values   |  |

| External Interrupt lines                                | 16                  | 16                  | 16                  |  |

| Peripheral Touch Controller<br>(PTC) X and Y lines      | 16x16               | 12x10 10x6          |                     |  |

| Maximum CPU frequency                                   | 48MHz               |                     |                     |  |

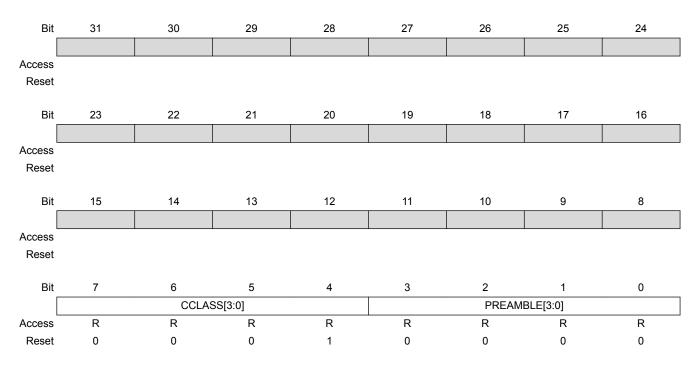

| Reset:    | 0x0000010 |

|-----------|-----------|

| Property: | -         |

### Bits 7:4 – CCLASS[3:0]: Component Class

These bits will always return 0x1 when read indicating that this ARM CoreSight component is ROM table (refer to the ARM Debug Interface v5 Architecture Specification at http://www.arm.com).

#### Bits 3:0 – PREAMBLE[3:0]: Preamble

These bits will always return 0x0 when read.

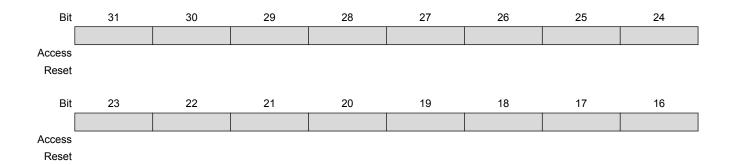

### 13.13.21 Component Identification 2

Name:

CID2

Offset:

0x1FF8

Reset:

0x00000005

Property:

Bits 7:0 – PREAMBLEB2[7:0]: Preamble Byte 2

These bits will always return 0x05 when read.

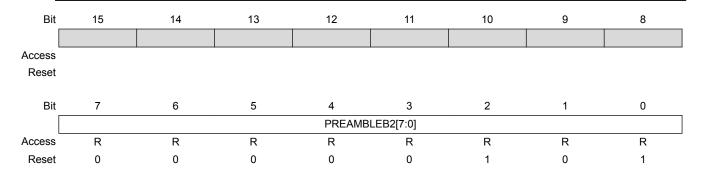

### 13.13.22 Component Identification 3

Name:CID3Offset:0x1FFCReset:0x00000B1Property:-

| Bit    | 31 | 30 | 29 | 28     | 27 | 26 | 25 | 24 |

|--------|----|----|----|--------|----|----|----|----|

|        |    |    |    |        |    |    |    |    |

| Access |    |    |    |        |    |    |    |    |

| Reset  |    |    |    |        |    |    |    |    |

|        |    |    |    |        |    |    |    |    |

| Bit    | 23 | 22 | 21 | 20     | 19 | 18 | 17 | 16 |

|        |    |    |    |        |    |    |    |    |

| Access |    |    |    |        |    |    |    |    |

| Reset  |    |    |    |        |    |    |    |    |

|        |    |    |    |        |    |    |    |    |

| Bit    | 15 | 14 | 13 | 12     | 11 | 10 | 9  | 8  |

|        |    |    |    |        |    |    |    |    |

| Access |    |    |    |        |    |    |    |    |

| Reset  |    |    |    |        |    |    |    |    |

|        |    |    |    |        |    |    |    |    |

| Bit    | 7  | 6  | 5  | 4      | 3  | 2  | 1  | 0  |

|        |    |    |    | PREAMB |    |    |    |    |

| Access | R  | R  | R  | R      | R  | R  | R  | R  |

| Reset  | 1  | 0  | 1  | 1      | 0  | 0  | 0  | 1  |

Bits 7:0 – PREAMBLEB3[7:0]: Preamble Byte 3

These bits will always return 0xB1 when read.

according to the Output Off Value bit. If the Output Off Value bit in GENCTRL (GENCTRL.OOV) is zero, the output clock will be low when generic clock generator is turned off. If GENCTRL.OOV=1, the output clock will be high when Generator is turned off.

In standby mode, if the clock is output (GENCTRL.OE=1), the clock on the GCLK\_IO pin is frozen to the OOV value if the Run In Standby bit in GENCTRL (GENCTRL.RUNSTDBY) is zero. If GENCTRL.RUNSTDBY=1, the GCLKGEN clock is kept running and output to GCLK\_IO.

#### 15.6.3 Generic Clock

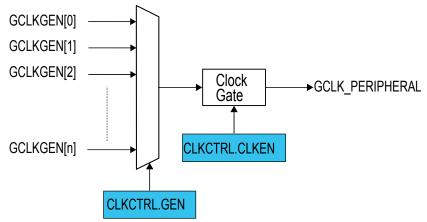

#### Figure 15-4. Generic Clock Multiplexer

### 15.6.3.1 Enabling a Generic Clock

Before a generic clock is enabled, one of the Generators must be selected as the source for the generic clock by writing to CLKCTRL.GEN. The clock source selection is individually set for each generic clock.

When a Generator has been selected, the generic clock is enabled by setting the Clock Enable bit in CLKCTRL (CLKCTRL.CLKEN=1). The CLKCTRL.CLKEN bit must be synchronized to the generic clock domain. CLKCTRL.CLKEN will continue to read as its previous state until the synchronization is complete.

#### 15.6.3.2 Disabling a Generic Clock

A generic clock is disabled by writing CLKCTRL.CLKEN=0. The SYNCBUSY bit will be cleared when this write-synchronization is complete. CLKCTRL.CLKEN will stay in its previous state until the synchronization is complete. The generic clock is gated when disabled.

#### 15.6.3.3 Selecting a Clock Source for the Generic Clock

When changing a generic clock source by writing to CLKCTRL.GEN, the generic clock must be disabled before being re-enabled it with the new clock source setting. This prevents glitches during the transition:

- 1. Write CLKCTRL.CLKEN=0

- 2. Assert that CLKCTRL.CLKEN reads '0'

- 3. Change the source of the generic clock by writing CLKCTRL.GEN

- 4. Re-enable the generic clock by writing CLKCTRL.CLKEN=1

#### 15.6.3.4 Configuration Lock

The generic clock configuration can be locked for further write accesses by setting the Write Lock bit in the CLKCTRL register (CLKCTRL.WRTLOCK). All writes to the CLKCTRL register will be ignored. It can only be unlocked by a Power Reset.

The Generator source of a locked generic clock are also locked, too: The corresponding GENCTRL and GENDIV are locked, and can be unlocked only by a Power Reset.

| GCLK<br>Generator ID | Reset Value after a User Reset                                                                                                                                                                |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x04                 | 0x0000004 if the generator is not used by the RTC and not a source of a 'locked'<br>generic clock<br>No change if the generator is used by the RTC or used by a GCLK with a WRTLOCK as<br>one |

| 0x05                 | 0x0000005 if the generator is not used by the RTC and not a source of a 'locked'<br>generic clock<br>No change if the generator is used by the RTC or used by a GCLK with a WRTLOCK as<br>one |

| 0x06                 | 0x0000006 if the generator is not used by the RTC and not a source of a 'locked' generic clock<br>No change if the generator is used by the RTC or used by a GCLK with a WRTLOCK as one       |

| 0x07                 | 0x0000007 if the generator is not used by the RTC and not a source of a 'locked'<br>generic clock<br>No change if the generator is used by the RTC or used by a GCLK with a WRTLOCK as<br>one |

| 0x08                 | 0x0000008 if the generator is not used by the RTC and not a source of a 'locked' generic clock<br>No change if the generator is used by the RTC or used by a GCLK with a WRTLOCK as one       |

| APBCDIV[2:0] | Name   | Description   |

|--------------|--------|---------------|

| 0x2          | DIV4   | Divide by 4   |

| 0x3          | DIV8   | Divide by 8   |

| 0x4          | DIV16  | Divide by 16  |

| 0x5          | DIV32  | Divide by 32  |

| 0x6          | DIV64  | Divide by 64  |

| 0x7          | DIV128 | Divide by 128 |

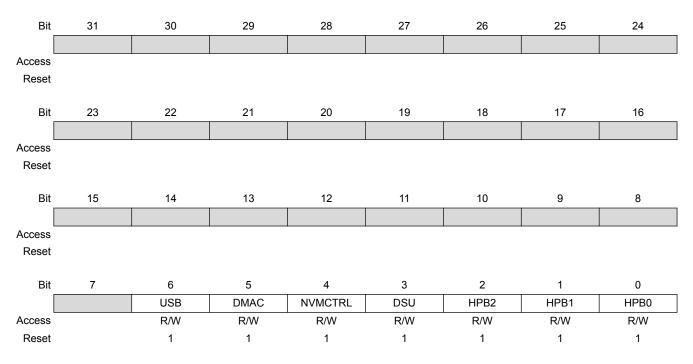

#### 16.8.7 AHB Mask

Name:AHBMASKOffset:0x14Reset:0x0000007FProperty:Write-Protected

#### Bit 6 – USB: USB AHB Clock Mask

| Value | Description                           |

|-------|---------------------------------------|

| 0     | The AHB clock for the USB is stopped. |

| 1     | The AHB clock for the USB is enabled. |

## Bit 5 – DMAC: DMAC AHB Clock Mask

| Value | Description                            |

|-------|----------------------------------------|

| 0     | The AHB clock for the DMAC is stopped. |

| 1     | The AHB clock for the DMAC is enabled. |

#### Bit 1 – XOSC32KRDY: XOSC32K Ready

This flag is cleared by writing a one to it.

This flag is set on a zero-to-one transition of the XOSC32K Ready bit in the Status register (PCLKSR.XOSC32KRDY) and will generate an interrupt request if INTENSET.XOSC32KRDY is one.

Writing a zero to this bit has no effect.

Writing a one to this bit clears the XOSC32K Ready interrupt flag.

#### Bit 0 – XOSCRDY: XOSC Ready

This flag is cleared by writing a one to it.

This flag is set on a zero-to-one transition of the XOSC Ready bit in the Status register (PCLKSR.XOSCRDY) and will generate an interrupt request if INTENSET.XOSCRDY is one.

Writing a zero to this bit has no effect.

Writing a one to this bit clears the XOSC Ready interrupt flag.

### 17.8.4 Power and Clocks Status

Name:

PCLKSR

Offset:

0x0C

Reset:

0x0000000

Property:

| Bit    | 31       | 30       | 29      | 28      | 27       | 26        | 25         | 24       |

|--------|----------|----------|---------|---------|----------|-----------|------------|----------|

|        |          |          |         |         |          |           |            |          |

| Access | R        | R        | R       | R       | R        | R         | R          | R        |

| Reset  | 0        | 0        | 0       | 0       | 0        | 0         | 0          | 0        |

|        |          |          |         |         |          |           |            |          |

| Bit    | 23       | 22       | 21      | 20      | 19       | 18        | 17         | 16       |

|        |          |          |         |         |          |           | DPLLLTO    | DPLLLCKF |

| Access | R        | R        | R       | R       | R        | R         | R          | R        |

| Reset  | 0        | 0        | 0       | 0       | 0        | 0         | 0          | 0        |

|        |          |          |         |         |          |           |            |          |

| Bit    | 15       | 14       | 13      | 12      | 11       | 10        | 9          | 8        |

|        | DPLLLCKR |          |         |         | B33SRDY  | BOD33DET  | BOD33RDY   | DFLLRCS  |

| Access | R        | R        | R       | R       | R        | R         | R          | R        |

| Reset  | 0        | 0        | 0       | 0       | 0        | 0         | 0          | 0        |

|        |          |          |         |         |          |           |            |          |

| Bit    | 7        | 6        | 5       | 4       | 3        | 2         | 1          | 0        |

|        | DFLLLCKC | DFLLLCKF | DFLLOOB | DFLLRDY | OSC8MRDY | OSC32KRDY | XOSC32KRDY | XOSCRDY  |

| Access | R        | R        | R       | R       | R        | R         | R          | R        |

| Reset  | 0        | 0        | 0       | 0       | 0        | 0         | 0          | 0        |

## Bit 17 – DPLLLTO: DPLL Lock Timeout

| Value | Description                      |

|-------|----------------------------------|

| 0     | DPLL Lock time-out not detected. |

| 1     | DPLL Lock time-out detected.     |

Name:XOSC32KOffset:0x14Reset:0x0080Property:Write-Protected

| Bit    | 15       | 14       | 13     | 12      | 11    | 10     | 9            | 8   |

|--------|----------|----------|--------|---------|-------|--------|--------------|-----|

|        |          |          |        | WRTLOCK |       |        | STARTUP[2:0] |     |

| Access |          |          |        | R/W     |       | R/W    | R/W          | R/W |

| Reset  |          |          |        | 0       |       | 0      | 0            | 0   |

|        |          |          |        |         |       |        |              |     |

| Bit    | 7        | 6        | 5      | 4       | 3     | 2      | 1            | 0   |

|        | ONDEMAND | RUNSTDBY | AAMPEN |         | EN32K | XTALEN | ENABLE       |     |

| Access | R/W      | R/W      | R/W    |         | R/W   | R/W    | R/W          |     |

| Reset  | 1        | 0        | 0      |         | 0     | 0      | 0            |     |

### Bit 12 – WRTLOCK: Write Lock

This bit locks the XOSC32K register for future writes to fix the XOSC32K configuration.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The XOSC32K configuration is not locked. |

| 1     | The XOSC32K configuration is locked.     |

### Bits 10:8 – STARTUP[2:0]: Oscillator Start-Up Time

These bits select the start-up time for the oscillator.

The OSCULP32K oscillator is used to clock the start-up counter.

Table 17-6.

Start-Up Time for 32kHz External Crystal Oscillator

| STARTUP[2:0] | Number of OSCULP32K<br>Clock Cycles | Number of XOSC32K<br>Clock Cycles | Approximate Equivalent<br>Time<br>(OSCULP = 32kHz) <sup>(1)(2)(3)</sup> |

|--------------|-------------------------------------|-----------------------------------|-------------------------------------------------------------------------|

| 0x0          | 1                                   | 3                                 | 122µs                                                                   |

| 0x1          | 32                                  | 3                                 | 1068µs                                                                  |

| 0x2          | 2048                                | 3                                 | 62592µs                                                                 |

| 0x3          | 4096                                | 3                                 | 125092µs                                                                |

| 0x4          | 16384                               | 3                                 | 500092µs                                                                |

| 0x5          | 32768                               | 3                                 | 1000092µs                                                               |

| 0x6          | 65536                               | 3                                 | 2000092µs                                                               |

| 0x7          | 131072                              | 3                                 | 4000092µs                                                               |

Notes: 1. Number of cycles for the start-up counter.

2. Number of cycles for the synchronization delay, before PCLKSR.XOSC32KRDY is set.

3. Start-up time is n OSCULP32K cycles + 3 XOSC32K cycles.

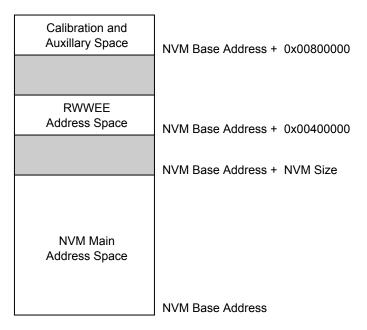

#### Figure 22-3. NVM Memory Organization

The lower rows in the NVM main address space can be allocated as a boot loader section by using the BOOTPROT fuses, and the upper rows can be allocated to EEPROM, as shown in the figure below.

The boot loader section is protected by the lock bit(s) corresponding to this address space and by the BOOTPROT[2:0] fuse. The EEPROM rows can be written regardless of the region lock status.

The number of rows protected by BOOTPROT is given in Boot Loader Size, the number of rows allocated to the EEPROM are given in EEPROM Size.

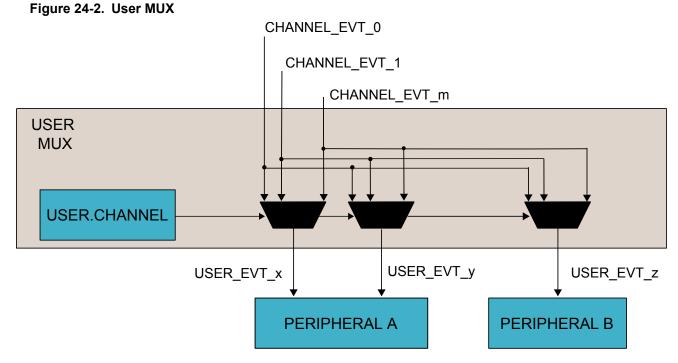

To configure a user multiplexer, the USER register must be written in a single 16-bit write. It is possible to read out the configuration of a user by first selecting the user by writing to USER.USER using an 8-bit write and then performing a read of the 16-bit USER register.

#### 24.6.2.4 Channel Setup

An event channel can select one event from a list of event generators. Depending on configuration, the selected event could be synchronized, resynchronized or asynchronously sent to the users. When synchronization or resynchronization is required, the channel includes an internal edge detector, allowing the Event System to generate internal events when rising, falling or both edges are detected on the selected event generator. An event channel is able to generate internal events for the specific software commands. All these configurations are available in the Channel register (CHANNEL).

To configure a channel, the Channel register must be written in a single 32-bit write. It is possible to read out the configuration of a channel by first selecting the channel by writing to CHANNEL.CHANNEL using a, 8-bit write, and then performing a read of the CHANNEL register.

#### 24.6.2.5 Channel Path

There are three different ways to propagate the event provided by an event generator:

- Asynchronous path

- Synchronous path

- Resynchronized path

# 27.7 Register Summary

| Offset | Name     | Bit Pos. |          |         |       |        |           |        |             |           |

|--------|----------|----------|----------|---------|-------|--------|-----------|--------|-------------|-----------|

| 0x00   |          | 7:0      | RUNSTDBY |         |       |        | MODE[2:0] |        | ENABLE      | SWRST     |

| 0x01   | CTRLA    | 15:8     |          |         |       |        |           |        |             | IBON      |

| 0x02   | CIRLA    | 23:16    |          |         | DIPC  | D[1:0] |           |        | DOPO        | D[1:0]    |

| 0x03   |          | 31:24    |          | DORD    | CPOL  | CPHA   |           | FOR    | V[3:0]      |           |

| 0x04   |          | 7:0      |          | PLOADEN |       |        |           |        | CHSIZE[2:0] |           |

| 0x05   | CTRLB    | 15:8     | AMOD     | E[1:0]  | MSSEN |        |           |        | SSDE        |           |

| 0x06   | CIRLB    | 23:16    |          |         |       |        |           |        | RXEN        |           |

| 0x07   |          | 31:24    |          |         |       |        |           |        |             |           |

| 0x08   |          |          |          |         |       |        |           |        |             |           |

|        | Reserved |          |          |         |       |        |           |        |             |           |

| 0x0B   |          |          |          |         |       |        |           |        |             |           |

| 0x0C   | BAUD     | 7:0      |          |         |       | BAU    | D[7:0]    |        |             |           |

| 0x0D   |          |          |          |         |       |        |           |        |             |           |

|        | Reserved |          |          |         |       |        |           |        |             |           |

| 0x13   |          |          |          |         |       |        |           |        |             |           |

| 0x14   | INTENCLR | 7:0      | ERROR    |         |       |        | SSL       | RXC    | TXC         | DRE       |

| 0x15   | Reserved |          |          |         |       |        |           |        |             |           |

| 0x16   | INTENSET | 7:0      | ERROR    |         |       |        | SSL       | RXC    | TXC         | DRE       |

| 0x17   | Reserved |          |          |         |       |        |           |        |             |           |

| 0x18   | INTFLAG  | 7:0      | ERROR    |         |       |        | SSL       | RXC    | TXC         | DRE       |

| 0x19   | Reserved |          |          |         |       |        |           |        |             |           |

| 0x1A   | STATUS   | 7:0      |          |         |       |        |           | BUFOVF |             |           |

| 0x1B   |          | 15:8     |          |         |       |        |           |        |             |           |

| 0x1C   |          | 7:0      |          |         |       |        |           | CTRLB  | ENABLE      | SWRST     |

| 0x1D   | SYNCBUSY | 15:8     |          |         |       |        |           |        |             |           |

| 0x1E   | 0        | 23:16    |          |         |       |        |           |        |             |           |

| 0x1F   |          | 31:24    |          |         |       |        |           |        |             |           |

| 0x20   |          |          |          |         |       |        |           |        |             |           |

|        | Reserved |          |          |         |       |        |           |        |             |           |

| 0x23   |          |          |          |         |       |        |           |        |             |           |

| 0x24   |          | 7:0      |          |         |       | ADD    | R[7:0]    |        |             |           |

| 0x25   | ADDR     | 15:8     |          |         |       |        |           |        |             |           |

| 0x26   |          | 23:16    |          |         |       | ADDRM  | IASK[7:0] |        |             |           |

| 0x27   |          | 31:24    |          |         |       |        |           |        |             |           |

| 0x28   | DATA     | 7:0      |          |         |       | DAT    | A[7:0]    |        |             |           |

| 0x29   |          | 15:8     |          |         |       |        |           |        |             | DATA[8:8] |

| 0x2A   |          |          |          |         |       |        |           |        |             |           |

|        | Reserved |          |          |         |       |        |           |        |             |           |

| 0x2F   |          |          |          |         |       |        |           |        |             |           |

| 0x30   | DBGCTRL  | 7:0      |          |         |       |        |           |        |             | DBGSTOP   |

# 29.4 Signal Description

### Table 29-1. Master Mode

| Pin Name | Pin Description                                                 | Туре         |

|----------|-----------------------------------------------------------------|--------------|

| MCKn     | Master Clock for Clock Unit n                                   | Input/Output |

| SCKn     | Serial Clock for Clock Unit n                                   | Input/Output |

| FSn      | I <sup>2</sup> S Word Select or TDM Frame Sync for Clock Unit n | Input/Output |

| SDm      | Serial Data Input or Output for Serializer m                    | Input/Output |

#### Table 29-2. Slave Mode

| Pin Name | Pin Description                                | Туре         |

|----------|------------------------------------------------|--------------|

| MCKn     | Master Clock                                   | Input        |

| SCKn     | Serial Clock for Clock Unit n                  | Input        |

| FSn      | I <sup>2</sup> S Word Select or TDM Frame Sync | Input        |

| SDm      | Serial Data Input or Output for Serializer m   | Input/Output |

# Table 29-3. Controller Mode

| Pin Name | Pin Description                                | Туре           |

|----------|------------------------------------------------|----------------|

| MCKn     | Master Clock for Clock Unit n                  | Output         |

| SCKn     | Serial Clock for Clock Unit n                  | Output         |

| FSn      | I <sup>2</sup> S Word Select or TDM Frame Sync | Output         |

| SDm      | Not Applicable                                 | Not Applicable |

Note: One signal can be mapped on several pins.

#### **Related Links**

I/O Multiplexing and Considerations

### 29.5 **Product Dependencies**

In order to use this module, other parts of the system must be configured correctly, as described below.

#### 29.5.1 I/O Lines

Using the  $I^2S$  I/O lines requires the I/O pins to be configured.

The I<sup>2</sup>S pins may be multiplexed with I/O Controller lines. The user must first program the I/O Controller to assign the desired I<sup>2</sup>S pins to their peripheral function. If the I<sup>2</sup>S I/O lines are not used by the application, they can be used for other purposes by the I/O Controller. It is required to enable only the I<sup>2</sup>S inputs and outputs actually in use.

#### **Related Links**

PORT - I/O Pin Controller

| DATASIZE[2:0] | Name | Description           |

|---------------|------|-----------------------|

| 0x6           | 8    | 8 bits                |

| 0x7           | 8C   | 8 bits compact stereo |

## Bit 7 – SLOTADJ: Data Slot Formatting Adjust

This field defines left or right adjustment of data samples in the slot.

| SLOTADJ | Name  | Description                    |

|---------|-------|--------------------------------|

| 0x0     | RIGHT | Data is right adjusted in slot |

| 0x1     | LEFT  | Data is left adjusted in slot  |

### Bit 5 – CLKSEL: Clock Unit Selection.

| CLKSEL | Name | Description      |

|--------|------|------------------|

| 0x0    | CLK0 | Use Clock Unit 0 |

| 0x1    | CLK1 | Use Clock Unit 1 |

### Bit 4 – TXSAME: Transmit Data when Underrun.

| TXSAME | Name | Description                               |

|--------|------|-------------------------------------------|

| 0x0    | ZERO | Zero data transmitted in case of underrun |

| 0x1    | SAME | Last data transmitted in case of underrun |

#### Bits 3:2 – TXDEFAULT[1:0]: Line Default Line when Slot Disabled

This field defines the default value driven on the SDn output pin during all disabled Slots.

| TXDEFAULT[1:0] | Name | Description                            |

|----------------|------|----------------------------------------|

| 0x0            | ZERO | Output Default Value is 0              |

| 0x1            | ONE  | Output Default Value is 1              |

| 0x2            |      | Reserved                               |

| 0x3            | HIZ  | Output Default Value is high impedance |

#### Bits 1:0 – SERMODE[1:0]: Serializer Mode.

| SERMODE[1:0] | Name | Description                                    |

|--------------|------|------------------------------------------------|

| 0x0          | RX   | Receive                                        |

| 0x1          | ТХ   | Transmit                                       |

| 0x2          | PDM2 | Receive one PDM data on each serial clock edge |

| 0x3          |      | Reserved                                       |

### 29.9.8 Data Holding m

Name: DATAmn

When the endpoint is enabled, the USB module then checks the Endpoint Configuration register (EPCFG) of the addressed output endpoint. If the type of the endpoint (EPCFG.EPTYPE0) is not set to OUT, the USB module returns to idle and waits for the next token packet.

The USB module then fetches the Data Buffer Address (ADDR) from the addressed endpoint's descriptor, and waits for a DATA0 or DATA1 packet. If a PID error or any other PID than DATA0 or DATA1 is detected, the USB module returns to idle and waits for the next token packet.

If EPSTATUS.STALLRQ0 in EPSTATUS is set, the incoming data is discarded. If the endpoint is not isochronous, a STALL handshake is returned to the host and the Transmit Stall Bank 0 interrupt bit in EPINTFLAG (EPINTFLAG.STALL0) is set.

For isochronous endpoints, data from both a DATA0 and DATA1 packet will be accepted. For other endpoint types the PID is checked against EPSTATUS.DTGLOUT. If a PID mismatch occurs, the incoming data is discarded, and an ACK handshake is returned to the host.

If EPSTATUS.BK0RDY is set, the incoming data is discarded, the bit Transmit Fail 0 interrupt bit in EPINTFLAG (EPINTFLAG.TRFAIL0) and the status bit STATUS\_BK.ERRORFLOW are set. If the endpoint is not isochronous, a NAK handshake is returned to the host.

The incoming data is written to the data buffer pointed to by the Data Buffer Address (ADDR). If the number of received data bytes exceeds the maximum data payload specified as PCKSIZE.SIZE, the remainders of the received data bytes are discarded. The packet will still be checked for bit-stuff and CRC errors. If a bit-stuff or CRC error is detected in the packet, the USB module returns to idle and waits for the next token packet.

If the endpoint is isochronous and a bit-stuff or CRC error in the incoming data, the number of received data bytes, excluding CRC, is written to PCKSIZE.BYTE\_COUNT. Finally the EPINTFLAG.TRFAIL0 and CRC Error bit in the Device Bank Status register (STATUS\_BK.CRCERR) is set for the addressed endpoint.

If data was successfully received, an ACK handshake is returned to the host if the endpoint is not isochronous, and the number of received data bytes, excluding CRC, is written to PCKSIZE.BYTE\_COUNT. If the number of received data bytes is the maximum data payload specified by PCKSIZE.SIZE no CRC data bytes are written to the data buffer. If the number of received data bytes is the maximum data payload specified by PCKSIZE.SIZE minus one, only the first CRC data byte is written to the data buffer If the number of received data is equal or less than the data payload specified by PCKSIZE.SIZE minus two, both CRC data bytes are written to the data buffer.

Finally in EPSTATUS for the addressed output endpoint, EPSTATUS.BK0RDY is set and EPSTATUS.DTGLOUT is toggled if the endpoint is not isochronous. The flag Transmit Complete 0 interrupt bit in EPINTFLAG (EPINTFLAG.TRCPT0) is set for the addressed endpoint.

#### 32.6.2.8 Multi-Packet Transfers for OUT Endpoint

The number of data bytes received is stored in endpoint PCKSIZE.BYTE\_COUNT as for normal operation. Since PCKSIZE.BYTE\_COUNT is updated after each transaction, it must be set to zero when setting up a new transfer. The total number of bytes to be received must be written to PCKSIZE.MULTI\_PACKET\_SIZE. This value must be a multiple of PCKSIZE.SIZE, otherwise excess data may be written to SRAM locations used by other parts of the application.

EPSTATUS.DTGLOUT management for non-isochronous packets and EPINTFLAG.BK1RDY/BK0RDY management are as for normal operation.

If a maximum payload size packet is received, PCKSIZE.BYTE\_COUNT will be incremented by PCKSIZE.SIZE after the transaction has completed, and EPSTATUS.DTGLOUT will be toggled if the endpoint is not isochronous. If the updated PCKSIZE.BYTE\_COUNT is equal to

© 2017 Microchip Technology Inc.

| Figure 33-5. ADC Timing for Free Running in Differential Mode without G                                                                                                                          | ain                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 1   2   3   4   5   6   7   8   9   10   11   1                                                                                                                                                  | 2   13   14   15   16                                |

|                                                                                                                                                                                                  |                                                      |

| START                                                                                                                                                                                            |                                                      |

|                                                                                                                                                                                                  |                                                      |

| INT                                                                                                                                                                                              |                                                      |

| Converting Bit 11 10 9 8 7 1 6 5 4 3 2 1 1 0 11 10 9 8 7 6 5 4 3 2                                                                                                                               | <u>1 0 11 10 9 8 7 6 5 </u>                          |

| Figure 33-6. ADC Timing for One Conversion in Single-Ended Mode with                                                                                                                             | out Gain                                             |

| 1 2 3 4 5 6 7 8                                                                                                                                                                                  | 9   10   11                                          |

|                                                                                                                                                                                                  |                                                      |

| START                                                                                                                                                                                            |                                                      |

| SAMPLE                                                                                                                                                                                           |                                                      |

|                                                                                                                                                                                                  |                                                      |

|                                                                                                                                                                                                  |                                                      |

|                                                                                                                                                                                                  |                                                      |

| Converting Bit                                                                                                                                                                                   |                                                      |

| Figure 33-7. ADC Timing for Free Running in Single-Ended Mode without                                                                                                                            | t Gain                                               |

| 1   2   3   4   5   6   7   8   9   10   11   1                                                                                                                                                  | 2   13   14   15   16                                |

|                                                                                                                                                                                                  |                                                      |

| START                                                                                                                                                                                            |                                                      |

|                                                                                                                                                                                                  |                                                      |

|                                                                                                                                                                                                  |                                                      |

| INT                                                                                                                                                                                              |                                                      |

| $Converting Bit \underbrace{\chi_{11}\chi_{10}\chi_{9}\chi_{8}\chi_{7}\chi_{8}\chi_{5}\chi_{4}\chi_{3}\chi_{2}\chi_{1}\chi_{0}\chi_{11}\chi_{10}\chi_{9}\chi_{8}\chi_{7}\chi_{6}\chi_{5}}_{(4)}$ | <u>4 3 2 1 0 11 10 11 10 10 11 10 10 11 10 10 10</u> |

#### 33.6.6 Accumulation

The result from multiple consecutive conversions can be accumulated. The number of samples to be accumulated is specified by the Number of Samples to be Collected field in the Average Control register (AVGCTRL.SAMPLENUM). When accumulating more than 16 samples, the result will be too large to match the 16-bit RESULT register size. To avoid overflow, the result is right shifted automatically to fit within the available register size. The number of automatic right shifts is specified in the table below.

**Note:** To perform the accumulation of two or more samples, the Conversion Result Resolution field in the Control B register (CTRLB.RESSEL) must be set.

| Number of<br>Accumulated<br>Samples | AVGCTRL.<br>SAMPLENUM | Intermediate<br>Result Precision |   | Final Result<br>Precision | Automatic<br>Division<br>Factor |

|-------------------------------------|-----------------------|----------------------------------|---|---------------------------|---------------------------------|

| 1                                   | 0x0                   | 12 bits                          | 0 | 12 bits                   | 0                               |

| 2                                   | 0x1                   | 13 bits                          | 0 | 13 bits                   | 0                               |

#### Table 33-2. Accumulation

| PRESCALER[2:0] | Name   | Description                     |

|----------------|--------|---------------------------------|

| 0x2            | DIV16  | Peripheral clock divided by 16  |

| 0x3            | DIV32  | Peripheral clock divided by 32  |

| 0x4            | DIV64  | Peripheral clock divided by 64  |

| 0x5            | DIV128 | Peripheral clock divided by 128 |

| 0x6            | DIV256 | Peripheral clock divided by 256 |

| 0x7            | DIV512 | Peripheral clock divided by 512 |

#### Bits 5:4 – RESSEL[1:0]: Conversion Result Resolution

These bits define whether the ADC completes the conversion at 12-, 10- or 8-bit result resolution.

| RESSEL[1:0] | Name  | Description               |

|-------------|-------|---------------------------|

| 0x0         | 12BIT | 12-bit result             |

| 0x1         | 16BIT | For averaging mode output |

| 0x2         | 10BIT | 10-bit result             |

| 0x3         | 8BIT  | 8-bit result              |

#### Bit 3 – CORREN: Digital Correction Logic Enabled

| Value | Description                                                                                                                                                                                                                                                                                                                               |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Disable the digital result correction.                                                                                                                                                                                                                                                                                                    |

| 1     | Enable the digital result correction. The ADC conversion result in the RESULT register is then corrected for gain and offset based on the values in the GAINCAL and OFFSETCAL registers. Conversion time will be increased by X cycles according to the value in the Offset Correction Value bit group in the Offset Correction register. |

#### Bit 2 – FREERUN: Free Running Mode

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | The ADC run is single conversion mode.                                                 |

| 1     | The ADC is in free running mode and a new conversion will be initiated when a previous |

|       | conversion completes.                                                                  |

#### Bit 1 – LEFTADJ: Left-Adjusted Result

| Value | Description                                                                                   |

|-------|-----------------------------------------------------------------------------------------------|

| 0     | The ADC conversion result is right-adjusted in the RESULT register.                           |

| 1     | The ADC conversion result is left-adjusted in the RESULT register. The high byte of the 12-   |

|       | bit result will be present in the upper part of the result register. Writing this bit to zero |

|       | (default) will right-adjust the value in the RESULT register.                                 |

#### Bit 0 – DIFFMODE: Differential Mode

| Value | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| 0     | The ADC is running in singled-ended mode.                                                 |

| 1     | The ADC is running in differential mode. In this mode, the voltage difference between the |

|       | MUXPOS and MUXNEG inputs will be converted by the ADC.                                    |

© 2017 Microchip Technology Inc.

#### 34.8.5 Interrupt Enable Set

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear register (INTENCLR).

Name: INTENSET Offset: 0x05 Reset: 0x00 Property: PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4    | 3 | 2 | 1     | 0     |

|--------|---|---|---|------|---|---|-------|-------|

|        |   |   |   | WIN0 |   |   | COMP1 | COMP0 |

| Access |   |   |   | R/W  | - |   | R/W   | R/W   |

| Reset  |   |   |   | 0    |   |   | 0     | 0     |

#### Bit 4 – WIN0: Window 0 Interrupt Enable

Reading this bit returns the state of the Window 0 interrupt enable.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit enables the Window 0 interrupt.

| Val | ue | Description                         |

|-----|----|-------------------------------------|

| 0   |    | The Window 0 interrupt is disabled. |

| 1   |    | The Window 0 interrupt is enabled.  |

#### Bits 1,0 – COMPx: Comparator x Interrupt Enable

Reading this bit returns the state of the Comparator x interrupt enable.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Ready interrupt bit and enable the Ready interrupt.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | The Comparator x interrupt is disabled. |

| 1     | The Comparator x interrupt is enabled.  |

#### 34.8.6 Interrupt Flag Status and Clear

| Name:            | INTFLAG |

|------------------|---------|

| Offset:          | 0x06    |

| Reset:           | 0x00    |

| <b>Property:</b> | -       |

| Bit    | 7 | 6 | 5 | 4    | 3 | 2 | 1     | 0     |

|--------|---|---|---|------|---|---|-------|-------|

|        |   |   |   | WIN0 |   |   | COMP1 | COMP0 |

| Access |   |   |   | R/W  |   |   | R/W   | R/W   |

| Reset  |   |   |   | 0    |   |   | 0     | 0     |

#### Bit 4 – WIN0: Window 0

This flag is set according to the Window 0 Interrupt Selection bit group in the WINCTRL register (WINCTRL.WINTSELx) and will generate an interrupt if INTENCLR/SET.WINx is also one.

| Average<br>Number | Conditions                                                        | SNR<br>(dB) | SINAD<br>(dB) | SFDR<br>(dB) | ENOB<br>(bits) |

|-------------------|-------------------------------------------------------------------|-------------|---------------|--------------|----------------|

| 1                 | V <sub>DDANA</sub> =3.0V, V <sub>REF</sub> =1.0V, 350kSps at 25°C | 66.0        | 65.0          | 72.8         | 10.5           |

| 8                 |                                                                   | 67.6        | 65.8          | 75.1         | 10.62          |

| 32                |                                                                   | 69.7        | 67.1          | 75.3         | 10.85          |

| 128               |                                                                   | 70.4        | 67.5          | 75.5         | 10.91          |

### Table 37-28. Averaging Feature (Device Variant B and C)

#### 37.10.4.2 Performance with the hardware offset and gain correction

Inherent gain and offset errors affect the absolute accuracy of the ADC. The offset error cancellation is handled by the Offset Correction register (OFFSETCORR) and the gain error cancellation, by the Gain Correction register (GAINCORR). The offset and gain correction value is subtracted from the converted data before writing the Result register (RESULT).

Table 37-29. Offset and Gain correction feature

| Gain<br>Factor | Conditions                              | Offset<br>Error (mV) | Gain Error<br>(mV) | Total Unadjusted<br>Error (LSB) |

|----------------|-----------------------------------------|----------------------|--------------------|---------------------------------|

| 0.5x           | V <sub>REF</sub> =1.0V, 350kSps at 25°C | 0.25                 | 1.0                | 2.4                             |

| 1x             |                                         | 0.20                 | 0.10               | 1.5                             |

| 2x             |                                         | 0.15                 | -0.15              | 2.7                             |

| 8x             |                                         | -0.05                | 0.05               | 3.2                             |

| 16x            |                                         | 0.10                 | -0.05              | 6.1                             |

#### 37.10.4.3 Inputs and Sample and Hold Acquisition Times

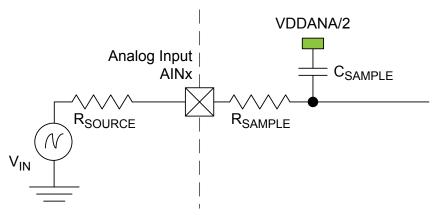

The analog voltage source must be able to charge the sample and hold (S/H) capacitor in the ADC in order to achieve maximum accuracy. Seen externally the ADC input consists of a resistor ( $R_{SAMPLE}$ ) and a capacitor ( $C_{SAMPLE}$ ). In addition, the source resistance ( $R_{SOURCE}$ ) must be taken into account when calculating the required sample and hold time. The next figure shows the ADC input channel equivalent circuit.

#### Figure 37-5. ADC Input

To achieve n bits of accuracy, the  $C_{\text{SAMPLE}}$  capacitor must be charged at least to a voltage of

- Oscillators

- XOSC (crystal oscillator) stopped

- XOSC32K (32 kHz crystal oscillator) running with external 32kHz crystal

- DFLL48M using XOSC32K as reference and running at 48 MHz

- Clocks

- DFLL48M used as main clock source, except otherwise specified

- CPU, AHB clocks undivided

- APBA clock divided by 4

- APBB and APBC bridges off

- The following AHB module clocks are running: NVMCTRL, APBA bridge

- All other AHB clocks stopped

- The following peripheral clocks running: PM, SYSCTRL, RTC

- All other peripheral clocks stopped

- I/Os are inactive with internal pull-up

- CPU is running on flash with 1 wait states

- Cache enabled

- BOD33 disabled

# 44.7 NVM Characteristics

#### Table 44-28. Maximum Operating Frequency

| V <sub>DD</sub> range | NVM Wait States | Maximum Operating Frequency | Units |

|-----------------------|-----------------|-----------------------------|-------|

| 1.62V to 2.7V         | 0               | 14                          | MHz   |

|                       | 1               | 28                          |       |

|                       | 2               | 40                          |       |

| 2.7V to 3.63V         | 0               | 24                          |       |

|                       | 1               | 40                          |       |

Note that on this flash technology, a max number of 8 consecutive write is allowed per row. Once this number is reached, a row erase is mandatory.

Table 44-29. Flash Endurance and Data Retention

| Symbol                 | Parameter                        | Conditions           | Min. | Тур. | Max. | Units  |

|------------------------|----------------------------------|----------------------|------|------|------|--------|

| Ret <sub>NVM25k</sub>  | Retention after up to 25k        | Average ambient 55°C | 10   | 50   | -    | Years  |

| Ret <sub>NVM2.5k</sub> | Retention after up to 2.5k       | Average ambient 55°C | 20   | 100  | -    | Years  |

| Ret <sub>NVM100</sub>  | Retention after up to 100        | Average ambient 55°C | 25   | >100 | -    | Years  |

| Cyc <sub>NVM</sub>     | Cycling Endurance <sup>(1)</sup> | -40°C < Ta < 85°C    | 25k  | 150k | -    | Cycles |

Note: 1. An endurance cycle is a write and an erase operation.

Table 44-30.

EEPROM Emulation<sup>(1)</sup>

Endurance and Data Retention

| Symbol                    | Parameter                        | Conditions           | Min. | Тур. | Max. | Units  |

|---------------------------|----------------------------------|----------------------|------|------|------|--------|

| Ret <sub>EEPROM100k</sub> | Retention after up to 100k       | Average ambient 55°C | 10   | 50   | -    | Years  |

| Ret <sub>EEPROM10k</sub>  | Retention after up to 10k        | Average ambient 55°C | 20   | 100  | -    | Years  |

| Cyc <sub>EEPROM</sub>     | Cycling Endurance <sup>(2)</sup> | -40°C < Ta < 85°C    | 100k | 600k | -    | Cycles |

Notes: 1. The EEPROM emulation is a software emulation described in the App note AT03265.

2. An endurance cycle is a write and an erase operation.

## Table 44-31. NVM Characteristics

| Symbol           | Parameter                        | Conditions | Min. | Тур. | Max. | Units |

|------------------|----------------------------------|------------|------|------|------|-------|

| t <sub>FPP</sub> | Page programming time            | -          | -    | -    | 2.5  | ms    |

| t <sub>FRE</sub> | Row erase time                   | -          | -    | -    | 6    | ms    |

| t <sub>FCE</sub> | DSU chip erase time (CHIP_ERASE) | -          | -    | -    | 240  | ms    |