#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 48MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 52                                                                        |

| Program Memory Size        | 128KB (128K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 16K × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                              |

| Data Converters            | A/D 20x12b; D/A 1x10b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-UFBGA                                                                  |

| Supplier Device Package    | 64-UFBGA (5x5)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd21j17a-cu |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Description

The SAM D21 is a series of low-power microcontrollers using the 32-bit ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ processor, and ranging from 32- to 64-pins with up to 256KB Flash and 32KB of SRAM. The SAM D21 operate at a maximum frequency of 48MHz and reach 2.46 CoreMark/MHz. They are designed for simple and intuitive migration with identical peripheral modules, hex compatible code, identical linear address map and pin compatible migration paths between all devices in the product series. All devices include intelligent and flexible peripherals, Event System for inter-peripheral signaling, and support for capacitive touch button, slider and wheel user interfaces.

The SAM D21 provide the following features: In-system programmable Flash, twelve-channel direct memory access (DMA) controller, 12 channel Event System, programmable interrupt controller, up to 52 programmable I/O pins, 32-bit real-time clock and calendar, up to five 16-bit Timer/Counters (TC) and three 24-bit Timer/Counters for Control (TCC), where each TC can be configured to perform frequency and waveform generation, accurate program execution timing or input capture with time and frequency measurement of digital signals. The TCs can operate in 8- or 16-bit mode, selected TCs can be cascaded to form a 32-bit TC, and three timer/counters have extended functions optimized for motor, lighting and other control applications. The series provide one full-speed USB 2.0 embedded host and device interface; up to six Serial Communication Modules (SERCOM) that each can be configured to act as an USART, UART, SPI, I<sup>2</sup>C up to 3.4MHz, SMBus, PMBus, and LIN slave; two-channel I<sup>2</sup>S interface; up to twenty-channel 350ksps 12-bit ADC with programmable gain and optional oversampling and decimation supporting up to 16-bit resolution, one 10-bit 350ksps DAC, two analog comparators with window mode, Peripheral Touch Controller supporting up to 256 buttons, sliders, wheels and proximity sensing; programmable Watchdog Timer, brown-out detector and power-on reset and two-pin Serial Wire Debug (SWD) program and debug interface.

All devices have accurate and low-power external and internal oscillators. All oscillators can be used as a source for the system clock. Different clock domains can be independently configured to run at different frequencies, enabling power saving by running each peripheral at its optimal clock frequency, and thus maintaining a high CPU frequency while reducing power consumption.

The SAM D21 have two software-selectable sleep modes, idle and standby. In idle mode the CPU is stopped while all other functions can be kept running. In standby all clocks and functions are stopped expect those selected to continue running. The device supports SleepWalking. This feature allows the peripheral to wake up from sleep based on predefined conditions, and thus allows the CPU to wake up only when needed, e.g. when a threshold is crossed or a result is ready. The Event System supports synchronous and asynchronous events, allowing peripherals to receive, react to and send events even in standby mode.

The Flash program memory can be reprogrammed in-system through the SWD interface. The same interface can be used for non-intrusive on-chip debug of application code. A boot loader running in the device can use any communication interface to download and upgrade the application program in the Flash memory.

The SAM D21 microcontrollers are supported with a full suite of program and system development tools, including C compilers, macro assemblers, program debugger/simulators, programmers and evaluation kits.

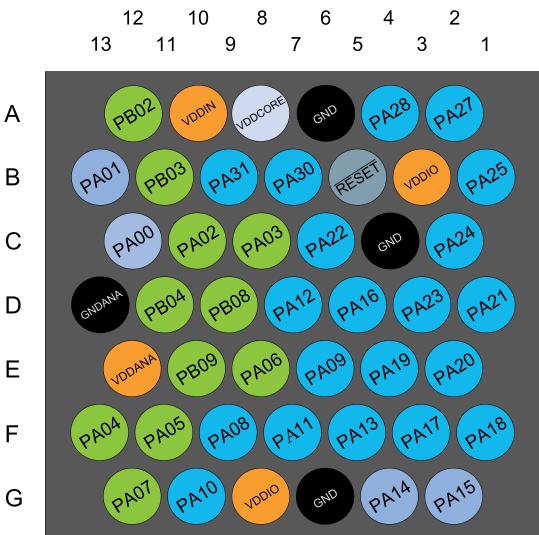

# 5.2.2 WLCSP45

- DIGITAL PIN

- ANALOG PIN

- OSCILLATOR

- GROUND

- INPUT SUPPLY

- REGULATED OUTPUT SUPPLY

- RESET PIN

|         | Pin <sup>(1)</sup> |         | I/O Pin             | Supply | A          |     | B(      | 2)(3) |       |     | с                        | D                  | E                 | F              | G                    | н          |

|---------|--------------------|---------|---------------------|--------|------------|-----|---------|-------|-------|-----|--------------------------|--------------------|-------------------|----------------|----------------------|------------|

| SAMD21E | SAMD21G            | SAMD21J |                     |        | EIC        | REF | ADC     | AC    | РТС   | DAC | SERCOM <sup>(2)(3)</sup> | SERCOM-ALT         | тс <sup>(4)</sup> | тсс            | сом                  | AC/        |

|         |                    |         |                     |        |            |     |         |       |       |     |                          |                    | /тсс              |                |                      | GCLK       |

|         |                    | 28      | PB15                | VDDIO  | EXTINT[15] |     |         |       | X[15] |     | SERCOM4/<br>PAD[3]       |                    | TC5/WO[1]         |                |                      | GCLK_IO[1] |

|         | 21                 | 29      | PA12                | VDDIO  | EXTINT[12] |     |         |       |       |     | SERCOM2/<br>PAD[0]       | SERCOM4/<br>PAD[0] | TCC2/WO[0]        | TCC0/<br>WO[6] |                      | AC/CMP[0]  |

|         | 22                 | 30      | PA13                | VDDIO  | EXTINT[13] |     |         |       |       |     | SERCOM2/<br>PAD[1]       | SERCOM4/<br>PAD[1] | TCC2/WO[1]        | TCC0/<br>WO[7] |                      | AC/CMP[1]  |

| 15      | 23                 | 31      | PA14                | VDDIO  | EXTINT[14] |     |         |       |       |     | SERCOM2/<br>PAD[2]       | SERCOM4/<br>PAD[2] | TC3/WO[0]         | TCC0/<br>WO[4] |                      | GCLK_IO[0] |

| 16      | 24                 | 32      | PA15                | VDDIO  | EXTINT[15] |     |         |       |       |     | SERCOM2/<br>PAD[3]       | SERCOM4/<br>PAD[3] | TC3/WO[1]         | TCC0/<br>WO[5] |                      | GCLK_IO[1] |

| 17      | 25                 | 35      | PA16                | VDDIO  | EXTINT[0]  |     |         |       | X[4]  |     | SERCOM1/<br>PAD[0]       | SERCOM3/<br>PAD[0] | TCC2/WO[0]        | TCC0/<br>WO[6] |                      | GCLK_IO[2] |

| 18      | 26                 | 36      | PA17                | VDDIO  | EXTINT[1]  |     |         |       | X[5]  |     | SERCOM1/<br>PAD[1]       | SERCOM3/<br>PAD[1] | TCC2/WO[1]        | TCC0/<br>WO[7] |                      | GCLK_IO[3] |

| 19      | 27                 | 37      | PA18                | VDDIO  | EXTINT[2]  |     |         |       | X[6]  |     | SERCOM1/<br>PAD[2]       | SERCOM3/<br>PAD[2] | TC3/WO[0]         | TCC0/<br>WO[2] |                      | AC/CMP[0]  |

| 20      | 28                 | 38      | PA19                | VDDIO  | EXTINT[3]  |     |         |       | X[7]  |     | SERCOM1/<br>PAD[3]       | SERCOM3/<br>PAD[3] | TC3/WO[1]         | TCC0/<br>WO[3] | 12S/SD[0]            | AC/CMP[1]  |

|         |                    | 39      | PB16                | VDDIO  | EXTINT[0]  |     |         |       |       |     | SERCOM5/<br>PAD[0]       |                    | TC6/WO[0]         | TCC0/<br>WO[4] | I2S/SD[1]            | GCLK_IO[2] |

|         |                    | 40      | PB17                | VDDIO  | EXTINT[1]  |     |         |       |       |     | SERCOM5/<br>PAD[1]       |                    | TC6/WO[1]         | TCC0/<br>WO[5] | 12S/<br>MCK[0]       | GCLK_IO[3] |

|         | 29                 | 41      | PA20                | VDDIO  | EXTINT[4]  |     |         |       | X[8]  |     | SERCOM5/<br>PAD[2]       | SERCOM3/<br>PAD[2] | TC7/WO[0]         | TCC0/<br>WO[6] | 12S/<br>SCK[0]       | GCLK_IO[4] |

|         | 30                 | 42      | PA21                | VDDIO  | EXTINT[5]  |     |         |       | X[9]  |     | SERCOM5/<br>PAD[3]       | SERCOM3/<br>PAD[3] | TC7/WO[1]         | TCC0/<br>WO[7] | I2S/FS[0]            | GCLK_IO[5] |

| 21      | 31                 | 43      | PA22                | VDDIO  | EXTINT[6]  |     |         |       | X[10] |     | SERCOM3/<br>PAD[0]       | SERCOM5/<br>PAD[0] | TC4/WO[0]         | TCC0/<br>WO[4] |                      | GCLK_IO[6] |

| 22      | 32                 | 44      | PA23                | VDDIO  | EXTINT[7]  |     |         |       | X[11] |     | SERCOM3/<br>PAD[1]       | SERCOM5/<br>PAD[1] | TC4/WO[1]         | TCC0/<br>WO[5] | USB/SOF<br>1kHz      | GCLK_IO[7] |

| 23      | 33                 | 45      | PA24 <sup>(6)</sup> | VDDIO  | EXTINT[12] |     |         |       |       |     | SERCOM3/<br>PAD[2]       | SERCOM5/<br>PAD[2] | TC5/WO[0]         | TCC1/<br>WO[2] | USB/DM               |            |

| 24      | 34                 | 46      | PA25 <sup>(6)</sup> | VDDIO  | EXTINT[13] |     |         |       |       |     | SERCOM3/<br>PAD[3]       | SERCOM5/<br>PAD[3] | TC5/WO[1]         | TCC1/<br>WO[3] | USB/DP               |            |

|         | 37                 | 49      | PB22                | VDDIO  | EXTINT[6]  |     |         |       |       |     |                          | SERCOM5/<br>PAD[2] | TC7/WO[0]         |                |                      | GCLK_IO[0] |

|         | 38                 | 50      | PB23                | VDDIO  | EXTINT[7]  |     |         |       |       |     |                          | SERCOM5/<br>PAD[3] | TC7/WO[1]         |                |                      | GCLK_IO[1] |

| 25      | 39                 | 51      | PA27                | VDDIO  | EXTINT[15] |     |         |       |       |     |                          |                    |                   |                |                      | GCLK_IO[0] |

| 27      | 41                 | 53      | PA28                | VDDIO  | EXTINT[8]  |     |         |       |       |     |                          |                    |                   |                |                      | GCLK_IO[0] |

| 31      | 45                 | 57      | PA30                | VDDIO  | EXTINT[10] |     |         |       |       |     |                          | SERCOM1/<br>PAD[2] | TCC1/WO[0]        |                | SWCLK                | GCLK_IO[0] |

| 32      | 46                 | 58      | PA31                | VDDIO  | EXTINT[11] |     |         |       |       |     |                          | SERCOM1/<br>PAD[3] | TCC1/WO[1]        |                | SWDIO <sup>(5)</sup> |            |

|         |                    | 59      | PB30                | VDDIO  | EXTINT[14] |     |         |       |       |     |                          | SERCOM5/<br>PAD[0] | TCC0/WO[0]        | TCC1/<br>WO[2] |                      |            |

|         |                    | 60      | PB31                | VDDIO  | EXTINT[15] |     |         |       |       |     |                          | SERCOM5/<br>PAD[1] | TCC0/WO[1]        | TCC1/<br>WO[3] |                      |            |

|         |                    | 61      | PB00                | VDDANA | EXTINT[0]  |     | AIN[8]  |       | Y[6]  |     |                          | SERCOM5/<br>PAD[2] | TC7/WO[0]         |                |                      |            |

|         |                    | 62      | PB01                | VDDANA | EXTINT[1]  |     | AIN[9]  |       | Y[7]  |     |                          | SERCOM5/<br>PAD[3] | TC7/WO[1]         |                |                      |            |

|         | 47                 | 63      | PB02                | VDDANA | EXTINT[2]  |     | AIN[10] |       | Y[8]  |     |                          | SERCOM5/<br>PAD[0] | TC6/WO[0]         |                |                      |            |

|         | 48                 | 64      | PB03                | VDDANA | EXTINT[3]  |     | AIN[11] |       | Y[9]  |     |                          | SERCOM5/<br>PAD[1] | TC6/WO[1]         |                |                      |            |

- 1. Use the SAMD21J pinout muxing for WLCSP45 package.

- 2. All analog pin functions are on peripheral function B. Peripheral function B must be selected to disable the digital control of the pin.

- 3. Only some pins can be used in SERCOM I2C mode. Refer to SERCOM I2C Pins.

### 13.5.3 Clocks

The DSU bus clocks (CLK\_DSU\_APB and CLK\_DSU\_AHB) can be enabled and disabled by the Power Manager. Refer to *PM – Power Manager*

### **Related Links**

PM – Power Manager

# 13.5.4 DMA

Not applicable.

### 13.5.5 Interrupts

Not applicable.

### 13.5.6 Events

Not applicable.

### 13.5.7 Register Access Protection

Registers with write-access can be optionally write-protected by the Peripheral Access Controller (PAC), except the following:

- Debug Communication Channel 0 register (DCC0)

- Debug Communication Channel 1 register (DCC1)

**Note:** Optional write-protection is indicated by the "PAC Write-Protection" property in the register description.

When the CPU is halted in debug mode, all write-protection is automatically disabled. Write-protection does not apply for accesses through an external debugger.

### **Related Links**

PAC - Peripheral Access Controller

### 13.5.8 Analog Connections

Not applicable.

# 13.6 Debug Operation

# 13.6.1 Principle of Operation

The DSU provides basic services to allow on-chip debug using the ARM Debug Access Port and the ARM processor debug resources:

- CPU reset extension

- Debugger probe detection

For more details on the ARM debug components, refer to the ARM Debug Interface v5 Architecture Specification.

### 13.6.2 CPU Reset Extension

"CPU reset extension" refers to the extension of the reset phase of the CPU core after the external reset is released. This ensures that the CPU is not executing code at startup while a debugger connects to the system. It is detected on a RESET release event when SWCLK is low. At startup, SWCLK is internally pulled up to avoid false detection of a debugger if SWCLK is left unconnected. When the CPU is held in

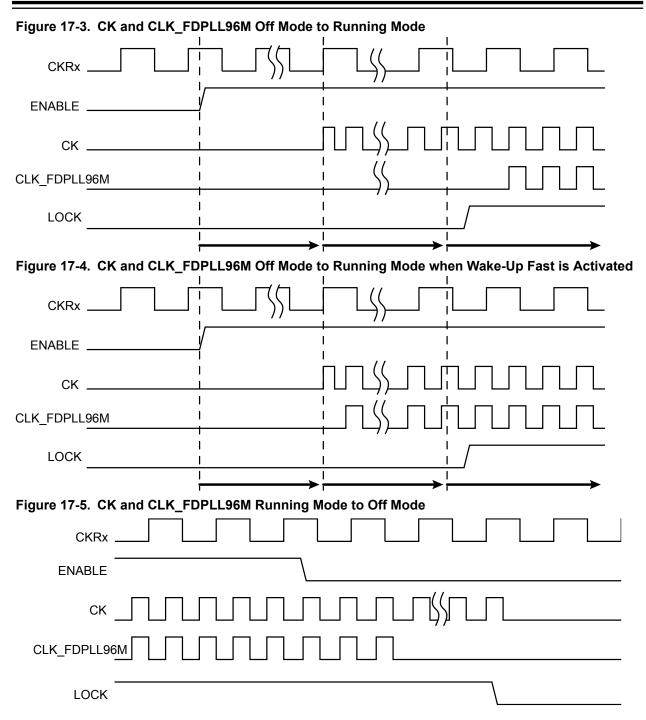

# 17.6.8.5 Reference Clock Switching

When a software operation requires reference clock switching, the normal operation is to disable the FDPLL96M, modify the DPLLCTRLB.REFCLK to select the desired reference source and activate the FDPLL96M again.

### 17.6.8.6 Loop Divider Ratio updates

The FDPLL96M supports on-the-fly update of the DPLLRATIO register, so it is allowed to modify the loop divider ratio and the loop divider ratio fractional part when the FDPLL96M is enabled. At that time, the DPLLSTATUS.LOCK bit is cleared and set again by hardware when the output frequency reached a stable state. The DPLL Lock Fail bit in the Interrupt Flag Status and Clear register (INTFLAG.DPLLLCK)

| Bit    | 23       | 22       | 21      | 20      | 19       | 18        | 17         | 16       |

|--------|----------|----------|---------|---------|----------|-----------|------------|----------|

|        |          |          |         |         |          |           | DPLLLTO    | DPLLLCKF |

| Access | R        | R        | R       | R       | R        | R         | R/W        | R/W      |

| Reset  | 0        | 0        | 0       | 0       | 0        | 0         | 0          | 0        |

|        |          |          |         |         |          |           |            |          |

| Bit    | 15       | 14       | 13      | 12      | 11       | 10        | 9          | 8        |

|        | DPLLLCKR |          |         |         | B33SRDY  | BOD33DET  | BOD33RDY   | DFLLRCS  |

| Access | R/W      | R        | R       | R       | R/W      | R/W       | R/W        | R/W      |

| Reset  | 0        | 0        | 0       | 0       | 0        | 0         | 0          | 0        |

|        |          |          |         |         |          |           |            |          |

| Bit    | 7        | 6        | 5       | 4       | 3        | 2         | 1          | 0        |

|        | DFLLLCKC | DFLLLCKF | DFLLOOB | DFLLRDY | OSC8MRDY | OSC32KRDY | XOSC32KRDY | XOSCRDY  |

| Access | R/W      | R/W      | R/W     | R/W     | R/W      | R/W       | R/W        | R/W      |

| Reset  | 0        | 0        | 0       | 0       | 0        | 0         | 0          | 0        |

# Bit 17 – DPLLLTO: DPLL Lock Timeout Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the DPLL Lock Timeout Interrupt Enable bit, which enables the DPLL Lock Timeout interrupt.

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | The DPLL Lock Timeout interrupt is disabled.                                           |

| 1     | The DPLL Lock Timeout interrupt is enabled, and an interrupt request will be generated |

|       | when the DPLL Lock Timeout Interrupt flag is set.                                      |

# Bit 16 – DPLLLCKF: DPLL Lock Fall Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the DPLL Lock Fall Interrupt Enable bit, which enables the DPLL Lock Fall interrupt.

| Value | Description                                                                                  |

|-------|----------------------------------------------------------------------------------------------|

| 0     | The DPLL Lock Fall interrupt is disabled.                                                    |

| 1     | The DPLL Lock Fall interrupt is enabled, and an interrupt request will be generated when the |

|       | DPLL Lock Fall Interrupt flag is set.                                                        |

# Bit 15 – DPLLLCKR: DPLL Lock Rise Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the DPLL Lock Rise Interrupt Enable bit, which enables the DPLL Lock Rise interrupt.

| Value | Description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| 0     | The DPLL Lock Rise interrupt is disabled.                                                |

| 1     | The DPLL Lock Rise interrupt is enabled, and an interrupt request will be generated when |

|       | the DPLL Lock Rise Interrupt flag is set.                                                |

# Bit 11 – B33SRDY: BOD33 Synchronization Ready Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the BOD33 Synchronization Ready Interrupt Enable bit, which enables the BOD33 Synchronization Ready interrupt.

In On Demand operation mode, i.e., if the ONDEMAND bit has been previously written to one, the oscillator will only be running when requested by a peripheral. If there is no peripheral requesting the oscillator s clock source, the oscillator will be in a disabled state.

If On Demand is disabled the oscillator will always be running when enabled.

In standby sleep mode, the On Demand operation is still active if the OSC8M.RUNSTDBY bit is one. If OSC8M.RUNSTDBY is zero, the oscillator is disabled.

| Value | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| 0     | The oscillator is always on, if enabled.                                                       |

| 1     | The oscillator is enabled when a peripheral is requesting the oscillator to be used as a clock |

|       | source. The oscillator is disabled if no peripheral is requesting the clock source.            |

### Bit 6 – RUNSTDBY: Run in Standby

This bit controls how the OSC8M behaves during standby sleep mode:

| Value | Description                                                                                                                                                                                                                                          |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The oscillator is disabled in standby sleep mode.                                                                                                                                                                                                    |

| 1     | The oscillator is not stopped in standby sleep mode. If OSC8M.ONDEMAND is one, the clock source will be running when a peripheral is requesting the clock. If OSC8M.ONDEMAND is zero, the clock source will always be running in standby sleep mode. |

# Bit 1 – ENABLE: Oscillator Enable

The user must ensure that the OSC8M is fully disabled before enabling it, and that the OSC8M is fully enabled before disabling it by reading OSC8M.ENABLE.

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | The oscillator is disabled or being enabled. |

| 1     | The oscillator is enabled or being disabled. |

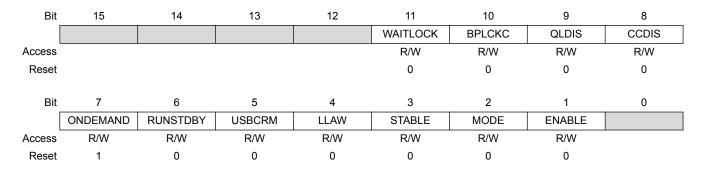

# 17.8.10 DFLL48M Control

Name:DFLLCTRLOffset:0x24Reset:0x0080Property:Write-Protected, Write-Synchronized

# Bit 11 – WAITLOCK: Wait Lock

This bit controls the DFLL output clock, depending on lock status:

| Bit    | 7         | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|--------|-----------|-----|-----|-----|-----|-----|-----|-----|--|

|        | FINE[7:0] |     |     |     |     |     |     |     |  |

| Access | R/W       | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Reset  | 0         | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

# Bits 31:16 – DIFF[15:0]: Multiplication Ratio Difference

In closed-loop mode (DFLLCTRL.MODE is written to one), this bit group indicates the difference between the ideal number of DFLL cycles and the counted number of cycles. This value is not updated in open-loop mode, and should be considered invalid in that case.

# Bits 15:10 - COARSE[5:0]: Coarse Value

Set the value of the Coarse Calibration register. In closed-loop mode, this field is read-only.

### Bits 9:0 - FINE[9:0]: Fine Value

Set the value of the Fine Calibration register. In closed-loop mode, this field is read-only.

### 17.8.12 DFLL48M Multiplier

Name:DFLLMULOffset:0x2CReset:0x00000000Property:Write-Protected

| Bit    | 31       | 30  | 29   | 28     | 27     | 26  | 25   | 24     |  |  |

|--------|----------|-----|------|--------|--------|-----|------|--------|--|--|

|        |          |     | CSTE | P[5:0] |        |     | FSTE | P[9:8] |  |  |

| Access | R/W      | R/W | R/W  | R/W    | R/W    | R/W | R/W  | R/W    |  |  |

| Reset  | 0        | 0   | 0    | 0      | 0      | 0   | 0    | 0      |  |  |

|        |          |     |      |        |        |     |      |        |  |  |

| Bit    | 23       | 22  | 21   | 20     | 19     | 18  | 17   | 16     |  |  |

|        |          |     |      | FSTE   | P[7:0] |     |      |        |  |  |

| Access | R/W      | R/W | R/W  | R/W    | R/W    | R/W | R/W  | R/W    |  |  |

| Reset  | 0        | 0   | 0    | 0      | 0      | 0   | 0    | 0      |  |  |

|        |          |     |      |        |        |     |      |        |  |  |

| Bit    | 15       | 14  | 13   | 12     | 11     | 10  | 9    | 8      |  |  |

|        |          |     |      | MUL    | [15:8] |     |      |        |  |  |

| Access | R/W      | R/W | R/W  | R/W    | R/W    | R/W | R/W  | R/W    |  |  |

| Reset  | 0        | 0   | 0    | 0      | 0      | 0   | 0    | 0      |  |  |

|        |          |     |      |        |        |     |      |        |  |  |

| Bit    | 7        | 6   | 5    | 4      | 3      | 2   | 1    | 0      |  |  |

|        | MUL[7:0] |     |      |        |        |     |      |        |  |  |

| Access | R/W      | R/W | R/W  | R/W    | R/W    | R/W | R/W  | R/W    |  |  |

| Reset  | 0        | 0   | 0    | 0      | 0      | 0   | 0    | 0      |  |  |

# Bits 31:26 – CSTEP[5:0]: Coarse Maximum Step

This bit group indicates the maximum step size allowed during coarse adjustment in closed-loop mode. When adjusting to a new frequency, the expected output frequency overshoot depends on this step size.

# Bits 25:16 – FSTEP[9:0]: Fine Maximum Step

This bit group indicates the maximum step size allowed during fine adjustment in closed-loop mode. When adjusting to a new frequency, the expected output frequency overshoot depends on this step size.

# Bits 15:0 - COMP[15:0]: Compare Value

The 16-bit value of COMPn is continuously compared with the 16-bit COUNT value. When a match occurs, the Compare n interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.CMPn) is set on the next counter cycle.

### 19.8.26 Alarm 0 Value - MODE2

Name:ALARM0Offset:0x18Reset:0x00000000Property:Write-Protected, Write-Synchronized

| Bit    | 31   | 30      | 29     | 28          | 27          | 26  | 25  | 24        |  |

|--------|------|---------|--------|-------------|-------------|-----|-----|-----------|--|

|        |      |         | YEAF   | R[5:0]      |             |     | MON | ITH[3:2]  |  |

| Access | R/W  | R/W     | R/W    | R/W         | R/W         | R/W | R/W | R/W       |  |

| Reset  | 0    | 0       | 0      | 0           | 0           | 0   | 0   | 0         |  |

|        |      |         |        |             |             |     |     |           |  |

| Bit    | 23   | 22      | 21     | 20          | 19          | 18  | 17  | 16        |  |

|        | MON  | TH[1:0] |        |             | DAY[4:0]    |     |     | HOUR[4:4] |  |

| Access | R/W  | R/W     | R/W    | R/W         | R/W         | R/W | R/W | R/W       |  |

| Reset  | 0    | 0       | 0      | 0           | 0           | 0   | 0   | 0         |  |

|        |      |         |        |             |             |     |     |           |  |

| Bit    | 15   | 14      | 13     | 12          | 11          | 10  | 9   | 8         |  |

|        |      | HOU     | R[3:0] |             | MINUTE[5:2] |     |     |           |  |

| Access | R/W  | R/W     | R/W    | R/W         | R/W         | R/W | R/W | R/W       |  |

| Reset  | 0    | 0       | 0      | 0           | 0           | 0   | 0   | 0         |  |

|        |      |         |        |             |             |     |     |           |  |

| Bit    | 7    | 6       | 5      | 4           | 3           | 2   | 1   | 0         |  |

|        | MINU | TE[1:0] |        | SECOND[5:0] |             |     |     |           |  |

| Access | R/W  | R/W     | R/W    | R/W         | R/W         | R/W | R/W | R/W       |  |

| Reset  | 0    | 0       | 0      | 0           | 0           | 0   | 0   | 0         |  |

### Bits 31:26 - YEAR[5:0]: Year

The alarm year. Years are only matched if MASKn.SEL is 6.

### Bits 25:22 - MONTH[3:0]: Month

The alarm month. Months are matched only if MASKn.SEL is greater than 4.

### Bits 21:17 - DAY[4:0]: Day

The alarm day. Days are matched only if MASKn.SEL is greater than 3.

### Bits 16:12 - HOUR[4:0]: Hour

The alarm hour. Hours are matched only if MASKn.SEL is greater than 2.

### Bits 11:6 - MINUTE[5:0]: Minute

The alarm minute. Minutes are matched only if MASKn.SEL is greater than 1.

### Bits 5:0 – SECOND[5:0]: Second

The alarm second. Seconds are matched only if MASKn.SEL is greater than 0.

# **Reset:** 0x00X0 **Property:** PAC Write-Protection, Enable-Protected

| 15 | 14      | 13 | 12 | 11     | 10                 | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8                                                                                                                                                                                                                                                                                                  |

|----|---------|----|----|--------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |         |    |    | LVLEN3 | LVLEN2             | LVLEN1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LVLEN0                                                                                                                                                                                                                                                                                             |

|    |         |    |    | R/W    | R/W                | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W                                                                                                                                                                                                                                                                                                |

|    |         |    |    | 0      | 0                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                  |

|    |         |    |    |        |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                    |

| 7  | 6       | 5  | 4  | 3      | 2                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                  |

|    |         |    |    |        | CRCENABLE          | DMAENABLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SWRST                                                                                                                                                                                                                                                                                              |

|    |         |    |    |        | R/W                | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W                                                                                                                                                                                                                                                                                                |

|    |         |    |    |        | 0                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                  |

|    | 15<br>7 |    |    |        | LVLEN3<br>R/W<br>0 | Image: Constraint of the system         Image: Constand of the system         Image: Constando | Image: constraint of the systemImage: constraint of the systemImage: constraint of the systemImage: constraint of the system7654321765432176543217654321765432176543217676777777777777777777777777777777777777777777777777777777777777777777777777777777777777777777777777777777777777777777777777 |

# Bits 8, 9, 10, 11 – LVLENx: Priority Level x Enable

When this bit is set, all requests with the corresponding level will be fed into the arbiter block. When cleared, all requests with the corresponding level will be ignored.

For details on arbitration schemes, refer to the Arbitration section.

These bits are not enable-protected.

| Value | Description                                                 |

|-------|-------------------------------------------------------------|

| 0     | Transfer requests for Priority level x will not be handled. |

| 1     | Transfer requests for Priority level x will be handled.     |

### Bit 2 – CRCENABLE: CRC Enable

Writing a '0' to this bit will disable the CRC calculation when the CRC Status Busy flag is cleared (CRCSTATUS. CRCBUSY). The bit is zero when the CRC is disabled.

Writing a '1' to this bit will enable the CRC calculation.

| Value | Description                      |

|-------|----------------------------------|

| 0     | The CRC calculation is disabled. |

| 1     | The CRC calculation is enabled.  |

### Bit 1 – DMAENABLE: DMA Enable

Setting this bit will enable the DMA module.

Writing a '0' to this bit will disable the DMA module. When writing a '0' during an ongoing transfer, the bit will not be cleared until the internal data transfer buffer is empty and the DMA transfer is aborted. The internal data transfer buffer will be empty once the ongoing burst transfer is completed.

This bit is not enable-protected.

| Value | Description                 |

|-------|-----------------------------|

| 0     | The peripheral is disabled. |

| 1     | The peripheral is enabled.  |

### Bit 0 – SWRST: Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit when both the DMAC and the CRC module are disabled (DMAENABLE and CRCENABLE are '0') resets all registers in the DMAC (except DBGCTRL) to their initial state. If either the

| Bit    | 7              | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|--------|----------------|-----|-----|-----|-----|-----|-----|-----|--|--|

|        | CRCCHKSUM[7:0] |     |     |     |     |     |     |     |  |  |

| Access | R/W            | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Reset  | 0              | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

# Bits 31:0 – CRCCHKSUM[31:0]: CRC Checksum

These bits store the generated CRC result. When CRC-16 is enabled, the 16 msb will always read '0'.

These bits should only be read when CRC Module Busy bit in the CRC Status register CRCSTATUS.BUSY=0.

If CRC-16 is selected and CRCSTATUS.BUSY=0 (CRC generation is completed), this bit group will contain a valid checksum.

If CRC-32 is selected and CRCSTATUS.BUSY=0 (CRC generation is completed), this bit group will contain a valid *reversed* checksum, i.e.: bit 31 is swapped with bit 0, bit 30 with bit 1, etc.

### 20.8.5 CRC Status

Name:CRCSTATUSOffset:0x0CReset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1       | 0       |

|--------|---|---|---|---|---|---|---------|---------|

|        |   |   |   |   |   |   | CRCZERO | CRCBUSY |

| Access |   |   |   |   |   |   | R       | R/W     |

| Reset  |   |   |   |   |   |   | 0       | 0       |

### Bit 1 – CRCZERO: CRC Zero

This bit is cleared when a new CRC source is selected.

This bit is set when the CRC generation is complete and the CRC Checksum is zero.

When running CRC-32 and appending the checksum at the end of the packet (as little endian), the final checksum should be 0x2144df1c, and not zero. However, if the checksum is complemented before it is appended (as little endian) to the data, the final result in the checksum register will be zero. See the description of CRCCHKSUM to read out different versions of the checksum.

# Bit 0 – CRCBUSY: CRC Module Busy

This flag is cleared by writing a one to it when used with I/O interface. When used with a DMA channel, the bit is set when the corresponding DMA channel is enabled, and cleared when the corresponding DMA channel is disabled. This register bit cannot be cleared by the application when the CRC is used with a DMA channel.

This bit is set when a source configuration is selected and as long as the source is using the CRC module.

### 20.8.6 Debug Control

Name:DBGCTRLOffset:0x0DReset:0x00

| Bit    | 7 | 6 | 5 | 4             | 3 | 2           | 1 | 0     |

|--------|---|---|---|---------------|---|-------------|---|-------|

|        |   |   |   | BLOCKACT[1:0] |   | EVOSEL[1:0] |   | VALID |

| Access |   |   |   |               |   |             |   |       |

Reset

# Bits 15:13 – STEPSIZE[2:0]: Address Increment Step Size

These bits select the address increment step size. The setting apply to source or destination address, depending on STEPSEL setting.

| Value | Name | Description                                  |

|-------|------|----------------------------------------------|

| 0x0   | X1   | Next ADDR = ADDR + (Beat size in byte) * 1   |

| 0x1   | X2   | Next ADDR = ADDR + (Beat size in byte) * 2   |

| 0x2   | X4   | Next ADDR = ADDR + (Beat size in byte) * 4   |

| 0x3   | X8   | Next ADDR = ADDR + (Beat size in byte) * 8   |

| 0x4   | X16  | Next ADDR = ADDR + (Beat size in byte) * 16  |

| 0x5   | X32  | Next ADDR = ADDR + (Beat size in byte) * 32  |

| 0x6   | X64  | Next ADDR = ADDR + (Beat size in byte) * 64  |

| 0x7   | X128 | Next ADDR = ADDR + (Beat size in byte) * 128 |

# Bit 12 – STEPSEL: Step Selection

This bit selects if source or destination addresses are using the step size settings.

| Value | Name | Description                                         |

|-------|------|-----------------------------------------------------|

| 0x0   | DST  | Step size settings apply to the destination address |

| 0x1   | SRC  | Step size settings apply to the source address      |

# Bit 11 – DSTINC: Destination Address Increment Enable

Writing a '0' to this bit will disable the destination address incrementation. The address will be kept fixed during the data transfer.

Writing a '1' to this bit will enable the destination address incrementation. By default, the destination address is incremented by 1. If the STEPSEL bit is cleared, flexible step-size settings are available in the STEPSIZE register.

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | The Destination Address Increment is disabled. |

| 1     | The Destination Address Increment is enabled.  |

# Bit 10 – SRCINC: Source Address Increment Enable

Writing a '0' to this bit will disable the source address incrementation. The address will be kept fixed during the data transfer.

Writing a '1' to this bit will enable the source address incrementation. By default, the source address is incremented by 1. If the STEPSEL bit is set, flexible step-size settings are available in the STEPSIZE register.

| Value | Description                               |

|-------|-------------------------------------------|

| 0     | The Source Address Increment is disabled. |

| 1     | The Source Address Increment is enabled.  |

# Bits 9:8 – BEATSIZE[1:0]: Beat Size

These bits define the size of one beat. A beat is the size of one data transfer bus access, and the setting apply to both read and write accesses.

### 23.6.2 Basic Operation

### 23.6.2.1 Initialization

After reset, all standard function device I/O pads are connected to the PORT with outputs tri-stated and input buffers disabled, even if there is no clock running.

However, specific pins, such as those used for connection to a debugger, may be configured differently, as required by their special function.

### 23.6.2.2 Operation

Each I/O pin y can be controlled by the registers in PORT. Each PORT group has its own set of PORT registers, the base address of the register set for pin y is at byte address PORT + ([y] \* 0x4). The index within that register set is [y].

To use pin number y as an *output*, write bit y of the DIR register to '1'. This can also be done by writing bit y in the DIRSET register to '1' - this will avoid disturbing the configuration of other pins in that group. The y bit in the OUT register must be written to the desired output value.

Similarly, writing an OUTSET bit to '1' will set the corresponding bit in the OUT register to '1'. Writing a bit in OUTCLR to '1' will set that bit in OUT to zero. Writing a bit in OUTTGL to '1' will toggle that bit in OUT.

To use pin y as an *input*, bit y in the DIR register must be written to '0'. This can also be done by writing bit y in the DIRCLR register to '1' - this will avoid disturbing the configuration of other pins in that group. The input value can be read from bit y in register IN as soon as the INEN bit in the Pin Configuration register (PINCFGy.INEN) is written to '1'.

Refer to I/O Multiplexing and Considerations for details on pin configuration and PORT groups.

By default, the input synchronizer is clocked only when an input read is requested. This will delay the read operation by two CLK\_PORT cycles. To remove the delay, the input synchronizers for each PORT group of eight pins can be configured to be always active, but this will increase power consumption. This is enabled by writing '1' to the corresponding SAMPLINGn bit field of the CTRL register, see CTRL.SAMPLING for details.

To use pin y as one of the available peripheral functions, the corresponding PMUXEN bit of the PINCFGy register must be '1'. The PINCFGy register for pin y is at byte offset (PINCFG0 + [y]).

The peripheral function can be selected by setting the PMUXO or PMUXE in the PMUXn register. The PMUXO/PMUXE is at byte offset PMUX0 + (y/2). The chosen peripheral must also be configured and enabled.

### **Related Links**

I/O Multiplexing and Considerations

# 23.6.3 I/O Pin Configuration

The Pin Configuration register (PINCFGy) is used for additional I/O pin configuration. A pin can be set in a totem-pole or pull configuration.

As pull configuration is done through the Pin Configuration register, all intermediate PORT states during switching of pin direction and pin values are avoided.

The I/O pin configurations are described further in this chapter, and summarized in Table 23-2.

| _      |            |          |        |         |  |         |         |         |

|--------|------------|----------|--------|---------|--|---------|---------|---------|

| Offset | Name       | Bit Pos. |        |         |  |         |         |         |

| 0x2C   |            |          |        |         |  |         |         |         |

|        | Reserved   |          |        |         |  |         |         |         |

| 0x2F   |            |          |        |         |  |         |         |         |

| 0x30   | PMUX0      | 7:0      | PMU>   | (O[3:0] |  | PMUX    | (E[3:0] |         |

| 0x31   | PMUX1      | 7:0      | PMU>   | (O[3:0] |  |         | (E[3:0] |         |

| 0x32   | PMUX2      | 7:0      | PMU    | (O[3:0] |  | PMUX    | (E[3:0] |         |

| 0x33   | PMUX3      | 7:0      | PMU    | (O[3:0] |  | PMUX    | (E[3:0] |         |

| 0x34   | PMUX4      | 7:0      | PMU    | (O[3:0] |  | PMUX    | (E[3:0] |         |

| 0x35   | PMUX5      | 7:0      | PMU>   | (O[3:0] |  | PMUX    | (E[3:0] |         |

| 0x36   | PMUX6      | 7:0      | PMU>   | (O[3:0] |  | PMUX    | (E[3:0] |         |

| 0x37   | PMUX7      | 7:0      | PMUX   | (O[3:0] |  | PMUX    | (E[3:0] |         |

| 0x38   | PMUX8      | 7:0      | PMU>   | (O[3:0] |  | PMUX    | (E[3:0] |         |

| 0x39   | PMUX9      | 7:0      | PMUX   | (O[3:0] |  | PMUX    | (E[3:0] |         |

| 0x3A   | PMUX10     | 7:0      |        | (O[3:0] |  |         | (E[3:0] |         |

| 0x3B   | PMUX11     | 7:0      | PMU>   | (O[3:0] |  | PMU     | (E[3:0] |         |

| 0x3C   | PMUX12     | 7:0      | PMUX   | (O[3:0] |  | PMUX    | (E[3:0] |         |

| 0x3D   | PMUX13     | 7:0      | PMU>   | (O[3:0] |  | PMU     | (E[3:0] |         |

| 0x3E   | PMUX14     | 7:0      | PMUX   | (O[3:0] |  | PMU     | (E[3:0] |         |

| 0x3F   | PMUX15     | 7:0      | PMU>   | (O[3:0] |  | PMU     | (E[3:0] |         |

| 0x40   | PINCFG0    | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x41   | PINCFG1    | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x42   | PINCFG2    | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x43   | PINCFG3    | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x44   | PINCFG4    | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x45   | PINCFG5    | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x46   | PINCFG6    | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x47   | PINCFG7    | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x48   | PINCFG8    | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x49   | PINCFG9    | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x4A   | PINCFG10   | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x4B   | PINCFG11   | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x4C   | PINCFG12   | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x4D   | PINCFG13   | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x4E   | PINCFG14   | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x4F   | PINCFG15   | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x50   | PINCFG16   | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x51   | PINCFG17   | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x52   | PINCFG18   | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x53   | PINCFG19   | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x54   | PINCFG20   | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x55   | PINCFG21   | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x56   | PINCFG22   | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x57   | PINCFG23   | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x58   | PINCFG24   | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x59   | PINCFG25   | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x5A   | PINCFG26   | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0x5B   | PINCFG27   | 7:0      | DRVSTR |         |  | PULLEN  | INEN    | PMUXEN  |

| 0,00   | 1 1101 021 | 1.0      | DRUGHR |         |  | I OLLEN |         | T MOALN |

# 29.4 Signal Description

# Table 29-1. Master Mode

| Pin Name | Pin Description                                                 | Туре         |

|----------|-----------------------------------------------------------------|--------------|

| MCKn     | Master Clock for Clock Unit n                                   | Input/Output |

| SCKn     | Serial Clock for Clock Unit n                                   | Input/Output |

| FSn      | I <sup>2</sup> S Word Select or TDM Frame Sync for Clock Unit n | Input/Output |

| SDm      | Serial Data Input or Output for Serializer m                    | Input/Output |

# Table 29-2. Slave Mode

| Pin Name | Pin Description                                | Туре         |

|----------|------------------------------------------------|--------------|

| MCKn     | Master Clock                                   | Input        |

| SCKn     | Serial Clock for Clock Unit n                  | Input        |

| FSn      | I <sup>2</sup> S Word Select or TDM Frame Sync | Input        |

| SDm      | Serial Data Input or Output for Serializer m   | Input/Output |

# Table 29-3. Controller Mode

| Pin Name | Pin Description                                | Туре           |

|----------|------------------------------------------------|----------------|

| MCKn     | Master Clock for Clock Unit n                  | Output         |

| SCKn     | Serial Clock for Clock Unit n                  | Output         |

| FSn      | I <sup>2</sup> S Word Select or TDM Frame Sync | Output         |

| SDm      | Not Applicable                                 | Not Applicable |

Note: One signal can be mapped on several pins.

# **Related Links**

I/O Multiplexing and Considerations

# 29.5 **Product Dependencies**

In order to use this module, other parts of the system must be configured correctly, as described below.

# 29.5.1 I/O Lines

Using the  $I^2S$  I/O lines requires the I/O pins to be configured.

The I<sup>2</sup>S pins may be multiplexed with I/O Controller lines. The user must first program the I/O Controller to assign the desired I<sup>2</sup>S pins to their peripheral function. If the I<sup>2</sup>S I/O lines are not used by the application, they can be used for other purposes by the I/O Controller. It is required to enable only the I<sup>2</sup>S inputs and outputs actually in use.

# **Related Links**

PORT - I/O Pin Controller

| Value | Name    | Description             |

|-------|---------|-------------------------|

| 0x0   | DIV1    | Prescaler: GCLK_TC      |

| 0x1   | DIV2    | Prescaler: GCLK_TC/2    |

| 0x2   | DIV4    | Prescaler: GCLK_TC/4    |

| 0x3   | DIV8    | Prescaler: GCLK_TC/8    |

| 0x4   | DIV16   | Prescaler: GCLK_TC/16   |

| 0x5   | DIV64   | Prescaler: GCLK_TC/64   |

| 0x6   | DIV256  | Prescaler: GCLK_TC/256  |

| 0x7   | DIV1024 | Prescaler: GCLK_TC/1024 |

# Bits 6:5 – WAVEGEN[1:0]: Waveform Generation Operation

These bits select the waveform generation operation. They affect the top value, as shown in "Waveform Output Operations". It also controls whether frequency or PWM waveform generation should be used. How these modes differ can also be seen from "Waveform Output Operations".

These bits are not synchronized.

| Table 30-7. | Waveform | Generation | Operation |

|-------------|----------|------------|-----------|

|-------------|----------|------------|-----------|

| Value | Name | Operation           | Top Value               | Waveform<br>Output on<br>Match                         | Waveform<br>Output on<br>Wraparound                    |

|-------|------|---------------------|-------------------------|--------------------------------------------------------|--------------------------------------------------------|

| 0x0   | NFRQ | Normal<br>frequency | PER <sup>(1)</sup> /Max | Toggle                                                 | No action                                              |

| 0x1   | MFRQ | Match<br>frequency  | CC0                     | Toggle                                                 | No action                                              |

| 0x2   | NPWM | Normal PWM          | PER <sup>(1)</sup> /Max | Clear when<br>counting up Set<br>when counting<br>down | Set when<br>counting up<br>Clear when<br>counting down |

| 0x3   | MPWM | Match PWM           | CC0                     | Clear when<br>counting up Set<br>when counting<br>down | Set when<br>counting up<br>Clear when<br>counting down |

# Note:

1. This depends on the TC mode. In 8-bit mode, the top value is the Period Value register (PER). In 16- and 32-bit mode it is the maximum value.

# Bits 3:2 – MODE[1:0]: Timer Counter Mode

These bits select the counter mode.

These bits are not synchronized.

| Value | Name    | Description            |

|-------|---------|------------------------|

| 0x0   | COUNT16 | Counter in 16-bit mode |

| 0x1   | COUNT8  | Counter in 8-bit mode  |

| 0x2   | COUNT32 | Counter in 32-bit mode |

| 0x3   | -       | Reserved               |

# 31.6.2.7 Capture Operations

To enable and use capture operations, the Match or Capture Channel x Event Input Enable bit in the Event Control register (EVCTRL.MCEIx) must be written to '1'. The capture channels to be used must also be enabled in the Capture Channel x Enable bit in the Control A register (CTRLA.CPTENx) before capturing can be performed.

### **Event Capture Action**

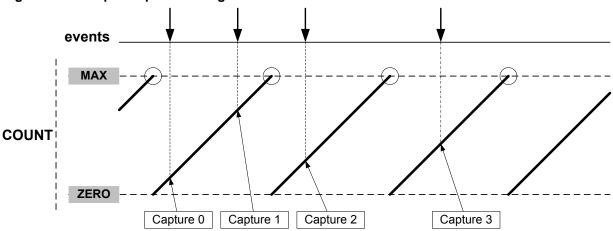

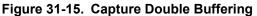

The compare/capture channels can be used as input capture channels to capture events from the Event System, and give them a timestamp. The following figure shows four capture events for one capture channel.

Figure 31-14. Input Capture Timing

For input capture, the buffer register and the corresponding CCx act like a FIFO. When CCx is empty or read, any content in CCBx is transferred to CCx. The buffer valid flag is passed to set the CCx interrupt flag (IF) and generate the optional interrupt, event or DMA request. CCBx register value can't be read, all captured data must be read from CCx register.

The TCC can detect capture overflow of the input capture channels: When a new capture event is detected while the Capture Buffer Valid flag (STATUS.CCBV) is still set, the new timestamp will not be stored and INTFLAG.ERR will be set.

# Period and Pulse-Width (PPW) Capture Action

| Bit    | 23     | 22     | 21     | 20     | 19  | 18  | 17  | 16  |

|--------|--------|--------|--------|--------|-----|-----|-----|-----|

|        |        |        |        |        | MC3 | MC2 | MC1 | MC0 |

| Access |        |        |        |        | R/W | R/W | R/W | R/W |

| Reset  |        |        |        |        | 0   | 0   | 0   | 0   |

|        |        |        |        |        |     |     |     |     |

| Bit    | 15     | 14     | 13     | 12     | 11  | 10  | 9   | 8   |

|        | FAULT1 | FAULT0 | FAULTB | FAULTA | DFS |     |     |     |

| Access | R/W    | R/W    | R/W    | R/W    | R/W |     |     |     |

| Reset  | 0      | 0      | 0      | 0      | 0   |     |     |     |

|        |        |        |        |        |     |     |     |     |

| Bit    | 7      | 6      | 5      | 4      | 3   | 2   | 1   | 0   |

|        |        |        |        |        | ERR | CNT | TRG | OVF |

| Access |        |        |        |        | R/W | R/W | R/W | R/W |

| Reset  |        |        |        |        | 0   | 0   | 0   | 0   |

### Bits 19,18,17,16 – MCx: Match or Capture Channel x Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the corresponding Match or Capture Channel x Interrupt Disable/Enable bit, which disables the Match or Capture Channel x interrupt.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | The Match or Capture Channel x interrupt is disabled. |

| 1     | The Match or Capture Channel x interrupt is enabled.  |

### Bits 15,14 – FAULTx: Non-Recoverable Fault x Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Non-Recoverable Fault x Interrupt Disable/Enable bit, which disables the Non-Recoverable Fault x interrupt.

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | The Non-Recoverable Fault x interrupt is disabled. |

| 1     | The Non-Recoverable Fault x interrupt is enabled.  |

### Bit 13 – FAULTB: Recoverable Fault B Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Recoverable Fault B Interrupt Disable/Enable bit, which disables the Recoverable Fault B interrupt.

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | The Recoverable Fault B interrupt is disabled. |

| 1     | The Recoverable Fault B interrupt is enabled.  |

### Bit 12 – FAULTA: Recoverable Fault A Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Recoverable Fault A Interrupt Disable/Enable bit, which disables the Recoverable Fault A interrupt.

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | The Recoverable Fault A interrupt is disabled. |

| 1     | The Recoverable Fault A interrupt is enabled.  |

| Mode    | Conditions                           | T <sub>A</sub> | V <sub>cc</sub> | Тур. | Max. | Units |

|---------|--------------------------------------|----------------|-----------------|------|------|-------|

| IDLE0   | Default operating conditions         | 25°C           | 3.3V            | 2.4  | 2.5  | mA    |

|         |                                      | 85°C           | 3.3V            | 2.5  | 2.6  |       |

| IDLE1   | Default operating conditions         | 25°C           | 3.3V            | 1.8  | 1.9  |       |

|         |                                      | 85°C           | 3.3V            | 1.9  | 2.0  |       |

| IDLE2   | Default operating conditions         | 25°C           | 3.3V            | 1.3  | 1.4  |       |

|         |                                      | 85°C           | 3.3V            | 1.4  | 1.5  |       |

| STANDBY | XOSC32K running, RTC running at 1kHz | 25°C           | 3.3V            | 4    | 6.2  | μΑ    |

|         |                                      | 85°C           | 3.3V            | 54   | 100  |       |

|         |                                      | 25°C           | 3.3V            | 2.8  | 5.0  |       |

|         |                                      | 85°C           | 3.3V            | 52   | 98.8 |       |

# Table 37-9. Current Consumption (Device Variant B and C / Die Revision F)

| Mode   | Conditions                                                        | T <sub>A</sub> | V <sub>cc</sub> | Тур.         | Max.         | Units                    |

|--------|-------------------------------------------------------------------|----------------|-----------------|--------------|--------------|--------------------------|

| ACTIVE | CPU running a While 1<br>algorithm                                | 25°C           | 3.3V            | 3.7          | 3.9          | mA                       |