#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                |                                                                            |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                               |

| Data Converters            | A/D 20x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-UFBGA                                                                   |

| Supplier Device Package    | 64-UFBGA (5x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd21j17a-cut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 32-bit ARM-Based Microcontrollers

| Device Variant     | DID.DEVSEL  | Device ID (DID)             |

|--------------------|-------------|-----------------------------|

| Reserved           | 0x25        |                             |

| SAMD21E16B         | 0x26        | 0x10011426 (die revision E) |

|                    |             | 0x10011526 (die revision F) |

| SAMD21E15B         | 0x27        | 0x10011427 (die revision E) |

|                    |             | 0x10011527 (die revision F) |

| Reserved           | 0x28-0x54   |                             |

| SAMD21E16B (WLCSP) | 0x55        | 0x10011455 (die revision E) |

| SAMD21E15B (WLCSP) | 0x56        | 0x10011456 (die revision E) |

| Reserved           | 0x57 - 0x61 |                             |

| SAMD21E16C (WLCSP) | 0x62        | 0x10011562 (die revision F) |

| SAMD21E15C (WLCSP) | 0x63        | 0x10011563 (die revision F) |

| Reserved           | 0x64-0xFF   |                             |

**Note:** The device variant (last letter of the ordering number) is independent of the die revision (DSU.DID.REVISION): The device variant denotes functional differences, whereas the die revision marks evolution of the die. The device variant denotes functional differences, whereas the die revision marks evolution of the die.

# **Related Links**

DID

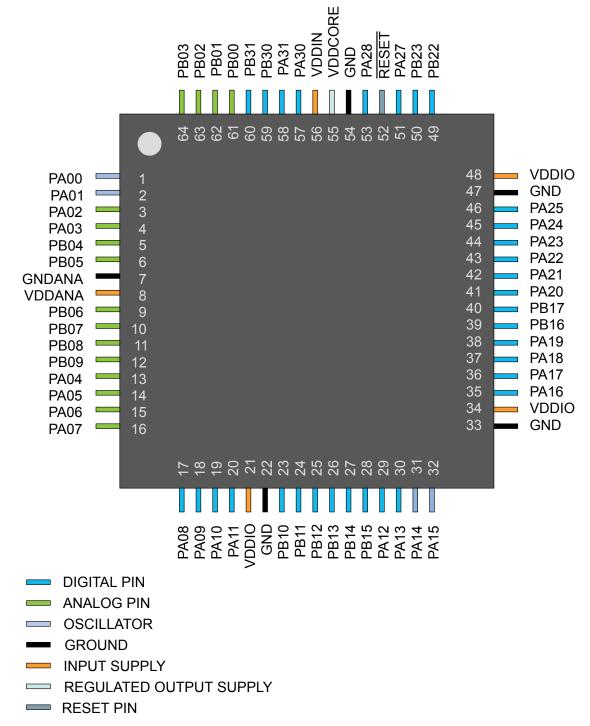

# 5. Pinout

# 5.1 SAM D21J

5.1.1 QFN64 / TQFP64

# 11.2.2 Interrupt Line Mapping

Each of the 28 interrupt lines is connected to one peripheral instance, as shown in the table below. Each peripheral can have one or more interrupt flags, located in the peripheral's Interrupt Flag Status and Clear (INTFLAG) register. The interrupt flag is set when the interrupt condition occurs. Each interrupt in the peripheral can be individually enabled by writing a one to the corresponding bit in the peripheral's Interrupt Enable Set (INTENSET) register, and disabled by writing a one to the corresponding bit in the peripheral's Interrupt Enable Clear (INTENCLR) register. An interrupt request is generated from the peripheral are ORed together on system level, generating one interrupt request for each peripheral. An interrupt request will set the corresponding interrupt pending bit in the NVIC interrupt, it must be enabled in the NVIC interrupt enable register (SETPEND/CLRPEND bits in ISPR/ICPR). For the NVIC to activate the interrupt, it must be enabled in the NVIC interrupt enable register (SETENA/CLRENA bits in ISER/ICER). The NVIC interrupt priority registers IPR0-IPR7 provide a priority field for each interrupt.

| Peripheral Source                          | NVIC Line |

|--------------------------------------------|-----------|

| EIC NMI – External Interrupt Controller    | NMI       |

| PM – Power Manager                         | 0         |

| SYSCTRL – System Control                   | 1         |

| WDT – Watchdog Timer                       | 2         |

| RTC – Real Time Counter                    | 3         |

| EIC – External Interrupt Controller        | 4         |

| NVMCTRL – Non-Volatile Memory Controller   | 5         |

| DMAC - Direct Memory Access Controller     | 6         |

| USB - Universal Serial Bus                 | 7         |

| EVSYS – Event System                       | 8         |

| SERCOM0 – Serial Communication Interface 0 | 9         |

| SERCOM1 – Serial Communication Interface 1 | 10        |

| SERCOM2 – Serial Communication Interface 2 | 11        |

| SERCOM3 – Serial Communication Interface 3 | 12        |

| SERCOM4 – Serial Communication Interface 4 | 13        |

| SERCOM5 – Serial Communication Interface 5 | 14        |

| TCC0 – Timer Counter for Control 0         | 15        |

| TCC1 – Timer Counter for Control 1         | 16        |

| TCC2 – Timer Counter for Control 2         | 17        |

| TC3 – Timer Counter 3                      | 18        |

| TC4 – Timer Counter 4                      | 19        |

| TC5 – Timer Counter 5                      | 20        |

# Bit 13 – FORCELDO: Force LDO Voltage Regulator

| Value | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| 0     | The voltage regulator is in low power and low drive configuration in standby sleep mode.  |

| 1     | The voltage regulator is in low power and high drive configuration in standby sleep mode. |

### Bit 6 – RUNSTDBY: Run in Standby

| Value | Description                                                                |

|-------|----------------------------------------------------------------------------|

| 0     | The voltage regulator is in low power configuration in standby sleep mode. |

| 1     | The voltage regulator is in normal configuration in standby sleep mode.    |

## 17.8.16 Voltage References System (VREF) Control

Name:VREFOffset:0x40Reset:0x0XXX0000Property:Write-Protected

| Bit    | 31       | 30  | 29  | 28    | 27     | 26      | 25          | 24  |

|--------|----------|-----|-----|-------|--------|---------|-------------|-----|

|        |          |     |     |       |        |         | CALIB[10:8] |     |

| Access |          |     |     |       |        | R/W     | R/W         | R/W |

| Reset  |          |     |     |       |        | x       | x           | x   |

|        |          |     |     |       |        |         |             |     |

| Bit    | 23       | 22  | 21  | 20    | 19     | 18      | 17          | 16  |

|        |          |     |     | CALII | B[7:0] |         |             |     |

| Access | R/W      | R/W | R/W | R/W   | R/W    | R/W     | R/W         | R/W |

| Reset  | x        | x   | x   | x     | x      | x       | x           | x   |

|        |          |     |     |       |        |         |             |     |

| Bit    | 15       | 14  | 13  | 12    | 11     | 10      | 9           | 8   |

|        |          |     |     |       |        |         |             |     |

| Access |          |     | •   |       |        |         |             |     |

| Reset  |          |     |     |       |        |         |             |     |

|        |          |     |     |       |        |         |             |     |

| Bit    | 7        | 6   | 5   | 4     | 3      | 2       | 1           | 0   |

|        |          |     |     |       |        | BGOUTEN | TSEN        |     |

| Access | <b>-</b> |     |     |       |        | R/W     | R/W         |     |

| Reset  |          |     |     |       |        | 0       | 0           |     |

|        |          |     |     |       |        |         |             |     |

# Bits 26:16 – CALIB[10:0]: Bandgap Voltage Generator Calibration

These bits are used to calibrate the output level of the bandgap voltage reference. These bits are loaded from Flash Calibration Row at startup.

#### **Bit 2 – BGOUTEN: Bandgap Output Enable**

| Value | Description                                                  |

|-------|--------------------------------------------------------------|

| 0     | The bandgap output is not available as an ADC input channel. |

| 1     | The bandgap output is routed to an ADC input channel.        |

### Bit 1 – TSEN: Temperature Sensor Enable

# **Reset:** 0x00 **Property:** Write-Protected

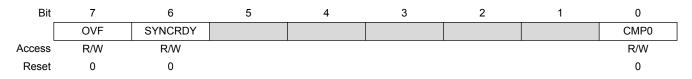

| Bit    | 7   | 6       | 5 | 4 | 3 | 2 | 1 | 0      |

|--------|-----|---------|---|---|---|---|---|--------|

|        | OVF | SYNCRDY |   |   |   |   |   | ALARM0 |

| Access | R/W | R/W     |   |   |   |   |   | R/W    |

| Reset  | 0   | 0       |   |   |   |   |   | 0      |

# Bit 7 – OVF: Overflow Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the Overflow Interrupt Enable bit and enable the Overflow interrupt.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The overflow interrupt is disabled. |

| 1     | The overflow interrupt is enabled.  |

# Bit 6 – SYNCRDY: Synchronization Ready Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the Synchronization Ready Interrupt bit and enable the Synchronization Ready interrupt.

| Value | Description                                      |

|-------|--------------------------------------------------|

| 0     | The synchronization ready interrupt is disabled. |

| 1     | The synchronization ready interrupt is enabled.  |

# Bit 0 – ALARM0: Alarm 0 Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the Alarm 0 Interrupt Enable bit and enable the Alarm 0 interrupt.

| Value | Description                        |

|-------|------------------------------------|

| 0     | The alarm 0 interrupt is disabled. |

| 1     | The alarm 0 interrupt is enabled.  |

# 19.8.14 Interrupt Flag Status and Clear - MODE0

| Name:            | INTFLAG |

|------------------|---------|

| Offset:          | 0x08    |

| Reset:           | 0x00    |

| <b>Property:</b> | -       |

# Bit 7 – OVF: Overflow

This flag is cleared by writing a one to the flag.

| Value | Description                                                          |

|-------|----------------------------------------------------------------------|

| 0     | The correction value is positive, i.e., frequency will be increased. |

| 1     | The correction value is negative, i.e., frequency will be decreased. |

## Bits 6:0 – VALUE[6:0]: Correction Value

These bits define the amount of correction applied to the RTC prescaler.

1–127: The RTC frequency is adjusted according to the value.

| Value | Description                                                |

|-------|------------------------------------------------------------|

| 0     | Correction is disabled and the RTC frequency is unchanged. |

#### 19.8.20 Counter Value - MODE0

Name: COUNT

Offset: 0x10

**Reset:** 0x0000000

Property: Read-Synchronized, Write-Protected, Write-Synchronized

| Bit    | 31           | 30  | 29  | 28    | 27       | 26  | 25  | 24  |  |  |  |  |

|--------|--------------|-----|-----|-------|----------|-----|-----|-----|--|--|--|--|

|        | COUNT[31:24] |     |     |       |          |     |     |     |  |  |  |  |

| Access | R/W          | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |  |  |

| Reset  | 0            | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |  |  |  |

|        |              |     |     |       |          |     |     |     |  |  |  |  |

| Bit    | 23           | 22  | 21  | 20    | 19       | 18  | 17  | 16  |  |  |  |  |

|        |              |     |     | COUNT | F[23:16] |     |     |     |  |  |  |  |

| Access | R/W          | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |  |  |

| Reset  | 0            | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |  |  |  |

|        |              |     |     |       |          |     |     |     |  |  |  |  |

| Bit    | 15           | 14  | 13  | 12    | 11       | 10  | 9   | 8   |  |  |  |  |

|        |              |     |     | COUN  | T[15:8]  |     |     |     |  |  |  |  |

| Access | R/W          | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |  |  |

| Reset  | 0            | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |  |  |  |

|        |              |     |     |       |          |     |     |     |  |  |  |  |

| Bit    | 7            | 6   | 5   | 4     | 3        | 2   | 1   | 0   |  |  |  |  |

|        |              |     |     | COUN  | IT[7:0]  |     |     |     |  |  |  |  |

| Access | R/W          | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |  |  |

| Reset  | 0            | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |  |  |  |

# Bits 31:0 - COUNT[31:0]: Counter Value

These bits define the value of the 32-bit RTC counter.

#### 19.8.21 Counter Value - MODE1

Name:COUNTOffset:0x10Reset:0x0000Property:Read-Synchronized, Write-Protected, Write-Synchronized

# 20.6.6 Events

The DMAC can generate the following output events:

• Channel (CH): Generated when a block transfer for a given channel has been completed, or when a beat transfer within a block transfer for a given channel has been completed. Refer to Event Output Selection section for details.

Setting the Channel Control B Event Output Enable bit (CHCTRLB.EVOE=1) enables the corresponding output event configured in the Event Output Selection bit group in the Block Transfer Control register (BTCTRL.EVOSEL). Clearing CHCTRLB.EVOE=0 disables the corresponding output event.

The DMAC can take the following actions on an input event:

- Transfer and Periodic Transfer Trigger (TRIG): normal transfer or periodic transfers on peripherals are enabled

- Conditional Transfer Trigger (CTRIG): conditional transfers on peripherals are enabled

- Conditional Block Transfer Trigger (CBLOCK): conditional block transfers on peripherals are enabled

- Channel Suspend Operation (SUSPEND): suspend a channel operation

- Channel Resume Operation (RESUME): resume a suspended channel operation

- Skip Next Block Suspend Action (SSKIP): skip the next block suspend transfer condition

- Increase Priority (INCPRI): increase channel priority

Setting the Channel Control B Event Input Enable bit (CHCTRLB.EVIE=1) enables the corresponding action on input event. clearing this bit disables the corresponding action on input event. Note that several actions can be enabled for incoming events. If several events are connected to the peripheral, any enabled action will be taken for any of the incoming events. For further details on event input actions, refer to Event Input Action section.

#### **Related Links**

EVSYS – Event System

# 20.6.7 Sleep Mode Operation

Each DMA channel can be configured to operate in any sleep mode. To be able to run in standby, the RUNSTDBY bit in Channel Control A register (CHCTRLA.RUNSTDBY) must be written to '1'. The DMAC can wake up the device using interrupts from any sleep mode or perform actions through the Event System.

For channels with CHCTRLA.RUNSTDBY=0, it is up to software to stop DMA transfers on these channels and wait for completion before going to standby mode using the following sequence:

- 1. Suspend the DMAC channels for which CHCTRLA.RUNSTDBY=0.

- 2. Check the SYNCBUSY bits of registers accessed by the DMAC channels being suspended.

- 3. Go to sleep

- 4. When the device wakes up, resume the suspended channels.

**Note:** In standby sleep mode, the DMAC can only access RAM when it is not back biased (PM.STDBYCFG.BBIASxx=0x0)

# 20.6.8 Synchronization

Not applicable.

# 32-bit ARM-Based Microcontrollers

| Value | Name  | Description         |

|-------|-------|---------------------|

| 0x0   | BYTE  | 8-bit bus transfer  |

| 0x1   | HWORD | 16-bit bus transfer |

| 0x2   | WORD  | 32-bit bus transfer |

| other |       | Reserved            |

# Bits 4:3 – BLOCKACT[1:0]: Block Action

These bits define what actions the DMAC should take after a block transfer has completed.

| BLOCKACT[1:0] | Name    | Description                                                                                      |

|---------------|---------|--------------------------------------------------------------------------------------------------|

| 0x0           | NOACT   | Channel will be disabled if it is the last block transfer in the transaction                     |

| 0x1           | INT     | Channel will be disabled if it is the last block transfer in the transaction and block interrupt |

| 0x2           | SUSPEND | Channel suspend operation is completed                                                           |

| 0x3           | BOTH    | Both channel suspend operation and block interrupt                                               |

# Bits 2:1 – EVOSEL[1:0]: Event Output Selection

These bits define the event output selection.

| EVOSEL[1:0] | Name    | Description                               |

|-------------|---------|-------------------------------------------|

| 0x0         | DISABLE | Event generation disabled                 |

| 0x1         | BLOCK   | Event strobe when block transfer complete |

| 0x2         |         | Reserved                                  |

| 0x3         | BEAT    | Event strobe when beat transfer complete  |

# Bit 0 – VALID: Descriptor Valid

Writing a '0' to this bit in the Descriptor or Write-Back memory will suspend the DMA channel operation when fetching the corresponding descriptor.

The bit is automatically cleared in the Write-Back memory section when channel is aborted, when an error is detected during the block transfer, or when the block transfer is completed.

| Value | Description                  |

|-------|------------------------------|

| 0     | The descriptor is not valid. |

| 1     | The descriptor is valid.     |

# 20.10.2 Block Transfer Count

The BTCNT register offset is relative to (BASEADDR or WRBADDR) + Channel Number \* 0x10

Name: BTCNT Offset: 0x02 Reset: -Property: -

| Figure 22-4. EEPROM and Boot L |                                           |

|--------------------------------|-------------------------------------------|

| EEPROM Emulation allocation    | NVM Base Address + NVM size               |

|                                | NVM Base Address + NVM size - EEPROM size |

| Program<br>allocation          |                                           |

|                                | NVM Base Address + BOOTPROT size          |

| BOOT<br>allocation             |                                           |

| Delated Links                  | NVM Base Address                          |

Figure 22-4. EEPROM and Boot Loader Allocation

**Related Links**

Physical Memory Map

# 22.6.3 Region Lock Bits

The NVM block is grouped into 16 equally sized regions. The region size is dependent on the Flash memory size, and is given in the table below. Each region has a dedicated lock bit preventing writing and erasing pages in the region. After production, all regions will be unlocked.

# Table 22-1. Region Size

| Memory Size [KB] | Region Size [KB] |

|------------------|------------------|

| 256              | 16               |

| 128              | 8                |

| 64               | 4                |

| 32               | 2                |

To lock or unlock a region, the Lock Region and Unlock Region commands are provided. Writing one of these commands will temporarily lock/unlock the region containing the address loaded in the ADDR register. ADDR can be written by software, or the automatically loaded value from a write operation can be used. The new setting will stay in effect until the next Reset, or until the setting is changed again using

© 2017 Microchip Technology Inc.

# 24.4 Signal Description

Not applicable.

# 24.5 **Product Dependencies**

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

### 24.5.1 I/O Lines

Not applicable.

### 24.5.2 Power Management

The EVSYS can be used to wake up the CPU from all sleep modes, even if the clock used by the EVSYS channel and the EVSYS bus clock are disabled. Refer to the *PM* – *Power Manager* for details on the different sleep modes.

In all sleep modes, although the clock for the EVSYS is stopped, the device still can wake up the EVSYS clock. Some event generators can generate an event when their clocks are stopped.

#### **Related Links**

PM – Power Manager

## 24.5.3 Clocks

The EVSYS bus clock (CLK\_EVSYS\_APB) can be enabled and disabled in the Main Clock module, and the default state of CLK\_EVSYS\_APB can be found in *Peripheral Clock Masking*.

Each EVSYS channel has a dedicated generic clock (GCLK\_EVSYS\_CHANNEL\_n). These are used for event detection and propagation for each channel. These clocks must be configured and enabled in the generic clock controller before using the EVSYS. Refer to *GCLK* - *Generic Clock Controller* for details.

#### **Related Links**

Peripheral Clock Masking GCLK - Generic Clock Controller

# 24.5.4 DMA

Not applicable.

#### 24.5.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. Using the EVSYS interrupts requires the interrupt controller to be configured first. Refer to *Nested Vector Interrupt Controller* for details.

# **Related Links**

Nested Vector Interrupt Controller

#### 24.5.6 Events

Not applicable.

# 24.5.7 Debug Operation

When the CPU is halted in debug mode, this peripheral will continue normal operation. If the peripheral is configured to require periodical service by the CPU through interrupts or similar, improper operation or data loss may result during debugging. This peripheral can be forced to halt operation during debugging.

# Bits 19,18,17,16,7,6,5,4,3,2,1,0 - OVRn : Channel n Overrun [n=11..0]

This flag is set on the next CLK\_EVSYS cycle after an overrun channel condition occurs, and an interrupt request will be generated if INTENCLR/SET.OVRn is one.

When the event channel path is asynchronous, the OVRn interrupt flag will not be set.

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Overrun Channel n interrupt flag.

# 26.7 Register Summary

| Offset | Name      | Bit Pos. |          |            |       |        |           |        |             |           |

|--------|-----------|----------|----------|------------|-------|--------|-----------|--------|-------------|-----------|

| 0x00   |           | 7:0      | RUNSTDBY |            |       |        | MODE[2:0] |        | ENABLE      | SWRST     |

| 0x01   | CTRLA     | 15:8     |          | SAMPR[2:0] |       |        |           |        |             | IBON      |

| 0x02   | UIRLA     | 23:16    | SAMP     | PA[1:0]    | RXPO  | D[1:0] |           |        | TXP         | D[1:0]    |

| 0x03   |           | 31:24    |          | DORD       | CPOL  | CMODE  |           | FOR    | V[3:0]      |           |

| 0x04   |           | 7:0      |          | SBMODE     |       |        |           |        | CHSIZE[2:0] |           |

| 0x05   |           | 15:8     |          |            | PMODE |        |           | ENC    | SFDE        | COLDEN    |

| 0x06   | CTRLB     | 23:16    |          |            |       |        |           |        | RXEN        | TXEN      |

| 0x07   |           | 31:24    |          |            |       |        |           |        |             |           |

| 0x08   |           |          |          |            |       |        |           |        |             |           |

|        | Reserved  |          |          |            |       |        |           |        |             |           |

| 0x0B   |           |          |          |            |       |        |           |        |             |           |

| 0x0C   | BAUD      | 7:0      |          |            |       | BAU    | D[7:0]    |        |             |           |

| 0x0D   | BAOD      | 15:8     |          |            |       | BAU    | D[15:8]   |        |             |           |

| 0x0E   | RXPL      | 7:0      |          |            |       | RXP    | L[7:0]    |        |             |           |

| 0x0F   |           |          |          |            |       |        |           |        |             |           |

|        | Reserved  |          |          |            |       |        |           |        |             |           |

| 0x13   |           |          |          |            |       |        |           |        |             |           |

| 0x14   | INTENCLR  | 7:0      | ERROR    |            | RXBRK | CTSIC  | RXS       | RXC    | TXC         | DRE       |

| 0x15   | Reserved  |          |          |            |       |        |           |        |             |           |

| 0x16   | INTENSET  | 7:0      | ERROR    |            | RXBRK | CTSIC  | RXS       | RXC    | TXC         | DRE       |

| 0x17   | Reserved  |          |          |            |       |        |           |        |             |           |

| 0x18   | INTFLAG   | 7:0      | ERROR    |            | RXBRK | CTSIC  | RXS       | RXC    | TXC         | DRE       |

| 0x19   | Reserved  |          |          |            |       |        |           |        |             |           |

| 0x1A   | STATUS    | 7:0      |          |            | COLL  | ISF    | CTS       | BUFOVF | FERR        | PERR      |

| 0x1B   | 014100    | 15:8     |          |            |       |        |           |        |             |           |

| 0x1C   |           | 7:0      |          |            |       |        |           | CTRLB  | ENABLE      | SWRST     |

| 0x1D   | SYNCBUSY  | 15:8     |          |            |       |        |           |        |             |           |

| 0x1E   | 311000031 | 23:16    |          |            |       |        |           |        |             |           |

| 0x1F   |           | 31:24    |          |            |       |        |           |        |             |           |

| 0x20   |           |          |          |            |       |        |           |        |             |           |

|        | Reserved  |          |          |            |       |        |           |        |             |           |

| 0x27   |           |          |          |            |       |        |           |        |             |           |

| 0x28   | DATA      | 7:0      |          |            |       | DAT    | A[7:0]    |        |             |           |

| 0x29   | Di ti t   | 15:8     |          |            |       |        |           |        |             | DATA[8:8] |

| 0x2A   |           |          |          |            |       |        |           |        |             |           |

|        | Reserved  |          |          |            |       |        |           |        |             |           |

| 0x2F   |           |          |          |            |       |        |           |        |             |           |

| 0x30   | DBGCTRL   | 7:0      |          |            |       |        |           |        |             | DBGSTOP   |

# 26.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

# 28.7 Register Summary - I2C Slave

| Offset | Name       | Bit Pos. |          |         |       |             |           |        |              |        |

|--------|------------|----------|----------|---------|-------|-------------|-----------|--------|--------------|--------|

| 0x00   |            | 7:0      | RUNSTDBY |         |       |             | MODE[2:0] |        | ENABLE       | SWRST  |

| 0x01   |            | 15:8     |          |         |       |             |           |        |              |        |

| 0x02   | CTRLA      | 23:16    | SEXTTOEN |         | SDAHC | DLD[1:0]    |           |        |              | PINOUT |

| 0x03   |            | 31:24    |          | LOWTOUT |       |             | SCLSM     |        | SPEE         | D[1:0] |

| 0x04   |            | 7:0      |          |         |       |             |           |        |              |        |

| 0x05   |            | 15:8     | AMOE     | DE[1:0] |       |             |           | AACKEN | GCMD         | SMEN   |

| 0x06   | CTRLB      | 23:16    |          |         |       |             |           | ACKACT | CME          | [1:0]  |

| 0x07   |            | 31:24    |          |         |       |             |           |        |              |        |

| 0x08   |            |          |          |         |       |             |           |        |              |        |

|        | Reserved   |          |          |         |       |             |           |        |              |        |

| 0x13   |            |          |          |         |       |             |           |        |              |        |

| 0x14   | INTENCLR   | 7:0      | ERROR    |         |       |             |           | DRDY   | AMATCH       | PREC   |

| 0x15   | Reserved   |          |          |         |       |             |           |        |              |        |

| 0x16   | INTENSET   | 7:0      | ERROR    |         |       |             |           | DRDY   | AMATCH       | PREC   |

| 0x17   | Reserved   |          |          |         |       |             |           |        |              |        |

| 0x18   | INTFLAG    | 7:0      | ERROR    |         |       |             |           | DRDY   | AMATCH       | PREC   |

| 0x19   | Reserved   |          |          |         |       |             |           |        |              |        |

| 0x1A   | STATUS     | 7:0      | CLKHOLD  | LOWTOUT |       | SR          | DIR       | RXNACK | COLL         | BUSERR |

| 0x1B   | STATUS     | 15:8     |          |         |       |             |           | LENERR | SEXTTOUT     |        |

| 0x1C   |            | 7:0      |          |         |       |             |           |        | ENABLE       | SWRST  |

| 0x1D   | CVN CDU CV | 15:8     |          |         |       |             |           |        |              |        |

| 0x1E   | SYNCBUSY   | 23:16    |          |         |       |             |           |        |              |        |

| 0x1F   |            | 31:24    |          |         |       |             |           |        |              |        |

| 0x20   |            |          |          |         |       |             |           |        |              |        |

|        | Reserved   |          |          |         |       |             |           |        |              |        |

| 0x23   |            |          |          |         |       |             |           |        |              |        |

| 0x24   |            | 7:0      |          |         |       | ADDR[6:0]   |           |        |              | GENCEN |

| 0x25   | ADDR       | 15:8     | TENBITEN |         |       |             |           |        | ADDR[9:7]    |        |

| 0x26   |            | 23:16    |          |         | ŀ     | ADDRMASK[6: | 0]        |        |              |        |

| 0x27   |            | 31:24    |          |         |       |             |           |        | ADDRMASK[9:7 | 7]     |

| 0x28   | DATA       | 7:0      |          |         |       | DAT         | A[7:0]    |        |              |        |

| 0x29   | DATA       | 15:8     |          |         |       |             |           |        |              |        |

# 28.8 Register Description - I<sup>2</sup>C Slave

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to Register Access Protection.

Some registers are synchronized when read and/or written. Synchronization is denoted by the "Write-Synchronized" or the "Read-Synchronized" property in each individual register description. For details, refer to Synchronization.

| Value | Description                                                                        |

|-------|------------------------------------------------------------------------------------|

| 0     | The CCBx, PERB, PGVB, PGOB, and SWAPBx buffer registers values are copied into the |

|       | corresponding CCx, PER, PGV, PGO and SWAPx registers on hardware update condition. |

| 1     | The CCBx, PERB, PGVB, PGOB, and SWAPBx buffer registers values are not copied into |

|       | the corresponding CCx, PER, PGV, PGO and SWAPx registers on hardware update        |

|       | condition.                                                                         |

### Bit 0 – DIR: Counter Direction

This bit is used to change the direction of the counter.

Writing a '0' to this bit has no effect

Writing a '1' to this bit will clear the bit and make the counter count up.

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | The timer/counter is counting up (incrementing).   |

| 1     | The timer/counter is counting down (decrementing). |

# 31.8.3 Control B Set

This register allows the user to change this register without doing a read-modify-write operation. Changes in this register will also be reflected in the Control B Set (CTRLBCLR) register.

Name:CTRLBSETOffset:0x05Reset:0x00Property:PAC Write-Protection, Write-Synchronized, Read-Synchronized

| Bit    | 7   | 6        | 5   | 4     | 3       | 2       | 1    | 0   |

|--------|-----|----------|-----|-------|---------|---------|------|-----|

|        |     | CMD[2:0] |     | IDXCM | 1D[1:0] | ONESHOT | LUPD | DIR |

| Access | R/W | R/W      | R/W | R/W   | R/W     | R/W     | R/W  | R/W |

| Reset  | 0   | 0        | 0   | 0     | 0       | 0       | 0    | 0   |

# Bits 7:5 – CMD[2:0]: TCC Command

These bits can be used for software control of re-triggering and stop commands of the TCC. When a command has been executed, the CMD bit field will be read back as zero. The commands are executed on the next prescaled GCLK\_TCC clock cycle.

Writing zero to this bit group has no effect

Writing a valid value to this bit group will set the associated command.

| Value | Name      | Description                               |

|-------|-----------|-------------------------------------------|

| 0x0   | NONE      | No action                                 |

| 0x1   | RETRIGGER | Force start, restart or retrigger         |

| 0x2   | STOP      | Force stop                                |

| 0x3   | UPDATE    | Force update of double buffered registers |

| 0x4   | READSYNC  | Force a read synchronization of COUNT     |

#### Bits 4:3 – IDXCMD[1:0]: Ramp Index Command

These bits can be used to force cycle A and cycle B changes in RAMP2 and RAMP2A operation. On timer/counter update condition, the command is executed, the IDX flag in STATUS register is updated and the IDXCMD command is cleared.

#### 32.6.3 Host Operations

This section gives an overview of the USB module Host operation during normal transactions. For more details on general USB and USB protocol, refer to Universal Serial Bus Specification revision 2.1.

#### 32.6.3.1 Device Detection and Disconnection

Prior to device detection the software must set the VBUS is OK bit in CTRLB (CTRLB.VBUSOK) register when the VBUS is available. This notifies the USB host that USB operations can be started. When the bit CTRLB.VBUSOK is zero and even if the USB HOST is configured and enabled, host operation is halted. Setting the bit CTRLB.VBUSOK will allow host operation when the USB is configured.

The Device detection is managed by the software using the Line State field in the Host Status (STATUS.LINESTATE) register. The device connection is detected by the host controller when DP or DM is pulled high, depending of the speed of the device.

The device disconnection is detected by the host controller when both DP and DM are pulled down using the STATUS.LINESTATE registers.

The Device Connection Interrupt bit in INTFLAG (INTFLAG.DCONN) is set if a device connection is detected.

The Device Disconnection Interrupt bit in INTFLAG (INTFLAG.DDISC) is set if a device disconnection is detected.

#### 32.6.3.2 Host Terminology

In host mode, the term pipe is used instead of endpoint. A host pipe corresponds to a device endpoint, refer to "Universal Serial Bus Specification revision 2.1." for more information.

#### 32.6.3.3 USB Reset

The USB sends a USB reset signal when the user writes a one to the USB Reset bit in CTRLB (CTRLB.BUSRESET). When the USB reset has been sent, the USB Reset Sent Interrupt bit in the INTFLAG (INTFLAG.RST) is set and all pipes will be disabled.

If the bus was previously in a suspended state (Start of Frame Generation Enable bit in CTRLB (CTRLB.SOFE) is zero) the USB will switch it to the Resume state, causing the bus to asynchronously set the Host Wakeup Interrupt flag (INTFLAG.WAKEUP). The CTRLB.SOFE bit will be set in order to generate SOFs immediately after the USB reset.

During USB reset the following registers are cleared:

- All Host Pipe Configuration register (PCFG)

- Host Frame Number register (FNUM)

- Interval for the Bulk-Out/Ping transaction register (BINTERVAL)

- Host Start-of-Frame Control register (HSOFC)

- Pipe Interrupt Enable Clear/Set register (PINTENCLR/SET)

- Pipe Interrupt Flag register (PINTFLAG)

- Pipe Freeze bit in Pipe Status register (PSTATUS.FREEZE)

After the reset the user should check the Speed Status field in the Status register (STATUS.SPEED) to find out the current speed according to the capability of the peripheral.

#### 32.6.3.4 Pipe Configuration

Pipe data can be placed anywhere in the RAM. The USB controller accesses these pipes directly through the AHB master (built-in DMA) with the help of the pipe descriptors. The base address of the pipe descriptors needs to be written in the Descriptor Address register (DESCADD) by the user. Refer also to Pipe Descriptor Structure.

# Bit 6 – UPRSM: Upstream Resume from Device Interrupt Disable

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Upstream Resume interrupt Enable bit and disable the corresponding interrupt request.

| Value | Description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| 0     | The Upstream Resume interrupt is disabled.                                               |

| 1     | The Upstream Resume interrupt is enabled and an interrupt request will be generated when |

|       | the Upstream Resume interrupt Flag is set.                                               |

# Bit 5 – DNRSM: Down Resume Interrupt Disable

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Down Resume interrupt Enable bit and disable the corresponding interrupt request.

| Value | Description                                                                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------|

| 0     | The Down Resume interrupt is disabled.                                                                                      |

| 1     | The Down Resume interrupt is enabled and an interrupt request will be generated when the Down Resume interrupt Flag is set. |

|       | Down Acounte interrupt hug to bet.                                                                                          |

# Bit 4 – WAKEUP: Wake Up Interrupt Disable

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Wake Up interrupt Enable bit and disable the corresponding interrupt request.

| Value | Description                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------|

| 0     | The Wake Up interrupt is disabled.                                                                                  |

| 1     | The Wake Up interrupt is enabled and an interrupt request will be generated when the Wake Up interrupt Flag is set. |

# Bit 3 – RST: BUS Reset Interrupt Disable

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Bus Reset interrupt Enable bit and disable the corresponding interrupt request.

| Value | Description                                                                                |

|-------|--------------------------------------------------------------------------------------------|

| 0     | The Bus Reset interrupt is disabled.                                                       |

| 1     | The Bus Reset interrupt is enabled and an interrupt request will be generated when the Bus |

|       | Reset interrupt Flag is set.                                                               |

# Bit 2 – HSOF: Host Start-of-Frame Interrupt Disable

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Host Start-of-Frame interrupt Enable bit and disable the corresponding interrupt request.

| Value | Description                                                                                                                                 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The Host Start-of-Frame interrupt is disabled.                                                                                              |

| 1     | The Host Start-of-Frame interrupt is enabled and an interrupt request will be generated when the Host Start-of-Frame interrupt Flag is set. |

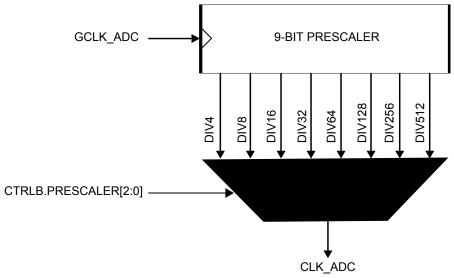

# Figure 33-2. ADC Prescaler

The propagation delay of an ADC measurement depends on the selected mode and is given by:

• Single-shot mode:

PropagationDelay =  $\frac{1 + \frac{\text{Resolution}}{2} + \text{DelayGain}}{f_{\text{CLK+} - \text{ADC}}}$

Free-running mode: PropagationDelay =  $\frac{\frac{\text{Resolution}}{2} + \text{DelayGain}}{f_{\text{CLK+} - \text{ADC}}}$

# Table 33-1. Delay Gain

|          |                      | Delay Gain (in CLK_ADC Period) |                      |                      |                      |  |

|----------|----------------------|--------------------------------|----------------------|----------------------|----------------------|--|

|          | INTPUTCTRL.GAIN[3:0] | Free-running mode              |                      | Single shot mode     |                      |  |

| Name     |                      | Differential<br>Mode           | Single-Ended<br>Mode | Differential<br>mode | Single-Ended<br>mode |  |

| 1X       | 0x0                  | 0                              | 0                    | 0                    | 1                    |  |

| 2X       | 0x1                  | 0                              | 1                    | 0.5                  | 1.5                  |  |

| 4X       | 0x2                  | 1                              | 1                    | 1                    | 2                    |  |

| 8X       | 0x3                  | 1                              | 2                    | 1.5                  | 2.5                  |  |

| 16X      | 0x4                  | 2                              | 2                    | 2                    | 3                    |  |

| Reserved | 0x5 0xE              | Reserved                       | Reserved             | Reserved             | Reserved             |  |

| DIV2     | 0xF                  | 0                              | 1                    | 0.5                  | 1.5                  |  |

# 33.6.4 ADC Resolution

The ADC supports 8-bit, 10-bit or 12-bit resolution. Resolution can be changed by writing the Resolution bit group in the Control B register (CTRLB.RESSEL). By default, the ADC resolution is set to 12 bits.

# 33.6.5 Differential and Single-Ended Conversions

The ADC has two conversion options: differential and single-ended:

| Value | Description                                                   |

|-------|---------------------------------------------------------------|

| 0     | The ADC is halted during standby sleep mode.                  |

| 1     | The ADC continues normal operation during standby sleep mode. |

#### Bit 1 – ENABLE: Enable

Due to synchronization, there is a delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRL.ENABLE will read back immediately and the Synchronization Busy bit in the Status register (STATUS.SYNCBUSY) will be set. STATUS.SYNCBUSY will be cleared when the operation is complete.

| Value | Description          |

|-------|----------------------|

| 0     | The ADC is disabled. |

| 1     | The ADC is enabled.  |

# Bit 0 – SWRST: Software Reset

Writing a zero to this bit has no effect.

Writing a one to this bit resets all registers in the ADC, except DBGCTRL, to their initial state, and the ADC will be disabled.

Writing a one to CTRL.SWRST will always take precedence, meaning that all other writes in the same write-operation will be discarded.

Due to synchronization, there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and STATUS.SYNCBUSY will both be cleared when the reset is complete.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

#### 33.8.2 Reference Control

Name: REFCTRL Offset: 0x01 Reset: 0x00 Property: Write-Protected

| Bit    | 7       | 6 | 5 | 4 | 3   | 2     | 1       | 0   |

|--------|---------|---|---|---|-----|-------|---------|-----|

| ſ      | REFCOMP |   |   |   |     | REFSE | EL[3:0] |     |

| Access | R/W     |   |   |   | R/W | R/W   | R/W     | R/W |

| Reset  | 0       |   |   |   | 0   | 0     | 0       | 0   |

#### Bit 7 – REFCOMP: Reference Buffer Offset Compensation Enable

The accuracy of the gain stage can be increased by enabling the reference buffer offset compensation. This will decrease the input impedance and thus increase the start-up time of the reference.

| Value | Description                                       |

|-------|---------------------------------------------------|

| 0     | Reference buffer offset compensation is disabled. |

| 1     | Reference buffer offset compensation is enabled.  |

#### Bits 3:0 – REFSEL[3:0]: Reference Selection

These bits select the reference for the ADC.

# 32-bit ARM-Based Microcontrollers

| MUXPOS[4:0] | Group configuration | Description            |

|-------------|---------------------|------------------------|

| 0x03        | PIN3                | ADC AIN3 pin           |

| 0x04        | PIN4                | ADC AIN4 pin           |

| 0x05        | PIN5                | ADC AIN5 pin           |

| 0x06        | PIN6                | ADC AIN6 pin           |

| 0x07        | PIN7                | ADC AIN7 pin           |

| 0x08        | PIN8                | ADC AIN8 pin           |

| 0x09        | PIN9                | ADC AIN9 pin           |

| 0x0A        | PIN10               | ADC AIN10 pin          |

| 0x0B        | PIN11               | ADC AIN11 pin          |

| 0x0C        | PIN12               | ADC AIN12 pin          |

| 0x0D        | PIN13               | ADC AIN13 pin          |

| 0x0E        | PIN14               | ADC AIN14 pin          |

| 0x0F        | PIN15               | ADC AIN15 pin          |

| 0x10        | PIN16               | ADC AIN16 pin          |

| 0x11        | PIN17               | ADC AIN17 pin          |

| 0x12        | PIN18               | ADC AIN18 pin          |

| 0x13        | PIN19               | ADC AIN19 pin          |

| 0x14-0x17   |                     | Reserved               |

| 0x18        | TEMP                | Temperature reference  |

| 0x19        | BANDGAP             | Bandgap voltage        |

| 0x1A        | SCALEDCOREVCC       | 1/4 scaled core supply |

| 0x1B        | SCALEDIOVCC         | 1/4 scaled I/O supply  |

| 0x1C        | DAC                 | DAC output             |

| 0x1D-0x1F   |                     | Reserved               |

# 33.8.9 Event Control

Name:EVCTRLOffset:0x14Reset:0x00Property:Write-Protected

|               | <ul> <li>4 – In TWI master mode, an ongoing transaction should be stalled immediately when DBGCTRL.DBGSTOP is set and the CPU enters debug mode. Instead, it is stopped when the current byte transaction is completed and the corresponding interrupt is triggered if enabled.</li> <li>Errata reference: 12499</li> <li>Fix/Workaround:</li> <li>In TWI master mode, keep DBGCTRL.DBGSTOP=0 when in debug mode.</li> </ul>                                                                                       |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40.1.4.12 TC  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|               | <ul> <li>1 – Spurious TC overflow and Match/Capture events may occur.</li> <li>Errata reference: 13268</li> <li>Fix/Workaround:</li> <li>Do not use the TC overflow and Match/Capture events. Use the corresponding Interrupts instead.</li> </ul>                                                                                                                                                                                                                                                                 |

| 40.1.4.13 TCC |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|               | <ul> <li>1 – Using TCC in dithering mode with external retrigger events can lead to unexpected stretch of right aligned pulses, or shrink of left aligned pulses.</li> <li>Errata reference: 15625</li> <li>Fix/Workaround:</li> <li>Do not use retrigger events/actions when TCC is configured in dithering mode.</li> </ul>                                                                                                                                                                                      |

|               | 2 – Advance capture mode (CAPTMIN CAPTMAX LOCMIN LOCMAX<br>DERIV0) doesn't work if an upper channel is not in one of these mode.<br>Example: when CC[0]=CAPTMIN, CC[1]=CAPTMAX, CC[2]=CAPTEN,<br>and CC[3]=CAPTEN, CAPTMIN and CAPTMAX won't work.<br>Errata reference: 14817<br>Fix/Workaround:<br>Basic capture mode must be set in lower channel and advance capture<br>mode in upper channel.<br>Example: CC[0]=CAPTEN, CC[1]=CAPTEN, CC[2]=CAPTMIN,<br>CC[3]=CAPTMAX<br>All capture will be done as expected. |

|               | <ul> <li>3 – In RAMP 2 mode with Fault keep, qualified and restart:</li> <li>If a fault occurred at the end of the period during the qualified state, the switch to the next ramp can have two restarts.</li> <li>Errata reference: 13262</li> <li>Fix/Workaround:</li> <li>Avoid faults few cycles before the end or the beginning of a ramp.</li> </ul>                                                                                                                                                          |

|               | 4 – With blanking enabled, a recoverable fault that occurs during the<br>first increment of a rising TCC is not blanked.<br>Errata reference: 12519<br>Fix/Workaround:<br>None                                                                                                                                                                                                                                                                                                                                     |

|               | 5 – In Dual slope mode a Retrigger Event does not clear the TCC<br>counter.<br>Errata reference: 12354<br>Fix/Workaround:<br>None                                                                                                                                                                                                                                                                                                                                                                                  |