#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                               |

| Data Converters            | A/D 20x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-QFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd21j17a-mut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.2 SAM D21G

Table 3-4. Device Variant A

| Ordering Code    | FLASH (bytes) | SRAM (bytes) | Package | Carrier Type |

|------------------|---------------|--------------|---------|--------------|

| ATSAMD21G15A-AU  | 32K           | 4K           | TQFP48  | Tray         |

| ATSAMD21G15A-AUT |               |              |         | Tape & Reel  |

| ATSAMD21G15A-AF  |               |              |         | Tray         |

| ATSAMD21G15A-AFT |               |              |         | Tape & Reel  |

| ATSAMD21G15A-MU  |               |              | QFN48   | Tray         |

| ATSAMD21G15A-MUT |               |              |         | Tape & Reel  |

| ATSAMD21G15A-MF  |               |              |         | Tray         |

| ATSAMD21G15A-MFT |               |              |         | Tape & Reel  |

| ATSAMD21G16A-AU  | 64K           | 8K           | TQFP48  | Tray         |

| ATSAMD21G16A-AUT |               |              |         | Tape & Reel  |

| ATSAMD21G16A-AF  |               |              |         | Tray         |

| ATSAMD21G16A-AFT |               |              |         | Tape & Reel  |

| ATSAMD21G16A-MU  |               |              | QFN48   | Tray         |

| ATSAMD21G16A-MUT |               |              |         | Tape & Reel  |

| ATSAMD21G16A-MF  |               |              |         | Tray         |

| ATSAMD21G16A-MFT |               |              |         | Tape & Reel  |

| ATSAMD21G17A-AU  | 128K          | 16K          | TQFP48  | Tray         |

| ATSAMD21G17A-AUT |               |              |         | Tape & Reel  |

| ATSAMD21G17A-AF  |               |              |         | Tray         |

| ATSAMD21G17A-AFT |               |              |         | Tape & Reel  |

| ATSAMD21G17A-MU  |               |              | QFN48   | Tray         |

| ATSAMD21G17A-MUT |               |              |         | Tape & Reel  |

| ATSAMD21G17A-MF  |               |              |         | Tray         |

| ATSAMD21G17A-MFT |               |              |         | Tape & Reel  |

| ATSAMD21G17A-UUT |               |              | WLCSP45 | Tape & Reel  |

| Device Variant     | DID.DEVSEL  | Device ID (DID)             |

|--------------------|-------------|-----------------------------|

| Reserved           | 0x25        |                             |

| SAMD21E16B         | 0x26        | 0x10011426 (die revision E) |

|                    |             | 0x10011526 (die revision F) |

| SAMD21E15B         | 0x27        | 0x10011427 (die revision E) |

|                    |             | 0x10011527 (die revision F) |

| Reserved           | 0x28-0x54   |                             |

| SAMD21E16B (WLCSP) | 0x55        | 0x10011455 (die revision E) |

| SAMD21E15B (WLCSP) | 0x56        | 0x10011456 (die revision E) |

| Reserved           | 0x57 - 0x61 |                             |

| SAMD21E16C (WLCSP) | 0x62        | 0x10011562 (die revision F) |

| SAMD21E15C (WLCSP) | 0x63        | 0x10011563 (die revision F) |

| Reserved           | 0x64-0xFF   |                             |

**Note:** The device variant (last letter of the ordering number) is independent of the die revision (DSU.DID.REVISION): The device variant denotes functional differences, whereas the die revision marks evolution of the die. The device variant denotes functional differences, whereas the die revision marks evolution of the die.

## **Related Links**

DID

| PACKAGE | CLUSTER |      |      |      |      |      |      |      |      | SUPPLIES<br>PINS<br>CONNECTED<br>TO THE<br>CLUSTER |      |      |      |      |      |      |      |                                                                 |

|---------|---------|------|------|------|------|------|------|------|------|----------------------------------------------------|------|------|------|------|------|------|------|-----------------------------------------------------------------|

| 32pins  | 1       | PA31 | PA30 |      |      |      |      |      |      |                                                    |      |      |      |      |      |      |      | VDDIN<br>pin30/GND pin<br>28                                    |

|         | 2       | PA28 | PA27 | PA25 | PA24 | PA23 | PA22 | PA19 | PA18 | PA17                                               | PA16 | PA15 | PA14 | PA11 | PA10 | PA09 | PA08 | VDDIN<br>pin30/GND pin<br>28 and<br>VDDANA<br>pin9/GND<br>pin10 |

|         | 3       | PA07 | PA06 | PA05 | PA04 | PA03 | PA02 | PA01 | PA00 |                                                    |      |      |      |      |      |      |      | VDDANA<br>pin9/GND<br>pin10                                     |

## 7.2.5 TCC Configurations

The SAM D21 has three instances of the Timer/Counter for Control applications (TCC) peripheral, , TCC[2:0]. The following table lists the features for each TCC instance.

## Table 7-6. TCC Configuration Summary

| TCC# | Channels<br>(CC_NUM) | Waveform<br>Output<br>(WO_NUM) | Counter<br>size | Fault | Dithering | Output<br>matrix | Dead Time<br>Insertion<br>(DTI) | SWAP | Pattern<br>generation |

|------|----------------------|--------------------------------|-----------------|-------|-----------|------------------|---------------------------------|------|-----------------------|

| 0    | 4                    | 8                              | 24-bit          | Yes   | Yes       | Yes              | Yes                             | Yes  | Yes                   |

| 1    | 2                    | 4                              | 24-bit          | Yes   | Yes       |                  |                                 |      | Yes                   |

| 2    | 2                    | 2                              | 16-bit          | Yes   |           |                  |                                 |      |                       |

**Note:** The number of CC registers (CC\_NUM) for each TCC corresponds to the number of compare/ capture channels, so that a TCC can have more Waveform Outputs (WO\_NUM) than CC registers.

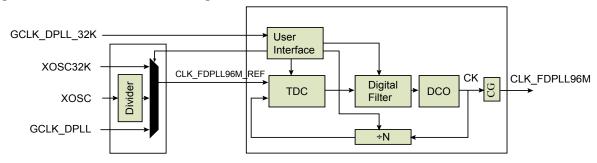

## 17.6.8 FDPLL96M – Fractional Digital Phase-Locked Loop Controller (DFLL96M)

## 17.6.8.1 Overview

The FDPLL96M controller allows flexible interface to the core digital function of the Digital Phase Locked Loop (DPLL). The FDPLL96M integrates a digital filter with a proportional integral controller, a Time-to-Digital Converter (TDC), a test mode controller, a Digitally Controlled Oscillator (DCO) and a PLL controller. It also provides a fractional multiplier of frequency N between the input and output frequency.

The CLK\_FDPLL96M\_REF is the DPLL input clock reference. The selectable sources for the reference clock are XOSC32K, XOSC and GCLK\_DPLL. The path between XOSC and input multiplexer integrates a clock divider. The selected clock must be configured and enabled before using the FDPLL96M. If the GCLK is selected as reference clock, it must be configured and enabled in the Generic Clock Controller before using the FDPLL96M. Refer to *GCLK* – *Generic Clock Controller* for details. If the GCLK\_DPLL is selected as the source for the CLK\_FDPLL96M\_REF, care must be taken to make sure the source for this GCLK is within the valid frequency range for the FDPLL96M.

The XOSC source can be divided inside the FDPLL96M. The user must make sure that the programmable clock divider and XOSC frequency provides a valid CLK\_FDPLL96M\_REF clock frequency that meets the FDPLL96M input frequency range.

The output clock of the FDPLL96M is CLK\_FDPLL96M. The state of the CLK\_FDPLL96M clock only depends on the FDPLL96M internal control of the final clock gater CG.

The FDPLL96M requires a 32kHz clock from the GCLK when the FDPLL96M internal lock timer is used. This clock must be configured and enabled in the Generic Clock Controller before using the FDPLL96M. Refer to *GCLK* – *Generic Clock Controller* for details.

### Table 17-3. Generic Clock Input for FDPLL96M

| Generic Clock        | FDPLL96M                              |

|----------------------|---------------------------------------|

| FDPLL96M 32kHz clock | GCLK_DPLL_32K for internal lock timer |

| FDPLL96M             | GCLK_DPLL for CLK_FDPLL96M_REF        |

### **Related Links**

**GCLK - Generic Clock Controller**

## 17.6.8.2 Block Diagram

### Figure 17-2. FDPLL96M Block Diagram

## 17.6.8.3 Principle of Operation

The task of the FDPLL96M is to maintain coherence between the input reference clock signal (CLK\_FDPLL96M\_REF) and the respective output frequency CK via phase comparison. The FDPLL96M supports three independent sources of clocks XOSC32K, XOSC and GCLK\_DPLL. When the FDPLL96M is enabled, the relationship between the reference clock (CLK\_FDPLL96M\_REF) frequency and the output clock (CLK\_FDPLL96M) frequency is defined below.

## Bit 1 – XOSC32KRDY: XOSC32K Ready

This flag is cleared by writing a one to it.

This flag is set on a zero-to-one transition of the XOSC32K Ready bit in the Status register (PCLKSR.XOSC32KRDY) and will generate an interrupt request if INTENSET.XOSC32KRDY is one.

Writing a zero to this bit has no effect.

Writing a one to this bit clears the XOSC32K Ready interrupt flag.

## Bit 0 – XOSCRDY: XOSC Ready

This flag is cleared by writing a one to it.

This flag is set on a zero-to-one transition of the XOSC Ready bit in the Status register (PCLKSR.XOSCRDY) and will generate an interrupt request if INTENSET.XOSCRDY is one.

Writing a zero to this bit has no effect.

Writing a one to this bit clears the XOSC Ready interrupt flag.

## 17.8.4 Power and Clocks Status

Name:

PCLKSR

Offset:

0x0C

Reset:

0x0000000

Property:

| Bit    | 31       | 30       | 29      | 28      | 27       | 26        | 25         | 24       |

|--------|----------|----------|---------|---------|----------|-----------|------------|----------|

|        |          |          |         |         |          |           |            |          |

| Access | R        | R        | R       | R       | R        | R         | R          | R        |

| Reset  | 0        | 0        | 0       | 0       | 0        | 0         | 0          | 0        |

|        |          |          |         |         |          |           |            |          |

| Bit    | 23       | 22       | 21      | 20      | 19       | 18        | 17         | 16       |

|        |          |          |         |         |          |           | DPLLLTO    | DPLLLCKF |

| Access | R        | R        | R       | R       | R        | R         | R          | R        |

| Reset  | 0        | 0        | 0       | 0       | 0        | 0         | 0          | 0        |

|        |          |          |         |         |          |           |            |          |

| Bit    | 15       | 14       | 13      | 12      | 11       | 10        | 9          | 8        |

|        | DPLLLCKR |          |         |         | B33SRDY  | BOD33DET  | BOD33RDY   | DFLLRCS  |

| Access | R        | R        | R       | R       | R        | R         | R          | R        |

| Reset  | 0        | 0        | 0       | 0       | 0        | 0         | 0          | 0        |

|        |          |          |         |         |          |           |            |          |

| Bit    | 7        | 6        | 5       | 4       | 3        | 2         | 1          | 0        |

|        | DFLLLCKC | DFLLLCKF | DFLLOOB | DFLLRDY | OSC8MRDY | OSC32KRDY | XOSC32KRDY | XOSCRDY  |

| Access | R        | R        | R       | R       | R        | R         | R          | R        |

| Reset  | 0        | 0        | 0       | 0       | 0        | 0         | 0          | 0        |

## Bit 17 – DPLLLTO: DPLL Lock Timeout

| Value | Description                      |

|-------|----------------------------------|

| 0     | DPLL Lock time-out not detected. |

| 1     | DPLL Lock time-out detected.     |

## 19.6.5 Interrupts

The RTC has the following interrupt sources which are asynchronous interrupts and can wake-up the device from any sleep mode.:

- Overflow (INTFLAG.OVF): Indicates that the counter has reached its top value and wrapped to zero.

- Compare n (INTFLAG.CMPn): Indicates a match between the counter value and the compare register.

- Alarm n (INTFLAG.ALARMn): Indicates a match between the clock value and the alarm register.

- Synchronization Ready (INTFLAG.SYNCRDY): Indicates an operation requires synchronization.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear (INTFLAG) register is set when the interrupt condition occurs. Each interrupt can be individually enabled by setting the corresponding bit in the Interrupt Enable Set register (INTENSET=1), and disabled by setting the corresponding bit in the Interrupt Enable Clear register (INTENCLR=1). An interrupt request is generated when the interrupt flag is raised and the corresponding interrupt is enabled. The interrupt request remains active until either the interrupt flag is cleared, the interrupt is disabled or the RTC is reset. See the description of the INTFLAG registers for details on how to clear interrupt flags. All interrupt requests from the peripheral are ORed together on system level to generate one combined interrupt request to the NVIC. Refer to the Nested Vector Interrupt Controller for details. The user must read the INTFLAG register to determine which interrupt condition is present.

**Note:** Interrupts must be globally enabled for interrupt requests to be generated. Refer to the Nested Vector Interrupt Controller for details.

### **Related Links**

Nested Vector Interrupt Controller

## 19.6.6 Events

The RTC can generate the following output events, which are generated in the same way as the corresponding interrupts:

- Overflow (OVF): Indicates that the counter has reached its top value and wrapped to zero.

- Period n (PERn): The corresponding bit in the prescaler has toggled. Refer to Periodic Events for details.

- Compare n (CMPn): Indicates a match between the counter value and the compare register.

- Alarm n (ALARMn): Indicates a match between the clock value and the alarm register.

Setting the Event Output bit in the Event Control Register (EVCTRL.xxxEO=1) enables the corresponding output event. Writing a zero to this bit disables the corresponding output event. Refer to the *EVSYS* - *Event System* for details on configuring the event system.

## **Related Links**

EVSYS – Event System

### 19.6.7 Sleep Mode Operation

The RTC will continue to operate in any sleep mode where the source clock is active. The RTC *interrupts* can be used to wake up the device from a sleep mode. RTC *events* can trigger other operations in the system without exiting the sleep mode.

An interrupt request will be generated after the wake-up if the Interrupt Controller is configured accordingly. Otherwise the CPU will wake up directly, without triggering any interrupt. In this case, the CPU will continue executing right from the first instruction that followed the entry into sleep.

© 2017 Microchip Technology Inc.

| Bit    | 7   | 6   | 5   | 4      | 3        | 2   | 1   | 0   |

|--------|-----|-----|-----|--------|----------|-----|-----|-----|

|        |     |     |     | CRCCHK | SUM[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W    | R/W      | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0      | 0        | 0   | 0   | 0   |

## Bits 31:0 – CRCCHKSUM[31:0]: CRC Checksum

These bits store the generated CRC result. When CRC-16 is enabled, the 16 msb will always read '0'.

These bits should only be read when CRC Module Busy bit in the CRC Status register CRCSTATUS.BUSY=0.

If CRC-16 is selected and CRCSTATUS.BUSY=0 (CRC generation is completed), this bit group will contain a valid checksum.

If CRC-32 is selected and CRCSTATUS.BUSY=0 (CRC generation is completed), this bit group will contain a valid *reversed* checksum, i.e.: bit 31 is swapped with bit 0, bit 30 with bit 1, etc.

## 20.8.5 CRC Status

Name:CRCSTATUSOffset:0x0CReset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1       | 0       |

|--------|---|---|---|---|---|---|---------|---------|

|        |   |   |   |   |   |   | CRCZERO | CRCBUSY |

| Access |   |   |   |   |   |   | R       | R/W     |

| Reset  |   |   |   |   |   |   | 0       | 0       |

## Bit 1 – CRCZERO: CRC Zero

This bit is cleared when a new CRC source is selected.

This bit is set when the CRC generation is complete and the CRC Checksum is zero.

When running CRC-32 and appending the checksum at the end of the packet (as little endian), the final checksum should be 0x2144df1c, and not zero. However, if the checksum is complemented before it is appended (as little endian) to the data, the final result in the checksum register will be zero. See the description of CRCCHKSUM to read out different versions of the checksum.

## Bit 0 – CRCBUSY: CRC Module Busy

This flag is cleared by writing a one to it when used with I/O interface. When used with a DMA channel, the bit is set when the corresponding DMA channel is enabled, and cleared when the corresponding DMA channel is disabled. This register bit cannot be cleared by the application when the CRC is used with a DMA channel.

This bit is set when a source configuration is selected and as long as the source is using the CRC module.

## 20.8.6 Debug Control

Name:DBGCTRLOffset:0x0DReset:0x00

| Bit    | 15      | 14      | 13      | 12      | 11       | 10       | 9       | 8       |

|--------|---------|---------|---------|---------|----------|----------|---------|---------|

| ſ      |         |         |         |         | BUSYCH11 | BUSYCH10 | BUSYCH9 | BUSYCH8 |

| Access |         |         |         |         | R        | R        | R       | R       |

| Reset  |         |         |         |         | 0        | 0        | 0       | 0       |

|        |         |         |         |         |          |          |         |         |

| Bit    | 7       | 6       | 5       | 4       | 3        | 2        | 1       | 0       |

|        | BUSYCH7 | BUSYCH6 | BUSYCH5 | BUSYCH4 | BUSYCH3  | BUSYCH2  | BUSYCH1 | BUSYCH0 |

| Access | R       | R       | R       | R       | R        | R        | R       | R       |

| Reset  | 0       | 0       | 0       | 0       | 0        | 0        | 0       | 0       |

## Bits 11:0 – BUSYCHn: Busy Channel n [x=11..0]

This bit is cleared when the channel trigger action for DMA channel n is complete, when a bus error for DMA channel n is detected, or when DMA channel n is disabled.

This bit is set when DMA channel n starts a DMA transfer.

## 20.8.13 Pending Channels

Name:

PENDCH

Offset:

0x2C

Reset:

0x0000000

Property:

| Bit             | 31           | 30           | 29           | 28           | 27            | 26            | 25          | 24           |

|-----------------|--------------|--------------|--------------|--------------|---------------|---------------|-------------|--------------|

|                 |              |              |              |              |               |               |             |              |

| Access          |              |              |              |              |               |               |             |              |

| Reset           |              |              |              |              |               |               |             |              |

|                 |              |              |              |              |               |               |             |              |

| Bit             | 23           | 22           | 21           | 20           | 19            | 18            | 17          | 16           |

|                 |              |              |              |              |               |               |             |              |

| Access          |              |              |              |              |               |               |             |              |

| Reset           |              |              |              |              |               |               |             |              |

|                 |              |              |              |              |               |               |             |              |

| Bit             | 15           | 14           | 13           | 12           | 11            | 10            | 9           | 8            |

|                 |              |              |              |              |               |               |             |              |

| l               |              |              |              |              | PENDCH11      | PENDCH10      | PENDCH9     | PENDCH8      |

| Access          |              |              |              |              | PENDCH11<br>R | PENDCH10<br>R | R R         | PENDCH8<br>R |

| Access<br>Reset |              |              |              |              |               |               |             |              |

|                 |              |              |              |              | R             | R             | R           | R            |

|                 | 7            | 6            | 5            | 4            | R             | R             | R           | R            |

| Reset           | 7<br>PENDCH7 | 6<br>PENDCH6 | 5<br>PENDCH5 | 4<br>PENDCH4 | R<br>0        | R<br>0        | R           | R<br>0       |

| Reset           |              |              |              |              | R<br>0<br>3   | R<br>0<br>2   | R<br>0<br>1 | R<br>0<br>0  |

## Bits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11 – PENDCHn: Pending Channel n [n=11..0]

This bit is cleared when trigger execution defined by channel trigger action settings for DMA channel n is started, when a bus error for DMA channel n is detected or when DMA channel n is disabled. For details on trigger action settings, refer to CHCTRLB.TRIGACT.

This bit is set when a transfer is pending on DMA channel n.

## 20.8.14 Active Channel and Levels

Name:

ACTIVE

Offset:

0x30

Reset:

0x0000000

Property:

| Bit    | 31    | 30 | 29 | 28   | 27       | 26      | 25     | 24     |

|--------|-------|----|----|------|----------|---------|--------|--------|

|        |       |    |    | BTCN | IT[15:8] |         |        |        |

| Access | R     | R  | R  | R    | R        | R       | R      | R      |

| Reset  | 0     | 0  | 0  | 0    | 0        | 0       | 0      | 0      |

|        |       |    |    |      |          |         |        |        |

| Bit    | 23    | 22 | 21 | 20   | 19       | 18      | 17     | 16     |

|        |       |    |    | BTCI | NT[7:0]  |         |        |        |

| Access | R     | R  | R  | R    | R        | R       | R      | R      |

| Reset  | 0     | 0  | 0  | 0    | 0        | 0       | 0      | 0      |

|        |       |    |    |      |          |         |        |        |

| Bit    | 15    | 14 | 13 | 12   | 11       | 10      | 9      | 8      |

|        | ABUSY |    |    |      |          | ID[4:0] |        |        |

| Access | R     |    |    | R    | R        | R       | R      | R      |

| Reset  | 0     |    |    | 0    | 0        | 0       | 0      | 0      |

|        |       |    |    |      |          |         |        |        |

| Bit    | 7     | 6  | 5  | 4    | 3        | 2       | 1      | 0      |

|        |       |    |    |      | LVLEX3   | LVLEX2  | LVLEX1 | LVLEX0 |

| Access |       |    |    |      | R        | R       | R      | R      |

| Reset  |       |    |    |      | 0        | 0       | 0      | 0      |

## Bits 31:16 – BTCNT[15:0]: Active Channel Block Transfer Count

These bits hold the 16-bit block transfer count of the ongoing transfer. This value is stored in the active channel and written back in the corresponding Write-Back channel memory location when the arbiter grants a new channel access. The value is valid only when the active channel active busy flag (ABUSY) is set.

## Bit 15 – ABUSY: Active Channel Busy

This bit is cleared when the active transfer count is written back in the write-back memory section.

This bit is set when the next descriptor transfer count is read from the write-back memory section.

## Bits 12:8 - ID[4:0]: Active Channel ID

These bits hold the channel index currently stored in the active channel registers. The value is updated each time the arbiter grants a new channel transfer access request.

### Bits 3,2,1,0 – LVLEXx: Level x Channel Trigger Request Executing [x=3..0]

This bit is set when a level-x channel trigger request is executing or pending.

This bit is cleared when no request is pending or being executed.

### 20.8.15 Descriptor Memory Section Base Address

| Name:   | BASEADDR   |

|---------|------------|

| Offset: | 0x34       |

| Reset:  | 0x00000000 |

| Offset | Name    | Bit<br>Pos. |                |                |                |                |                |                |                |                |

|--------|---------|-------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

|        |         | F05.        |                |                |                |                |                |                |                |                |

| 0x10   |         | 7:0         | EXTINT7        | EXTINT6        | EXTINT5        | EXTINT4        | EXTINT3        | EXTINT2        | EXTINT1        | EXTINT0        |

| 0x11   | INTFLAG | 15:8        | EXTINT15       | EXTINT14       | EXTINT13       | EXTINT12       | EXTINT11       | EXTINT10       | EXTINT9        | EXTINT8        |

| 0x12   | INTLAG  | 23:16       |                |                |                |                |                |                | EXTINT17       | EXTINT16       |

| 0x13   |         | 31:24       |                |                |                |                |                |                |                |                |

| 0x14   |         | 7:0         | WAKEUPEN7      | WAKEUPEN6      | WAKEUPEN5      | WAKEUPEN4      | WAKEUPEN3      | WAKEUPEN2      | WAKEUPEN1      | WAKEUPEN0      |

| 0x15   | WAKEUP  | 15:8        | WAKEUPEN1<br>5 | WAKEUPEN1<br>4 | WAKEUPEN1<br>3 | WAKEUPEN1<br>2 | WAKEUPEN1<br>1 | WAKEUPEN1<br>0 | WAKEUPEN9      | WAKEUPEN8      |

| 0x16   | WAREUP  | 23:16       |                |                |                |                |                |                | WAKEUPEN1<br>7 | WAKEUPEN1<br>6 |

| 0x17   |         | 31:24       |                |                |                |                |                |                |                |                |

| 0x18   |         | 7:0         | FILTEN1        |                | SENSE1[2:0]    |                | FILTEN0        | SENSE0[2:0]    |                | 1              |

| 0x19   |         | 15:8        | FILTEN3        | SENSE3[2:0]    |                |                | FILTEN2        |                | SENSE2[2:0]    |                |

| 0x1A   | CONFIG0 | 23:16       | FILTEN5        | SENSE5[2:0]    |                |                | FILTEN4        | SENSE4[2:0]    |                |                |

| 0x1B   |         | 31:24       | FILTEN7        |                | SENSE7[2:0]    |                | FILTEN6        | SENSE6[2:0]    |                |                |

| 0x1C   |         | 7:0         | FILTEN9        |                | SENSE9[2:0]    |                | FILTEN8        | SENSE8[2:0]    |                |                |

| 0x1D   |         | 15:8        | FILTEN11       |                | SENSE11[2:0]   |                | FILTEN10       | SENSE10[2:0]   |                |                |

| 0x1E   | CONFIG1 | 23:16       | FILTEN13       |                | SENSE13[2:0]   |                | FILTEN12       | SENSE12[2:0]   |                |                |

| 0x1F   |         | 31:24       | FILTEN15       | SENSE15[2:0]   |                | FILTEN14       | SENSE14[2:0]   |                |                |                |

| 0x20   |         | 7:0         | FILTEN25       |                | SENSE25[2:0]   |                | FILTEN24       |                | SENSE24[2:0]   |                |

| 0x21   | CONFIG2 | 15:8        | FILTEN27       |                | SENSE27[2:0]   |                | FILTEN26       |                | SENSE26[2:0]   |                |

| 0x22   | CUNFIGZ | 23:16       | FILTEN29       |                | SENSE29[2:0]   |                | FILTEN28       | SENSE28[2:0]   |                |                |

| 0x23   |         | 31:24       | FILTEN31       |                | SENSE31[2:0]   |                | FILTEN30       |                | SENSE30[2:0]   |                |

## 21.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

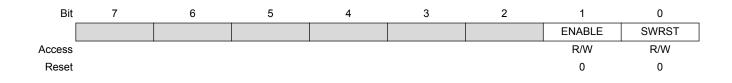

## 21.8.1 Control

Name: CTRL Offset: 0x00 Reset: 0x00 Property: Write-Protected, Write-Synchronized

| Bit    | 7 | 6 | 5 | 4 | 3         | 2   | 1             | 0   |

|--------|---|---|---|---|-----------|-----|---------------|-----|

|        |   |   |   |   | NMIFILTEN |     | NMISENSE[2:0] | l   |

| Access |   |   |   |   | R/W       | R/W | R/W           | R/W |

| Reset  |   |   |   |   | 0         | 0   | 0             | 0   |

## Bit 3 – NMIFILTEN: Non-Maskable Interrupt Filter Enable

| Value | Description             |

|-------|-------------------------|

| 0     | NMI filter is disabled. |

| 1     | NMI filter is enabled.  |

## Bits 2:0 – NMISENSE[2:0]: Non-Maskable Interrupt Sense

These bits define on which edge or level the NMI triggers.

| NMISENSE[2:0] | Name | Description            |

|---------------|------|------------------------|

| 0x0           | NONE | No detection           |

| 0x1           | RISE | Rising-edge detection  |

| 0x2           | FALL | Falling-edge detection |

| 0x3           | BOTH | Both-edges detection   |

| 0x4           | HIGH | High-level detection   |

| 0x5           | LOW  | Low-level detection    |

| 0x6-0x7       |      | Reserved               |

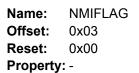

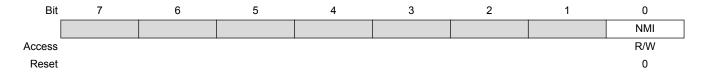

## 21.8.4 Non-Maskable Interrupt Flag Status and Clear

## Bit 0 – NMI: Non-Maskable Interrupt

This flag is cleared by writing a one to it.

This flag is set when the NMI pin matches the NMI sense configuration, and will generate an interrupt request.

Writing a zero to this bit has no effect.

Writing a one to this bit clears the non-maskable interrupt flag.

## 21.8.5 Event Control

Name: EVCTRL

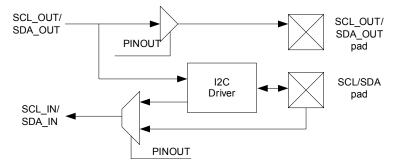

## Figure 28-13. I<sup>2</sup>C Pad Interface

### 28.6.3.4 Quick Command

Setting the Quick Command Enable bit in the Control B register (CTRLB.QCEN) enables quick command. When quick command is enabled, the corresponding interrupt flag (INTFLAG.SB or INTFLAG.MB) is set immediately after the slave acknowledges the address. At this point, the software can either issue a stop command or a repeated start by writing CTRLB.CMD or ADDR.ADDR.

## 28.6.4 DMA, Interrupts and Events

## Table 28-1. Module Request for SERCOM I<sup>2</sup>C Slave

| Condition                                                 | Request                                          |           |       |  |  |  |  |  |

|-----------------------------------------------------------|--------------------------------------------------|-----------|-------|--|--|--|--|--|

|                                                           | DMA                                              | Interrupt | Event |  |  |  |  |  |

| Data needed for transmit<br>(TX) (Slave transmit<br>mode) | Yes<br>(request cleared when<br>data is written) |           | NA    |  |  |  |  |  |

| Data received (RX)<br>(Slave receive mode)                | Yes<br>(request cleared when<br>data is read)    |           |       |  |  |  |  |  |

| Data Ready (DRDY)                                         |                                                  | Yes       |       |  |  |  |  |  |

| Address Match<br>(AMATCH)                                 |                                                  | Yes       |       |  |  |  |  |  |

| Stop received (PREC)                                      |                                                  | Yes       |       |  |  |  |  |  |

| Error (ERROR)                                             |                                                  | Yes       |       |  |  |  |  |  |

## **Waveform Output Generation Operations**

The compare channels can be used for waveform generation on output port pins. To make the waveform available on the connected pin, the following requirements must be fulfilled:

- 1. Choose a waveform generation mode in the Waveform Generation Operation bit in Waveform register (WAVE.WAVEGEN).

- 2. Optionally invert the waveform output WO[x] by writing the corresponding Waveform Output x Inversion bit in the Driver Control register (DRVCTRL.INVENx).

- 3. Configure the pins with the I/O Pin Controller. Refer to PORT I/O Pin Controller for details.

The counter value is continuously compared with each CCx value. On a comparison match, the Match or Capture Channel x bit in the Interrupt Flag Status and Clear register (INTFLAG.MCx) will be set on the next zero-to-one transition of CLK\_TCC\_COUNT (see Normal Frequency Operation). An interrupt and/or event can be generated on the same condition if Match/Capture occurs, i.e. INTENSET.MCx and/or EVCTRL.MCEOx is '1'. Both interrupt and event can be generated simultaneously. The same condition generates a DMA request.

There are seven waveform configurations for the Waveform Generation Operation bit group in the Waveform register (WAVE.WAVEGEN). This will influence how the waveform is generated and impose restrictions on the top value. The configurations are:

- Normal Frequency (NFRQ)

- Match Frequency (MFRQ)

- Normal Pulse-Width Modulation (NPWM)

- Dual-slope, interrupt/event at TOP (DSTOP)

- Dual-slope, interrupt/event at ZERO (DSBOTTOM)

- Dual-slope, interrupt/event at Top and ZERO (DSBOTH)

- Dual-slope, critical interrupt/event at ZERO (DSCRITICAL)

When using MFRQ configuration, the TOP value is defined by the CC0 register value. For the other waveform operations, the TOP value is defined by the Period (PER) register value.

For dual-slope waveform operations, the update time occurs when the counter reaches ZERO. For the other waveforms generation modes, the update time occurs on counter wraparound, on overflow, underflow, or re-trigger.

The table below shows the update counter and overflow event/interrupt generation conditions in different operation modes.

| Name | Operation           | ТОР | Update       | Output Waveform |           | OVFIF/Event |      |

|------|---------------------|-----|--------------|-----------------|-----------|-------------|------|

|      |                     |     |              | On Match        | On Update | Up          | Down |

| NFRQ | Normal<br>Frequency | PER | TOP/<br>ZERO | Toggle          | Stable    | ТОР         | ZERO |

| MFRQ | Match<br>Frequency  | CC0 | TOP/<br>ZERO | Toggle          | Stable    | ТОР         | ZERO |

### Table 31-2. Counter Update and Overflow Event/interrupt Conditions

## 32.8.3.7 Device Interrupt EndPoint Set n

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Endpoint Interrupt Enable Set (EPINTENCLR) register. This register is cleared by USB reset or when EPEN[n] is zero.

Name:EPINTENSETnOffset:0x109 + (n x 0x20)Reset:0x0000Property:PAC Write-Protection

| Bit    | 7 | 6 | 5     | 4     | 3 | 2      | 1 | 0     |

|--------|---|---|-------|-------|---|--------|---|-------|

|        |   |   | STALL | RXSTP |   | TRFAIL |   | TRCPT |

| Access |   |   | R/W   | R/W   |   | R/W    |   | R/W   |

| Reset  |   |   | 0     | 0     |   | 0      |   | 0     |

## Bit 5 – STALL: Transmit Stall x Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will enable the Transmit bank x Stall interrupt.

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | The Transmit Stall x interrupt is disabled. |

| 1     | The Transmit Stall x interrupt is enabled.  |

## Bit 4 – RXSTP: Received Setup Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will enable the Received Setup interrupt.

| Value | Description                               |

|-------|-------------------------------------------|

| 0     | The Received Setup interrupt is disabled. |

| 1     | The Received Setup interrupt is enabled.  |

### Bit 2 – TRFAIL: Transfer Fail bank x Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will enable the Transfer Fail interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The Transfer Fail interrupt is disabled. |

| 1     | The Transfer Fail interrupt is enabled.  |

## Bit 0 – TRCPT: Transfer Complete bank x interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will enable the Transfer Complete x interrupt.

### 0.2.4 Device Registers - Endpoint RAM

| Value | Description                                         |

|-------|-----------------------------------------------------|

| 0     | The Transfer Complete bank x interrupt is disabled. |

| 1     | The Transfer Complete bank x interrupt is enabled.  |

| PTOKEN[1:0] 1) | Description |

|----------------|-------------|

| 0x2            | OUT         |

| 0x3            | Reserved    |

1. PTOKEN field is ignored when PTYPE is configured as EXTENDED.

2. Available only when PTYPE is configured as CONTROL

Theses bits are cleared upon sending a USB reset.

## 32.8.6.2 Interval for the Bulk-Out/Ping Transaction

Name:BINTERVALOffset:0x103 + (n x 0x20)Reset:0x00Property:PAC Write-Protection

| Bit    | 7   | 6   | 5   | 4      | 3        | 2   | 1   | 0   |

|--------|-----|-----|-----|--------|----------|-----|-----|-----|

| Γ      |     |     |     | BINTER | VAL[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W    | R/W      | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0      | 0        | 0   | 0   | 0   |

## Bits 7:0 - BINTERVAL[7:0]: BINTERVAL

These bits contains the Ping/Bulk-out period.

These bits are cleared when a USB reset is sent or when PEN[n] is zero.

| BINTERVAL | Description                                                                                  |

|-----------|----------------------------------------------------------------------------------------------|

| =0        | Multiple consecutive OUT token is sent in the same frame until it is acked by the peripheral |

| >0        | One OUT token is sent every BINTERVAL frame until it is acked by the peripheral              |

Depending from the type of pipe the desired period is defined as:

| ΡΤΥΡΕ           | Description                                             |

|-----------------|---------------------------------------------------------|

| Interrupt       | 1 ms to 255 ms                                          |

| Isochronous     | 2^(Binterval) * 1 ms                                    |

| Bulk or control | 1 ms to 255 ms                                          |

| EXT LPM         | bInterval ignored. Always 1 ms when a NYET is received. |

## 32.8.6.3 Pipe Status Clear n

Name:PSTATUSCLROffset:0x104 + (n x 0x20)Reset:0x00Property:PAC Write-Protection

## Bit 19 – HYST: Hysteresis Enable

This bit indicates the hysteresis mode of comparator n. Hysteresis is available only for continuous mode (COMPCTRLn. SINGLE=0). COMPCTRLn.HYST can be written only while COMPCTRLn.ENABLE is zero.

This bit is not synchronized.

These bits are not synchronized.

| Value | Name                    |

|-------|-------------------------|

| 0     | Hysteresis is disabled. |

| 1     | Hysteresis is enabled.  |

## Bits 17:16 – OUT[1:0]: Output

These bits configure the output selection for comparator n. COMPCTRLn.OUT can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value | Name  | Description                                                                           |

|-------|-------|---------------------------------------------------------------------------------------|

| 0x0   | OFF   | The output of COMPn is not routed to the COMPn I/O port                               |

| 0x1   | ASYNC | The asynchronous output of COMPn is routed to the COMPn I/O port                      |

| 0x2   | SYNC  | The synchronous output (including filtering) of COMPn is routed to the COMPn I/O port |

| 0x3   | N/A   | Reserved                                                                              |

## Bit 15 – SWAP: Swap Inputs and Invert

This bit swaps the positive and negative inputs to COMPn and inverts the output. This function can be used for offset cancellation. COMPCTRLn.SWAP can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | The output of MUXPOS connects to the positive input, and the output of MUXNEG connects |

|       | to the negative input.                                                                 |

| 1     | The output of MUXNEG connects to the positive input, and the output of MUXPOS connects |

|       | to the negative input.                                                                 |

## Bits 13:12 – MUXPOS[1:0]: Positive Input Mux Selection

These bits select which input will be connected to the positive input of comparator n. COMPCTRLn.MUXPOS can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value | Name | Description |

|-------|------|-------------|

| 0x0   | PIN0 | I/O pin 0   |

| 0x1   | PIN1 | I/O pin 1   |

| 0x2   | PIN2 | I/O pin 2   |

| 0x3   | PIN3 | I/O pin 3   |

## Bits 10:8 – MUXNEG[2:0]: Negative Input Mux Selection

These bits select which input will be connected to the negative input of comparator n. COMPCTRLn.MUXNEG can only be written while COMPCTRLn.ENABLE is zero.

Name:DATAOffset:0x08Reset:0x0000Property:PAC Write-Protection, Write-Synchronized

| Bit    | 15 | 14 | 13 | 12   | 11     | 10 | 9 | 8 |

|--------|----|----|----|------|--------|----|---|---|

|        |    |    |    | DATA | [15:8] |    |   |   |

| Access | W  | W  | W  | W    | W      | W  | W | W |

| Reset  | 0  | 0  | 0  | 0    | 0      | 0  | 0 | 0 |

|        |    |    |    |      |        |    |   |   |

| Bit    | 7  | 6  | 5  | 4    | 3      | 2  | 1 | 0 |

|        |    |    |    | DATA | 4[7:0] |    |   |   |

| Access | W  | W  | W  | W    | W      | W  | W | W |

| Reset  | 0  | 0  | 0  | 0    | 0      | 0  | 0 | 0 |

## Bits 15:0 – DATA[15:0]: Data value to be converted

DATA register contains the 10-bit value that is converted to a voltage by the DAC. The adjustment of these 10 bits within the 16-bit register is controlled by CTRLB.LEFTADJ.

| Table 35-1. Valid Data | Table 35-1. | Valid | Data | Bits |

|------------------------|-------------|-------|------|------|

|------------------------|-------------|-------|------|------|

| CTRLB.LEFTADJ | DATA       | Description             |

|---------------|------------|-------------------------|

| 0             | DATA[9:0]  | Right adjusted, 10-bits |

| 1             | DATA[15:6] | Left adjusted, 10-bits  |

## 35.8.9 Data Buffer

Name:DATABUFOffset:0x0CReset:0x0000Property:Write-Synchronized

| Bit    | 15            | 14 | 13 | 12 | 11 | 10 | 9 | 8 |  |

|--------|---------------|----|----|----|----|----|---|---|--|

|        | DATABUF[15:8] |    |    |    |    |    |   |   |  |

| Access | W             | W  | W  | W  | W  | W  | W | W |  |

| Reset  | 0             | 0  | 0  | 0  | 0  | 0  | 0 | 0 |  |

|        |               |    |    |    |    |    |   |   |  |

| Bit    | 7             | 6  | 5  | 4  | 3  | 2  | 1 | 0 |  |

|        | DATABUF[7:0]  |    |    |    |    |    |   |   |  |

| Access | W             | W  | W  | W  | W  | W  | W | W |  |

| Reset  | 0             | 0  | 0  | 0  | 0  | 0  | 0 | 0 |  |

## Bits 15:0 – DATABUF[15:0]: Data Buffer

DATABUF contains the value to be transferred into DATA register.

| Symbol | Parameter                      | Conditions                                 | Min.    | Тур.   | Max.    | Units |

|--------|--------------------------------|--------------------------------------------|---------|--------|---------|-------|

|        | Gain Error                     | Ext. Ref 1x                                | -10.0   | 2.5    | +10.0   | mV    |

|        |                                | V <sub>REF</sub> =V <sub>DDANA</sub> /1.48 | -15.0   | -1.5   | +10.0   | mV    |

|        |                                | Bandgap                                    | -20.0   | -5.0   | +20.0   | mV    |

|        | Gain Accuracy <sup>(5)</sup>   | Ext. Ref. 0.5x                             | +/-0.1  | +/-0.2 | +/-0.45 | %     |

|        |                                | Ext. Ref. 2x to 16x                        | +/-0.05 | +/-0.1 | +/-0.11 | %     |

|        | Offset Error                   | Ext. Ref. 1x                               | -5.0    | -1.5   | +5.0    | mV    |

|        |                                | V <sub>REF</sub> =V <sub>DDANA</sub> /1.48 | -5.0    | 0.5    | +5.0    | mV    |

|        |                                | Bandgap                                    | -5.0    | 3.0    | +5.0    | mV    |

| SFDR   | Spurious Free Dynamic Range    | 1x Gain                                    | 62.7    | 70.0   | 75.0    | dB    |

| SINAD  | Signal-to-Noise and Distortion | $F_{CLK\_ADC} = 2.1MHz$                    | 54.1    | 65.0   | 68.5    | dB    |

| SNR    | Signal-to-Noise Ratio          | $F_{IN} = 40 \text{kHz}$                   | 54.5    | 65.5   | 68.6    | dB    |

| THD    | Total Harmonic Distortion      | A <sub>IN</sub> = 95%FSR                   | -77.0   | -64.0  | -63.0   | dB    |

|        | Noise RMS                      | T=25°C                                     | 0.6     | 1.0    | 1.6     | mV    |

## Table 37-24. Differential Mode (Device Variant B and C)

| Symbol | Parameter                      | Conditions                                 | Min.    | Тур.    | Max.    | Units |

|--------|--------------------------------|--------------------------------------------|---------|---------|---------|-------|

| ENOB   | Effective Number Of Bits       | With gain compensation                     | -       | 10.5    | 10.8    | bits  |

| TUE    | Total Unadjusted Error         | 1x gain                                    | 1.5     | 2.7     | 10.0    | LSB   |

| INLI   | Integral Non Linearity         | 1x gain                                    | 0.9     | 1.3     | 4.0     | LSB   |

| DNL    | Differential Non Linearity     | 1x gain                                    | +/-0.3  | +/-0.5  | +/-0.95 | LSB   |

|        | Gain Error                     | Ext. Ref 1x                                | -10.0   | 1.3     | +10.0   | mV    |

|        |                                | V <sub>REF</sub> =V <sub>DDANA</sub> /1.48 | -10.0   | -1.0    | +10.0   | mV    |

|        |                                | Bandgap                                    | -20.0   | -2.0    | +20.0   | mV    |

|        | Gain Accuracy <sup>(5)</sup>   | Ext. Ref. 0.5x                             | +/-0.02 | +/-0.05 | +/-0.1  | %     |

|        |                                | Ext. Ref. 2x to 16x                        | +/-0.01 | +/-0.03 | +/-0.5  | %     |

|        | Offset Error                   | Ext. Ref. 1x                               | -5.0    | -1.0    | +5.0    | mV    |

|        |                                | V <sub>REF</sub> =V <sub>DDANA</sub> /1.48 | -5.0    | 0.6     | +5.0    | mV    |

|        |                                | Bandgap                                    | -5.0    | -1.0    | +5.0    | mV    |

| SFDR   | Spurious Free Dynamic Range    | 1x gain                                    | 65      | 71.3    | 77.0    | dB    |

| SINAD  | Signal-to-Noise and Distortion | $F_{CLK\_ADC} = 2.1 MHz$                   | 58      | 65      | 67      | dB    |

| SNR    | Signal-to-Noise Ratio          | $F_{IN} = 40 \text{kHz}$                   | 60      | 66      | 68.6    | dB    |

| THD    | Total Harmonic Distortion      | A <sub>IN</sub> = 95%FSR                   | -75.0   | -71.0   | -67.0   | dB    |

|        | Noise RMS                      | T=25°C                                     | 0.6     | 1.0     | 1.6     | mV    |

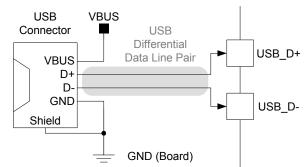

## Figure 39-14. Low Cost USB Interface Example Schematic

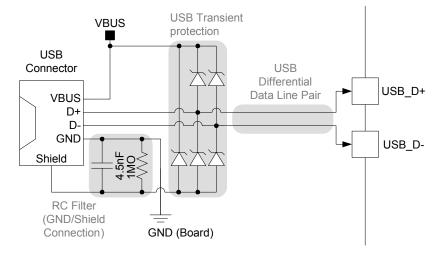

It is recommended to increase ESD protection on the USB D+, D-, and VBUS lines using dedicated transient suppressors. These protections should be located as close as possible to the USB connector to reduce the potential discharge path and reduce discharge propagation within the entire system.

The USB FS cable includes a dedicated shield wire that should be connected to the board with caution. Special attention should be paid to the connection between the board ground plane and the shield from the USB connector and the cable.

Tying the shield directly to ground would create a direct path from the ground plane to the shield, turning the USB cable into an antenna. To limit the USB cable antenna effect, it is recommended to connect the shield and ground through an RC filter.

## Figure 39-15. Protected USB Interface Example Schematic

## 44.9.3 I2S Timing

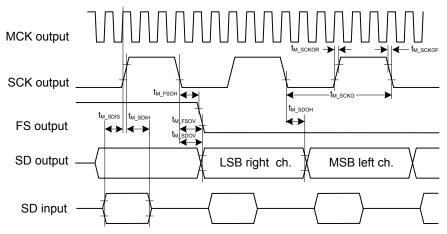

Figure 44-5. I2S Timing Master Mode

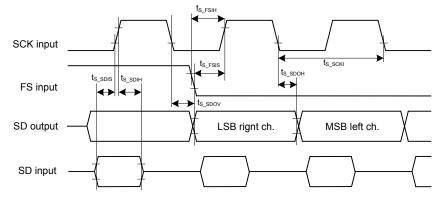

Figure 44-6. I2S Timing Slave Mode

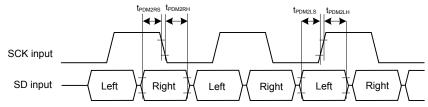

Table 44-51. I2S Timing Characteristics and Requirements (Device Variant A)

| Symbol               | Description                      | Mode                                           | VDD=1.8V |      |      | VDD=3.3V |      |     | Units |

|----------------------|----------------------------------|------------------------------------------------|----------|------|------|----------|------|-----|-------|

|                      |                                  |                                                | Min.     | Тур. | Max. | Min.     | Тур. | Max |       |

| t <sub>M_MCKOR</sub> | I2S MCK rise time <sup>(3)</sup> | Master mode /<br>Capacitive load CL =<br>15 pF |          |      | 10   |          |      | 4.7 | ns    |

| t <sub>M_MCKOF</sub> | I2S MCK fall time <sup>(3)</sup> | Master mode /<br>Capacitive load CL =<br>15 pF |          |      | 12.1 |          |      | 5.3 | ns    |

| d <sub>M_MCKO</sub>  | I2S MCK duty cycle               | Master mode                                    | 45.4     |      | 50   | 45.4     |      | 50  | %     |