Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | ARM® Cortex®-M0+                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 48MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 52                                                                        |

| Program Memory Size        | 256KB (256K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 32K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                              |

| Data Converters            | A/D 20x12b; D/A 1x10b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd21j18a-af |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 17. | SYSCTRL – System Controller            | 150 |

|-----|----------------------------------------|-----|

|     | 17.1. Overview                         |     |

|     | 17.2. Features                         |     |

|     | 17.3. Block Diagram                    |     |

|     | 17.4. Signal Description               |     |

|     | 17.5. Product Dependencies             |     |

|     | 17.6. Functional Description           |     |

|     | 17.7. Register Summary                 | 170 |

|     | 17.8. Register Description             |     |

| 18. | WDT – Watchdog Timer                   |     |

|     | 18.1. Overview                         |     |

|     | 18.2. Features                         |     |

|     | 18.3. Block Diagram                    |     |

|     | 18.4. Signal Description               |     |

|     | 18.5. Product Dependencies             |     |

|     | 18.6. Functional Description           | 207 |

|     | 18.7. Register Summary                 | 212 |

|     | 18.8. Register Description             | 212 |

| 19. | RTC – Real-Time Counter                | 218 |

|     | 19.1. Overview                         |     |

|     | 19.2. Features                         |     |

|     | 19.3. Block Diagram                    | 219 |

|     | 19.4. Signal Description               |     |

|     | 19.5. Product Dependencies             |     |

|     | 19.6. Functional Description           | 221 |

|     | 19.7. Register Summary                 |     |

|     | 19.8. Register Description             |     |

| 20. | DMAC – Direct Memory Access Controller |     |

|     | 20.1. Overview                         | 252 |

|     | 20.2. Features                         |     |

|     | 20.3. Block Diagram                    |     |

|     | 20.4. Signal Description               |     |

|     | 20.5. Product Dependencies             |     |

|     | 20.6. Functional Description           |     |

|     | 20.7. Register Summary                 |     |

|     | 20.8. Register Description             |     |

|     | 20.9. Register Summary - SRAM          |     |

|     | 20.10. Register Description - SRAM     |     |

| 21. | EIC – External Interrupt Controller    |     |

|     | 21.1. Overview                         |     |

|     | 21.2. Features                         |     |

|     | 21.3. Block Diagram                    |     |

|     | 21.4. Signal Description               |     |

|     | 21.5. Product Dependencies             |     |

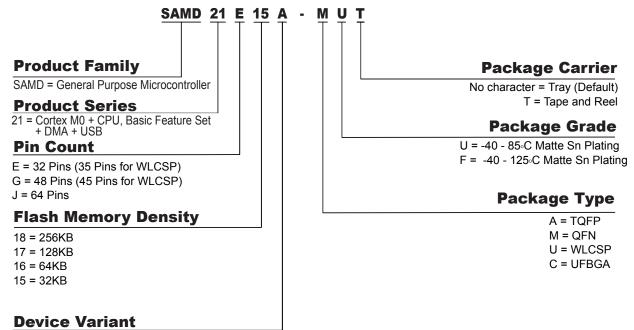

## 3. Ordering Information

A = Default Variant

B = Added RWW support for 32KB and 64KB memory options

C = Silicon revision F for WLCSP35 package option.

## 3.1 SAM D21E

## Table 3-1. Device Variant A

| Ordering Code    | FLASH (bytes) | SRAM (bytes) | Package | Carrier Type |

|------------------|---------------|--------------|---------|--------------|

| ATSAMD21E15A-AU  | 32K           | 4K           | TQFP32  | Tray         |

| ATSAMD21E15A-AUT |               |              |         | Tape & Reel  |

| ATSAMD21E15A-AF  |               |              |         | Tray         |

| ATSAMD21E15A-AFT |               |              |         | Tape & Reel  |

| ATSAMD21E15A-MU  |               |              | QFN32   | Tray         |

| ATSAMD21E15A-MUT |               |              |         | Tape & Reel  |

| ATSAMD21E15A-MF  |               |              |         | Tray         |

| ATSAMD21E15A-MFT |               |              |         | Tape & Reel  |

| Ordering Code    | FLASH (bytes) | SRAM (bytes) | Package | Carrier Type |

|------------------|---------------|--------------|---------|--------------|

| ATSAMD21E16A-AU  | 64K           | 8K           | TQFP32  | Tray         |

| ATSAMD21E16A-AUT | -             |              |         | Tape & Reel  |

| ATSAMD21E16A-AF  | -             |              |         | Tray         |

| ATSAMD21E16A-AFT | -             |              |         | Tape & Reel  |

| ATSAMD21E16A-MU  | -             |              | QFN32   | Tray         |

| ATSAMD21E16A-MUT | -             |              |         | Tape & Reel  |

| ATSAMD21E16A-MF  | -             |              |         | Tray         |

| ATSAMD21E16A-MFT | -             |              |         | Tape & Reel  |

| ATSAMD21E17A-AU  | 128K          | 16K          | TQFP32  | Tray         |

| ATSAMD21E17A-AUT | -             |              |         | Tape & Reel  |

| ATSAMD21E17A-AF  | -             |              |         | Tray         |

| ATSAMD21E17A-AFT | -             |              |         | Tape & Reel  |

| ATSAMD21E17A-MU  | -             |              | QFN32   | Tray         |

| ATSAMD21E17A-MUT | -             |              |         | Tape & Reel  |

| ATSAMD21E17A-MF  | -             |              |         | Tray         |

| ATSAMD21E17A-MFT | -             |              |         | Tape & Reel  |

| ATSAMD21E18A-AU  | 256K          | 32K          | TQFP32  | Tray         |

| ATSAMD21E18A-AUT | -             |              |         | Tape & Reel  |

| ATSAMD21E18A-AF  | -             |              |         | Tray         |

| ATSAMD21E18A-AFT |               |              |         | Tape & Reel  |

| ATSAMD21E18A-MU  | -             |              | QFN32   | Tray         |

| ATSAMD21E18A-MUT |               |              |         | Tape & Reel  |

| ATSAMD21E18A-MF  |               |              |         | Tray         |

| ATSAMD21E18A-MFT |               |              |         | Tape & Reel  |

## 10. Memories

## **10.1 Embedded Memories**

- Internal high-speed flash with Read-While-Write (RWW) capability on section of the array (Device Variant B).

- Internal high-speed flash

- Internal high-speed RAM, single-cycle access at full speed

## 10.2 Physical Memory Map

The High-Speed bus is implemented as a bus matrix. All High-Speed bus addresses are fixed, and they are never remapped in any way, even during boot. The 32-bit physical address space is mapped as follow:

| Table 10-1. | SAM D21 | physical | memory | map <sup>(1)</sup> |

|-------------|---------|----------|--------|--------------------|

|-------------|---------|----------|--------|--------------------|

| Memory                              | Start address | Size      |           |           |           |

|-------------------------------------|---------------|-----------|-----------|-----------|-----------|

|                                     |               | SAMD21x18 | SAMD21x17 | SAMD21x16 | SAMD21x15 |

| Internal Flash                      | 0x0000000     | 256Kbytes | 128Kbytes | 64Kbytes  | 32Kbytes  |

| Internal RWW section <sup>(2)</sup> | 0x00400000    | -         | -         | 2Kbytes   | 1Kbytes   |

| Internal SRAM                       | 0x20000000    | 32Kbytes  | 16Kbytes  | 8Kbytes   | 4Kbytes   |

| Peripheral Bridge A                 | 0x40000000    | 64Kbytes  | 64Kbytes  | 64Kbytes  | 64Kbytes  |

| Peripheral Bridge B                 | 0x41000000    | 64Kbytes  | 64Kbytes  | 64Kbytes  | 64Kbytes  |

| Peripheral Bridge C                 | 0x42000000    | 64Kbytes  | 64Kbytes  | 64Kbytes  | 64Kbytes  |

1. x = G, J or E.

2. Only applicable for Device Variant B.

## Table 10-2. Flash memory parameters<sup>(1)</sup>

| Device    | Flash size | Number of pages | Page size |

|-----------|------------|-----------------|-----------|

| SAMD21x18 | 256Kbytes  | 4096            | 64 bytes  |

| SAMD21x17 | 128Kbytes  | 2046            | 64 bytes  |

| SAMD21x16 | 64Kbytes   | 1024            | 64 bytes  |

| SAMD21x15 | 32Kbytes   | 512             | 64 bytes  |

1. x = G, J or E.

2. The number of pages (NVMP) and page size (PSZ) can be read from the NVM Pages and Page Size bits in the NVM Parameter register in the NVMCTRL (PARAM.NVMP and PARAM.PSZ, respectively). Refer to *NVM Parameter* (PARAM) register for details.

# Table 13-6. Available Features when Operated From The External Address Range and Device is Protected

| Features                                  | Availability From The External Address Range and Device is Protected |

|-------------------------------------------|----------------------------------------------------------------------|

| Chip-Erase command and status             | Yes                                                                  |

| CRC32                                     | Yes, only full array or full EEPROM                                  |

| CoreSight Compliant Device identification | Yes                                                                  |

| Debug communication channels              | Yes                                                                  |

| Testing of onboard memories (MBIST)       | No                                                                   |

| STATUSA.CRSTEXT clearing                  | No (STATUSA.PERR is set when attempting to do so)                    |

| Bit    | 15 | 14   | 13      | 12 | 11 | 10 | 9   | 8     |

|--------|----|------|---------|----|----|----|-----|-------|

|        |    | ADDO | FF[3:0] |    |    |    |     |       |

| Access | R  | R    | R       | R  |    |    |     |       |

| Reset  | x  | x    | x       | x  |    |    |     |       |

|        |    |      |         |    |    |    |     |       |

| Bit    | 7  | 6    | 5       | 4  | 3  | 2  | 1   | 0     |

|        |    |      |         |    |    |    | FMT | EPRES |

| Access |    | •    |         |    |    |    | R   | R     |

| Reset  |    |      |         |    |    |    | 1   | x     |

|        |    |      |         |    |    |    |     |       |

### Bits 31:12 - ADDOFF[19:0]: Address Offset

The base address of the component, relative to the base address of this ROM table.

### Bit 1 – FMT: Format

Always read as '1', indicating a 32-bit ROM table.

### Bit 0 – EPRES: Entry Present

This bit indicates whether an entry is present at this location in the ROM table.

This bit is set at power-up if the device is not protected indicating that the entry is not present.

This bit is cleared at power-up if the device is not protected indicating that the entry is present.

## 13.13.12 CoreSight ROM Table End

Name:

END

Offset:

0x1008

Reset:

0x0000000

Property:

| Bit    | 31 | 30 | 29 | 28   | 27     | 26 | 25 | 24 |

|--------|----|----|----|------|--------|----|----|----|

|        |    |    |    | END[ | 31:24] |    |    |    |

| Access | R  | R  | R  | R    | R      | R  | R  | R  |

| Reset  | 0  | 0  | 0  | 0    | 0      | 0  | 0  | 0  |

|        |    |    |    |      |        |    |    |    |

| Bit    | 23 | 22 | 21 | 20   | 19     | 18 | 17 | 16 |

|        |    |    |    | END[ | 23:16] |    |    |    |

| Access | R  | R  | R  | R    | R      | R  | R  | R  |

| Reset  | 0  | 0  | 0  | 0    | 0      | 0  | 0  | 0  |

|        |    |    |    |      |        |    |    |    |

| Bit    | 15 | 14 | 13 | 12   | 11     | 10 | 9  | 8  |

|        |    |    |    | END  | [15:8] |    |    |    |

| Access | R  | R  | R  | R    | R      | R  | R  | R  |

| Reset  | 0  | 0  | 0  | 0    | 0      | 0  | 0  | 0  |

|        |    |    |    |      |        |    |    |    |

| Bit    | 7  | 6  | 5  | 4    | 3      | 2  | 1  | 0  |

|        |    |    |    | END  | [7:0]  |    |    |    |

| Access | R  | R  | R  | R    | R      | R  | R  | R  |

| Reset  | 0  | 0  | 0  | 0    | 0      | 0  | 0  | 0  |

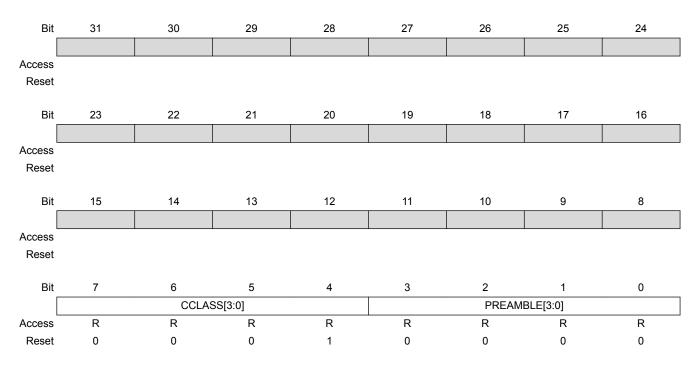

| Reset:    | 0x0000010 |

|-----------|-----------|

| Property: | -         |

## Bits 7:4 – CCLASS[3:0]: Component Class

These bits will always return 0x1 when read indicating that this ARM CoreSight component is ROM table (refer to the ARM Debug Interface v5 Architecture Specification at http://www.arm.com).

## Bits 3:0 – PREAMBLE[3:0]: Preamble

These bits will always return 0x0 when read.

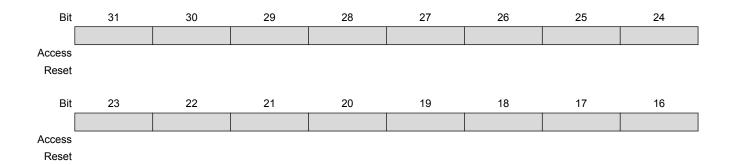

## 13.13.21 Component Identification 2

Name:

CID2

Offset:

0x1FF8

Reset:

0x00000005

Property:

| APBCDIV[2:0] | Name   | Description   |

|--------------|--------|---------------|

| 0x2          | DIV4   | Divide by 4   |

| 0x3          | DIV8   | Divide by 8   |

| 0x4          | DIV16  | Divide by 16  |

| 0x5          | DIV32  | Divide by 32  |

| 0x6          | DIV64  | Divide by 64  |

| 0x7          | DIV128 | Divide by 128 |

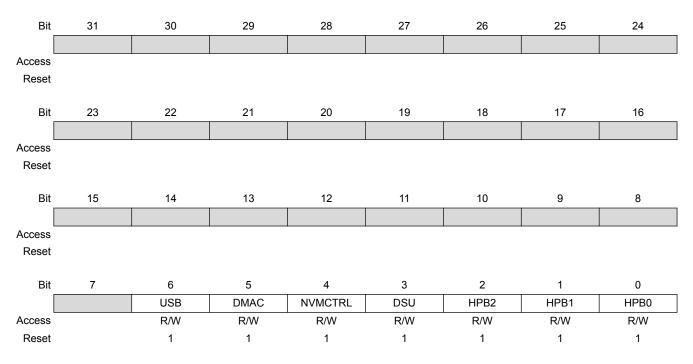

## 16.8.7 AHB Mask

Name:AHBMASKOffset:0x14Reset:0x0000007FProperty:Write-Protected

### Bit 6 – USB: USB AHB Clock Mask

| Value | Description                           |

|-------|---------------------------------------|

| 0     | The AHB clock for the USB is stopped. |

| 1     | The AHB clock for the USB is enabled. |

## Bit 5 – DMAC: DMAC AHB Clock Mask

| Value | Description                            |

|-------|----------------------------------------|

| 0     | The AHB clock for the DMAC is stopped. |

| 1     | The AHB clock for the DMAC is enabled. |

The periodic events can also wake up the CPU through the interrupt function of the Event System. In this case, the event must be enabled and connected to an event channel with its interrupt enabled. See *Event System* for more information.

#### **Related Links**

EVSYS - Event System

## 19.6.8 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

When executing an operation that requires synchronization, the Synchronization Busy bit in the Status register (STATUS.SYNCBUSY) will be set immediately, and cleared when synchronization is complete. The Synchronization Ready interrupt can be used to signal when synchronization is complete. This can be accessed via the Synchronization Ready Interrupt Flag in the Interrupt Flag Status and Clear register (INTFLAG.SYNCRDY). If an operation that requires synchronization is executed while STATUS.SYNCBUSY is one, the bus will be stalled. All operations will complete successfully, but the CPU will be stalled and interrupts will be pending as long as the bus is stalled.

The following bits are synchronized when written:

- Software Reset bit in the Control register (CTRL.SWRST)

- Enable bit in the Control register (CTRL.ENABLE)

The following registers are synchronized when written:

- Counter Value register (COUNT)

- Clock Value register (CLOCK)

- Counter Period register (PER)

- Compare n Value registers (COMPn)

- Alarm n Value registers (ALARMn)

- Frequency Correction register (FREQCORR)

- Alarm n Mask register (MASKn)

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

The following registers are synchronized when read:

- The Counter Value register (COUNT)

- The Clock Value register (CLOCK)

Required read-synchronization is denoted by the "Read-Synchronized" property in the register description.

#### **Related Links**

Register Synchronization

## 19.6.9 Additional Features

#### 19.6.9.1 Periodic Events

The RTC prescaler can generate events at periodic intervals, allowing flexible system tick creation. Any of the upper eight bits of the prescaler (bits 2 to 9) can be the source of an event. When one of the eight Periodic Event Output bits in the Event Control register (EVCTRL.PEREO[n=0..7]) is '1', an event is generated on the 0-to-1 transition of the related bit in the prescaler, resulting in a periodic event frequency of:

This bit will always read as zero.

## Bit 16 – PMUXEN: Peripheral Multiplexer Enable

This bit determines the new value written to PINCFGy.PMUXEN for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits, when the WRCONFIG.WRPINCFG bit is set.

This bit will always read as zero.

### Bits 15:0 – PINMASK[15:0]: Pin Mask for Multiple Pin Configuration

These bits select the pins to be configured within the half-word group selected by the WRCONFIG.HWSEL bit.

These bits will always read as zero.

| Value | Description                                                                                   |

|-------|-----------------------------------------------------------------------------------------------|

| 0     | The configuration of the corresponding I/O pin in the half-word group will be left unchanged. |

| 1     | The configuration of the corresponding I/O pin in the half-word PORT group will be updated.   |

### 23.8.12 Peripheral Multiplexing n

There are up to 16 Peripheral Multiplexing registers in each group, one for every set of two subsequent I/O lines. The n denotes the number of the set of I/O lines.

Name: PMUXn Offset: 0x30 + n\*0x01 [n=0..15] Reset: 0x00 Property: PAC Write-Protection

| Bit    | 7          | 6   | 5   | 4          | 3   | 2   | 1   | 0   |

|--------|------------|-----|-----|------------|-----|-----|-----|-----|

|        | PMUXO[3:0] |     |     | PMUXE[3:0] |     |     |     |     |

| Access | R/W        | R/W | R/W | R/W        | R/W | R/W | R/W | R/W |

| Reset  | 0          | 0   | 0   | 0          | 0   | 0   | 0   | 0   |

## Bits 7:4 – PMUXO[3:0]: Peripheral Multiplexing for Odd-Numbered Pin

These bits select the peripheral function for odd-numbered pins  $(2^n + 1)$  of a PORT group, if the corresponding PINCFGy.PMUXEN bit is '1'.

Not all possible values for this selection may be valid. For more details, refer to the *I/O Multiplexing and Considerations*.

| PMUXO[3:0] | Name | Description                      |  |  |  |

|------------|------|----------------------------------|--|--|--|

| 0x0        | А    | Peripheral function A selected   |  |  |  |

| 0x1        | В    | Peripheral function B selected   |  |  |  |

| 0x2        | С    | Peripheral function C selected   |  |  |  |

| 0x3        | D    | Peripheral function D selected   |  |  |  |

| 0x4        | E    | E Peripheral function E selected |  |  |  |

| 0x5        | F    | Peripheral function F selected   |  |  |  |

| 0x6        | G    | Peripheral function G selected   |  |  |  |

| 0x7        | Н    | Peripheral function H selected   |  |  |  |

## 26. SERCOM USART – SERCOM Universal Synchronous and Asynchronous Receiver and Transmitter

## 26.1 Overview

The Universal Synchronous and Asynchronous Receiver and Transmitter (USART) is one of the available modes in the Serial Communication Interface (SERCOM).

The USART uses the SERCOM transmitter and receiver, see Block Diagram. Labels in uppercase letters are synchronous to CLK\_SERCOMx\_APB and accessible for CPU. Labels in lowercase letters can be programmed to run on the internal generic clock or an external clock.

The transmitter consists of a single write buffer, a shift register, and control logic for different frame formats. The write buffer support data transmission without any delay between frames. The receiver consists of a two-level receive buffer and a shift register. Status information of the received data is available for error checking. Data and clock recovery units ensure robust synchronization and noise filtering during asynchronous data reception.

#### **Related Links**

SERCOM - Serial Communication Interface

## 26.2 USART Features

- Full-duplex operation

- Asynchronous (with clock reconstruction) or synchronous operation

- Internal or external clock source for asynchronous and synchronous operation

- Baud-rate generator

- Supports serial frames with 5, 6, 7, 8 or 9 data bits and 1 or 2 stop bits

- Odd or even parity generation and parity check

- Selectable LSB- or MSB-first data transfer

- Buffer overflow and frame error detection

- Noise filtering, including false start-bit detection and digital low-pass filter

- Collision detection

- Can operate in all sleep modes

- Operation at speeds up to half the system clock for internally generated clocks

- Operation at speeds up to the system clock for externally generated clocks

- RTS and CTS flow control

- IrDA modulation and demodulation up to 115.2kbps

- Start-of-frame detection

- Can work with DMA

#### **Related Links**

Features

| Value | Description                                                       |

|-------|-------------------------------------------------------------------|

| 0x0   | Standard-mode (Sm) up to 100 kHz and Fast-mode (Fm) up to 400 kHz |

| 0x1   | Fast-mode Plus (Fm+) up to 1 MHz                                  |

| 0x2   | High-speed mode (Hs-mode) up to 3.4 MHz                           |

| 0x3   | Reserved                                                          |

## Bit 23 – SEXTTOEN: Slave SCL Low Extend Time-Out

This bit enables the slave SCL low extend time-out. If SCL is cumulatively held low for greater than 25ms from the initial START to a STOP, the slave will release its clock hold if enabled and reset the internal state machine. Any interrupt flags set at the time of time-out will remain set. If the address was recognized, PREC will be set when a STOP is received.

This bit is not synchronized.

| Value | Description       |

|-------|-------------------|

| 0     | Time-out disabled |

| 1     | Time-out enabled  |

## Bits 21:20 – SDAHOLD[1:0]: SDA Hold Time

These bits define the SDA hold time with respect to the negative edge of SCL.

These bits are not synchronized.

| Value | Name | Description         |

|-------|------|---------------------|

| 0x0   | DIS  | Disabled            |

| 0x1   | 75   | 50-100ns hold time  |

| 0x2   | 450  | 300-600ns hold time |

| 0x3   | 600  | 400-800ns hold time |

## Bit 16 – PINOUT: Pin Usage

This bit sets the pin usage to either two- or four-wire operation:

This bit is not synchronized.

| Value | Description               |

|-------|---------------------------|

| 0     | 4-wire operation disabled |

| 1     | 4-wire operation enabled  |

## Bit 7 – RUNSTDBY: Run in Standby

This bit defines the functionality in standby sleep mode.

This bit is not synchronized.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | Disabled – All reception is dropped. |

| 1     | Wake on address match, if enabled.   |

## Bits 4:2 – MODE[2:0]: Operating Mode

These bits must be written to 0x04 to select the I<sup>2</sup>C slave serial communication interface of the SERCOM.

These bits are not synchronized.

## Bit 1 – ENABLE: Enable

Due to synchronization, there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRL.ENABLE will read back immediately and the Enable Synchronization

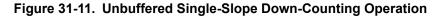

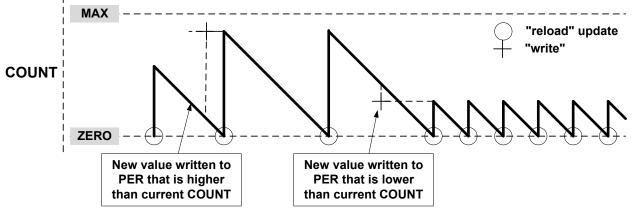

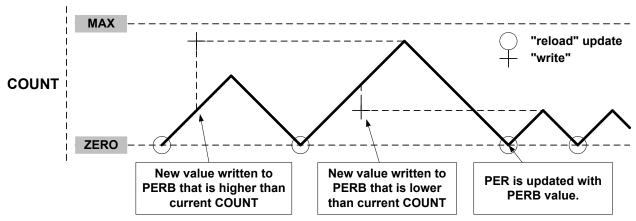

A counter wraparound can occur in any operation mode when up-counting without buffering, see Figure 31-10. COUNT and TOP are continuously compared, so when a new value that is lower than the current COUNT is written to TOP, COUNT will wrap before a compare match.

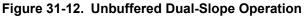

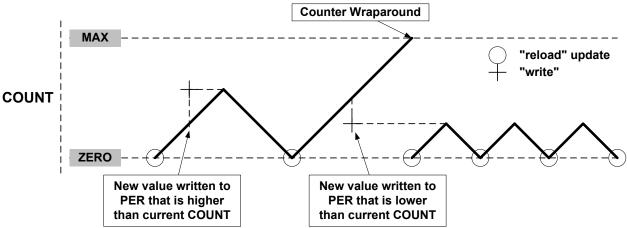

When double buffering is used, the buffer can be written at any time and the counter will still maintain correct operation. The period register is always updated on the update condition, as shown in Figure 31-13. This prevents wraparound and the generation of odd waveforms.

Figure 31-13. Changing the Period Using Buffering

## Property: PAC Write-Protection

| Bit    | 7 | 6 | 5   | 4          | 3   | 2   | 1    | 0       |

|--------|---|---|-----|------------|-----|-----|------|---------|

|        |   |   |     | PTYPE[2:0] |     | BK  | PTOK | EN[1:0] |

| Access |   |   | R/W | R/W        | R/W | R/W | R/W  | R/W     |

| Reset  |   |   | 0   | 0          | 0   | 0   | 0    | 0       |

## Bits 5:3 – PTYPE[2:0]: Type of the Pipe

These bits contains the pipe type.

| PTYPE[2:0] | Description                                 |

|------------|---------------------------------------------|

| 0x0        | Pipe is disabled                            |

| 0x1        | Pipe is enabled and configured as CONTROL   |

| 0x2        | Pipe is enabled and configured as ISO       |

| 0x3        | Pipe is enabled and configured as BULK      |

| 0x4        | Pipe is enabled and configured as INTERRUPT |

| 0x5        | Pipe is enabled and configured as EXTENDED  |

| 0x06-0x7   | Reserved                                    |

These bits are cleared upon sending a USB reset.

#### Bit 2 – BK: Pipe Bank

This bit selects the number of banks for the pipe.

For control endpoints writing a zero to this bit is required as only Bank0 is used for Setup/In/Out transactions.

This bit is cleared when a USB reset is sent.

| BK <mark>(1)</mark> | Description          |  |

|---------------------|----------------------|--|

| 0x0                 | Single-bank endpoint |  |

| 0x1                 | Dual-bank endpoint   |  |

1. Bank field is ignored when PTYPE is configured as EXTENDED.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | A single bank is used for the pipe. |

| 1     | A dual bank is used for the pipe.   |

## Bits 1:0 – PTOKEN[1:0]: Pipe Token

These bits contains the pipe token.

| PTOKEN[1:0] 1) | Description |  |

|----------------|-------------|--|

| 0x0            | SETUP(2)    |  |

| 0x1            | IN          |  |

Writing this bit to zero will have no effect.

| Value | Description                                                                                                                                                                                                                                      |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | No flush action.                                                                                                                                                                                                                                 |

| 1     | "Writing a '1' to this bit will flush the ADC pipeline. A flush will restart the ADC clock on the next peripheral clock edge, and all conversions in progress will be aborted and lost. This bit will be cleared after the ADC has been flushed. |

|       | After the flush, the ADC will resume where it left off; i.e., if a conversion was pending, the ADC will start a new conversion.                                                                                                                  |

## 33.8.8 Input Control

Offset: 0x10

Reset: 0x0000000

Property: Write-Protected, Write-Synchronized

| Bit    | 31  | 30      | 29        | 28          | 27          | 26     | 25       | 24  |

|--------|-----|---------|-----------|-------------|-------------|--------|----------|-----|

|        |     |         |           |             | GAIN[3:0]   |        |          |     |

| Access |     |         |           |             | R/W         | R/W    | R/W      | R/W |

| Reset  |     |         |           |             | 0           | 0      | 0        | 0   |

|        |     |         |           |             |             |        |          |     |

| Bit    | 23  | 22      | 21        | 20          | 19          | 18     | 17       | 16  |

|        |     | INPUTOF | FSET[3:0] |             |             | INPUTS | CAN[3:0] |     |

| Access | R/W | R/W     | R/W       | R/W         | R/W         | R/W    | R/W      | R/W |

| Reset  | 0   | 0       | 0         | 0           | 0           | 0      | 0        | 0   |

|        |     |         |           |             |             |        |          |     |

| Bit    | 15  | 14      | 13        | 12          | 11          | 10     | 9        | 8   |

|        |     |         |           |             | MUXNEG[4:0] |        |          |     |

| Access |     |         | •         | R/W         | R/W         | R/W    | R/W      | R/W |

| Reset  |     |         |           | 0           | 0           | 0      | 0        | 0   |

|        |     |         |           |             |             |        |          |     |

| Bit    | 7   | 6       | 5         | 4           | 3           | 2      | 1        | 0   |

|        |     |         |           | MUXPOS[4:0] |             |        |          |     |

| Access |     |         |           | R/W         | R/W         | R/W    | R/W      | R/W |

| Reset  |     |         |           | 0           | 0           | 0      | 0        | 0   |

## Bits 27:24 – GAIN[3:0]: Gain Factor Selection

These bits set the gain factor of the ADC gain stage.

| GAIN[3:0] | Name | Description |

|-----------|------|-------------|

| 0x0       | 1X   | 1x          |

| 0x1       | 2X   | 2x          |

| 0x2       | 4X   | 4x          |

| 0x3       | 8X   | 8x          |

| 0x4       | 16X  | 16x         |

## Bit 19 – HYST: Hysteresis Enable

This bit indicates the hysteresis mode of comparator n. Hysteresis is available only for continuous mode (COMPCTRLn. SINGLE=0). COMPCTRLn.HYST can be written only while COMPCTRLn.ENABLE is zero.

This bit is not synchronized.

These bits are not synchronized.

| Value | Name                    |

|-------|-------------------------|

| 0     | Hysteresis is disabled. |

| 1     | Hysteresis is enabled.  |

### Bits 17:16 – OUT[1:0]: Output

These bits configure the output selection for comparator n. COMPCTRLn.OUT can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value | Name  | Description                                                                           |

|-------|-------|---------------------------------------------------------------------------------------|

| 0x0   | OFF   | The output of COMPn is not routed to the COMPn I/O port                               |

| 0x1   | ASYNC | The asynchronous output of COMPn is routed to the COMPn I/O port                      |

| 0x2   | SYNC  | The synchronous output (including filtering) of COMPn is routed to the COMPn I/O port |

| 0x3   | N/A   | Reserved                                                                              |

## Bit 15 – SWAP: Swap Inputs and Invert

This bit swaps the positive and negative inputs to COMPn and inverts the output. This function can be used for offset cancellation. COMPCTRLn.SWAP can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | The output of MUXPOS connects to the positive input, and the output of MUXNEG connects |

|       | to the negative input.                                                                 |

| 1     | The output of MUXNEG connects to the positive input, and the output of MUXPOS connects |

|       | to the negative input.                                                                 |

## Bits 13:12 – MUXPOS[1:0]: Positive Input Mux Selection

These bits select which input will be connected to the positive input of comparator n. COMPCTRLn.MUXPOS can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value | Name | Description |

|-------|------|-------------|

| 0x0   | PIN0 | I/O pin 0   |

| 0x1   | PIN1 | I/O pin 1   |

| 0x2   | PIN2 | I/O pin 2   |

| 0x3   | PIN3 | I/O pin 3   |

## Bits 10:8 – MUXNEG[2:0]: Negative Input Mux Selection

These bits select which input will be connected to the negative input of comparator n. COMPCTRLn.MUXNEG can only be written while COMPCTRLn.ENABLE is zero.

## **39.5** Clocks and Crystal Oscillators

The SAM D21 can be run from internal or external clock sources, or a mix of internal and external sources. An example of usage will be to use the internal 8MHz oscillator as source for the system clock, and an external 32.768kHz watch crystal as clock source for the Real-Time counter (RTC).

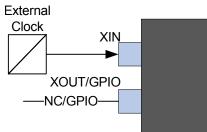

## 39.5.1 External Clock Source

## Figure 39-5. External Clock Source Example Schematic

## Table 39-4. External Clock Source Connections

| Signal Name | Recommended Pin Connection                        | Description                        |

|-------------|---------------------------------------------------|------------------------------------|

| XIN         | XIN is used as input for an external clock signal | Input for inverting oscillator pin |

| XOUT/GPIO   | Can be left unconnected or used as normal GPIO    |                                    |

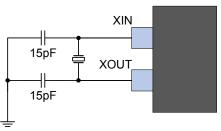

## 39.5.2 Crystal Oscillator

### Figure 39-6. Crystal Oscillator Example Schematic

The crystal should be located as close to the device as possible. Long signal lines may cause too high load to operate the crystal, and cause crosstalk to other parts of the system.

### Table 39-5. Crystal Oscillator Checklist

| Signal Name | Recommended Pin Connection            | Description                           |

|-------------|---------------------------------------|---------------------------------------|

| XIN         | Load capacitor 15pF <sup>(1)(2)</sup> | External crystal between 0.4 to 30MHz |

| XOUT        | Load capacitor 15pF <sup>(1)(2)</sup> |                                       |

- 1. These values are given only as typical example.

- 2. Decoupling capacitor should be placed close to the device for each supply pin pair in the signal group.

## 39.5.3 External Real Time Oscillator

The low frequency crystal oscillator is optimized for use with a 32.768kHz watch crystal. When selecting crystals, load capacitance and crystal's Equivalent Series Resistance (ESR) must be taken into consideration. Both values are specified by the crystal vendor.

| are already active, the channel number of the new channel enabled must be greater than the other channel numbers.                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 – If data is written to CRCDATAIN in two consecutive instructions, the<br>CRC computation may be incorrect.<br>Errata reference: 13507<br>Fix/Workaround:                                                                                                                                                                                                                                                                                                                                          |

| Add a NOP instruction between each write to CRCDATAIN register.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <ul> <li>1 – When the EIC is configured to generate an interrupt on a low level<br/>or rising edge or both edges (CONFIGn.SENSEx) with the filter enabled<br/>(CONFIGn.FILTENx), a spurious flag might appear for the dedicated pin<br/>on the INTFLAG.EXTINT[x] register as soon as the EIC is enabled using<br/>CTRLA ENABLE bit.</li> <li>Errata reference: 15341</li> <li>Fix/Workaround:</li> <li>Clear the INTFLAG bit once the EIC enabled and before enabling the<br/>interrupts.</li> </ul> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1 – Default value of MANW in NVM.CTRLB is 0.<br>This can lead to spurious writes to the NVM if a data write is done<br>through a pointer with a wrong address corresponding to NVM area.<br>Errata reference: 13134<br>Fix/Workaround:<br>Set MANW in the NVM.CTRLB to 1 at startup                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <ul> <li>1 – I2S RX serializer in LSBIT mode (SERCTRL.BITREV set) only works when the slot size is 32 bits.</li> <li>Errata reference: 13320</li> <li>Fix/Workaround:</li> <li>In SERCTRL.SERMODE RX, SERCTRL.BITREV LSBIT must be used with CLKCTRL.SLOTSIZE 32.</li> </ul>                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1 – In USART autobaud mode, missing stop bits are not recognized as<br>inconsistent sync (ISF) or framing (FERR) errors.<br>Errata reference: 13852<br>Fix/Workaround:<br>None                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1 – FCTRLX.CAPTURE[CAPTMARK] does not work as described in the<br>datasheet. CAPTMARK cannot be used to identify captured values<br>triggered by fault inputs source A or B on the same channel.<br>Errata reference: 13316<br>Fix/Workaround:<br>Use two different channels to timestamp FaultA and FaultB.                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Abbreviation       | Description                                                            |

|--------------------|------------------------------------------------------------------------|

| ULP                | Ultra-low power                                                        |

| USART              | Universal Synchronous and Asynchronous Serial Receiver and Transmitter |

| USB                | Universal Serial Bus                                                   |

| V <sub>DD</sub>    | Common voltage to be applied to VDDIO, VDDIN and VDDANA                |

| V <sub>DDIN</sub>  | Digital supply voltage                                                 |

| V <sub>DDIO</sub>  | Digital supply voltage                                                 |

| V <sub>DDANA</sub> | Analog supply voltage                                                  |

| VREF               | Voltage reference                                                      |

| WDT                | Watchdog Timer                                                         |

| XOSC               | Crystal Oscillator                                                     |

## 43. Datasheet Revision History

Please note that the referring page numbers in this section are referred to this document. The referring revision in this section are referring to the document revision.

## 43.1 Rev. A – 01/2017

| General                                                  | <ul> <li>Template: Updated from Atmel to Microchip template.</li> <li>Document number: Changed from the Atmel 42181 to Microchip xxxxx.</li> <li>Document revision letter reset to A.</li> <li>ISBN number added.</li> </ul>                                                                                                    |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrical<br>Characteristics                            | <ul> <li>Die Revision F final characterization added.</li> <li>Power Consumption: Added Standby typical numbers for Device Variant C /<br/>Die Revision F.</li> <li>Fractional Digital Phase Locked Loop (FDPLL96M) Characteristics: Added<br/>characterization data for Device Variant C / Die Revision F.</li> </ul>          |

| Errata                                                   | <ul> <li>New errata added:</li> <li>B</li> <li>Device Variant A: Errata reverence 15625, 15683, 15753 added.</li> <li>Device Variant B: Errata reverence 15625, 15683, 15753 added.</li> <li>Device Variant C: Errata reverence 15625, 15683, 15753 added.</li> </ul>                                                           |

| Appendix A.<br>Electrical<br>Characteristics at<br>125°C | <ul> <li>Die Revision F final characterization is preliminary.</li> <li>Power Consumption: Added Standby typical numbers for Device Variant C /<br/>Die Revision F.</li> <li>Fractional Digital Phase Locked Loop (FDPLL96M) Characteristics: Added<br/>characterization data for Device Variant C / Die Revision F.</li> </ul> |

## 43.2 Rev. O – 12/2016

| General                                               | Introduced Device Variant C.                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrical<br>Characteristics                         | <ul> <li>Die Revision F characterization is preliminary.</li> <li>Power Consumption: Added Standby typical numbers for Device Variant<br/>C / Die Revision F.</li> <li>Fractional Digital Phase Locked Loop (FDPLL96M) Characteristics:<br/>Added characterization data for Device Variant C / Die Revision F.</li> </ul> |

| Appendix A. Electrical<br>Characteristics at<br>125°C | <ul> <li>Die Revision F characterization is preliminary.</li> <li>Power Consumption: Added Standby typical numbers for Device Variant<br/>C / Die Revision F.</li> <li>Fractional Digital Phase Locked Loop (FDPLL96M) Characteristics:<br/>Added characterization data for Device Variant C / Die Revision F.</li> </ul> |