#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 48MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 52                                                                        |

| Program Memory Size        | 256КВ (256К х 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 32K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                              |

| Data Converters            | A/D 20x12b; D/A 1x10b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 64-QFN (9x9)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd21j18a-mu |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 32-bit ARM-Based Microcontrollers

| XOSC.RUNSTDBY | XOSC.ONDEMAND | XOSC.ENABLE | Sleep Behavior                                                                                   |

|---------------|---------------|-------------|--------------------------------------------------------------------------------------------------|

| -             | -             | 0           | Disabled                                                                                         |

| 0             | 0             | 1           | Always run in IDLE sleep modes. Disabled in STANDBY sleep mode.                                  |

| 0             | 1             | 1           | Only run in IDLE sleep modes if requested<br>by a peripheral. Disabled in STANDBY<br>sleep mode. |

| 1             | 0             | 1           | Always run in IDLE and STANDBY sleep modes.                                                      |

| 1             | 1             | 1           | Only run in IDLE or STANDBY sleep modes if requested by a peripheral.                            |

After a hard reset, or when waking up from a sleep mode where the XOSC was disabled, the XOSC will need a certain amount of time to stabilize on the correct frequency. This start-up time can be configured by changing the Oscillator Start-Up Time bit group (XOSC.STARTUP) in the External Multipurpose Crystal Oscillator Control register. During the start-up time, the oscillator output is masked to ensure that no unstable clock propagates to the digital logic. The External Multipurpose Crystal Oscillator Ready bit in the Power and Clock Status register (PCLKSR.XOSCRDY) is set when the user-selected start-up time is over. An interrupt is generated on a zero-to-one transition on PCLKSR.XOSCRDY if the External Multipurpose Crystal Oscillator Ready bit in the Interrupt Enable Set register (INTENSET.XOSCRDY) is set.

**Note:** Do not enter standby mode when an oscillator is in start-up:

Wait for the OSCxRDY bit in SYSCTRL.PCLKSR register to be set before going into standby mode.

## **Related Links**

GCLK - Generic Clock Controller

# 17.6.3 32kHz External Crystal Oscillator (XOSC32K) Operation

The XOSC32K can operate in two different modes:

- External clock, with an external clock signal connected to XIN32

- Crystal oscillator, with an external 32.768kHz crystal connected between XIN32 and XOUT32

The XOSC32K can be used as a source for generic clock generators, as described in the *GCLK* – *Generic Clock Controller*.

At power-on reset (POR) the XOSC32K is disabled, and the XIN32/XOUT32 pins can be used as General Purpose I/O (GPIO) pins or by other peripherals in the system. When XOSC32K is enabled, the operating mode determines the GPIO usage. When in crystal oscillator mode, XIN32 and XOUT32 are controlled by the SYSCTRL, and GPIO functions are overridden on both pins. When in external clock mode, only the XIN32 pin will be overridden and controlled by the SYSCTRL, while the XOUT32 pin can still be used as a GPIO pin.

The external clock or crystal oscillator is enabled by writing a one to the Enable bit (XOSC32K.ENABLE) in the 32kHz External Crystal Oscillator Control register. To enable the XOSC32K as a crystal oscillator, a one must be written to the XTAL Enable bit (XOSC32K.XTALEN). If XOSC32K.XTALEN is zero, external clock input will be enabled.

The oscillator is disabled by writing a zero to the Enable bit (XOSC32K.ENABLE) in the 32kHz External Crystal Oscillator Control register while keeping the other bits unchanged. Writing to the

© 2017 Microchip Technology Inc.

## Bit 6 – RUNSTDBY: Run in Standby

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | The BOD33 is disabled in standby sleep mode. |

| 1     | The BOD33 is enabled in standby sleep mode.  |

## Bits 4:3 – ACTION[1:0]: BOD33 Action

These bits are used to select the BOD33 action when the supply voltage crosses below the BOD33 threshold.

These bits are loaded from Flash User Row at start-up.

| ACTION[1:0] | Name      | Description                      |

|-------------|-----------|----------------------------------|

| 0x0         | NONE      | No action                        |

| 0x1         | RESET     | The BOD33 generates a reset      |

| 0x2         | INTERRUPT | The BOD33 generates an interrupt |

| 0x3         |           | Reserved                         |

#### Bit 2 – HYST: Hysteresis

This bit indicates whether hysteresis is enabled for the BOD33 threshold voltage:

This bit is loaded from Flash User Row at start-up. Refer to NVM User Row Mapping for more details.

| Value | Description         |

|-------|---------------------|

| 0     | No hysteresis.      |

| 1     | Hysteresis enabled. |

#### Bit 1 – ENABLE: Enable

This bit is loaded from Flash User Row at startup. Refer to NVM User Row Mapping for more details.

| Value | Description        |

|-------|--------------------|

| 0     | BOD33 is disabled. |

| 1     | BOD33 is enabled.  |

#### 17.8.15 Voltage Regulator System (VREG) Control

Name:VREGOffset:0x3CReset:0x0X00Property:Write-Protected

| Bit    | 15      | 14       | 13       | 12 | 11 | 10 | 9 | 8                                            |

|--------|---------|----------|----------|----|----|----|---|----------------------------------------------|

|        |         |          | FORCELDO |    |    |    |   |                                              |

| Access |         |          | R/W      |    |    |    |   |                                              |

| Reset  |         |          | 0        |    |    |    |   |                                              |

|        |         |          |          |    |    |    |   |                                              |

| Bit    | 7       | 6        | 5        | 4  | 3  | 2  | 1 | 0                                            |

|        |         | RUNSTDBY |          |    |    |    |   |                                              |

| Access | <u></u> | R/W      |          |    | •  |    |   | <u>.                                    </u> |

| Reset  |         | 0        |          |    |    |    |   |                                              |

## 19.8.17 Status

|        | Name:<br>Offset:<br>Reset:<br>Property: |    |   |   |   |   |   |   |

|--------|-----------------------------------------|----|---|---|---|---|---|---|

| Bit    | 7                                       | 6  | 5 | 4 | 3 | 2 | 1 | 0 |

|        | SYNCBUS                                 | SY |   |   |   |   |   |   |

| Access | R                                       |    |   |   | • | • | • |   |

Reset 0

#### Bit 7 – SYNCBUSY: Synchronization Busy

This bit is cleared when the synchronization of registers between the clock domains is complete.

This bit is set when the synchronization of registers between clock domains is started.

## 19.8.18 Debug Control

Name: DBGCTRL Offset: 0x0B Reset: 0x00 Property: -

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|--------|---|---|---|---|---|---|---|--------|

|        |   |   |   |   |   |   |   | DBGRUN |

| Access |   | • |   |   |   |   | • | R/W    |

| Reset  |   |   |   |   |   |   |   | 0      |

#### Bit 0 – DBGRUN: Run During Debug

This bit is not reset by a software reset.

Writing a zero to this bit causes the RTC to halt during debug mode.

Writing a one to this bit allows the RTC to continue normal operation during debug mode.

#### 19.8.19 Frequency Correction

Name:FREQCORROffset:0x0CReset:0x00Property:Write-Protected, Write-Synchronized

| Bit    | 7    | 6   | 5   | 4   | 3          | 2   | 1   | 0   |

|--------|------|-----|-----|-----|------------|-----|-----|-----|

|        | SIGN |     |     |     | VALUE[6:0] |     |     |     |

| Access | R/W  | R/W | R/W | R/W | R/W        | R/W | R/W | R/W |

| Reset  | 0    | 0   | 0   | 0   | 0          | 0   | 0   | 0   |

## Bit 7 – SIGN: Correction Sign

# 20. DMAC – Direct Memory Access Controller

# 20.1 Overview

The Direct Memory Access Controller (DMAC) contains both a Direct Memory Access engine and a Cyclic Redundancy Check (CRC) engine. The DMAC can transfer data between memories and peripherals, and thus off-load these tasks from the CPU. It enables high data transfer rates with minimum CPU intervention, and frees up CPU time. With access to all peripherals, the DMAC can handle automatic transfer of data between communication modules.

The DMA part of the DMAC has several DMA channels which all can receive different types of transfer triggers to generate transfer requests from the DMA channels to the arbiter, see also the Block Diagram. The arbiter will grant one DMA channel at a time to act as the active channel. When an active channel has been granted, the fetch engine of the DMAC will fetch a transfer descriptor from the SRAM and store it in the internal memory of the active channel, which will execute the data transmission.

An ongoing data transfer of an active channel can be interrupted by a higher prioritized DMA channel. The DMAC will write back the updated transfer descriptor from the internal memory of the active channel to SRAM, and grant the higher prioritized channel to start transfer as the new active channel. Once a DMA channel is done with its transfer, interrupts and events can be generated optionally.

The DMAC has four bus interfaces:

- The data transfer bus is used for performing the actual DMA transfer.

- The AHB/APB Bridge bus is used when writing and reading the I/O registers of the DMAC.

- The *descriptor fetch bus* is used by the fetch engine to fetch transfer descriptors before data transfer can be started or continued.

- The write-back bus is used to write the transfer descriptor back to SRAM.

All buses are AHB master interfaces but the AHB/APB Bridge bus, which is an APB slave interface.

The CRC engine can be used by software to detect an accidental error in the transferred data and to take corrective action, such as requesting the data to be sent again or simply not using the incorrect data.

# 20.2 Features

- Data transfer from:

- Peripheral to peripheral

- Peripheral to memory

- Memory to peripheral

- Memory to memory

- Transfer trigger sources

- Software

- Events from Event System

- Dedicated requests from peripherals

- SRAM based transfer descriptors

- Single transfer using one descriptor

- Multi-buffer or circular buffer modes by linking multiple descriptors

- Up to 12 channels

An AHB clock (CLK\_DMAC\_AHB) is required to clock the DMAC. This clock must be configured and enabled in the power manager before using the DMAC, and the default state of CLK\_DMAC\_AHB can be found in *Peripheral Clock Masking*.

This bus clock (CLK\_DMAC\_APB) is always synchronous to the module clock (CLK\_DMAC\_AHB), but can be divided by a prescaler and may run even when the module clock is turned off.

#### **Related Links**

Peripheral Clock Masking

#### 20.5.4 DMA

Not applicable.

## 20.5.5 Interrupts

The interrupt request line is connected to the interrupt controller. Using the DMAC interrupt requires the interrupt controller to be configured first.

## **Related Links**

Nested Vector Interrupt Controller

## 20.5.6 Events

The events are connected to the event system.

## **Related Links**

EVSYS - Event System

## 20.5.7 Debug Operation

When the CPU is halted in debug mode the DMAC will halt normal operation. The DMAC can be forced to continue operation during debugging. Refer to DBGCTRL for details.

#### 20.5.8 Register Access Protection

All registers with write-access can be write-protected optionally by the Peripheral Access Controller (PAC), except the following registers:

- Interrupt Pending register (INTPEND)

- Channel ID register (CHID)

- Channel Interrupt Flag Status and Clear register (CHINTFLAG)

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

PAC write-protection does not apply to accesses through an external debugger.

# **Related Links**

PAC - Peripheral Access Controller

#### 20.5.9 Analog Connections

Not applicable.

# 20.6 Functional Description

## 20.6.1 Principle of Operation

The DMAC consists of a DMA module and a CRC module.

## 21.6.6 Interrupts

The EIC has the following interrupt sources:

- External interrupt pins (EXTINTx). See Basic Operation.

- Non-maskable interrupt pin (NMI). See Additional Features.

Each interrupt source has an associated interrupt flag. The interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) is set when an interrupt condition occurs (NMIFLAG for NMI). Each interrupt, except NMI, can be individually enabled by setting the corresponding bit in the Interrupt Enable Set register (INTENSET=1), and disabled by setting the corresponding bit in the Interrupt Enable Clear register (INTENCLR=1).

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the EIC is reset. See the INTFLAG register for details on how to clear interrupt flags. The EIC has one common interrupt request line for all the interrupt sources, and one interrupt request line for the NMI. The user must read the INTFLAG (or NMIFLAG) register to determine which interrupt condition is present.

Note: Interrupts must be globally enabled for interrupt requests to be generated.

**Note:** If an external interrupts (EXTINT) is common on two or more I/O pins, only one will be active (the first one programmed).

## **Related Links**

Multiplexed Signals Processor And Architecture

## 21.6.7 Events

The EIC can generate the following output events:

External event from pin (EXTINTx).

Setting an Event Output Control register (EVCTRL.EXTINTEO) enables the corresponding output event. Clearing this bit disables the corresponding output event. Refer to *Event System* for details on configuring the Event System.

When the condition on pin EXTINTx matches the configuration in the CONFIGn register, the corresponding event is generated, if enabled.

## **Related Links**

EVSYS – Event System

## 21.6.8 Sleep Mode Operation

In sleep modes, an EXTINTx pin can wake up the device if the corresponding condition matches the configuration in CONFIGy register. Writing a one to a Wake-Up Enable bit (WAKEUP.WAKEUPEN[x]) enables the wake-up from pin EXTINTx. Writing a zero to a Wake-Up Enable bit (WAKEUP.WAKEUPEN[x]) disables the wake-up from pin EXTINTx.

Using WAKEUPEN[x]=1 with INTENSET=0 is not recommended.

In sleep modes, an EXTINTx pin can wake up the device if the corresponding condition matches the configuration in CONFIGn register, and the corresponding bit in the Interrupt Enable Set register (INTENSET) is written to '1'. WAKEUP.WAKEUPEN[x]=1 can enable the wake-up from pin EXTINTx.

has control over the output state of the pad, as well as the ability to read the current physical pad state. Refer to *I/O Multiplexing and Considerations* for details.

Device-specific configurations may cause some lines (and the corresponding Pxy pin) not to be implemented.

#### **Related Links**

I/O Multiplexing and Considerations

#### 23.5.2 Power Management

During reset, all PORT lines are configured as inputs with input buffers, output buffers and pull disabled.

The PORT will continue operating in any sleep mode where the selected module source clock is running because the selected module source clock is still running.

## 23.5.3 Clocks

The PORT bus clock (CLK\_PORT\_APB) can be enabled and disabled in the Power Manager, and the default state of CLK\_PORT\_APB can be found in the *Peripheral Clock Masking* section in *PM – Power Manager*.

The PORT is fed by two different clocks: a CPU main clock, which allows the CPU to access the PORT through the low latency CPU local bus (IOBUS); an APB clock, which is a divided clock of the CPU main clock and allows the CPU to access the registers of PORT through the high-speed matrix and the AHB/APB bridge.

The priority of IOBUS accesses is higher than event accesses and APB accesses. The EVSYS and APB will insert wait states in the event of concurrent PORT accesses.

The PORT input synchronizers use the CPU main clock so that the resynchronization delay is minimized with respect to the APB clock.

#### **Related Links**

Peripheral Clock Masking

#### 23.5.4 DMA

Not applicable.

#### 23.5.5 Interrupts

Not applicable.

## 23.5.6 Events

The events of this peripheral are connected to the Event System.

## **Related Links**

EVSYS - Event System

#### 23.5.7 Debug Operation

When the CPU is halted in debug mode, this peripheral will continue normal operation. If the peripheral is configured to require periodical service by the CPU through interrupts or similar, improper operation or data loss may result during debugging. This peripheral can be forced to halt operation during debugging - refer to the Debug Control (DBGCTRL) register for details.

#### 23.5.8 Register Access Protection

All registers with write-access can be optionally write-protected by the Peripheral Access Controller (PAC).

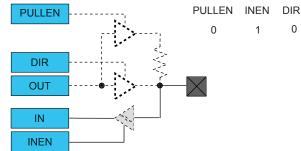

## 23.6.3.1 Pin Configurations Summary Table 23-2. Pin Configurations Summary

| DIR | INEN | PULLEN | OUT | Configuration                             |

|-----|------|--------|-----|-------------------------------------------|

| 0   | 0    | 0      | Х   | Reset or analog I/O: all digital disabled |

| 0   | 0    | 1      | 0   | Pull-down; input disabled                 |

| 0   | 0    | 1      | 1   | Pull-up; input disabled                   |

| 0   | 1    | 0      | Х   | Input                                     |

| 0   | 1    | 1      | 0   | Input with pull-down                      |

| 0   | 1    | 1      | 1   | Input with pull-up                        |

| 1   | 0    | Х      | Х   | Output; input disabled                    |

| 1   | 1    | Х      | Х   | Output; input enabled                     |

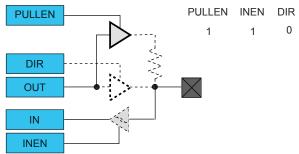

## 23.6.3.2 Input Configuration

# Figure 23-4. I/O configuration - Standard Input

## Figure 23-5. I/O Configuration - Input with Pull

**Note:** When pull is enabled, the pull value is defined by the OUT value.

## 23.6.3.3 Totem-Pole Output

When configured for totem-pole (push-pull) output, the pin is driven low or high according to the corresponding bit setting in the OUT register. In this configuration there is no current limitation for sink or source other than what the pin is capable of. If the pin is configured for input, the pin will float if no external pull is connected.

Note: Enabling the output driver will automatically disable pull.

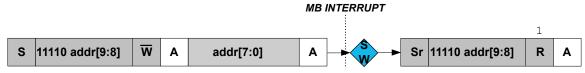

#### Figure 28-8. 10-bit Address Transmission for a Read Transaction

This implies the following procedure for a 10-bit read operation:

- 1. Write the 10-bit address to ADDR.ADDR[10:1]. ADDR.TENBITEN must be '1', the direction bit (ADDR.ADDR[0]) must be '0' (can be written simultaneously with ADDR).

- 2. Once the Master on Bus interrupt is asserted, Write ADDR[7:0] register to '11110 address[9:8] 1'. ADDR.TENBITEN must be cleared (can be written simultaneously with ADDR).

- 3. Proceed to transmit data.

## 28.6.2.5 I<sup>2</sup>C Slave Operation

The I<sup>2</sup>C slave is byte-oriented and interrupt-based. The number of interrupts generated is kept at a minimum by automatic handling of most events. The software driver complexity and code size are reduced by auto-triggering of operations, and a special smart mode, which can be enabled by the Smart Mode Enable bit in the Control A register (CTRLA.SMEN).

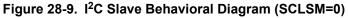

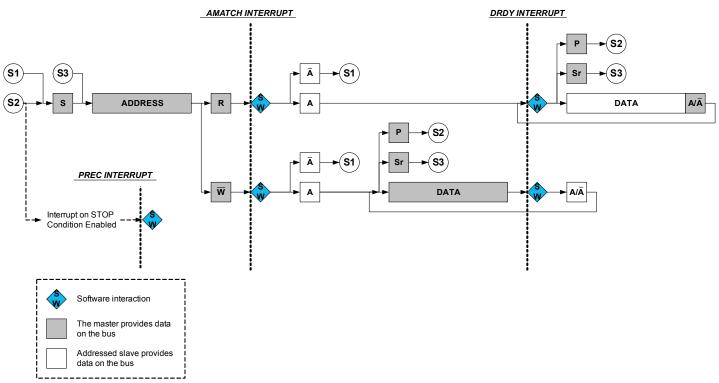

The I<sup>2</sup>C slave has two interrupt strategies.

When SCL Stretch Mode bit (CTRLA.SCLSM) is '0', SCL is stretched before or after the acknowledge bit. In this mode, the I<sup>2</sup>C slave operates according to I<sup>2</sup>C Slave Behavioral Diagram (SCLSM=0). The circles labelled "Sn" (S1, S2..) indicate the nodes the bus logic can jump to, based on software or hardware interaction.

This diagram is used as reference for the description of the I<sup>2</sup>C slave operation throughout the document.

In the second strategy (CTRLA.SCLSM=1), interrupts only occur after the ACK bit is sent as shown in Slave Behavioral Diagram (SCLSM=1). This strategy can be used when it is not necessary to check

DATA before acknowledging. For master reads, an address and data interrupt will be issued simultaneously after the address acknowledge. However, for master writes, the first data interrupt will be seen after the first data byte has been received by the slave and the acknowledge bit has been sent to the master.

**Note:** For I<sup>2</sup>C High-speed mode (*Hs*), SCLSM=1 is required.

## Receiving Address Packets (SCLSM=0)

When CTRLA.SCLSM=0, the I2C slave stretches the SCL line according to Figure 28-9. When the I<sup>2</sup>C slave is properly configured, it will wait for a start condition.

When a start condition is detected, the successive address packet will be received and checked by the address match logic. If the received address is not a match, the packet will be rejected, and the I<sup>2</sup>C slave will wait for a new start condition. If the received address is a match, the Address Match bit in the Interrupt Flag register (INTFLAG.AMATCH) will be set.

SCL will be stretched until the I<sup>2</sup>C slave clears INTFLAG.AMATCH. As the I<sup>2</sup>C slave holds the clock by forcing SCL low, the software has unlimited time to respond.

The direction of a transaction is determined by reading the Read / Write Direction bit in the Status register (STATUS.DIR). This bit will be updated only when a valid address packet is received.

If the Transmit Collision bit in the Status register (STATUS.COLL) is set, this indicates that the last packet addressed to the I<sup>2</sup>C slave had a packet collision. A collision causes the SDA and SCL lines to be released without any notification to software. Therefore, the next AMATCH interrupt is the first indication of the previous packet's collision. Collisions are intended to follow the SMBus Address Resolution Protocol (ARP).

After the address packet has been received from the I<sup>2</sup>C master, one of two cases will arise based on transfer direction.

## Case 1: Address packet accepted – Read flag set

The STATUS.DIR bit is '1', indicating an I<sup>2</sup>C master read operation. The SCL line is forced low, stretching the bus clock. If an ACK is sent, I<sup>2</sup>C slave hardware will set the Data Ready bit in the Interrupt Flag

© 2017 Microchip Technology Inc.

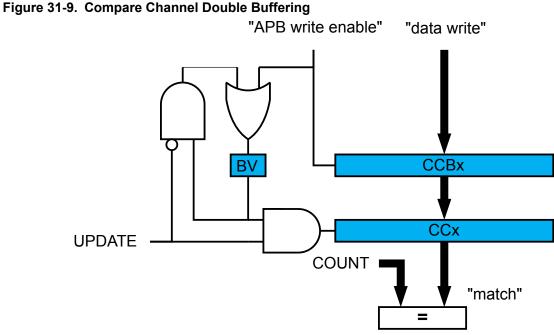

Both the registers (PATT/WAVE/PER/CCx) and corresponding buffer registers (PATTB/WAVEBV/PERB/ CCBx) are available in the I/O register map, and the double buffering feature is not mandatory. The double buffering is disabled by writing a '1' to CTRLSET.LUPD.

**Note:** In NFRQ, MFRQ or PWM down-counting counter mode (CTRLBSET.DIR=1), when double buffering is enabled (CTRLBCLR.LUPD=1), PERB register is continuously copied into the PER independently of update conditions.

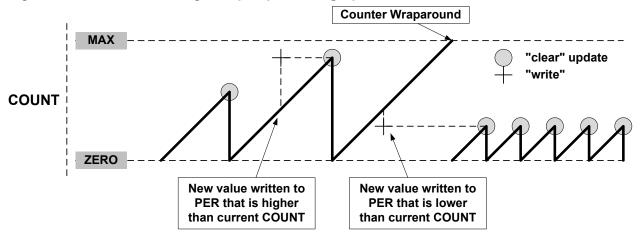

# Changing the Period

The counter period can be changed by writing a new Top value to the Period register (PER or CC0, depending on the waveform generation mode), any period update on registers (PER or CCx) is effective after the synchronization delay, whatever double buffering enabling is.

| Figure 31-10.  | Unbuffered Sin | ale-Slope Up-C | ounting Operation |

|----------------|----------------|----------------|-------------------|

| 1 19410 01 101 |                | gio ciopo op c | ounding operation |

## 32.5.6 Events

Not applicable.

## 32.5.7 Debug Operation

When the CPU is halted in debug mode the USB peripheral continues normal operation. If the USB peripheral is configured in a way that requires it to be periodically serviced by the CPU through interrupts or similar, improper operation or data loss may result during debugging.

#### 32.5.8 Register Access Protection

Registers with write-access can be optionally write-protected by the Peripheral Access Controller (PAC), except the following:

- Device Interrupt Flag (INTFLAG) register

- Endpoint Interrupt Flag (EPINTFLAG) register

- Host Interrupt Flag (INTFLAG) register

- Pipe Interrupt Flag (PINTFLAG) register

**Note:** Optional write-protection is indicated by the "PAC Write-Protection" property in the register description.

When the CPU is halted in debug mode, all write-protection is automatically disabled. Write-protection does not apply for accesses through an external debugger.

## 32.5.9 Analog Connections

Not applicable.

## 32.5.10 Calibration

The output drivers for the DP/DM USB line interface can be fine tuned with calibration values from production tests. The calibration values must be loaded from the NVM Software Calibration Area into the USB Pad Calibration register (PADCAL) by software, before enabling the USB, to achieve the specified accuracy. Refer to *NVM Software Calibration Area Mapping* for further details.

For details on Pad Calibration, refer to Pad Calibration (PADCAL) register.

#### **Related Links**

NVM Software Calibration Area Mapping

# 32.6 Functional Description

## 32.6.1 USB General Operation

#### 32.6.1.1 Initialization

After a hardware reset, the USB is disabled. The user should first enable the USB (CTRLA.ENABLE) in either device mode or host mode (CTRLA.MODE).

#### 32.6.3 Host Operations

This section gives an overview of the USB module Host operation during normal transactions. For more details on general USB and USB protocol, refer to Universal Serial Bus Specification revision 2.1.

#### 32.6.3.1 Device Detection and Disconnection

Prior to device detection the software must set the VBUS is OK bit in CTRLB (CTRLB.VBUSOK) register when the VBUS is available. This notifies the USB host that USB operations can be started. When the bit CTRLB.VBUSOK is zero and even if the USB HOST is configured and enabled, host operation is halted. Setting the bit CTRLB.VBUSOK will allow host operation when the USB is configured.

The Device detection is managed by the software using the Line State field in the Host Status (STATUS.LINESTATE) register. The device connection is detected by the host controller when DP or DM is pulled high, depending of the speed of the device.

The device disconnection is detected by the host controller when both DP and DM are pulled down using the STATUS.LINESTATE registers.

The Device Connection Interrupt bit in INTFLAG (INTFLAG.DCONN) is set if a device connection is detected.

The Device Disconnection Interrupt bit in INTFLAG (INTFLAG.DDISC) is set if a device disconnection is detected.

#### 32.6.3.2 Host Terminology

In host mode, the term pipe is used instead of endpoint. A host pipe corresponds to a device endpoint, refer to "Universal Serial Bus Specification revision 2.1." for more information.

#### 32.6.3.3 USB Reset

The USB sends a USB reset signal when the user writes a one to the USB Reset bit in CTRLB (CTRLB.BUSRESET). When the USB reset has been sent, the USB Reset Sent Interrupt bit in the INTFLAG (INTFLAG.RST) is set and all pipes will be disabled.

If the bus was previously in a suspended state (Start of Frame Generation Enable bit in CTRLB (CTRLB.SOFE) is zero) the USB will switch it to the Resume state, causing the bus to asynchronously set the Host Wakeup Interrupt flag (INTFLAG.WAKEUP). The CTRLB.SOFE bit will be set in order to generate SOFs immediately after the USB reset.

During USB reset the following registers are cleared:

- All Host Pipe Configuration register (PCFG)

- Host Frame Number register (FNUM)

- Interval for the Bulk-Out/Ping transaction register (BINTERVAL)

- Host Start-of-Frame Control register (HSOFC)

- Pipe Interrupt Enable Clear/Set register (PINTENCLR/SET)

- Pipe Interrupt Flag register (PINTFLAG)

- Pipe Freeze bit in Pipe Status register (PSTATUS.FREEZE)

After the reset the user should check the Speed Status field in the Status register (STATUS.SPEED) to find out the current speed according to the capability of the peripheral.

#### 32.6.3.4 Pipe Configuration

Pipe data can be placed anywhere in the RAM. The USB controller accesses these pipes directly through the AHB master (built-in DMA) with the help of the pipe descriptors. The base address of the pipe descriptors needs to be written in the Descriptor Address register (DESCADD) by the user. Refer also to Pipe Descriptor Structure.

| Offset<br>0x n0 | Name        | Bit Pos. |                 |                        |           |         |                          |           |           |        |  |  |

|-----------------|-------------|----------|-----------------|------------------------|-----------|---------|--------------------------|-----------|-----------|--------|--|--|

| +0x10<br>+index |             |          |                 |                        |           |         |                          |           |           |        |  |  |

| 0x00            |             | 7:0      |                 |                        |           | ADD     | [7:0]                    | I         |           |        |  |  |

| 0x01            | 4555        | 15:8     |                 |                        |           | ADD     | [15:8]                   |           |           |        |  |  |

| 0x02            | ADDR -      | 23:16    |                 | ADD[23:16]             |           |         |                          |           |           |        |  |  |

| 0x03            |             | 31:24    | ADD[31:24]      |                        |           |         |                          |           |           |        |  |  |

| 0x04            |             | 7:0      | BYTE_COUNT[7:0] |                        |           |         |                          |           |           |        |  |  |

| 0x05            |             | 15:8     | MULTI_PACH      | ET_SIZE[1:0            |           |         | BYTE_CO                  | UNT[13:8] |           |        |  |  |

| 0x06            | PCKSIZE     | 23:16    |                 | MULTI_PACKET_SIZE[9:2] |           |         |                          |           |           |        |  |  |

| 0x07            |             | 31:24    | AUTO_ZLP        |                        | SIZE[2:0] |         | MULTI_PACKET_SIZE[13:10] |           |           |        |  |  |

| 0x08            |             | 7:0      |                 |                        |           |         |                          |           |           |        |  |  |

| 0x09            |             | 15:8     |                 |                        |           |         |                          |           |           |        |  |  |

| 0x0A            | STATUS_BK   | 7:0      |                 |                        |           |         |                          |           | ERRORFLOW | CRCERR |  |  |

| 0x0B            |             | 15:8     |                 |                        |           |         |                          |           |           |        |  |  |

| 0x0C            |             | 7:0      |                 |                        |           |         |                          |           |           |        |  |  |

| 0x0D            |             | 15:8     |                 |                        |           |         |                          |           |           |        |  |  |

| 0x0E            |             | 7:0      |                 | ERCNT[2:0]             |           | CRC16ER | TOUTER                   | PIDER     | DAPIDER   | DTGLER |  |  |

| 0x0F            | STATUS_PIPE | 15:8     |                 |                        |           |         |                          |           |           |        |  |  |

# 32.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

Refer to the Register Access Protection, PAC - Peripheral Access Controller and GCLK Synchronization for details.

#### **Related Links**

PAC - Peripheral Access Controller

#### 32.8.1 Communication Device Host Registers

#### 32.8.1.1 Control A

Name:CTRLAOffset:0x00Reset:0x00Property:PAC Write-Protection, Write-Synchronised

Writing a one to this bit will set PSTATUS.PFREEZE bit.

## Bit 2 – CURBK: Current Bank Set

Writing a zero to this bit has no effect.

Writing a one to this bit will set PSTATUS.CURBK bit.

#### Bit 0 – DTGL: Data Toggle Set

Writing a zero to this bit has no effect.

Writing a one to this bit will set PSTATUS.DTGL bit.

#### 32.8.6.5 Pipe Status Register n

Name:PSTATUSOffset:0x106 + (n x 0x20)Reset:0x00Property:PAC Write-Protection

| Bit    | 7      | 6      | 5 | 4       | 3 | 2     | 1 | 0    |

|--------|--------|--------|---|---------|---|-------|---|------|

| [      | BK1RDY | BK0RDY |   | PFREEZE |   | CURBK |   | DTGL |

| Access | R      | R      |   | R       |   | R     |   | R    |

| Reset  | 0      | 0      |   | 0       |   | 0     |   | 0    |

## Bit 7 – BK1RDY: Bank 1 is ready

Writing a one to the bit EPSTATUSCLR.BK1RDY will clear this bit.

Writing a one to the bit EPSTATUSSET.BK1RDY will set this bit.

This bank is not used for Control pipe.

| Value | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| 0     | The bank number 1 is not ready: For IN the bank is empty. For Control/OUT the bank is not      |

|       | yet fill in.                                                                                   |

| 1     | The bank number 1 is ready: For IN the bank is filled full. For Control/OUT the bank is filled |

|       | in.                                                                                            |

#### Bit 6 – BK0RDY: Bank 0 is ready

Writing a one to the bit EPSTATUSCLR.BK0RDY will clear this bit.

Writing a one to the bit EPSTATUSSET.BK0RDY will set this bit.

This bank is the only one used for Control pipe.

| Value | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| 0     | The bank number 0 is not ready: For IN the bank is not empty. For Control/OUT the bank is      |

|       | not yet fill in.                                                                               |

| 1     | The bank number 0 is ready: For IN the bank is filled full. For Control/OUT the bank is filled |

|       | in.                                                                                            |

## Bit 4 – PFREEZE: Pipe Freeze

Writing a one to the bit EPSTATUSCLR.PFREEZE will clear this bit.

Writing a one to the bit EPSTATUSSET.PFREEZE will set this bit.

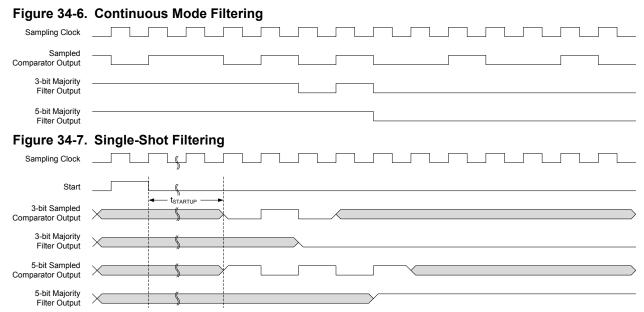

During sleep modes, filtering is supported only for single-shot measurements. Filtering must be disabled if continuous measurements will be done during sleep modes, or the resulting interrupt/event may be generated incorrectly.

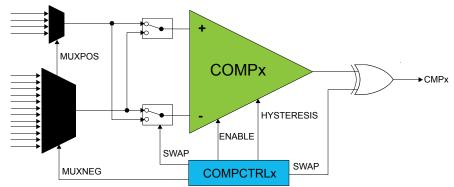

## 34.6.10 Comparator Output

The output of each comparator can be routed to an I/O pin by setting the Output bit group in the Comparator Control x register (COMPCTRLx.OUT). This allows the comparator to be used by external circuitry. Either the raw, non-synchronized output of the comparator or the CLK\_AC-synchronized version, including filtering, can be used as the I/O signal source. The output appears on the corresponding CMP[x] pin.

#### 34.6.11 Offset Compensation

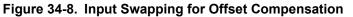

The Swap bit in the Comparator Control registers (COMPCTRLx.SWAP) controls switching of the input signals to a comparator's positive and negative terminals. When the comparator terminals are swapped, the output signal from the comparator is also inverted, as shown in Figure 34-8. This allows the user to measure or compensate for the comparator input offset voltage. As part of the input selection, COMPCTRLx.SWAP can be changed only while the comparator is disabled.

#### 34.6.12 Interrupts

The AC has the following interrupt sources:

# 32-bit ARM-Based Microcontrollers

| Mode    | Conditions                           | T <sub>A</sub> | V <sub>cc</sub> | Тур. | Max.  | Units |

|---------|--------------------------------------|----------------|-----------------|------|-------|-------|

| IDLE0   | Default operating conditions         | 25°C           | 3.3V            | 2.4  | 2.5   | mA    |

|         |                                      | 85°C           | 3.3V            | 2.5  | 2.6   |       |

| IDLE1   | Default operating conditions         | 25°C           | 3.3V            | 1.8  | 1.9   | a     |

|         |                                      | 85°C           | 3.3V            | 1.9  | 2     |       |

| IDLE2   | Default operating conditions         | 25°C           | 3.3V            | 1.3  | 1.4   | a     |

|         |                                      | 85°C           | 3.3V            | 1.4  | 1.5   |       |

| STANDBY | XOSC32K running, RTC running at 1kHz | 25°C           | 3.3V            | 4.6  | 15.0  | μΑ    |

|         |                                      | 85°C           | 3.3V            | 43   | 102.0 |       |

|         | XOSC32K and RTC stopped              | 25°C           | 3.3V            | 3.4  | 14.0  |       |

|         |                                      | 85°C           | 3.3V            | 42   | 100.0 |       |

# Table 37-10. Wake-up Time

| Mode    | Conditions                                       | T <sub>A</sub> | Min. | Тур. | Max. | Units |

|---------|--------------------------------------------------|----------------|------|------|------|-------|

| IDLE0   | OSC8M used as main clock source, Cache disabled  | 25°C           | -    | 4.0  | -    | μs    |

|         |                                                  | 85°C           | -    | 4.0  | -    |       |

| IDLE1   | IOSC8M used as main clock source, Cache disabled | 25°C           | -    | 12.1 | -    |       |

|         |                                                  | 85°C           | -    | 13.6 | -    |       |

| IDLE2   | IOSC8M used as main clock source, Cache disabled | 25°C           | -    | 13.0 | -    |       |

|         |                                                  | 85°C           | -    | 14.5 | -    |       |

| STANDBY | IOSC8M used as main clock source, Cache disabled | 25°C           | -    | 19.6 | -    |       |

|         |                                                  | 85°C           | -    | 19.7 | -    |       |

| Symbol                | Parameter           | Conditions                                                                                      | Min. | Тур. | Max. | Units |

|-----------------------|---------------------|-------------------------------------------------------------------------------------------------|------|------|------|-------|

| f <sub>IN</sub>       | Input frequency     |                                                                                                 | 32   | -    | 2000 | KHz   |

| f <sub>OUT</sub>      | Output frequency    |                                                                                                 | 48   | -    | 96   | MHz   |

| I <sub>FDPLL96M</sub> | Current consumption | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 48 MHz                                             | -    | 500  | 700  | μA    |

|                       |                     | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 96 MHz                                             | -    | 900  | 1200 |       |

| J <sub>p</sub>        | Period jitter       | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 48 MHz                                             | -    | 1.5  | 2.1  | %     |

|                       |                     | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 96 MHz                                             | -    | 4.0  | 10.0 |       |

|                       |                     | f <sub>IN</sub> = 2 MHz, f <sub>OUT</sub> = 48 MHz                                              | -    | 1.6  | 2.2  |       |

|                       |                     | f <sub>IN</sub> = 2 MHz, f <sub>OUT</sub> = 96 MHz                                              | -    | 4.6  | 10.2 |       |

| t <sub>LOCK</sub>     | Lock Time           | After start-up, time to get lock signal.<br>f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 96 MHz | -    | 1.2  | 2    | ms    |

|                       |                     | f <sub>IN</sub> = 2 MHz, f <sub>OUT</sub> = 96 MHz                                              | -    | 25   | 50   | μs    |

| Duty                  | Duty cycle          |                                                                                                 | 40   | 50   | 60   | %     |

| Table 37-57. FDPLL96M Characteristics <sup>(</sup> | (Device Variant B / Die Revision E) |

|----------------------------------------------------|-------------------------------------|

|----------------------------------------------------|-------------------------------------|

| Symbol                | Parameter           | Conditions                                                                                      | Min. | Тур. | Max. | Units |

|-----------------------|---------------------|-------------------------------------------------------------------------------------------------|------|------|------|-------|

| f <sub>IN</sub>       | Input frequency     |                                                                                                 | 32   | -    | 2000 | KHz   |

| f <sub>OUT</sub>      | Output frequency    |                                                                                                 | 48   | -    | 96   | MHz   |

| I <sub>FDPLL96M</sub> | Current consumption | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 48 MHz                                             | -    | 500  | -    | μA    |

|                       |                     | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 96 MHz                                             | -    | 900  | -    |       |

| J <sub>p</sub>        | Period jitter       | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 48 MHz                                             | -    | 2.2  | 3.0  | %     |

|                       |                     | f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 96 MHz                                             | -    | 3.7  | 9.0  |       |

|                       |                     | f <sub>IN</sub> = 2 MHz, f <sub>OUT</sub> = 48 MHz                                              | -    | 2.2  | 3.0  |       |

|                       |                     | f <sub>IN</sub> = 2 MHz, f <sub>OUT</sub> = 96 MHz                                              | -    | 4.4  | 9.7  |       |

| t <sub>LOCK</sub>     | Lock Time           | After start-up, time to get lock signal.<br>f <sub>IN</sub> = 32 kHz, f <sub>OUT</sub> = 96 MHz | -    | 1.0  | 2    | ms    |

|                       |                     | f <sub>IN</sub> = 2 MHz, f <sub>OUT</sub> = 96 MHz                                              | -    | 22   | 50   | μs    |

| Duty                  | Duty cycle          |                                                                                                 | 40   | 50   | 60   | %     |

## Note:

1. All values have been characterized with FILTSEL[1/0] as default value.

# Errata reference: 13574

# Fix/Workaround:

Write CTRLB.ACKACT to 0 using the following sequence:

// If higher priority interrupts exist, then disable so that the

// following two writes are atomic.

SERCOM - STATUS.reg = 0;

SERCOM - CTRLB.reg = 0;

// Re-enable interrupts if applicable.

Write CTRLB.ACKACT to 1 using the following sequence:

// If higher priority interrupts exist, then disable so that the

// following two writes are atomic.

SERCOM - STATUS.reg = 0;

SERCOM - CTRLB.reg = SERCOM\_I2CS\_CTRLB\_ACKACT;

// Re-enable interrupts if applicable.

Otherwise, only write to CTRLB in the AMATCH or DRDY interrupts if it is to close out a transaction.

When not closing a transaction, clear the AMATCH interrupt by writing a 1 to its bit position instead of using CTRLB.CMD. The DRDY interrupt is automatically cleared by reading/writing to the DATA register in smart mode.

If not in smart mode, DRDY should be cleared by writing a 1 to its bit position.

Code replacements examples:

Current:

SERCOM - CTRLB.reg |= SERCOM\_I2CS\_CTRLB\_ACKACT; Change to:

// If higher priority interrupts exist, then disable so that the

// following two writes are atomic.

SERCOM - STATUS.reg = 0;

SERCOM - CTRLB.reg = SERCOM\_I2CS\_CTRLB\_ACKACT;

// Re-enable interrupts if applicable.

Current:

SERCOM - CTRLB.reg &= ~SERCOM\_I2CS\_CTRLB\_ACKACT;

Change to:

// If higher priority interrupts exist, then disable so that the

// following two writes are atomic.

SERCOM - STATUS.reg = 0;

SERCOM - CTRLB.reg = 0;

// Re-enable interrupts if applicable.

Current:

/\* ACK or NACK address \*/ SERCOM - CTRLB.reg |= SERCOM\_I2CS\_CTRLB\_CMD(0x3); Change to:

// CMD=0x3 clears all interrupts, so to keep the result similar,

// PREC is cleared if it was set.

if (SERCOM - INTFLAG.bit.PREC) SERCOM - INTFLAG.reg =

SERCOM\_I2CS\_INTFLAG\_PREC;

SERCOM - INTFLAG.reg = SERCOM\_I2CS\_INTFLAG\_AMATCH;

15 – The SYSTICK calibration value is incorrect. Errata reference: 14154 Fix/Workaround: if (SERCOM - INTFLAG.bit.PREC) SERCOM - INTFLAG.reg =

SERCOM\_I2CS\_INTFLAG\_PREC;

SERCOM - INTFLAG.reg = SERCOM I2CS INTFLAG AMATCH;

# 6 – PA24 and PA25 cannot be used as input when configured as GPIO with continuous sampling (cannot be read by PORT). Errata reference: 12005

## Fix/Workaround:

- Use PA24 and PA25 for peripherals or only as output pins.

- Or configure PA31 to PA24 for on-demand sampling (CTRL[31:24] all zeroes) and access the IN register through the APB (not the IOBUS), to allow waiting for on-demand sampling.

## 7 – Rx serializer in the RIGHT Data Slot Formatting Adjust mode (SERCTRL.SLOTADJ clear) does not work when the slot size is not 32 bits.

## Errata reference: 13411

## Fix/Workaround:

In SERCTRL.SERMODE RX, SERCTRL.SLOTADJ RIGHT must be used with CLKCTRL.SLOTSIZE 32.

# 8 – The SYSTICK calibration value is incorrect.

# Errata reference: 14154

## Fix/Workaround:

The correct SYSTICK calibration value is 0x40000000. This value should not be used to initialize the Systick RELOAD value register, which should be initialized instead with a value depending on the main clock frequency and on the tick period required by the application. For a detailed description of the SYSTICK module, refer to the official ARM Cortex-M0+ documentation.

9 – While the internal startup is not completed, PA07 pin is driven low by the chip. Then as all the other pins it is configured as an High Impedance pin.

#### Errata reference: 12118 Fix/Workaround:

None

10 – Pulldown functionality is not available on GPIO pin PA24 and PA25 Errata reference: 13883

Fix/Workaround:

None

11 – The voltage regulator in low power mode is not functional at temperatures above 85C.

## Errata reference: 12291

## Fix/Workaround:

Enable normal mode on the voltage regulator in standby sleep mode. Example code:

// Set the voltage regulator in normal mode configuration in standby sleep mode

SYSCTRL->VREG.bit.RUNSTDBY = 1;

12 – If the external XOSC32K is broken, neither the external pin RST nor the GCLK software reset can reset the GCLK generators using XOSC32K as source clock.