Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | HC08                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 8MHz                                                         |

| Connectivity               | CANbus, LINbus, SCI, SPI                                     |

| Peripherals                | LVD, POR, PWM                                                |

| Number of I/O              | 21                                                           |

| Program Memory Size        | 16KB (16K x 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                    |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 32-LQFP                                                      |

| Supplier Device Package    | 32-LQFP (7x7)                                                |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68908gz16mfje |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### General Description

- System protection features:

- Optional computer operating properly (COP) reset

- Low-voltage detection with optional reset and selectable trip points for 3.3-V and 5.0-V operation

- Illegal opcode detection with reset

- Illegal address detection with reset

- Low-power design; fully static with stop and wait modes

- Standard low-power modes of operation:

- Wait mode

- Stop mode

- Master reset pin and power-on reset (POR)

- On-chip FLASH memory:

- MC68HC908GZ16 16 Kbytes

- MC68HC908GZ8 8 Kbytes

- 1 Kbyte of on-chip random-access memory (RAM)

- 406 bytes of FLASH programming routines read-only memory (ROM)

- Serial peripheral interface (SPI) module

- Enhanced serial communications interface (ESCI) module

- Fine adjust baud rate prescalers for precise control of baud rate

- Arbiter module:

- Measurement of received bit timings for baud rate recovery without use of external timer

- Bitwise arbitration for arbitrated UART communications

- LIN specific enhanced features:

- Generation of LIN 1.2 break symbols without extra software steps on each message

- Break detection filtering to prevent false interrupts

- Two 16-bit, 2-channel timer interface modules (TIM1 and TIM2) with selectable input capture, output compare, and pulse-width modulation (PWM) capability on each channel. One 2-channel timer and one 1-channel timer on the 32-pin package.

- Up to 8-channel, 10-bit successive approximation analog-to-digital converter (ADC) depending on package choice

- BREAK (BRK) module to allow single breakpoint setting during in-circuit debugging

- Internal pullups on IRQ and RST to reduce customer system cost

- Up to 37 general-purpose input/output (I/O) pins, including:

- 28 shared-function I/O pins

- Up to nine dedicated I/O pins, depending on package choice

- Selectable pullups on inputs only on ports A, C, and D. Selection is on an individual port bit basis. During output mode, pullups are disengaged.

- High current 10-mA sink/source capability on all port pins

- Higher current 20-mA sink/source capability on PTC0-PTC4

- Timebase module (TBM) with clock prescaler circuitry for eight user selectable periodic real-time interrupts with optional active clock source during stop mode for periodic wakeup from stop using an external crystal

- User selection of having the oscillator enabled or disabled during stop mode

- Up to 8-bit keyboard wakeup port depending on package choice

- 2 mA maximum current injection on all port pins to maintain input protection

- Available packages:

- 32-pin quad flat pack (LQFP)

- 48-pin quad flat pack (LQFP)

# Chapter 2 Memory

# 2.1 Introduction

The CPU08 can address 64 Kbytes of memory space. The memory map, shown in Figure 2-1, includes:

- 15,872 bytes of user FLASH memory

- 1024 bytes of random-access memory (RAM)

- 406 bytes of FLASH programming routines read-only memory (ROM)

- 44 bytes of user-defined vectors

- 350 bytes of monitor ROM

# 2.2 Unimplemented Memory Locations

Accessing an unimplemented location can cause an illegal address reset. In the memory map (Figure 2-1) and in register figures in this document, unimplemented locations are shaded.

# 2.3 Reserved Memory Locations

Accessing a reserved location can have unpredictable effects on microcontroller (MCU) operation. In the Figure 2-1 and in register figures in this document, reserved locations are marked with the word Reserved or with the letter R.

# 2.4 Input/Output (I/O) Section

Most of the control, status, and data registers are in the zero page area of \$0000-\$003F. Additional I/O registers have these addresses:

- \$FE00; break status register, SBSR

- \$FE01; SIM reset status register, SRSR

- \$FE02; break auxiliary register, BRKAR

- \$FE03; break flag control register, BFCR

- \$FE04; interrupt status register 1, INT1

- \$FE05; interrupt status register 2, INT2

- \$FE06; interrupt status register 3, INT3

- \$FE07; reserved

- \$FE08; FLASH control register, FLCR

- \$FE09; break address register high, BRKH

- \$FE0A; break address register low, BRKL

- \$FE0B; break status and control register, BRKSCR

- \$FE0C; LVI status register, LVISR

- \$FF7E; FLASH block protect register, FLBPR

Data registers are shown in Figure 2-2. Table 2-1 is a list of vector locations.

Input/Output (I/O) Section

| Vector Priority | Vector | Address | Vector                                |

|-----------------|--------|---------|---------------------------------------|

| Lowest          | 1500   | \$FFD4  | MSCAN08 Transmit Vector (High)        |

|                 | IF20   | \$FFD5  | MSCAN08 Transmit Vector (Low)         |

| l Î             | 1540   | \$FFD6  | MSCAN08 Receive Vector (High)         |

|                 | IF19   | \$FFD7  | MSCAN08 Receive Vector (Low)          |

|                 | 1540   | \$FFD8  | MSCAN08 Error Vector (High)           |

|                 | IF18   | \$FFD9  | MSCAN08 Error Vector (Low)            |

|                 | 1515   | \$FFDA  | MSCAN08 Wakeup Vector (High)          |

|                 | IF17   | \$FFDB  | MSCAN08 Wakeup Vector (Low)           |

|                 | 1540   | \$FFDC  | Timebase Vector (High)                |

|                 | IF16   | \$FFDD  | Timebase Vector (Low)                 |

|                 | 1545   | \$FFDE  | ADC Conversion Complete Vector (High) |

|                 | IF15   | \$FFDF  | ADC Conversion Complete Vector (Low)  |

|                 | 1544   | \$FFE0  | Keyboard Vector (High)                |

|                 | IF14   | \$FFE1  | Keyboard Vector (Low)                 |

|                 | 1510   | \$FFE2  | ESCI Transmit Vector (High)           |

|                 | IF13   | \$FFE3  | ESCI Transmit Vector (Low)            |

|                 | 1510   | \$FFE4  | ESCI Receive Vector (High)            |

|                 | IF12   | \$FFE5  | ESCI Receive Vector (Low)             |

|                 | 1514   | \$FFE6  | ESCI Error Vector (High)              |

|                 | IF11   | \$FFE7  | ESCI Error Vector (Low)               |

|                 | IF10   | \$FFE8  | SPI Transmit Vector (High)            |

|                 | IFIU   | \$FFE9  | SPI Transmit Vector (Low)             |

|                 | IF9    | \$FFEA  | SPI Receive Vector (High)             |

|                 | IF9    | \$FFEB  | SPI Receive Vector (Low)              |

|                 | IF8    | \$FFEC  | TIM2 Overflow Vector (High)           |

|                 | IFO    | \$FFED  | TIM2 Overflow Vector (Low)            |

|                 | IF7    | \$FFEE  | TIM2 Channel 1 Vector (High)          |

|                 |        | \$FFEF  | TIM2 Channel 1 Vector (Low)           |

|                 | IF6    | \$FFF0  | TIM2 Channel 0 Vector (High)          |

|                 | 110    | \$FFF1  | TIM2 Channel 0 Vector (Low)           |

|                 | IF5    | \$FFF2  | TIM1 Overflow Vector (High)           |

|                 | 11.5   | \$FFF3  | TIM1 Overflow Vector (Low)            |

|                 | IF4    | \$FFF4  | TIM1 Channel 1 Vector (High)          |

|                 |        | \$FFF5  | TIM1 Channel 1 Vector (Low)           |

|                 | IF3    | \$FFF6  | TIM1 Channel 0 Vector (High)          |

|                 | 11 0   | \$FFF7  | TIM1 Channel 0 Vector (Low)           |

|                 | IF2    | \$FFF8  | PLL Vector (High)                     |

|                 |        | \$FFF9  | PLL Vector (Low)                      |

|                 | IF1    | \$FFFA  | IRQ Vector (High)                     |

|                 |        | \$FFFB  | IRQ Vector (Low)                      |

|                 | _      | \$FFFC  | SWI Vector (High)                     |

|                 |        | \$FFFD  | SWI Vector (Low)                      |

| *               |        | \$FFFE  | Reset Vector (High)                   |

| Highest         |        | \$FFFF  | Reset Vector (Low)                    |

### Table 2-1. Vector Addresses

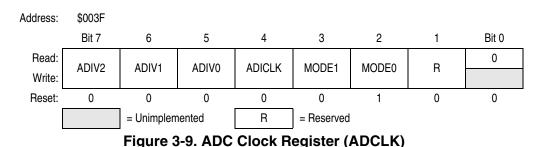

### 3.8.3 ADC Clock Register

The ADC clock register (ADCLK) selects the clock frequency for the ADC.

# ADIV2–ADIV0 — ADC Clock Prescaler Bits

ADIV2–ADIV0 form a 3-bit field which selects the divide ratio used by the ADC to generate the internal ADC clock. Table 3-2 shows the available clock configurations. The ADC clock should be set to approximately 1 MHz.

| ADIV2 | ADIV1            | ADIV0            | ADC Clock Rate       |

|-------|------------------|------------------|----------------------|

| 0     | 0                | 0                | ADC input clock ÷ 1  |

| 0     | 0                | 1                | ADC input clock ÷ 2  |

| 0     | 1                | 0                | ADC input clock ÷ 4  |

| 0     | 1                | 1                | ADC input clock ÷ 8  |

| 1     | X <sup>(1)</sup> | X <sup>(1)</sup> | ADC input clock ÷ 16 |

Table 3-2. ADC Clock Divide Ratio

1. X = Don't care

#### ADICLK — ADC Input Clock Select Bit

ADICLK selects either the bus clock or the oscillator output clock (CGMXCLK) as the input clock source to generate the internal ADC clock. Reset selects CGMXCLK as the ADC clock source.

1 = Internal bus clock

0 = Oscillator output clock (CGMXCLK)

The ADC requires a clock rate of approximately 1 MHz for correct operation. If the selected clock source is not fast enough, the ADC will generate incorrect conversions. See 21.10 5.0-Volt ADC Characteristics.

$f_{ADIC} = \frac{f_{CGMXCLK} \text{ or bus frequency}}{ADIV[2:0]} \cong 1 \text{ MHz}$

#### MODE1 and MODE0 — Modes of Result Justification Bits

MODE1 and MODE0 select among four modes of operation. The manner in which the ADC conversion results will be placed in the ADC data registers is controlled by these modes of operation. Reset returns right-justified mode.

00 = 8-bit truncation mode

01 = Right justified mode

10 = Left justified mode

11 = Left justified signed data mode

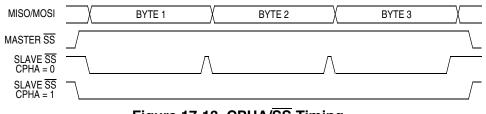

# Chapter 4 Clock Generator Module (CGM)

# 4.1 Introduction

This section describes the clock generator module. The CGM generates the crystal clock signal, CGMXCLK, which operates at the frequency of the crystal. The CGM also generates the base clock signal, CGMOUT, which is based on either the crystal clock divided by two or the phase-locked loop (PLL) clock, CGMVCLK, divided by two. In user mode, CGMOUT is the clock from which the SIM derives the system clocks, including the bus clock, which is at a frequency of CGMOUT/2. The PLL is a fully functional frequency generator designed for use with crystals or ceramic resonators. The PLL can generate a maximum bus frequency of 8 MHz using a 1-8MHz crystal or external clock source.

# 4.2 Features

Features of the CGM include:

- Phase-locked loop with output frequency in integer multiples of an integer dividend of the crystal reference

- High-frequency crystal operation with low-power operation and high-output frequency resolution

- Programmable hardware voltage-controlled oscillator (VCO) for low-jitter operation

- Automatic bandwidth control mode for low-jitter operation

- Automatic frequency lock detector

- CPU interrupt on entry or exit from locked condition

- Configuration register bit to allow oscillator operation during stop mode

# 4.3 Functional Description

The CGM consists of three major submodules:

- Crystal oscillator circuit The crystal oscillator circuit generates the constant crystal frequency clock, CGMXCLK.

- Phase-locked loop (PLL) The PLL generates the programmable VCO frequency clock, CGMVCLK.

- Base clock selector circuit This software-controlled circuit selects either CGMXCLK divided by two or the VCO clock, CGMVCLK, divided by two as the base clock, CGMOUT. The SIM derives the system clocks from either CGMOUT or CGMXCLK.

Figure 4-1 shows the structure of the CGM.

#### **Clock Generator Module (CGM)**

frequency, f<sub>RCLK</sub>. The circuit determines the mode of the PLL and the lock condition based on this comparison.

### 4.3.4 Acquisition and Tracking Modes

The PLL filter is manually or automatically configurable into one of two operating modes:

- Acquisition mode In acquisition mode, the filter can make large frequency corrections to the VCO. This mode is used at PLL start up or when the PLL has suffered a severe noise hit and the VCO frequency is far off the desired frequency. When in acquisition mode, the ACQ bit is clear in the PLL bandwidth control register. (See 4.5.2 PLL Bandwidth Control Register.)

- Tracking mode In tracking mode, the filter makes only small corrections to the frequency of the VCO. PLL jitter is much lower in tracking mode, but the response to noise is also slower. The PLL enters tracking mode when the VCO frequency is nearly correct, such as when the PLL is selected as the base clock source. (See 4.3.8 Base Clock Selector Circuit.) The PLL is automatically in tracking mode when not in acquisition mode or when the ACQ bit is set.

### 4.3.5 Manual and Automatic PLL Bandwidth Modes

The PLL can change the bandwidth or operational mode of the loop filter manually or automatically. Automatic mode is recommended for most users.

In automatic bandwidth control mode (AUTO = 1), the lock detector automatically switches between acquisition and tracking modes. Automatic bandwidth control mode also is used to determine when the VCO clock, CGMVCLK, is safe to use as the source for the base clock, CGMOUT. (See 4.5.2 PLL Bandwidth Control Register.) If PLL interrupts are enabled, the software can wait for a PLL interrupt request and then check the LOCK bit. If interrupts are disabled, software can poll the LOCK bit continuously (for example, during PLL start up) or at periodic intervals. In either case, when the LOCK bit is set, the VCO clock is safe to use as the source for the base clock. (See 4.3.8 Base Clock Selector Circuit.) If the VCO is selected as the source for the base clock and the LOCK bit is clear, the PLL has suffered a severe noise hit and the software must take appropriate action, depending on the application. (See 4.6 Interrupts for information and precautions on using interrupts.)

The following conditions apply when the PLL is in automatic bandwidth control mode:

- The ACQ bit (See 4.5.2 PLL Bandwidth Control Register.) is a read-only indicator of the mode of the filter. (See 4.3.4 Acquisition and Tracking Modes.)

- The ACQ bit is set when the VCO frequency is within a certain tolerance and is cleared when the VCO frequency is out of a certain tolerance. (See 4.8 Acquisition/Lock Time Specifications for more information.)

- The LOCK bit is a read-only indicator of the locked state of the PLL.

- The LOCK bit is set when the VCO frequency is within a certain tolerance and is cleared when the VCO frequency is out of a certain tolerance. (See 4.8 Acquisition/Lock Time Specifications for more information.)

- CPU interrupts can occur if enabled (PLLIE = 1) when the PLL's lock condition changes, toggling the LOCK bit. (See 4.5.1 PLL Control Register.)

The PLL also may operate in manual mode (AUTO = 0). Manual mode is used by systems that do not require an indicator of the lock condition for proper operation. Such systems typically operate well below  $f_{BUSMAX}$ .

#### **Clock Generator Module (CGM)**

#### LOCK — Lock Indicator Bit

When the AUTO bit is set, LOCK is a read-only bit that becomes set when the VCO clock, CGMVCLK, is locked (running at the programmed frequency). When the AUTO bit is clear, LOCK reads as logic 0 and has no meaning. The write one function of this bit is reserved for test, so this bit must **always** be written a 0. Reset clears the LOCK bit.

1 = VCO frequency correct or locked

0 = VCO frequency incorrect or unlocked

#### ACQ — Acquisition Mode Bit

When the AUTO bit is set,  $\overline{ACQ}$  is a read-only bit that indicates whether the PLL is in acquisition mode or tracking mode. When the AUTO bit is clear,  $\overline{ACQ}$  is a read/write bit that controls whether the PLL is in acquisition or tracking mode.

In automatic bandwidth control mode (AUTO = 1), the last-written value from manual operation is stored in a temporary location and is recovered when manual operation resumes. Reset clears this bit, enabling acquisition mode.

1 = Tracking mode

0 = Acquisition mode

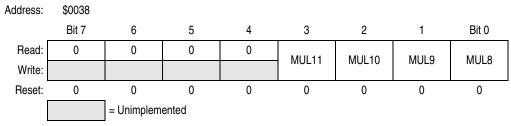

### 4.5.3 PLL Multiplier Select Register High

The PLL multiplier select register high (PMSH) contains the programming information for the high byte of the modulo feedback divider.

Figure 4-6. PLL Multiplier Select Register High (PMSH)

#### MUL11–MUL8 — Multiplier Select Bits

These read/write bits control the high byte of the modulo feedback divider that selects the VCO frequency multiplier N. (See 4.3.3 PLL Circuits and 4.3.6 Programming the PLL.) A value of \$0000 in the multiplier select registers configures the modulo feedback divider the same as a value of \$0001. Reset initializes the registers to \$0040 for a default multiply value of 64.

#### NOTE

The multiplier select bits have built-in protection such that they cannot be written when the PLL is on (PLLON = 1).

#### PMSH[7:4] — Unimplemented Bits

These bits have no function and always read as logic 0s.

#### Computer Operating Properly (COP) Module

The COP counter is a free-running 6-bit counter preceded by a 12-bit prescaler counter. If not cleared by software, the COP counter overflows and generates an asynchronous reset after  $2^{18} - 2^4$  or  $2^{13} - 2^4$  CGMXCLK cycles, depending on the state of the COP rate select bit, COPRS, in the configuration register. With a  $2^{13} - 2^4$  CGMXCLK cycle overflow option, a 4.9152-MHz crystal gives a COP timeout period of 53.3 ms. Writing any value to location \$FFFF before an overflow occurs prevents a COP reset by clearing the COP counter and stages 12–5 of the prescaler.

#### NOTE

Service the COP immediately after reset and before entering or after exiting stop mode to guarantee the maximum time before the first COP counter overflow.

A COP reset pulls the RST pin low for 32 CGMXCLK cycles and sets the COP bit in the reset status register (RSR).

In monitor mode, the COP is disabled if the  $\overline{RST}$  pin or the  $\overline{IRQ1}$  is held at  $V_{TST}$ . During the break state,  $V_{TST}$  on the  $\overline{RST}$  pin disables the COP.

#### NOTE

Place COP clearing instructions in the main program and not in an interrupt subroutine. Such an interrupt subroutine could keep the COP from generating a reset even while the main program is not working properly.

# 6.3 I/O Signals

The following paragraphs describe the signals shown in Figure 6-1.

### 6.3.1 CGMXCLK

CGMXCLK is the crystal oscillator output signal. CGMXCLK frequency is equal to the crystal frequency.

### 6.3.2 STOP Instruction

The STOP instruction clears the COP prescaler.

#### 6.3.3 COPCTL Write

Writing any value to the COP control register (COPCTL) clears the COP counter and clears bits 12–5 of the prescaler. Reading the COP control register returns the low byte of the reset vector. See 6.4 COP Control Register.

### 6.3.4 Power-On Reset

The power-on reset (POR) circuit clears the COP prescaler 4096 CGMXCLK cycles after power-up.

#### 6.3.5 Internal Reset

An internal reset clears the COP prescaler and the COP counter.

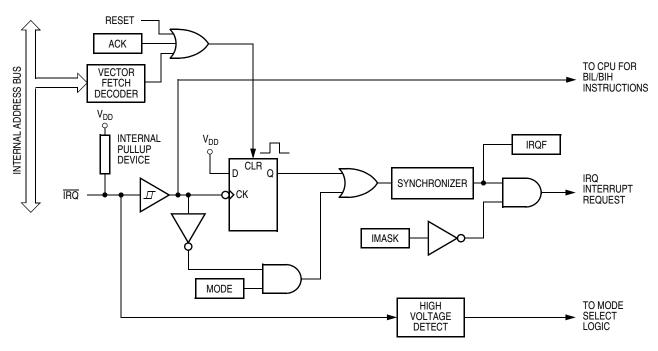

#### External Interrupt (IRQ)

Figure 8-1. IRQ Module Block Diagram

When an interrupt pin is both falling-edge and low-level triggered, the interrupt remains set until both of these events occur:

- Vector fetch or software clear

- Return of the interrupt pin to logic 1

The vector fetch or software clear may occur before or after the interrupt pin returns to logic 1. As long as the pin is low, the interrupt request remains pending. A reset will clear the latch and the MODE control bit, thereby clearing the interrupt even if the pin stays low.

When set, the IMASK bit in the INTSCR mask all external interrupt requests. A latched interrupt request is not presented to the interrupt priority logic unless the IMASK bit is clear.

**NOTE** The interrupt mask (I) in the condition code register (CCR) masks all interrupt requests, including external interrupt requests.

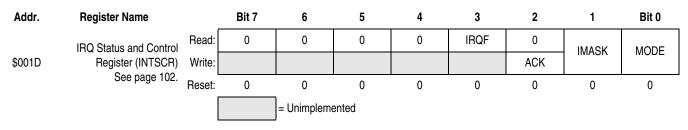

Figure 8-2. IRQ I/O Register Summary

# 10.3 Break Module (BRK)

### 10.3.1 Wait Mode

If enabled, the break (BRK) module is active in wait mode. In the break routine, the user can subtract one from the return address on the stack if the SBSW bit in the break status register is set.

### 10.3.2 Stop Mode

The break module is inactive in stop mode. The STOP instruction does not affect break module register states.

# 10.4 Central Processor Unit (CPU)

### 10.4.1 Wait Mode

The WAIT instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling interrupts. After exit from wait mode by interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

### 10.4.2 Stop Mode

The STOP instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling external interrupts. After exit from stop mode by external interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

After exiting stop mode, the CPU clock begins running after the oscillator stabilization delay.

# 10.5 Clock Generator Module (CGM)

### 10.5.1 Wait Mode

The clock generator module (CGM) remains active in wait mode. Before entering wait mode, software can disengage and turn off the PLL by clearing the BCS and PLLON bits in the PLL control register (PCTL). Less power-sensitive applications can disengage the PLL without turning it off. Applications that require the PLL to wake the MCU from wait mode also can deselect the PLL output without turning off the PLL.

### 10.5.2 Stop Mode

If the OSCSTOPEN bit in the CONFIG register is cleared (default), then the STOP instruction disables the CGM (oscillator and phase-locked loop) and holds low all CGM outputs (CGMXCLK, CGMOUT, and CGMINT).

If the OSCSTOPEN bit in the CONFIG register is set, then the phase locked loop is shut off, but the oscillator will continue to operate in stop mode.

| MSCAN08 Mode | CPU                                    | Mode                    |

|--------------|----------------------------------------|-------------------------|

| MSCANOO MODE | STOP                                   | WAIT or RUN             |

| Power Down   | SLPAK = X <sup>(1)</sup><br>SFTRES = X |                         |

| Sleep        |                                        | SLPAK = 1<br>SFTRES = 0 |

| Soft Reset   |                                        | SLPAK = 0<br>SFTRES = 1 |

| Normal       |                                        | SLPAK = 0<br>SFTRES = 0 |

#### Table 12-2. MSCAN08 versus CPU Operating Modes

1. 'X' means don't care.

#### 12.8.1 MSCAN08 Sleep Mode

The CPU can request the MSCAN08 to enter the low-power mode by asserting the SLPRQ bit in the module configuration register (see Figure 12-7). The time when the MSCAN08 enters sleep mode depends on its activity:

- If it is transmitting, it continues to transmit until there is no more message to be transmitted, and then goes into sleep mode

- If it is receiving, it waits for the end of this message and then goes into sleep mode

- If it is neither transmitting or receiving, it will immediately go into sleep mode

#### NOTE

The application software must avoid setting up a transmission (by clearing or more TXE flags) and immediately request sleep mode (by setting SLPRQ). It then depends on the exact sequence of operations whether MSCAN08 starts transmitting or goes into sleep mode directly.

During sleep mode, the SLPAK flag is set. The application software should use SLPAK as a handshake indication for the request (SLPRQ) to go into sleep mode. When in sleep mode, the MSCAN08 stops its internal clocks. However, clocks to allow register accesses still run. If the MSCAN08 is in bus-off state, it stops counting the 128\*11 consecutive recessive bits due to the stopped clocks. The CAN<sub>TX</sub> pin stays in recessive state. If RXF = 1, the message can be read and RXF can be cleared. Copying of RxGB into RxFG doesn't take place while in sleep mode. It is possible to access the transmit buffers and to clear the TXE flags. No message abort takes place while in sleep mode.

The MSCAN08 leaves sleep mode (wakes-up) when:

- Bus activity occurs, or

- The MCU clears the SLPRQ bit, or

- The MCU sets the SFTRES bit

#### NOTE

The MCU cannot clear the SLPRQ bit before the MSCAN08 is in sleep mode (SLPAK=1).

**MSCAN08 Controller (MSCAN08)**

# 12.12.3 Data Length Register (DLR)

This register keeps the data length field of the CAN frame.

#### DLC3–DLC0 — Data Length Code Bits

The data length code contains the number of bytes (data byte count) of the respective message. At transmission of a remote frame, the data length code is transmitted as programmed while the number of transmitted bytes is always 0. The data byte count ranges from 0 to 8 for a data frame. Table 12-5 shows the effect of setting the DLC bits.

|      | Data Len | gth Code |      | Data Byte |

|------|----------|----------|------|-----------|

| DLC3 | DLC2     | DLC1     | DLC0 | Count     |

| 0    | 0        | 0        | 0    | 0         |

| 0    | 0        | 0        | 1    | 1         |

| 0    | 0        | 1        | 0    | 2         |

| 0    | 0        | 1        | 1    | 3         |

| 0    | 1        | 0        | 0    | 4         |

| 0    | 1        | 0        | 1    | 5         |

| 0    | 1        | 1        | 0    | 6         |

| 0    | 1        | 1        | 1    | 7         |

| 1    | 0        | 0        | 0    | 8         |

Table 12-5. Data Length Codes

### 12.12.4 Data Segment Registers (DSRn)

The eight data segment registers contain the data to be transmitted or received. The number of bytes to be transmitted or being received is determined by the data length code in the corresponding DLR.

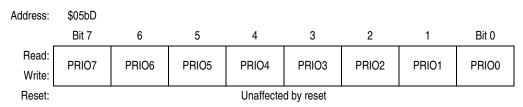

### 12.12.5 Transmit Buffer Priority Registers

| Figure 12-14. Transmit Buffer Priority Register (TBPR) |

|--------------------------------------------------------|

|--------------------------------------------------------|

#### PRIO7–PRIO0 — Local Priority

This field defines the local priority of the associated message buffer. The local priority is used for the internal prioritization process of the MSCAN08 and is defined to be highest for the smallest binary number. The MSCAN08 implements the following internal prioritization mechanism:

- All transmission buffers with a cleared TXE flag participate in the prioritization right before the SOF is sent.

- The transmission buffer with the lowest local priority field wins the prioritization.

- In case more than one buffer has the same lowest priority, the message buffer with the lower index number wins.

MSCAN08 Controller (MSCAN08)

Input/Output (I/O) Ports

#### PTAPUE7–PTAPUE0 — Port A Input Pullup Enable Bits

These writable bits are software programmable to enable pullup devices on an input port bit.

- 1 = Corresponding port A pin configured to have internal pullup

- 0 = Corresponding port A pin has internal pullup disconnected

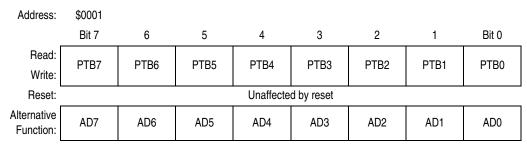

# 13.4 Port B

Port B is an 8-bit special-function port that shares all eight of its pins with the analog-to-digital converter (ADC) module.

### 13.4.1 Port B Data Register

The port B data register (PTB) contains a data latch for each of the eight port pins.

Figure 13-6. Port B Data Register (PTB)

#### PTB7-PTB0 — Port B Data Bits

These read/write bits are software-programmable. Data direction of each port B pin is under the control of the corresponding bit in data direction register B. Reset has no effect on port B data.

#### AD7-AD0 — Analog-to-Digital Input Bits

AD7–AD0 are pins used for the input channels to the analog-to-digital converter module. The channel select bits in the ADC status and control register define which port B pin will be used as an ADC input and overrides any control from the port I/O logic by forcing that pin as the input to the analog circuitry. See Chapter 3 Analog-to-Digital Converter (ADC) for more information.

#### NOTE

Care must be taken when reading port B while applying analog voltages to AD7–AD0 pins. If the appropriate ADC channel is not enabled, excessive current drain may occur if analog voltages are applied to the PTBx/ADx pin, while PTB is read as a digital input. Those ports not selected as analog input channels are considered digital I/O ports.

### 13.4.2 Data Direction Register B

Data direction register B (DDRB) determines whether each port B pin is an input or an output. Writing a logic 1 to a DDRB bit enables the output buffer for the corresponding port B pin; a logic 0 disables the output buffer.

Input/Output (I/O) Ports

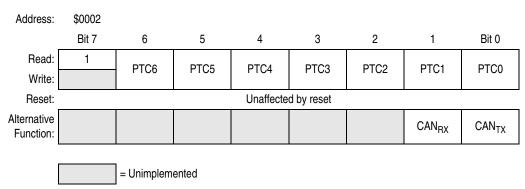

# 13.5 Port C

Port C is a 7-bit, general-purpose bidirectional I/O port. Port C also has software configurable pullup devices if configured as an input port.

### 13.5.1 Port C Data Register

The port C data register (PTC) contains a data latch for each of the seven port C pins.

**NOTE** Bit 6 through bit 2 of PTC are not available in the 32-pin LQFP package.

Figure 13-9. Port C Data Register (PTC)

### PTC6-PTC0 — Port C Data Bits

These read/write bits are software-programmable. Data direction of each port C pin is under the control of the corresponding bit in data direction register C. Reset has no effect on port C data.

### CAN<sub>RX</sub> and CAN<sub>TX</sub> — MSCAN08 Bits

The CAN<sub>RX</sub>–CAN<sub>TX</sub> pins are the MSCAN08 modules receive and transmit pins. The CANEN bit in the MSCAN08 control register determines, whether the PTC1/CAN<sub>RX</sub>–PTC0/CAN<sub>TX</sub> pins are MSCAN08 pins or general-purpose I/O pins. See Chapter 12 MSCAN08 Controller (MSCAN08).

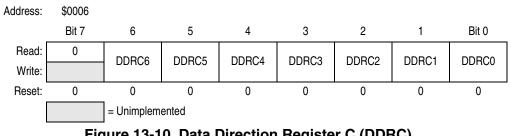

### 13.5.2 Data Direction Register C

Data direction register C (DDRC) determines whether each port C pin is an input or an output. Writing a logic 1 to a DDRC bit enables the output buffer for the corresponding port C pin; a logic 0 disables the output buffer.

The maximum percent difference between the receiver count and the transmitter count of a slow 9-bit character with no errors is:

$$\frac{170 - 163}{170} \times 100 = 4.12\%$$

#### **Fast Data Tolerance**

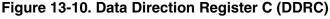

Figure 15-9 shows how much a fast received character can be misaligned without causing a noise error or a framing error. The fast stop bit ends at RT10 instead of RT16 but is still there for the stop bit data samples at RT8, RT9, and RT10.

Figure 15-9. Fast Data

For an 8-bit character, data sampling of the stop bit takes the receiver9 bit times  $\times$  16 RT cycles + 10 RT cycles = 154 RT cycles.

With the misaligned character shown in Figure 15-9, the receiver counts 154 RT cycles at the point when the count of the transmitting device is 10 bit times  $\times$  16 RT cycles = 160 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 8-bit character with no errors is

$$\frac{154 - 160}{154} \times 100 = 3.90\%.$$

For a 9-bit character, data sampling of the stop bit takes the receiver 10 bit times  $\times$  16 RT cycles + 10 RT cycles = 170 RT cycles.

With the misaligned character shown in Figure 15-9, the receiver counts 170 RT cycles at the point when the count of the transmitting device is 11 bit times  $\times$  16 RT cycles = 176 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 9-bit character with no errors is:

$$\left|\frac{170 - 176}{170}\right| \times 100 = 3.53\%.$$

#### 15.4.3.6 Receiver Wakeup

So that the MCU can ignore transmissions intended only for other receivers in multiple-receiver systems, the receiver can be put into a standby state. Setting the receiver wakeup bit, RWU, in SCC2 puts the receiver into a standby state during which receiver interrupts are disabled.

#### Enhanced Serial Communications Interface (ESCI) Module

must receive a valid character that sets the SCRF bit before an idle condition can set the IDLE bit. Also, after the IDLE bit has been cleared, a valid character must again set the SCRF bit before an idle condition can set the IDLE bit. Reset clears the IDLE bit.

- 1 = Receiver input idle

- 0 = Receiver input active (or idle since the IDLE bit was cleared)

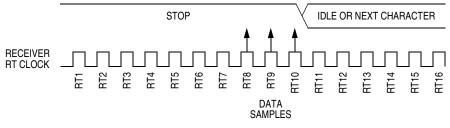

#### **OR** — Receiver Overrun Bit

This clearable, read-only bit is set when software fails to read the SCDR before the receive shift register receives the next character. The OR bit generates an ESCI error CPU interrupt request if the ORIE bit in SCC3 is also set. The data in the shift register is lost, but the data already in the SCDR is not affected. Clear the OR bit by reading SCS1 with OR set and then reading the SCDR. Reset clears the OR bit.

- 1 = Receive shift register full and SCRF = 1

- 0 = No receiver overrun

Software latency may allow an overrun to occur between reads of SCS1 and SCDR in the flag-clearing sequence. Figure 15-14 shows the normal flag-clearing sequence and an example of an overrun caused by a delayed flag-clearing sequence. The delayed read of SCDR does not clear the OR bit because OR was not set when SCS1 was read. Byte 2 caused the overrun and is lost. The next flag-clearing sequence reads byte 3 in the SCDR instead of byte 2.

In applications that are subject to software latency or in which it is important to know which byte is lost due to an overrun, the flag-clearing routine can check the OR bit in a second read of SCS1 after reading the data register.

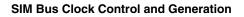

# 16.2 SIM Bus Clock Control and Generation

The bus clock generator provides system clock signals for the CPU and peripherals on the MCU. The system clocks are generated from an incoming clock, CGMOUT, as shown in Figure 16-3. This clock originates from either an external oscillator or from the on-chip PLL.

# 16.2.1 Bus Timing

In user mode, the internal bus frequency is either the crystal oscillator output (CGMXCLK) divided by four or the PLL output (CGMVCLK) divided by four.

### 16.2.2 Clock Startup from POR or LVI Reset

When the power-on reset module or the low-voltage inhibit module generates a reset, the clocks to the CPU and peripherals are inactive and held in an inactive phase until after the 4096 CGMXCLK cycle POR timeout has completed. The RST pin is driven low by the SIM during this entire period. The IBUS clocks start upon completion of the timeout.

Figure 16-3. System Clock Signals

### 16.2.3 Clocks in Stop Mode and Wait Mode

Upon exit from stop mode by an interrupt or reset, the SIM allows CGMXCLK to clock the SIM counter. The CPU and peripheral clocks do not become active until after the stop delay timeout. This timeout is selectable as 4096 or 32 CGMXCLK cycles. See 16.6.2 Stop Mode.

In wait mode, the CPU clocks are inactive. The SIM also produces two sets of clocks for other modules. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

#### Serial Peripheral Interface (SPI) Module

### 17.12.2 MOSI (Master Out/Slave In)

MOSI is one of the two SPI module pins that transmits serial data. In full-duplex operation, the MOSI pin of the master SPI module is connected to the MOSI pin of the slave SPI module. The master SPI simultaneously transmits data from its MOSI pin and receives data on its MISO pin.

When enabled, the SPI controls data direction of the MOSI pin regardless of the state of the data direction register of the shared I/O port.

### 17.12.3 SPSCK (Serial Clock)

The serial clock synchronizes data transmission between master and slave devices. In a master MCU, the SPSCK pin is the clock output. In a slave MCU, the SPSCK pin is the clock input. In full-duplex operation, the master and slave MCUs exchange a byte of data in eight serial clock cycles.

When enabled, the SPI controls data direction of the SPSCK pin regardless of the state of the data direction register of the shared I/O port.

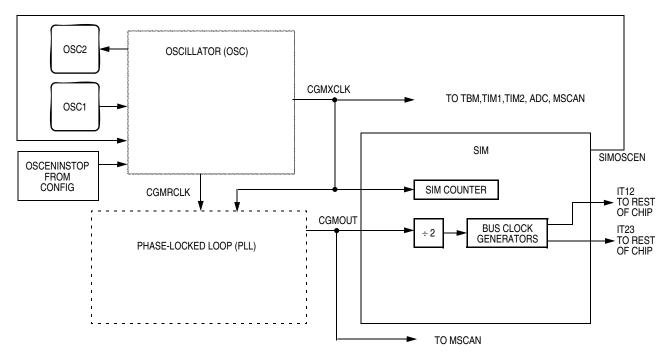

### 17.12.4 SS (Slave Select)

The  $\overline{SS}$  pin has various functions depending on the current state of the SPI. For an SPI configured as a slave, the  $\overline{SS}$  is used to select a slave. For CPHA = 0, the  $\overline{SS}$  is used to define the start of a transmission. (See 17.5 Transmission Formats.) Since it is used to indicate the start of a transmission, the  $\overline{SS}$  must be toggled high and low between each byte transmitted for the CPHA = 0 format. However, it can remain low between transmissions for the CPHA = 1 format. See Figure 17-13.

Figure 17-13. CPHA/SS Timing

When an SPI is configured as a slave, the  $\overline{SS}$  pin is always configured as an input. It cannot be used as a general-purpose I/O regardless of the state of the MODFEN control bit. However, the MODFEN bit can still prevent the state of the  $\overline{SS}$  from creating a MODF error. See 17.13.2 SPI Status and Control Register.

#### NOTE

A logic 1 voltage on the SS pin of a slave SPI puts the MISO pin in a high-impedance state. The slave SPI ignores all incoming SPSCK clocks, even if it was already in the middle of a transmission.

When an SPI is configured as a master, the SS input can be used in conjunction with the MODF flag to prevent multiple masters from driving MOSI and SPSCK. (See 17.7.2 Mode Fault Error.) For the state of the SS pin to set the MODF flag, the MODFEN bit in the SPSCK register must be set. If the MODFEN bit is low for an SPI master, the SS pin can be used as a general-purpose I/O under the control of the data direction register of the shared I/O port. With MODFEN high, it is an input-only pin to the SPI regardless of the state of the data direction register of the shared I/O port.

1. Ports are software configurable with pullup device if input port.

2. Higher current drive port pins

3. Pin contains integrated pullup device

#### Figure A-1. MC68HC908GZ8 Block Diagram