Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | HC08                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | CANbus, LINbus, SCI, SPI                                                 |

| Peripherals                | LVD, POR, PWM                                                            |

| Number of I/O              | 37                                                                       |

| Program Memory Size        | 16KB (16K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 48-LQFP                                                                  |

| Supplier Device Package    | 48-LQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908gz16mfa |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Memory

| Addr.                           | Register Name                                    |                 | Bit 7                     | 6                         | 5      | 4           | 3              | 2            | 1      | Bit 0                                        |

|---------------------------------|--------------------------------------------------|-----------------|---------------------------|---------------------------|--------|-------------|----------------|--------------|--------|----------------------------------------------|

| \$0024                          | Timer 1 Counter Modulo<br>Register Low (T1MODL)  | Read:<br>Write: | Bit 7                     | 6                         | 5      | 4           | 3              | 2            | 1      | Bit 0                                        |

|                                 | See page 267.                                    | Reset:          | 1                         | 1                         | 1      | 1           | 1              | 1            | 1      | 1                                            |

|                                 | Timer 1 Channel 0 Status and                     | Read:           | CH0F                      |                           | MOOD   | MCOA        |                |              |        | CLIOMAX                                      |

| \$0025 Control Register (T1SC0) | Write:                                           | 0               | CH0IE                     | MS0B                      | MS0A   | ELS0B       | ELS0A          | TOV0         | CH0MAX |                                              |

|                                 | See page 267.                                    | Reset:          | 0                         | 0                         | 0      | 0           | 0              | 0            | 0      | 0                                            |

| \$0026                          | Timer 1 Channel 0<br>Register High (T1CH0H)      | Read:<br>Write: | Bit 15                    | 14                        | 13     | 12          | 11             | 10           | 9      | Bit 8                                        |

|                                 | See page 270.                                    | Reset:          |                           |                           |        | Indetermina | te after reset |              | 1      |                                              |

| \$0027                          | Timer 1 Channel 0<br>Register Low (T1CH0L)       | Read:<br>Write: | Bit 7                     | 6                         | 5      | 4           | 3              | 2            | 1      | Bit 0                                        |

|                                 | See page 270.                                    | Reset:          |                           |                           |        | Indetermina | te after reset |              |        |                                              |

|                                 | Timer 1 Channel 1 Status and                     | Read:           | CH1F                      | CH1IE                     | 0      | MS1A        | ELS1B          | ELS1A        | TOV1   | CH1MAX                                       |

| \$0028                          | Control Register (T1SC1)                         | Write:          | 0                         | OTTIL                     |        |             | ELGID          | LLOIA        |        |                                              |

|                                 | See page 267.                                    | Reset:          | 0                         | 0                         | 0      | 0           | 0              | 0            | 0      | 0                                            |

| \$0029                          | Timer 1 Channel 1<br>Register High (T1CH1H)      | Read:<br>Write: | Bit 15                    | 14                        | 13     | 12          | 11             | 10           | 9      | Bit 8                                        |

|                                 | See page 270.                                    | Reset:          | Indeterminate after reset |                           |        |             |                |              |        |                                              |

| \$002A                          | Timer 1 Channel 1<br>Register Low (T1CH1L)       | Read:<br>Write: | Bit 7                     | 6                         | 5      | 4           | 3              | 2            | 1      | Bit 0                                        |

|                                 | See page 270.                                    | Reset:          |                           | Indeterminate after reset |        |             |                |              |        | <u>.                                    </u> |

|                                 | Timer 2 Status and Control                       | Read:           | TOF                       | TOIE                      | TSTOP  | 0           | 0              | PS2          | PS1    | PS0                                          |

| \$002B                          | Register (T2SC)                                  | Write:          | 0                         | TOIL                      | 10101  | TRST        |                | 1.02         | FOI    | 1.00                                         |

|                                 | See page 265.                                    | Reset:          | 0                         | 0                         | 1      | 0           | 0              | 0            | 0      | 0                                            |

|                                 | Timer 2 Counter                                  | Read:           | Bit 15                    | 14                        | 13     | 12          | 11             | 10           | 9      | Bit 8                                        |

| \$002C                          | Register High (T2CNTH)                           | Write:          |                           |                           |        |             |                |              |        |                                              |

|                                 | See page 266.                                    | Reset:          | 0                         | 0                         | 0      | 0           | 0              | 0            | 0      | 0                                            |

|                                 | Timer 2 Counter                                  | Read:           | Bit 7                     | 6                         | 5      | 4           | 3              | 2            | 1      | Bit 0                                        |

| \$002D                          | Register Low (T2CNTL)                            | Write:          |                           |                           |        |             |                |              |        |                                              |

|                                 | See page 266.                                    | Reset:          | 0                         | 0                         | 0      | 0           | 0              | 0            | 0      | 0                                            |

| \$002E                          | Timer 2 Counter Modulo<br>Register High (T2MODH) | Read:<br>Write: | Bit 15                    | 14                        | 13     | 12          | 11             | 10           | 9      | Bit 8                                        |

|                                 | See page 267.                                    | Reset:          | 1                         | 1                         | 1      | 1           | 1              | 1            | 1      | 1                                            |

| \$002F                          | Timer 2 Counter Modulo<br>Register Low (T2MODL)  | Read:<br>Write: | Bit 7                     | 6                         | 5      | 4           | 3              | 2            | 1      | Bit 0                                        |

|                                 | See page 267.                                    | Reset:          | 1                         | 1                         | 1      | 1           | 1              | 1            | 1      | 1                                            |

|                                 |                                                  |                 |                           | = Unimplem                | nented | R = Reserve | ed             | U = Unaffect | ted    |                                              |

#### Input/Output (I/O) Section

| Addr.  | Register Name                                            |                 | Bit 7                     | 6          | 5      | 4           | 3              | 2            | 1    | Bit 0  |

|--------|----------------------------------------------------------|-----------------|---------------------------|------------|--------|-------------|----------------|--------------|------|--------|

| \$0030 | Timer 2 Channel 0 Status and<br>Control Register (T2SC0) | Read:<br>Write: | CH0F<br>0                 | CH0IE      | MS0B   | MS0A        | ELS0B          | ELS0A        | TOV0 | CH0MAX |

|        | See page 267.                                            | Reset:          | 0                         | 0          | 0      | 0           | 0              | 0            | 0    | 0      |

| \$0031 | Timer 2 Channel 0<br>Register High (T2CH0H)              | Read:<br>Write: | Bit 15                    | 14         | 13     | 12          | 11             | 10           | 9    | Bit 8  |

|        | See page 270.                                            | Reset:          |                           |            |        | Indetermina | te after reset |              |      |        |

| \$0032 | Timer 2 Channel 0<br>Register Low (T2CH0L)               | Read:<br>Write: | Bit 7                     | 6          | 5      | 4           | 3              | 2            | 1    | Bit 0  |

|        | See page 270.                                            | Reset:          |                           |            |        | Indetermina | te after reset |              |      | ·      |

| \$0033 | Timer 2 Channel 1 Status and<br>Control Register (T2SC1) | Read:<br>Write: | CH1F<br>0                 | CH1IE      | 0      | MS1A        | ELS1B          | ELS1A        | TOV1 | CH1MAX |

|        | See page 267.                                            | Reset:          | 0                         | 0          | 0      | 0           | 0              | 0            | 0    | 0      |

| \$0034 | Timer 2 Channel 1<br>Register High (T2CH1H)              | Read:<br>Write: | Bit 15                    | 14         | 13     | 12          | 11             | 10           | 9    | Bit 8  |

|        | See page 270.                                            | Reset:          |                           |            |        | Indetermina | te after reset |              |      |        |

| \$0035 | Timer 2 Channel 1<br>Register Low (T2CH1L)               | Read:<br>Write: | Bit 7                     | 6          | 5      | 4           | 3              | 2            | 1    | Bit 0  |

|        | See page 270.                                            | Reset:          | Indeterminate after reset |            |        |             |                |              |      |        |

| \$0036 | PLL Control Register<br>(PCTL)                           | Read:<br>Write: | PLLIE                     | PLLF       | PLLON  | BCS         | R              | R            | VPR1 | VPR0   |

|        | See page 69.                                             | Reset:          | 0                         | 0          | 1      | 0           | 0              | 0            | 0    | 0      |

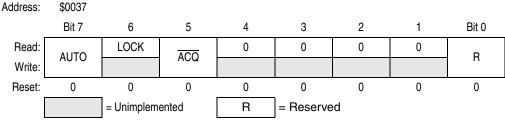

| \$0037 | PLL Bandwidth Control<br>Register (PBWC)                 | Read:<br>Write: | AUTO                      | LOCK       | ACQ    | 0           | 0              | 0            | 0    | R      |

|        | See page 71.                                             | Reset:          | 0                         | 0          | 0      | 0           | 0              | 0            | 0    | 0      |

| \$0038 | PLL Multiplier Select High<br>Register (PMSH)            | Read:<br>Write: | 0                         | 0          | 0      | 0           | MUL11          | MUL10        | MUL9 | MUL8   |

|        | See page 72.                                             | Reset:          | 0                         | 0          | 0      | 0           | 0              | 0            | 0    | 0      |

| \$0039 | PLL Multiplier Select Low<br>Register (PMSL)             | Read:<br>Write: | MUL7                      | MUL6       | MUL5   | MUL4        | MUL3           | MUL2         | MUL1 | MUL0   |

|        | See page 73.                                             | Reset:          | 0                         | 0          | 0      | 0           | U              | U            | U    | U      |

| \$003A | PLL VCO Select Range<br>Register (PMRS)                  | Read:<br>Write: | VRS7                      | VRS6       | VRS5   | VRS4        | VRS3           | VRS2         | VRS1 | VRS0   |

|        | See page 73.                                             | Reset:          | 0                         | 1          | 0      | 0           | 0              | 0            | 0    | 0      |

|        |                                                          | Read:           | 0                         | 0          | 0      | 0           | R              | R            | R    | R      |

| \$003B | Reserved                                                 | Write:          |                           |            |        |             |                |              |      |        |

|        |                                                          | Reset:          | 0                         | 0          | 0      | 0           | 0              | 0            | 0    | 1      |

|        |                                                          |                 |                           | = Unimplem | nented | R = Reserve | d              | U = Unaffect | ed   |        |

#### Memory

- 10. Clear the PGM bit.<sup>(1)</sup>

- 11. Wait for a time,  $t_{NVH}$  (minimum 5  $\mu$ s).

- 12. Clear the HVEN bit.

- 13. After time,  $t_{RCV}$  (typical 1  $\mu$ s), the memory can be accessed in read mode again.

This program sequence is repeated throughout the memory until all data is programmed.

#### NOTE

Programming and erasing of FLASH locations can not be performed by code being executed from the same FLASH array.

#### NOTE

While these operations must be performed in the order shown, other unrelated operations may occur between the steps. Care must be taken within the FLASH array memory space such as the COP control register (COPCTL) at \$FFFF.

#### NOTE

It is highly recommended that interrupts be disabled during program/ erase operations.

#### NOTE

Do not exceed  $t_{PROG}$  maximum or  $t_{HV}$  maximum.  $t_{HV}$  is defined as the cumulative high voltage programming time to the same row before next erase.  $t_{HV}$  must satisfy this condition:

$t_{NVS} + t_{NVH} + t_{PGS} + (t_{PROG} \times 32) \le t_{HV}$  maximum

Refer to 21.15 Memory Characteristics.

#### NOTE

The time between programming the FLASH address change (step 7 to step 7), or the time between the last FLASH programmed to clearing the PGM bit (step 7 to step 10) must not exceed the maximum programming time, t<sub>PROG</sub> maximum.

#### CAUTION

Be cautious when programming the FLASH array to ensure that non-FLASH locations are not used as the address that is written to when selecting either the desired row address range in step 3 of the algorithm or the byte to be programmed in step 7 of the algorithm. This applies particularly to \$FFD4-\$FFDF.

Memory

## 2.6.6 FLASH Block Protection

Due to the ability of the on-board charge pump to erase and program the FLASH memory in the target application, provision is made for protecting a block of memory from unintentional erase or program operations due to system malfunction. This protection is done by using of a FLASH block protect register (FLBPR). The FLBPR determines the range of the FLASH memory which is to be protected. The range of the protected area starts from a location defined by FLBPR and ends at the bottom of the FLASH memory (\$FFFF). When the memory is protected, the HVEN bit cannot be set in either ERASE or PROGRAM operations.

### NOTE

In performing a program or erase operation, the FLASH block protect register must be read after setting the PGM or ERASE bit and before asserting the HVEN bit

When the FLBPR is program with all 0's, the entire memory is protected from being programmed and erased. When all the bits are erased (all 1's), the entire memory is accessible for program and erase.

When bits within the FLBPR are programmed, they lock a block of memory, address ranges as shown in 2.6.7 FLASH Block Protect Register. Once the FLBPR is programmed with a value other than \$FF or \$FE, any erase or program of the FLBPR or the protected block of FLASH memory is prohibited. Mass erase is disabled whenever any block is protected (FLBPR does not equal \$FF). The presence of a  $V_{TST}$  on the IRQ pin will bypass the block protection so that all of the memory included in the block protect register is open for program and erase operations.

#### NOTE

The FLASH block protect register is not protected with special hardware or software. Therefore, if this page is not protected by FLBPR the register is erased by either a page or mass erase operation.

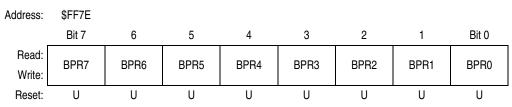

## 2.6.7 FLASH Block Protect Register

The FLASH block protect register (FLBPR) is implemented as a byte within the FLASH memory, and therefore can only be written during a programming sequence of the FLASH memory. The value in this register determines the starting location of the protected range within the FLASH memory.

U = Unaffected by reset. Initial value from factory is 1.

Write to this register is by a programming sequence to the FLASH memory.

## Figure 2-5. FLASH Block Protect Register (FLBPR)

## BPR[7:0] — FLASH Block Protect Bits

These eight bits represent bits [13:6] of a 16-bit memory address. Bit 15 and Bit 14 are 1s and bits [5:0] are 0s.

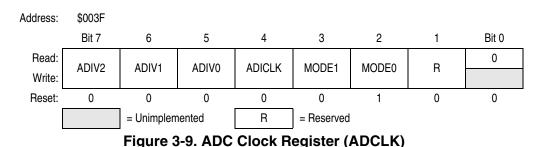

## 3.8.3 ADC Clock Register

The ADC clock register (ADCLK) selects the clock frequency for the ADC.

## ADIV2–ADIV0 — ADC Clock Prescaler Bits

ADIV2–ADIV0 form a 3-bit field which selects the divide ratio used by the ADC to generate the internal ADC clock. Table 3-2 shows the available clock configurations. The ADC clock should be set to approximately 1 MHz.

| ADIV2 | ADIV1            | ADIV0            | ADC Clock Rate       |

|-------|------------------|------------------|----------------------|

| 0     | 0                | 0                | ADC input clock ÷ 1  |

| 0     | 0                | 1                | ADC input clock ÷ 2  |

| 0     | 1                | 0                | ADC input clock ÷ 4  |

| 0     | 1                | 1                | ADC input clock ÷ 8  |

| 1     | X <sup>(1)</sup> | X <sup>(1)</sup> | ADC input clock ÷ 16 |

Table 3-2. ADC Clock Divide Ratio

1. X = Don't care

#### ADICLK — ADC Input Clock Select Bit

ADICLK selects either the bus clock or the oscillator output clock (CGMXCLK) as the input clock source to generate the internal ADC clock. Reset selects CGMXCLK as the ADC clock source.

1 = Internal bus clock

0 = Oscillator output clock (CGMXCLK)

The ADC requires a clock rate of approximately 1 MHz for correct operation. If the selected clock source is not fast enough, the ADC will generate incorrect conversions. See 21.10 5.0-Volt ADC Characteristics.

$f_{ADIC} = \frac{f_{CGMXCLK} \text{ or bus frequency}}{ADIV[2:0]} \cong 1 \text{ MHz}$

#### MODE1 and MODE0 — Modes of Result Justification Bits

MODE1 and MODE0 select among four modes of operation. The manner in which the ADC conversion results will be placed in the ADC data registers is controlled by these modes of operation. Reset returns right-justified mode.

00 = 8-bit truncation mode

01 = Right justified mode

10 = Left justified mode

11 = Left justified signed data mode

# Chapter 4 Clock Generator Module (CGM)

# 4.1 Introduction

This section describes the clock generator module. The CGM generates the crystal clock signal, CGMXCLK, which operates at the frequency of the crystal. The CGM also generates the base clock signal, CGMOUT, which is based on either the crystal clock divided by two or the phase-locked loop (PLL) clock, CGMVCLK, divided by two. In user mode, CGMOUT is the clock from which the SIM derives the system clocks, including the bus clock, which is at a frequency of CGMOUT/2. The PLL is a fully functional frequency generator designed for use with crystals or ceramic resonators. The PLL can generate a maximum bus frequency of 8 MHz using a 1-8MHz crystal or external clock source.

# 4.2 Features

Features of the CGM include:

- Phase-locked loop with output frequency in integer multiples of an integer dividend of the crystal reference

- High-frequency crystal operation with low-power operation and high-output frequency resolution

- Programmable hardware voltage-controlled oscillator (VCO) for low-jitter operation

- Automatic bandwidth control mode for low-jitter operation

- Automatic frequency lock detector

- CPU interrupt on entry or exit from locked condition

- Configuration register bit to allow oscillator operation during stop mode

# 4.3 Functional Description

The CGM consists of three major submodules:

- Crystal oscillator circuit The crystal oscillator circuit generates the constant crystal frequency clock, CGMXCLK.

- Phase-locked loop (PLL) The PLL generates the programmable VCO frequency clock, CGMVCLK.

- Base clock selector circuit This software-controlled circuit selects either CGMXCLK divided by two or the VCO clock, CGMVCLK, divided by two as the base clock, CGMOUT. The SIM derives the system clocks from either CGMOUT or CGMXCLK.

Figure 4-1 shows the structure of the CGM.

#### **Clock Generator Module (CGM)**

#### PLLIE — PLL Interrupt Enable Bit

This read/write bit enables the PLL to generate an interrupt request when the LOCK bit toggles, setting the PLL flag, PLLF. When the AUTO bit in the PLL bandwidth control register (PBWC) is clear, PLLIE cannot be written and reads as logic 0. Reset clears the PLLIE bit.

1 = PLL interrupts enabled

0 = PLL interrupts disabled

#### PLLF — PLL Interrupt Flag Bit

This read-only bit is set whenever the LOCK bit toggles. PLLF generates an interrupt request if the PLLIE bit also is set. PLLF always reads as logic 0 when the AUTO bit in the PLL bandwidth control register (PBWC) is clear. Clear the PLLF bit by reading the PLL control register. Reset clears the PLLF bit.

1 = Change in lock condition

0 = No change in lock condition

#### NOTE

Do not inadvertently clear the PLLF bit. Any read or read-modify-write operation on the PLL control register clears the PLLF bit.

#### PLLON — PLL On Bit

This read/write bit activates the PLL and enables the VCO clock, CGMVCLK. PLLON cannot be cleared if the VCO clock is driving the base clock, CGMOUT (BCS = 1). (See 4.3.8 Base Clock Selector Circuit.) Reset sets this bit so that the loop can stabilize as the MCU is powering up.

1 = PLL on

0 = PLL off

#### BCS — Base Clock Select Bit

This read/write bit selects either the crystal oscillator output, CGMXCLK, or the VCO clock, CGMVCLK, as the source of the CGM output, CGMOUT. CGMOUT frequency is one-half the frequency of the selected clock. BCS cannot be set while the PLLON bit is clear. After toggling BCS, it may take up to three CGMXCLK and three CGMVCLK cycles to complete the transition from one source clock to the other. During the transition, CGMOUT is held in stasis. (See 4.3.8 Base Clock Selector Circuit.) Reset clears the BCS bit.

1 = CGMVCLK divided by two drives CGMOUT

0 = CGMXCLK divided by two drives CGMOUT

#### NOTE

PLLON and BCS have built-in protection that prevents the base clock selector circuit from selecting the VCO clock as the source of the base clock if the PLL is off. Therefore, PLLON cannot be cleared when BCS is set, and BCS cannot be set when PLLON is clear. If the PLL is off (PLLON = 0), selecting CGMVCLK requires two writes to the PLL control register. (See 4.3.8 Base Clock Selector Circuit.).

#### **CGM Registers**

#### VPR1 and VPR0 — VCO Power-of-Two Range Select Bits

These read/write bits control the VCO's hardware power-of-two range multiplier E that, in conjunction with L controls the hardware center-of-range frequency, f<sub>VRS</sub>. VPR1:VPR0 cannot be written when the PLLON bit is set. Reset clears these bits. (See 4.3.3 PLL Circuits, 4.3.6 Programming the PLL, and 4.5.5 PLL VCO Range Select Register.)

| VPR1 and VPR0 | Е                | VCO Power-of-Two<br>Range Multiplier |

|---------------|------------------|--------------------------------------|

| 00            | 0                | 1                                    |

| 01            | 1                | 2                                    |

| 10            | 2 <sup>(1)</sup> | 4                                    |

#### Table 4-4. VPR1 and VPR0 Programming

1. Do not program E to a value of 3.

#### NOTE

Verify that the value of the VPR1 and VPR0 bits in the PCTL register are appropriate for the given reference and VCO clock frequencies before enabling the PLL. See 4.3.6 Programming the PLL for detailed instructions on selecting the proper value for these control bits.

## 4.5.2 PLL Bandwidth Control Register

The PLL bandwidth control register (PBWC):

- Selects automatic or manual (software-controlled) bandwidth control mode

- Indicates when the PLL is locked

- In automatic bandwidth control mode, indicates when the PLL is in acquisition or tracking mode

- In manual operation, forces the PLL into acquisition or tracking mode

#### AUTO — Automatic Bandwidth Control Bit

This read/write bit selects automatic or manual bandwidth control. When initializing the PLL for manual operation (AUTO = 0), clear the  $\overline{ACQ}$  bit before turning on the PLL. Reset clears the AUTO bit.

1 = Automatic bandwidth control

0 = Manual bandwidth control

#### LVISTOP — LVI Enable in Stop Mode Bit

When the LVIPWRD bit is clear, setting the LVISTOP bit enables the LVI to operate during stop mode. Reset clears LVISTOP.

1 = LVI enabled during stop mode

0 = LVI disabled during stop mode

#### LVIRSTD — LVI Reset Disable Bit

LVIRSTD disables the reset signal from the LVI module. See Chapter 11 Low-Voltage Inhibit (LVI).

1 = LVI module resets disabled

0 = LVI module resets enabled

#### LVIPWRD — LVI Power Disable Bit

LVIPWRD disables the LVI module. See Chapter 11 Low-Voltage Inhibit (LVI).

1 = LVI module power disabled

0 = LVI module power enabled

#### LVI5OR3 — LVI 5-V or 3-V Operating Mode Bit

LVI5OR3 selects the voltage operating mode of the LVI module (see Chapter 11 Low-Voltage Inhibit (LVI)). The voltage mode selected for the LVI should match the operating  $V_{DD}$  (see Chapter 21

Electrical Specifications) for the LVI's voltage trip points for each of the modes.

1 = LVI operates in 5-V mode

0 = LVI operates in 3-V mode

#### NOTE

The LVI5OR3 bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

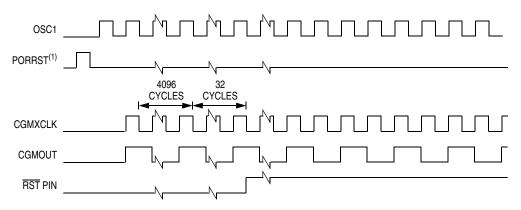

#### SSREC — Short Stop Recovery Bit

SSREC enables the CPU to exit stop mode with a delay of 32 CGMXCLK cycles instead of a 4096-CGMXCLK cycle delay.

1 = Stop mode recovery after 32 CGMXCLK cycles

0 = Stop mode recovery after 4096 CGMXCLCK cycles

#### NOTE

#### Exiting stop mode by an LVI reset will result in the long stop recovery.

If the system clock source selected is the internal oscillator or the external crystal and the OSCENINSTOP configuration bit is not set, the oscillator will be disabled during stop mode. The short stop recovery does not provide enough time for oscillator stabilization and for this reason the SSREC bit should not be set.

The system stabilization time for power-on reset and long stop recovery (both 4096 CGMXCLK cycles) gives a delay longer than the LVI enable time for these startup scenarios. There is no period where the MCU is not protected from a low-power condition. However, when using the short stop recovery configuration option, the 32-CGMXCLK delay must be greater than the LVI's turn on time to avoid a period in startup where the LVI is not protecting the MCU.

## STOP — STOP Instruction Enable Bit

STOP enables the STOP instruction.

1 = STOP instruction enabled

0 = STOP instruction treated as illegal opcode

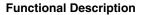

## 7.3.3 Stack Pointer

The stack pointer is a 16-bit register that contains the address of the next location on the stack. During a reset, the stack pointer is preset to \$00FF. The reset stack pointer (RSP) instruction sets the least significant byte to \$FF and does not affect the most significant byte. The stack pointer decrements as data is pushed onto the stack and increments as data is pulled from the stack.

In the stack pointer 8-bit offset and 16-bit offset addressing modes, the stack pointer can function as an index register to access data on the stack. The CPU uses the contents of the stack pointer to determine the conditional address of the operand.

Figure 7-4. Stack Pointer (SP)

#### NOTE

The location of the stack is arbitrary and may be relocated anywhere in random-access memory (RAM). Moving the SP out of page 0 (\$0000 to \$00FF) frees direct address (page 0) space. For correct operation, the stack pointer must point only to RAM locations.

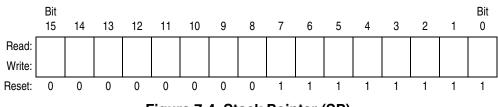

## 7.3.4 Program Counter

The program counter is a 16-bit register that contains the address of the next instruction or operand to be fetched.

Normally, the program counter automatically increments to the next sequential memory location every time an instruction or operand is fetched. Jump, branch, and interrupt operations load the program counter with an address other than that of the next sequential location.

During reset, the program counter is loaded with the reset vector address located at \$FFFE and \$FFFF. The vector address is the address of the first instruction to be executed after exiting the reset state.

Figure 7-5. Program Counter (PC)

# Chapter 11 Low-Voltage Inhibit (LVI)

# **11.1 Introduction**

This section describes the low-voltage inhibit (LVI) module, which monitors the voltage on the  $V_{DD}$  pin and can force a reset when the  $V_{DD}$  voltage falls below the LVI trip falling voltage,  $V_{TRIPF}$ .

# 11.2 Features

Features of the LVI module include:

- Programmable LVI reset

- Selectable LVI trip voltage

- Programmable stop mode operation

# **11.3 Functional Description**

Figure 11-1 shows the structure of the LVI module. The LVI is enabled out of reset. The LVI module contains a bandgap reference circuit and comparator. Clearing the LVI power disable bit, LVIPWRD, enables the LVI to monitor  $V_{DD}$  voltage. Clearing the LVI reset disable bit, LVIRSTD, enables the LVI module to generate a reset when  $V_{DD}$  falls below a voltage,  $V_{TRIPF}$ . Setting the LVI enable in stop mode bit, LVISTOP, enables the LVI to operate in stop mode. Setting the LVI 5-V or 3-V trip point bit, LVISOR3, enables the trip point voltage,  $V_{TRIPF}$ , to be configured for 5-V operation. Clearing the LVI5OR3 bit enables the trip point voltage,  $V_{TRIPF}$ , to be configured for 3-V operation. The actual trip points are shown in Chapter 21 Electrical Specifications.

#### NOTE

After a power-on reset (POR) the LVI's default mode of operation is 3 V. If a 5-V system is used, the user must set the LVI5OR3 bit to raise the trip point to 5-V operation. Note that this must be done after every power-on reset since the default will revert back to 3-V mode after each power-on reset. If the V<sub>DD</sub> supply is below the 5-V mode trip voltage but above the 3-V mode trip voltage when POR is released, the part will operate because V<sub>TRIPF</sub> defaults to 3-V mode after a POR. So, in a 5-V system care must be taken to ensure that V<sub>DD</sub> is above the 5-V mode trip voltage after POR is released.

If the user requires 5-V mode and sets the LVI5OR3 bit after a power-on reset while the  $V_{DD}$  supply is not above the  $V_{TRIPR}$  for 5-V mode, the microcontroller unit (MCU) will immediately go into reset. The LVI in this case will hold the part in reset until either  $V_{DD}$  goes above the rising 5-V trip point,  $V_{TRIPR}$ , which will release reset or  $V_{DD}$  decreases to approximately 0 V which will re-trigger the power-on reset and reset the trip point to 3-V operation.

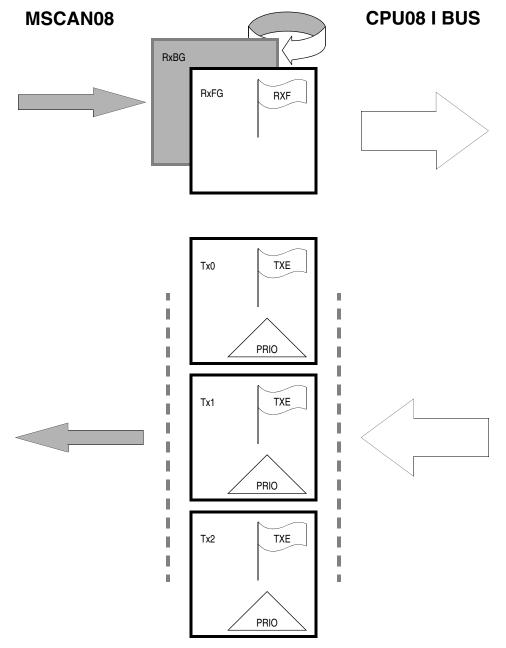

Figure 12-3. User Model for Message Buffer Organization

## 12.4.3 Transmit Structures

The MSCAN08 has a triple transmit buffer scheme to allow multiple messages to be set up in advance and to achieve an optimized real-time performance. The three buffers are arranged as shown in Figure 12-3.

All three buffers have a 13-byte data structure similar to the outline of the receive buffers (see 12.12 Programmer's Model of Message Storage). An additional transmit buffer priority register (TBPR) contains an 8-bit "local priority" field (PRIO) (see 12.12.5 Transmit Buffer Priority Registers).

#### **MSCAN08 Controller (MSCAN08)**

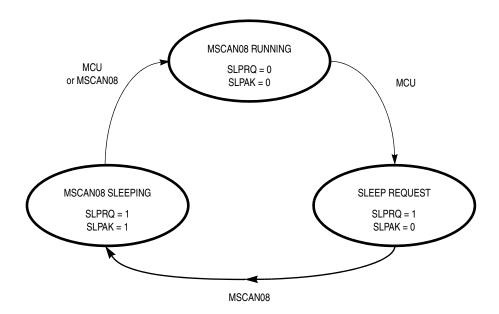

Figure 12-7. Sleep Request/Acknowledge Cycle

After wakeup, the MSCAN08 waits for 11 consecutive recessive bits to synchronize to the bus. As a consequence, if the MSCAN08 is woken-up by a CAN frame, this frame is not received. The receive message buffers (RxFG and RxBG) contain messages if they were received before sleep mode was entered. All pending actions are executed upon wakeup: copying of RxBG into RxFG, message aborts and message transmissions. If the MSCAN08 is still in bus-off state after sleep mode was left, it continues counting the 128\*11 consecutive recessive bits.

## 12.8.2 MSCAN08 Soft Reset Mode

In soft reset mode, the MSCAN08 is stopped. Registers can still be accessed. This mode is used to initialize the module configuration, bit timing and the CAN message filter. See 12.13.1 MSCAN08 Module Control Register 0 for a complete description of the soft reset mode.

When setting the SFTRES bit, the MSCAN08 immediately stops all ongoing transmissions and receptions, potentially causing CAN protocol violations.

NOTE

The user is responsible to take care that the MSCAN08 is not active when soft reset mode is entered. The recommended procedure is to bring the MSCAN08 into sleep mode before the SFTRES bit is set.

## 12.8.3 MSCAN08 Power-Down Mode

The MSCAN08 is in power-down mode when the CPU is in stop mode.

When entering the power-down mode, the MSCAN08 immediately stops all ongoing transmissions and receptions, potentially causing CAN protocol violations.

#### NOTE

The user is responsible to take care that the MSCAN08 is not active when power-down mode is entered. The recommended procedure is to bring the MSCAN08 into sleep mode before the STOP instruction is executed.

#### MSCAN08 Controller (MSCAN08)

| Addr.  | Register        | _               | Bit 7 | 6    | 5    | 4        | 3        | 2    | 1    | Bit 0 |

|--------|-----------------|-----------------|-------|------|------|----------|----------|------|------|-------|

| \$05b0 | IDR0            | Read:<br>Write: | ID28  | ID27 | ID26 | ID25     | ID24     | ID23 | ID22 | ID21  |

| \$05b1 | IDR1            | Read:<br>Write: | ID20  | ID19 | ID18 | SRR (=1) | IDE (=1) | ID17 | ID16 | ID15  |

| \$05b2 | IDR2            | Read:<br>Write: | ID14  | ID13 | ID12 | ID11     | ID10     | ID9  | ID8  | ID7   |

| \$05b3 | IDR3            | Read:<br>Write: | ID6   | ID5  | ID4  | ID3      | ID2      | ID1  | ID0  | RTR   |

| \$05b4 | DSR0            | Read:<br>Write: | DB7   | DB6  | DB5  | DB4      | DB3      | DB2  | DB1  | DB0   |

| \$05b5 | DSR1            | Read:<br>Write: | DB7   | DB6  | DB5  | DB4      | DB3      | DB2  | DB1  | DB0   |

| \$05b6 | DSR2            | Read:<br>Write: | DB7   | DB6  | DB5  | DB4      | DB3      | DB2  | DB1  | DB0   |

| \$05b7 | DSR3            | Read:<br>Write: | DB7   | DB6  | DB5  | DB4      | DB3      | DB2  | DB1  | DB0   |

| \$05b8 | DSR4            | Read:<br>Write: | DB7   | DB6  | DB5  | DB4      | DB3      | DB2  | DB1  | DB0   |

| \$05b9 | DSR5            | Read:<br>Write: | DB7   | DB6  | DB5  | DB4      | DB3      | DB2  | DB1  | DB0   |

| \$05bA | DSR6            | Read:<br>Write: | DB7   | DB6  | DB5  | DB4      | DB3      | DB2  | DB1  | DB0   |

| \$05bB | DSR7            | Read:<br>Write: | DB7   | DB6  | DB5  | DB4      | DB3      | DB2  | DB1  | DB0   |

| \$05bC | DLR             | Read:<br>Write: |       |      |      |          | DLC3     | DLC2 | DLC1 | DLC0  |

|        | = Unimplemented |                 |       |      |      |          |          |      |      |       |

## Figure 12-12. Receive/Transmit Message Buffer Extended Identifier (IDRn)

Input/Output (I/O) Ports

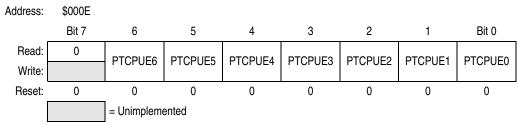

## 13.5.3 Port C Input Pullup Enable Register

The port C input pullup enable register (PTCPUE) contains a software configurable pullup device for each of the seven port C pins. Each bit is individually configurable and requires that the data direction register, DDRC, bit be configured as an input. Each pullup is automatically and dynamically disabled when a port bit's DDRC is configured for output mode.

## PTCPUE6–PTCPUE0 — Port C Input Pullup Enable Bits

These writable bits are software programmable to enable pullup devices on an input port bit.

- 1 = Corresponding port C pin configured to have internal pullup

- 0 = Corresponding port C pin internal pullup disconnected

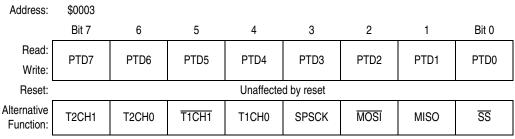

# 13.6 Port D

Port D is an 8-bit special-function port that shares four of its pins with the serial peripheral interface (SPI) module and four of its pins with the two timer interface (TIM1 and TIM2) modules. Port D also has software configurable pullup devices if configured as an input port.

## 13.6.1 Port D Data Register

The port D data register (PTD) contains a data latch for each of the eight port D pins.

Figure 13-13. Port D Data Register (PTD)

#### PTD7-PTD0 — Port D Data Bits

These read/write bits are software-programmable. Data direction of each port D pin is under the control of the corresponding bit in data direction register D. Reset has no effect on port D data.

#### T2CH1 and T2CH0 — Timer 2 Channel I/O Bits

The PTD7/T2CH1–PTD6/T2CH0 pins are the TIM2 input capture/output compare pins. The edge/level select bits, ELSxB:ELSxA, determine whether the PTD7/T2CH1–PTD6/T2CH0 pins are timer channel I/O pins or general-purpose I/O pins. See Chapter 19 Timer Interface Module (TIM).

#### Resets and Interrupts

## 14.2.3.1 Power-On Reset (POR)

A power-on reset (POR) is an internal reset caused by a positive transition on the  $V_{DD}$  pin.  $V_{DD}$  at the POR must go below  $V_{POR}$  to reset the MCU. This distinguishes between a reset and a POR. The POR is not a brown-out detector, low-voltage detector, or glitch detector.

A power-on reset:

- Holds the clocks to the central processor unit (CPU) and modules inactive for an oscillator stabilization delay of 4096 CGMXCLK cycles

- Drives the RST pin low during the oscillator stabilization delay

- · Releases the RST pin 32 CGMXCLK cycles after the oscillator stabilization delay

- Releases the CPU to begin the reset vector sequence 64 CGMXCLK cycles after the oscillator stabilization delay

- Sets the POR and LVI bits in the SIM reset status register and clears all other bits in the register

1. PORRST is an internally generated power-on reset pulse.

#### Figure 14-1. Power-On Reset Recovery

#### 14.2.3.2 Computer Operating Properly (COP) Reset

A computer operating properly (COP) reset is an internal reset caused by an overflow of the COP counter. A COP reset sets the COP bit in the SIM reset status register.

To clear the COP counter and prevent a COP reset, write any value to the COP control register at location \$FFFF.

#### 14.2.3.3 Low-Voltage Inhibit (LVI) Reset

A low-voltage inhibit (LVI) reset is an internal reset caused by a drop in the power supply voltage to the LVI<sub>TRIPF</sub> voltage.

An LVI reset:

- Holds the clocks to the CPU and modules inactive for an oscillator stabilization delay of 4096 CGMXCLK cycles after the power supply voltage rises to the LVI<sub>TRIPR</sub> voltage

- Drives the RST pin low for as long as V<sub>DD</sub> is below the LVI<sub>TRIPR</sub> voltage and during the oscillator stabilization delay

- Releases the RST pin 32 CGMXCLK cycles after the oscillator stabilization delay

- Releases the CPU to begin the reset vector sequence 64 CGMXCLK cycles after the oscillator stabilization delay

- Sets the LVI bit in the SIM reset status register

Enhanced Serial Communications Interface (ESCI) Module

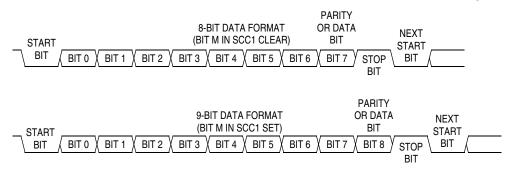

## 15.4.1 Data Format

The SCI uses the standard non-return-to-zero mark/space data format illustrated in Figure 15-4.

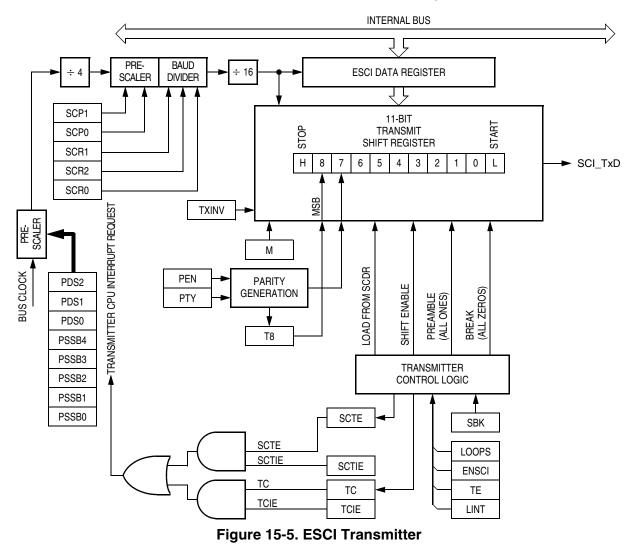

## 15.4.2 Transmitter

Figure 15-5 shows the structure of the SCI transmitter and the registers are summarized in Figure 15-3. The baud rate clock source for the ESCI can be selected via the configuration bit, ESCIBDSRC.

# Chapter 19 Timer Interface Module (TIM)

# **19.1 Introduction**

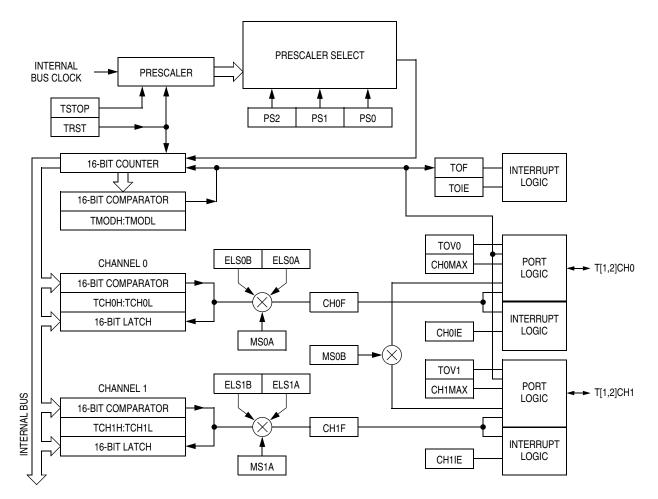

This section describes the timer interface (TIM) module. The TIM is a two-channel timer that provides a timing reference with input capture, output compare, and pulse-width-modulation functions. Figure 19-1 is a block diagram of the TIM.

This particular MCU has two timer interface modules which are denoted as TIM1 and TIM2.

# Chapter 22 Ordering Information and Mechanical Specifications

# 22.1 Introduction

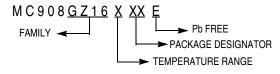

This section provides ordering information for the MC68HC908GZ16 along with the dimensions for:

- 32-pin low-profile quad flat pack package (case 873A)

- 48-pin low-profile quad flat pack (case 932-03)

The following figures show the latest package drawings at the time of this publication. To make sure that you have the latest package specifications, contact your local Freescale Semiconductor Sales Office.

# 22.2 MC Order Numbers

| MC Order Number | Operating<br>Temperature Range | Package            |

|-----------------|--------------------------------|--------------------|

| MC908GZ16CFJ    | –40°C to +85°C                 | 32-pin low-profile |

| MC908GZ16VFJ    | –40°C to +105°C                | quad flat package  |

| MC908GZ16MFJ    | –40°C to +125°C                | (LQFP)             |

| MC908GZ16CFA    | –40°C to +85°C                 | 48-pin low-profile |

| MC908GZ16VFA    | –40°C to +105°C                | quad flat package  |

| MC908GZ16MFA    | –40°C to +125°C                | (LQFP)             |

Table 22-1. MC Order Numbers

Temperature designators:  $C = -40^{\circ}C$  to  $+85^{\circ}C$  $V = -40^{\circ}C$  to  $+105^{\circ}C$

$M = -40^{\circ}C \text{ to } + 105^{\circ}C$ M = -40°C to +125°C

#### Figure 22-1. Device Numbering System

# 22.3 Package Dimensions

Refer to the following pages for detailed package dimensions.

NOTES:

- 1. DIMENSIONS AND TOLERANCING PER ASME Y14.5M-1994.

- 2. CONTROLLING DIMENSION: MILLIMETER.

- 3. DATUM PLANE AB IS LOCATED AT BOTTOM OF LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOM OF THE PARTING LINE.

- 4. DATUMS T, U, AND Z TO BE DETERMINED AT DATUM PLANE AB.

$\mathbf{X}$  dimensions to be determined at seating plane ac.

6. DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.250 PER SIDE. DIMENSIONS DO INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE AB.

THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.350.

8. MINIMUM SOLDER PLATE THICKNESS SHALL BE 0.0076.

9. EXACT SHAPE OF EACH CORNER IS OPTIONAL.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | LOUTLINE          | PRINT VERSION NO           | DT TO SCALE    |             |

|---------------------------------------------------------|-------------------|----------------------------|----------------|-------------|

| TITLE:                                                  |                   | DOCUMENT NO                | ): 98ASH00962A | REV: G      |

| LQFP, 48 LEAD, 0.50 PITCH                               |                   | CASE NUMBER: 932–03 14 APR |                | 14 APR 2005 |

|                                                         | (7.0 X 7.0 X 1.4) |                            |                |             |