Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | HC08                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | CANbus, LINbus, SCI, SPI                                                |

| Peripherals                | LVD, POR, PWM                                                           |

| Number of I/O              | 37                                                                      |

| Program Memory Size        | 8KB (8K x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908gz8vfa |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

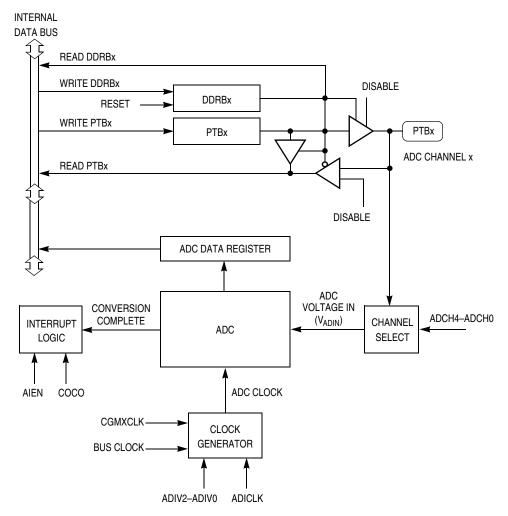

Figure 3-2. ADC Block Diagram

## 3.3.2 Voltage Conversion

When the input voltage to the ADC equals  $V_{REFH}$ , the ADC converts the signal to \$3FF (full scale). If the input voltage equals  $V_{REFL}$ , the ADC converts it to \$000. Input voltages between  $V_{REFH}$  and  $V_{REFL}$  are a straight-line linear conversion.

#### NOTE

The ADC input voltage must always be greater than  $V_{SSAD}$  and less than  $V_{DDAD}$ .

Connect the  $V_{DDAD}$  pin to the same voltage potential as the  $V_{DD}$  pin, and connect the  $V_{SSAD}$  pin to the same voltage potential as the  $V_{SS}$  pin.

The  $V_{DDAD}$  pin should be routed carefully for maximum noise immunity.

#### **Analog-to-Digital Converter (ADC)**

#### 3.3.3 Conversion Time

Conversion starts after a write to the ADC status and control register (ADSCR). One conversion will take between 16 and 17 ADC clock cycles. The ADIVx and ADICLK bits should be set to provide a 1-MHz ADC clock frequency.

Conversion time =

$$\frac{16 \text{ to } 17 \text{ ADC cycles}}{\text{ADC frequency}}$$

Number of bus cycles = conversion time  $\times$  bus frequency

#### 3.3.4 Conversion

In continuous conversion mode, the ADC data register will be filled with new data after each conversion. Data from the previous conversion will be overwritten whether that data has been read or not. Conversions will continue until the ADCO bit is cleared. The COCO bit is set after each conversion and will stay set until the next read of the ADC data register.

In single conversion mode, conversion begins with a write to the ADSCR. Only one conversion occurs between writes to the ADSCR.

When a conversion is in process and the ADCSCR is written, the current conversion data should be discarded to prevent an incorrect reading.

## 3.3.5 Accuracy and Precision

The conversion process is monotonic and has no missing codes.

#### 3.3.6 Result Justification

The conversion result may be formatted in four different ways:

- 1. Left justified

- 2. Right justified

- 3. Left Justified sign data mode

- 4. 8-bit truncation mode

All four of these modes are controlled using MODE0 and MODE1 bits located in the ADC clock register (ADCLK).

Left justification will place the eight most significant bits (MSB) in the corresponding ADC data register high, ADRH. This may be useful if the result is to be treated as an 8-bit result where the two least significant bits (LSB), located in the ADC data register low, ADRL, can be ignored. However, ADRL must be read after ADRH or else the interlocking will prevent all new conversions from being stored.

Right justification will place only the two MSBs in the corresponding ADC data register high, ADRH, and the eight LSBs in ADC data register low, ADRL. This mode of operation typically is used when a 10-bit unsigned result is desired.

Left justified sign data mode is similar to left justified mode with one exception. The MSB of the 10-bit result, AD9 located in ADRH, is complemented. This mode of operation is useful when a result, represented as a signed magnitude from mid-scale, is needed. Finally, 8-bit truncation mode will place the eight MSBs in the ADC data register low, ADRL. The two LSBs are dropped. This mode of operation

## 4.4 I/O Signals

The following paragraphs describe the CGM I/O signals.

## 4.4.1 Crystal Amplifier Input Pin (OSC1)

The OSC1 pin is an input to the crystal oscillator amplifier.

## 4.4.2 Crystal Amplifier Output Pin (OSC2)

The OSC2 pin is the output of the crystal oscillator inverting amplifier.

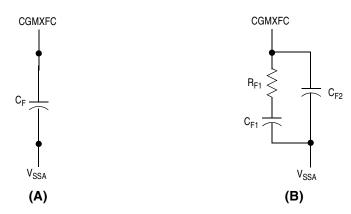

## 4.4.3 External Filter Capacitor Pin (CGMXFC)

The CGMXFC pin is required by the loop filter to filter out phase corrections. An external filter network is connected to this pin. (See Figure 4-2.)

#### NOTE

To prevent noise problems, the filter network should be placed as close to the CGMXFC pin as possible, with minimum routing distances and no routing of other signals across the network.

## 4.4.4 PLL Analog Power Pin (V<sub>DDA</sub>)

$V_{DDA}$  is a power pin used by the analog portions of the PLL. Connect the  $V_{DDA}$  pin to the same voltage potential as the  $V_{DD}$  pin.

#### NOTE

Route  $V_{DDA}$  carefully for maximum noise immunity and place bypass capacitors as close as possible to the package.

## 4.4.5 PLL Analog Ground Pin (V<sub>SSA</sub>)

$V_{SSA}$  is a ground pin used by the analog portions of the PLL. Connect the  $V_{SSA}$  pin to the same voltage potential as the  $V_{SS}$  pin.

#### NOTE

Route  $V_{SSA}$  carefully for maximum noise immunity and place bypass capacitors as close as possible to the package.

## 4.4.6 Oscillator Enable Signal (SIMOSCEN)

The SIMOSCEN signal comes from the system integration module (SIM) and enables the oscillator and PLL.

## 4.4.7 Oscillator Stop Mode Enable Bit (OSCSTOPENB)

OSCSTOPENB is a bit in the CONFIG register that enables the oscillator to continue operating during stop mode. If this bit is set, the Oscillator continues running during stop mode. If this bit is not set (default), the oscillator is controlled by the SIMOSCEN signal which will disable the oscillator during stop mode.

Figure 4-9. PLL Filter

**Table 4-5. Example Filter Component Values**

| f <sub>RCLK</sub> | C <sub>F1</sub> | C <sub>F2</sub> | R <sub>F1</sub> | C <sub>F</sub> |

|-------------------|-----------------|-----------------|-----------------|----------------|

| 1 MHz             | 8.2 nF          | 820 pF          | 2k              | 18 nF          |

| 2 MHz             | 4.7 nF          | 470 pF          | 2k              | 6.8 nF         |

| 3 MHz             | 3.3 nF          | 330 pF          | 2k              | 5.6 nF         |

| 4 MHz             | 2.2 nF          | 220 pF          | 2k              | 4.7 nF         |

| 5 MHz             | 1.8 nF          | 180 pF          | 2k              | 3.9 nF         |

| 6 MHz             | 1.5 nF          | 150 pF          | 2k              | 3.3 nF         |

| 7 MHz             | 1.2 nF          | 120 pF          | 2k              | 2.7 nF         |

| 8 MHz             | 1 nF            | 100 pF          | 2k              | 2.2 nF         |

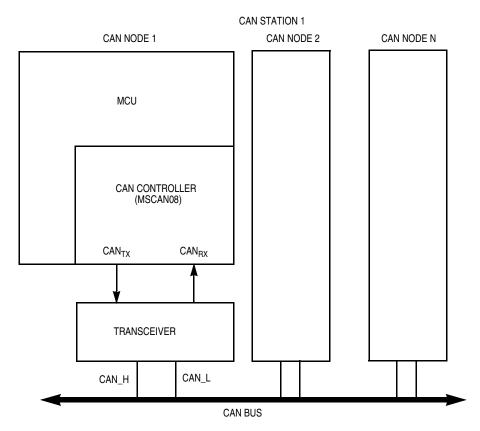

Figure 12-2. The CAN System

Each CAN station is connected physically to the CAN bus lines through a transceiver chip. The transceiver is capable of driving the large current needed for the CAN and has current protection against defected CAN or defected stations.

## 12.4 Message Storage

MSCAN08 facilitates a sophisticated message storage system which addresses the requirements of a broad range of network applications.

## 12.4.1 Background

Modern application layer software is built under two fundamental assumptions:

- Any CAN node is able to send out a stream of scheduled messages without releasing the bus between two messages. Such nodes will arbitrate for the bus right after sending the previous message and will only release the bus in case of lost arbitration.

- 2. The internal message queue within any CAN node is organized as such that the highest priority message will be sent out first if more than one message is ready to be sent.

Above behavior cannot be achieved with a single transmit buffer. That buffer must be reloaded right after the previous message has been sent. This loading process lasts a definite amount of time and has to be completed within the inter-frame sequence (IFS) to be able to send an uninterrupted stream of messages. Even if this is feasible for limited CAN bus speeds, it requires that the CPU reacts with short latencies to the transmit interrupt.

MC68HC908GZ16 • MC68HC908GZ8 Data Sheet, Rev. 4

#### **MSCAN08 Controller (MSCAN08)**

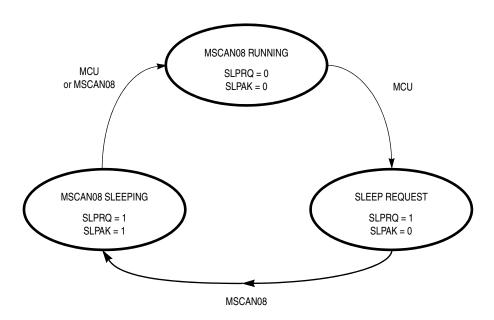

Figure 12-7. Sleep Request/Acknowledge Cycle

After wakeup, the MSCAN08 waits for 11 consecutive recessive bits to synchronize to the bus. As a consequence, if the MSCAN08 is woken-up by a CAN frame, this frame is not received. The receive message buffers (RxFG and RxBG) contain messages if they were received before sleep mode was entered. All pending actions are executed upon wakeup: copying of RxBG into RxFG, message aborts and message transmissions. If the MSCAN08 is still in bus-off state after sleep mode was left, it continues counting the 128\*11 consecutive recessive bits.

#### 12.8.2 MSCAN08 Soft Reset Mode

In soft reset mode, the MSCAN08 is stopped. Registers can still be accessed. This mode is used to initialize the module configuration, bit timing and the CAN message filter. See 12.13.1 MSCAN08 Module Control Register 0 for a complete description of the soft reset mode.

When setting the SFTRES bit, the MSCAN08 immediately stops all ongoing transmissions and receptions, potentially causing CAN protocol violations.

#### NOTE

The user is responsible to take care that the MSCAN08 is not active when soft reset mode is entered. The recommended procedure is to bring the MSCAN08 into sleep mode before the SFTRES bit is set.

#### 12.8.3 MSCAN08 Power-Down Mode

The MSCAN08 is in power-down mode when the CPU is in stop mode.

When entering the power-down mode, the MSCAN08 immediately stops all ongoing transmissions and receptions, potentially causing CAN protocol violations.

#### NOTE

The user is responsible to take care that the MSCAN08 is not active when power-down mode is entered. The recommended procedure is to bring the MSCAN08 into sleep mode before the STOP instruction is executed.

MC68HC908GZ16 • MC68HC908GZ8 Data Sheet, Rev. 4

## 12.12 Programmer's Model of Message Storage

This section details the organization of the receive and transmit message buffers and the associated control registers. For reasons of programmer interface simplification, the receive and transmit message buffers have the same outline. Each message buffer allocates 16 bytes in the memory map containing a 13-byte data structure. An additional transmit buffer priority register (TBPR) is defined for the transmit buffers.

| Addr <sup>(1)</sup> | Register Name                                    |

|---------------------|--------------------------------------------------|

| \$05b0              | IDENTIFIER REGISTER 0                            |

| \$05b1              | IDENTIFIER REGISTER 1                            |

| \$05b2              | IDENTIFIER REGISTER 2                            |

| \$05b3              | IDENTIFIER REGISTER 3                            |

| \$05b4              | DATA SEGMENT REGISTER 0                          |

| \$05b5              | DATA SEGMENT REGISTER 1                          |

| \$05b6              | DATA SEGMENT REGISTER 2                          |

| \$05b7              | DATA SEGMENT REGISTER 3                          |

| \$05b8              | DATA SEGMENT REGISTER 4                          |

| \$05b9              | DATA SEGMENT REGISTER 5                          |

| \$05bA              | DATA SEGMENT REGISTER 6                          |

| \$05bB              | DATA SEGMENT REGISTER 7                          |

| \$05bC              | DATA LENGTH REGISTER                             |

| \$05bD              | TRANSMIT BUFFER PRIORITY REGISTER <sup>(2)</sup> |

| \$05bE              | UNUSED                                           |

| \$05bF              | UNUSED                                           |

<sup>1.</sup> Where b equals the following:

Figure 12-11. Message Buffer Organization

## 12.12.1 Message Buffer Outline

Figure 12-12 shows the common 13-byte data structure of receive and transmit buffers for extended identifiers. The mapping of standard identifiers into the IDR registers is shown in Figure 12-13. All bits of the 13-byte data structure are undefined out of reset.

#### NOTE

The foreground receive buffer can be read anytime but cannot be written. The transmit buffers can be read or written anytime.

b=4 for receive buffer

b=5 for transmit buffer 0

b=6 for transmit buffer 1

b=7 for transmit buffer 2

<sup>2.</sup> Not applicable for receive buffers

**MSCAN08 Controller (MSCAN08)**

## 12.13.8 MSCAN08 Transmitter Control Register

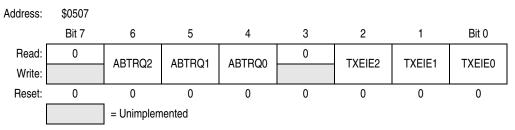

Figure 12-23. Transmitter Control Register (CTCR)

## ABTRQ2-ABTRQ0 — Abort Request

The CPU sets an ABTRQx bit to request that an already scheduled message buffer (TXE = 0) be aborted. The MSCAN08 will grant the request if the message has not already started transmission, or if the transmission is not successful (lost arbitration or error). When a message is aborted the associated TXE and the abort acknowledge flag (ABTAK) (see 12.13.7 MSCAN08 Transmitter Flag Register) will be set and an TXE interrupt is generated if enabled. The CPU cannot reset ABTRQx. ABTRQx is cleared implicitly whenever the associated TXE flag is set.

- 1 = Abort request pending

- 0 = No abort request

#### NOTE

The software must not clear one or more of the TXE flags in CTFLG and simultaneously set the respective ABTRQ bit(s).

### TXEIE2-TXEIE0 — Transmitter Empty Interrupt Enable

- 1 = A transmitter empty (transmit buffer available for transmission) event results in a transmitter empty interrupt.

- 0 = No interrupt is generated from this event.

#### NOTE

The CTCR register is held in the reset state when the SFTRES bit in CMCR0 is set.

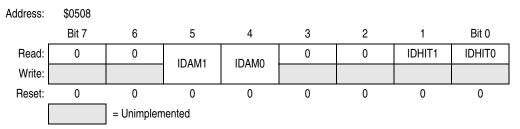

## 12.13.9 MSCAN08 Identifier Acceptance Control Register

Figure 12-24. Identifier Acceptance Control Register (CIDAC)

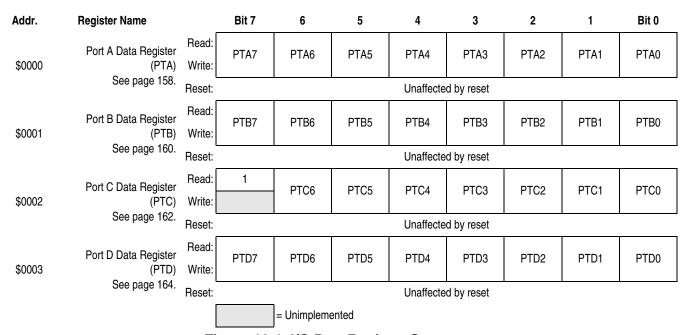

## Chapter 13 Input/Output (I/O) Ports

## 13.1 Introduction

Bidirectional input-output (I/O) pins form five parallel ports. All I/O pins are programmable as inputs or outputs. All individual bits within port A, port C, and port D are software configurable with pullup devices if configured as input port bits. The pullup devices are automatically and dynamically disabled when a port bit is switched to output mode.

## 13.2 Unused Pin Termination

Input pins and I/O port pins that are not used in the application must be terminated. This prevents excess current caused by floating inputs, and enhances immunity during noise or transient events. Termination methods include:

- 1. Configuring unused pins as outputs and driving high or low;

- 1. Configuring unused pins as inputs and enabling internal pull-ups;

- 1. Configuring unused pins as inputs and using external pull-up or pull-down resistors.

Never connect unused pins directly to V<sub>DD</sub> or V<sub>SS</sub>.

Since some general-purpose I/O pins are not available on all packages, these pins must be terminated as well. Either method 1 or 2 above are appropriate.

Figure 13-1. I/O Port Register Summary

MC68HC908GZ16 • MC68HC908GZ8 Data Sheet, Rev. 4

## Input/Output (I/O) Ports

| Addr.                                  | Register Name                                          |                 | Bit 7   | 6               | 5       | 4                   | 3       | 2       | 1       | Bit 0   |

|----------------------------------------|--------------------------------------------------------|-----------------|---------|-----------------|---------|---------------------|---------|---------|---------|---------|

| \$0004                                 |                                                        |                 | DDRA7   | DDRA6           | DDRA5   | DDRA4               | DDRA3   | DDRA2   | DDRA1   | DDRA0   |

|                                        | See page 158.                                          | Reset:          | 0       | 0               | 0       | 0                   | 0       | 0       | 0       | 0       |

| \$0005                                 | Data Direction Register B (DDRB)                       | Read:<br>Write: | DDRB7   | DDRB6           | DDRB5   | DDRB4               | DDRB3   | DDRB2   | DDRB1   | DDRB0   |

|                                        | See page 161.                                          | Reset:          | 0       | 0               | 0       | 0                   | 0       | 0       | 0       | 0       |

|                                        | Data Direction Register C                              | Read:           | 0       | DDRC6           | DDRC5   | DDBC4               | DDBC3   | DDBCa   | DDBC1   | DDBC0   |

| \$0006                                 | (DDRC)                                                 | Write:          |         | DDRC0           | DDRCS   | DDRC4               | DDRC3   | DDRC2   | DDRC1   | DDRC0   |

|                                        | See page 162.                                          | Reset:          | 0       | 0               | 0       | 0                   | 0       | 0       | 0       | 0       |

| \$0007                                 | Data Direction Register D<br>\$0007 (DDRD)             | Read:<br>Write: | DDRD7   | DDRD6           | DDRD5   | DDRD4               | DDRD3   | DDRD2   | DDRD1   | DDRD0   |

|                                        | See page 165.                                          | Reset:          | 0       | 0               | 0       | 0                   | 0       | 0       | 0       | 0       |

|                                        | Port E Data Register                                   | Read:           | 0       | 0               | DTE     | DTE4                | DTEO    | DTEO    | DTE4    | DTEO    |

| \$0008 (PTE)                           | (PTE)                                                  | Write:          |         |                 | PTE5    | PTE4                | PTE3    | PTE2    | PTE1    | PTE0    |

|                                        | See page 167.                                          | Reset:          |         |                 |         | Unaffected by reset |         |         |         |         |

|                                        | Data Direction Register E                              | Read:           | 0       | 0               | DDRE5   | DDRE4               | DDRE3   | DDRE2   | DDRE1   | DDRE0   |

| \$000C                                 | (DDRE)                                                 | Write:          |         |                 | DDNES   | DDITE               | DDITES  | DDNEZ   | DDNEI   | מחטבט   |

|                                        | See page 168.                                          | Reset:          | 0       | 0               | 0       | 0                   | 0       | 0       | 0       | 0       |

| \$000D                                 | Port A Input Pullup Enable<br>\$000D Register (PTAPUE) | Read:<br>Write: | PTAPUE7 | PTAPUE6         | PTAPUE5 | PTAPUE4             | PTAPUE3 | PTAPUE2 | PTAPUE1 | PTAPUE0 |

|                                        | See page 159.                                          | Reset:          | 0       | 0               | 0       | 0                   | 0       | 0       | 0       | 0       |

|                                        | Port C Input Pullup Enable                             | Read:           | 0       |                 |         |                     |         |         |         |         |

| \$000E Register (PTCPUE) See page 164. | Write:                                                 |                 | PTCPUE6 | PTCPUE6 PTCPUE5 | PTCPUE4 | PTCPUE3             | PTCPUE2 | PTCPUE1 | PTCPUE0 |         |

|                                        | Reset:                                                 | 0               | 0       | 0               | 0       | 0                   | 0       | 0       | 0       |         |

| \$000F                                 |                                                        | Read:<br>Write: | PTDPUE7 | PTDPUE6         | PTDPUE5 | PTDPUE4             | PTDPUE3 | PTDPUE2 | PTDPUE1 | PTDPUE0 |

|                                        | See page 166.                                          | Reset:          | 0       | 0               | 0       | 0                   | 0       | 0       | 0       | 0       |

|                                        |                                                        |                 |         | = Unimplem      | ented   |                     |         |         |         |         |

Figure 13-1. I/O Port Register Summary (Continued)

## **Chapter 14 Resets and Interrupts**

## 14.1 Introduction

Resets and interrupts are responses to exceptional events during program execution. A reset re-initializes the microcontroller (MCU) to its startup condition. An interrupt vectors the program counter to a service routine.

## 14.2 Resets

A reset immediately returns the MCU to a known startup condition and begins program execution from a user-defined memory location.

#### 14.2.1 Effects

#### A reset:

- Immediately stops the operation of the instruction being executed

- Initializes certain control and status bits

- Loads the program counter with a user-defined reset vector address from locations \$FFFE and \$FFFF

- Selects CGMXCLK divided by four as the bus clock

#### 14.2.2 External Reset

A logic 0 applied to the  $\overline{RST}$  pin for a time,  $t_{RL}$ , generates an external reset. An external reset sets the PIN bit in the system integration module (SIM) reset status register.

#### 14.2.3 Internal Reset

#### Sources:

- Power-on reset (POR)

- Computer operating properly (COP)

- Low-power reset circuits

- Illegal opcode

- Illegal address

All internal reset sources pull the  $\overline{RST}$  pin low for 32 CGMXCLK cycles to allow resetting of external devices. The MCU is held in reset for an additional 32 CGMXCLK cycles after releasing the  $\overline{RST}$  pin.

169

#### Resets and Interrupts

#### 14.3.2.3 TRQ Pin

A logic 0 on the IRQ1 pin latches an external interrupt request.

## 14.3.2.4 Clock Generator (CGM)

The CGM can generate a CPU interrupt request every time the phase-locked loop circuit (PLL) enters or leaves the locked state. When the LOCK bit changes state, the PLL flag (PLLF) is set. The PLL interrupt enable bit (PLLIE) enables PLLF CPU interrupt requests. LOCK is in the PLL bandwidth control register. PLLF is in the PLL control register.

#### 14.3.2.5 Timer Interface Module 1 (TIM1)

TIM1 CPU interrupt sources:

- TIM1 overflow flag (TOF) The TOF bit is set when the TIM1 counter value rolls over to \$0000 after matching the value in the TIM1 counter modulo registers. The TIM1 overflow interrupt enable bit, TOIE, enables TIM1 overflow CPU interrupt requests. TOF and TOIE are in the TIM1 status and control register.

- TIM1 channel flags (CH1F–CH0F) The CHxF bit is set when an input capture or output compare occurs on channel x. The channel x interrupt enable bit, CHxIE, enables channel x TIM1 CPU interrupt requests. CHxF and CHxIE are in the TIM1 channel x status and control register.

## 14.3.2.6 Timer Interface Module 2 (TIM2)

TIM2 CPU interrupt sources:

- TIM2 overflow flag (TOF) The TOF bit is set when the TIM2 counter value rolls over to \$0000 after matching the value in the TIM2 counter modulo registers. The TIM2 overflow interrupt enable bit, TOIE, enables TIM2 overflow CPU interrupt requests. TOF and TOIE are in the TIM2 status and control register.

- TIM2 channel flags (CH1F–CH0F) The CHxF bit is set when an input capture or output compare occurs on channel x. The channel x interrupt enable bit, CHxIE, enables channel x TIM2 CPU interrupt requests. CHxF and CHxIE are in the TIM2 channel x status and control register.

#### 14.3.2.7 Serial Peripheral Interface (SPI)

SPI CPU interrupt sources:

- SPI receiver full bit (SPRF) The SPRF bit is set every time a byte transfers from the shift register

to the receive data register. The SPI receiver interrupt enable bit, SPRIE, enables SPRF CPU

interrupt requests. SPRF is in the SPI status and control register and SPRIE is in the SPI control

register.

- SPI transmitter empty (SPTE) The SPTE bit is set every time a byte transfers from the transmit data register to the shift register. The SPI transmit interrupt enable bit, SPTIE, enables SPTE CPU interrupt requests. SPTE is in the SPI status and control register and SPTIE is in the SPI control register.

- Mode fault bit (MODF) The MODF bit is set in a slave SPI if the SS pin goes high during a transmission with the mode fault enable bit (MODFEN) set. In a master SPI, the MODF bit is set if the SS pin goes low at any time with the MODFEN bit set. The error interrupt enable bit, ERRIE, enables MODF CPU interrupt requests. MODF, MODFEN, and ERRIE are in the SPI status and control register.

MC68HC908GZ16 • MC68HC908GZ8 Data Sheet, Rev. 4

**System Integration Module (SIM)**

## 16.3 Reset and System Initialization

The MCU has these reset sources:

- Power-on reset module (POR)

- External reset pin (RST)

- Computer operating properly module (COP)

- Low-voltage inhibit module (LVI)

- Illegal opcode

- Illegal address

- Forced monitor mode entry reset (MODRST)

All of these resets produce the vector \$FFFE:\$FFFF (\$FEFE:\$FEFF in monitor mode) and assert the internal reset signal (IRST). IRST causes all registers to be returned to their default values and all modules to be returned to their reset states.

An internal reset clears the SIM counter (see 16.4 SIM Counter), but an external reset does not. Each of the resets sets a corresponding bit in the SIM reset status register (SRSR). See 16.7 SIM Registers.

#### 16.3.1 External Pin Reset

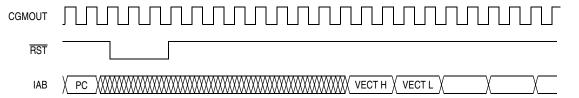

The RST pin circuit includes an internal pullup device. Pulling the asynchronous RST pin low halts all processing. The PIN bit of the SIM reset status register (SRSR) is set as long as RST is held low for a minimum of 67 CGMXCLK cycles, assuming that neither the POR nor the LVI was the source of the reset. See Table 16-2 for details. Figure 16-4 shows the relative timing.

Table 16-2. PIN Bit Set Timing

| Reset Type | Number of Cycles Required to Set PIN |

|------------|--------------------------------------|

| POR/LVI    | 4163 (4096 + 64 + 3)                 |

| All others | 67 (64 + 3)                          |

Figure 16-4. External Reset Timing

# **Chapter 17 Serial Peripheral Interface (SPI) Module**

## 17.1 Introduction

This section describes the serial peripheral interface (SPI) module, which allows full-duplex, synchronous, serial communications with peripheral devices.

## 17.2 Features

Features of the SPI module include:

- Full-duplex operation

- Master and slave modes

- Double-buffered operation with separate transmit and receive registers

- Four master mode frequencies (maximum = bus frequency ÷ 2)

- Maximum slave mode frequency = bus frequency

- Serial clock with programmable polarity and phase

- Two separately enabled interrupts:

- SPRF (SPI receiver full)

- SPTE (SPI transmitter empty)

- Mode fault error flag with CPU interrupt capability

- Overflow error flag with CPU interrupt capability

- Programmable wired-OR mode

- I<sup>2</sup>C (inter-integrated circuit) compatibility

- I/O (input/output) port bit(s) software configurable with pullup device(s) if configured as input port bit(s)

#### 17.3 Pin Name Conventions

The text that follows describes the SPI. The SPI I/O pin names are  $\overline{SS}$  (slave select), SPSCK (SPI serial clock), CGND (clock ground), MOSI (master out slave in), and MISO (master in/slave out). The SPI shares four I/O pins with four parallel I/O ports.

The full names of the SPI I/O pins are shown in Table 17-1. The generic pin names appear in the text that follows.

**Table 17-1. Pin Name Conventions**

| SPI Generic<br>Pin Names: |     | MISO      | MOSI      | SS      | SPSCK      | CGND     |

|---------------------------|-----|-----------|-----------|---------|------------|----------|

| Full SPI<br>Pin Names:    | SPI | PTD1/MISO | PTD2/MOSI | PTD0/SS | PTD3/SPSCK | $V_{SS}$ |

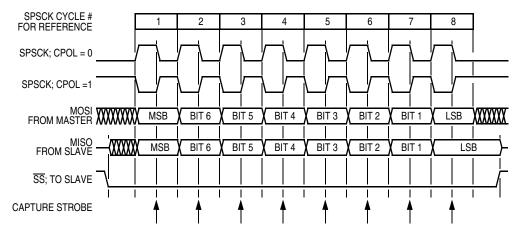

#### 17.5.3 Transmission Format When CPHA = 1

Figure 17-7 shows an SPI transmission in which CPHA is logic 1. The figure should not be used as a replacement for data sheet parametric information. Two waveforms are shown for SPSCK: one for CPOL = 0 and another for CPOL = 1. The diagram may be interpreted as a master or slave timing diagram since the serial clock (SPSCK), master in/slave out (MISO), and master out/slave in (MOSI) pins are directly connected between the master and the slave. The MISO signal is the output from the slave, and the MOSI signal is the output from the master. The  $\overline{SS}$  line is the slave select input to the slave. The slave SPI drives its MISO output only when its slave select input  $(\overline{SS})$  is at logic 0, so that only the selected slave drives to the master. The  $\overline{SS}$  pin of the master is not shown but is assumed to be inactive. The  $\overline{SS}$ pin of the master must be high or must be reconfigured as general-purpose I/O not affecting the SPI. (See 17.7.2 Mode Fault Error.) When CPHA = 1, the master begins driving its MOSI pin on the first SPSCK edge. Therefore, the slave uses the first SPSCK edge as a start transmission signal. The SS pin can remain low between transmissions. This format may be preferable in systems having only one master and only one slave driving the MISO data line.

Figure 17-7. Transmission Format (CPHA = 1)

When CPHA = 1 for a slave, the first edge of the SPSCK indicates the beginning of the transmission. This causes the SPI to leave its idle state and begin driving the MISO pin with the MSB of its data. Once the transmission begins, no new data is allowed into the shift register from the transmit data register. Therefore, the SPI data register of the slave must be loaded with transmit data before the first edge of SPSCK. Any data written after the first edge is stored in the transmit data register and transferred to the shift register after the current transmission.

## 17.5.4 Transmission Initiation Latency

When the SPI is configured as a master (SPMSTR = 1), writing to the SPDR starts a transmission. CPHA has no effect on the delay to the start of the transmission, but it does affect the initial state of the SPSCK signal. When CPHA = 0, the SPSCK signal remains inactive for the first half of the first SPSCK cycle. When CPHA = 1, the first SPSCK cycle begins with an edge on the SPSCK line from its inactive to its active level. The SPI clock rate (selected by SPR1:SPR0) affects the delay from the write to SPDR and the start of the SPI transmission. (See Figure 17-8.)

MC68HC908GZ16 • MC68HC908GZ8 Data Sheet, Rev. 4 Freescale Semiconductor 237

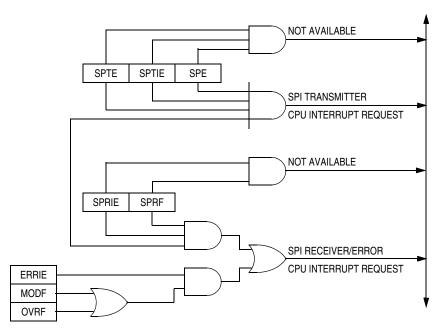

## 17.8 Interrupts

Four SPI status flags can be enabled to generate CPU interrupt requests. See Table 17-2.

| Flag                      | Request                                                    |

|---------------------------|------------------------------------------------------------|

| SPTE<br>Transmitter empty | SPI transmitter CPU interrupt request (SPTIE = 1, SPE = 1) |

| SPRF<br>Receiver full     | SPI receiver CPU interrupt request (SPRIE = 1)             |

| OVRF<br>Overflow          | SPI receiver/error interrupt request (ERRIE = 1)           |

| MODF<br>Mode fault        | SPI receiver/error interrupt request (ERRIE = 1)           |

Table 17-2. SPI Interrupts

Reading the SPI status and control register with SPRF set and then reading the receive data register clears SPRF. The clearing mechanism for the SPTE flag is always just a write to the transmit data register.

The SPI transmitter interrupt enable bit (SPTIE) enables the SPTE flag to generate transmitter CPU interrupt requests, provided that the SPI is enabled (SPE = 1).

The SPI receiver interrupt enable bit (SPRIE) enables the SPRF bit to generate receiver CPU interrupt requests, regardless of the state of the SPE bit. See Figure 17-12.

The error interrupt enable bit (ERRIE) enables both the MODF and OVRF bits to generate a receiver/error CPU interrupt request.

The mode fault enable bit (MODFEN) can prevent the MODF flag from being set so that only the OVRF bit is enabled by the ERRIE bit to generate receiver/error CPU interrupt requests.

Figure 17-12. SPI Interrupt Request Generation

MC68HC908GZ16 • MC68HC908GZ8 Data Sheet, Rev. 4

## Chapter 18 Timebase Module (TBM)

#### 18.1 Introduction

This section describes the timebase module (TBM). The TBM will generate periodic interrupts at user selectable rates using a counter clocked by the external clock source. This TBM version uses 15 divider stages, eight of which are user selectable. A configuration option bit to select an additional 128 divide of the external clock source can be selected. See Chapter 5 Configuration Register (CONFIG)

### 18.2 Features

Features of the TBM module include:

- External clock or an additional divide-by-128 selected by configuration option bit as clock source

- Software configurable periodic interrupts with divide-by: 8, 16, 32, 64, 128, 2048, 8192, and 32768 taps of the selected clock source

- Configurable for operation during stop mode to allow periodic wakeup from stop

## 18.3 Functional Description

This module can generate a periodic interrupt by dividing the clock source supplied from the clock generator module, CGMXCLK.

The counter is initialized to all 0s when TBON bit is cleared. The counter, shown in Figure 18-1, starts counting when the TBON bit is set. When the counter overflows at the tap selected by TBR2–TBR0, the TBIF bit gets set. If the TBIE bit is set, an interrupt request is sent to the CPU. The TBIF flag is cleared by writing a 1 to the TACK bit. The first time the TBIF flag is set after enabling the timebase module, the interrupt is generated at approximately half of the overflow period. Subsequent events occur at the exact period.

The timebase module may remain active after execution of the STOP instruction if the crystal oscillator has been enabled to operate during stop mode through the OSCENINSTOP bit in the configuration register. The timebase module can be used in this mode to generate a periodic wakeup from stop mode.

## 18.4 Interrupts

The timebase module can periodically interrupt the CPU with a rate defined by the selected TBMCLK and the select bits TBR2–TBR0. When the timebase counter chain rolls over, the TBIF flag is set. If the TBIE bit is set, enabling the timebase interrupt, the counter chain overflow will generate a CPU interrupt request.

#### NOTE

Interrupts must be acknowledged by writing a logic 1 to the TACK bit.

**Timer Interface Module (TIM)**

## PS[2:0] — Prescaler Select Bits

These read/write bits select one of the seven prescaler outputs as the input to the TIM counter as Table 19-2 shows. Reset clears the PS[2:0] bits.

**Table 19-2. Prescaler Selection**

| PS2 | PS1 | PS0 | TIM Clock Source        |

|-----|-----|-----|-------------------------|

| 0   | 0   | 0   | Internal bus clock ÷ 1  |

| 0   | 0   | 1   | Internal bus clock ÷ 2  |

| 0   | 1   | 0   | Internal bus clock ÷ 4  |

| 0   | 1   | 1   | Internal bus clock ÷ 8  |

| 1   | 0   | 0   | Internal bus clock ÷ 16 |

| 1   | 0   | 1   | Internal bus clock ÷ 32 |

| 1   | 1   | 0   | Internal bus clock ÷ 64 |

| 1   | 1   | 1   | Not available           |

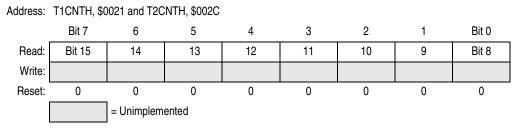

## 19.9.2 TIM Counter Registers

The two read-only TIM counter registers contain the high and low bytes of the value in the TIM counter. Reading the high byte (TCNTH) latches the contents of the low byte (TCNTL) into a buffer. Subsequent reads of TCNTH do not affect the latched TCNTL value until TCNTL is read. Reset clears the TIM counter registers. Setting the TIM reset bit (TRST) also clears the TIM counter registers.

#### NOTE

If you read TCNTH during a break interrupt, be sure to unlatch TCNTL by reading TCNTL before exiting the break interrupt. Otherwise, TCNTL retains the value latched during the break.

Figure 19-6. TIM Counter Registers High (TCNTH)

Figure 19-7. TIM Counter Registers Low (TCNTL)

MC68HC908GZ16 • MC68HC908GZ8 Data Sheet, Rev. 4

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### E-mail:

support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2005, 2006. All rights reserved.