Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | HC08                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | CANbus, LINbus, SCI, SPI                                                |

| Peripherals                | LVD, POR, PWM                                                           |

| Number of I/O              | 21                                                                      |

| Program Memory Size        | 8KB (8K x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-LQFP                                                                 |

| Supplier Device Package    | 32-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908gz8vfj |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 15.7 I/O | Signals                                  | 195 |

|----------|------------------------------------------|-----|

| 15.7.1   | PTE0/TxD (Transmit Data)                 | 195 |

| 15.7.2   | PTE1/RxD (Receive Data)                  | 195 |

| 15.8 I/O | Registers                                | 196 |

| 15.8.1   | ESCI Control Register 1                  | 196 |

| 15.8.2   | ESCI Control Register 2                  | 198 |

| 15.8.3   | ESCI Control Register 3                  | 200 |

| 15.8.4   | ESCI Status Register 1                   | 201 |

| 15.8.5   | ESCI Status Register 2                   | 203 |

| 15.8.6   | ESCI Data Register                       | 204 |

| 15.8.7   | ESCI Baud Rate Register                  | 204 |

| 15.8.8   | ESCI Prescaler Register                  | 206 |

| 15.9 ES  | CI Arbiter                               | 209 |

| 15.9.1   | ESCI Arbiter Control Register            | 209 |

| 15.9.2   | ESCI Arbiter Data Register               |     |

| 15.9.3   | Bit Time Measurement                     |     |

| 15.9.4   | Arbitration Mode                         | 212 |

|          |                                          |     |

|          | Chapter 16                               |     |

|          | System Integration Module (SIM)          |     |

|          | oduction                                 |     |

| 16.2 SIN | M Bus Clock Control and Generation       | 215 |

| 16.2.1   | Bus Timing                               | 215 |

| 16.2.2   | Clock Startup from POR or LVI Reset      |     |

| 16.2.3   | Clocks in Stop Mode and Wait Mode        | 215 |

| 16.3 Re  | set and System Initialization            | 216 |

| 16.3.1   | External Pin Reset                       | 216 |

| 16.3.2   | Active Resets from Internal Sources      | 217 |

| 16.3.2.1 | Power-On Reset                           | 217 |

| 16.3.2.2 | Computer Operating Properly (COP) Reset  | 218 |

| 16.3.2.3 | Illegal Opcode Reset                     | 218 |

| 16.3.2.4 | Illegal Address Reset                    | 218 |

| 16.3.2.5 | Low-Voltage Inhibit (LVI) Reset          | 218 |

| 16.3.2.6 | Monitor Mode Entry Module Reset (MODRST) | 219 |

| 16.4 SIN | M Counter                                | 219 |

| 16.4.1   | SIM Counter During Power-On Reset        | 219 |

| 16.4.2   | SIM Counter During Stop Mode Recovery    |     |

| 16.4.3   | SIM Counter and Reset States             |     |

| 16.5 Exc | ception Control                          | 219 |

| 16.5.1   | Interrupts                               |     |

| 16.5.1.1 | Hardware Interrupts                      |     |

| 16.5.1.2 | SWI Instruction                          |     |

| 16.5.1.3 | Interrupt Status Registers               |     |

| 16.5.2   | Reset                                    |     |

| 16.5.3   | Break Interrupts                         |     |

| 16.5.4   | Status Flag Protection in Break Mode     |     |

|          |                                          | _   |

| Addr.  | Register Name                                |                 | Bit 7  | 6          | 5      | 4           | 3              | 2            | 1     | Bit 0    |

|--------|----------------------------------------------|-----------------|--------|------------|--------|-------------|----------------|--------------|-------|----------|

|        | Timer 2 Channel 0 Status and                 | Read:           | CH0F   | CH0IE      | MS0B   | MS0A        | ELS0B          | ELS0A        | TOV0  | CH0MAX   |

| \$0030 | Control Register (T2SC0) See page 267.       | Write:          | 0      |            |        |             |                |              |       |          |

|        | See page 207.                                | Reset:          | 0      | 0          | 0      | 0           | 0              | 0            | 0     | 0        |

| \$0031 | Timer 2 Channel 0<br>Register High (T2CH0H)  | Read:<br>Write: | Bit 15 | 14         | 13     | 12          | 11             | 10           | 9     | Bit 8    |

|        | See page 270.                                | Reset:          |        |            |        | Indetermina | te after reset |              |       |          |

| \$0032 | Timer 2 Channel 0<br>Register Low (T2CH0L)   | Read:<br>Write: | Bit 7  | 6          | 5      | 4           | 3              | 2            | 1     | Bit 0    |

|        | See page 270.                                | Reset:          |        | l .        |        | Indetermina | te after reset |              |       | !I       |

|        | Timer 2 Channel 1 Status and                 | Read:           | CH1F   | CUTIE      | 0      | MC1A        | EL C1D         | EL C1A       | TOVA  | CHIMAY   |

| \$0033 | Control Register (T2SC1)                     | Write:          | 0      | CH1IE      |        | MS1A        | ELS1B          | ELS1A        | TOV1  | CH1MAX   |

|        | See page 267.                                | Reset:          | 0      | 0          | 0      | 0           | 0              | 0            | 0     | 0        |

| \$0034 | Timer 2 Channel 1<br>Register High (T2CH1H)  | Read:<br>Write: | Bit 15 | 14         | 13     | 12          | 11             | 10           | 9     | Bit 8    |

|        | See page 270.                                | Reset:          |        | l .        |        | Indetermina | te after reset |              |       |          |

| \$0035 | Timer 2 Channel 1<br>Register Low (T2CH1L)   | Read:<br>Write: | Bit 7  | 6          | 5      | 4           | 3              | 2            | 1     | Bit 0    |

|        | See page 270.                                | Reset:          |        | I.         | I      | Indetermina | te after reset |              | l     | <u> </u> |

|        | PLL Control Register                         | Read:           | DLLIE  | PLLF       | DLLON  | DCC         | п              | В            | VDD4  | VDDO     |

| \$0036 | (PCTL)                                       | Write:          | PLLIE  |            | PLLON  | BCS         | R              | R            | VPR1  | VPR0     |

|        | See page 69.                                 | Reset:          | 0      | 0          | 1      | 0           | 0              | 0            | 0     | 0        |

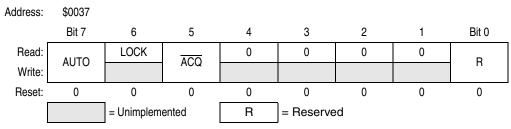

| \$0037 | PLL Bandwidth Control<br>Register (PBWC)     | Read:<br>Write: | AUTO   | LOCK       | ACQ    | 0           | 0              | 0            | 0     | R        |

|        | See page 71.                                 | Reset:          | 0      | 0          | 0      | 0           | 0              | 0            | 0     | 0        |

|        | PLL Multiplier Select High                   | Read:           | 0      | 0          | 0      | 0           | MIII 44        | MUL10        | MILLO | MULO     |

| \$0038 | Register (PMSH)                              | Write:          |        |            |        |             | MUL11          | MOLIU        | MUL9  | MUL8     |

|        | See page 72.                                 | Reset:          | 0      | 0          | 0      | 0           | 0              | 0            | 0     | 0        |

| \$0039 | PLL Multiplier Select Low<br>Register (PMSL) | Read:<br>Write: | MUL7   | MUL6       | MUL5   | MUL4        | MUL3           | MUL2         | MUL1  | MUL0     |

|        | See page 73.                                 | Reset:          | 0      | 0          | 0      | 0           | U              | U            | U     | U        |

| \$003A | PLL VCO Select Range<br>Register (PMRS)      | Read:<br>Write: | VRS7   | VRS6       | VRS5   | VRS4        | VRS3           | VRS2         | VRS1  | VRS0     |

|        | See page 73.                                 |                 | 0      | 1          | 0      | 0           | 0              | 0            | 0     | 0        |

|        |                                              | Read:           | 0      | 0          | 0      | 0           | -              | -            | -     |          |

| \$003B | Reserved                                     | Write:          |        |            |        |             | R              | R            | R     | R        |

|        |                                              | Reset:          | 0      | 0          | 0      | 0           | 0              | 0            | 0     | 1        |

|        |                                              |                 |        | = Unimplem | nented | R = Reserve | ed             | U = Unaffect | red   |          |

Figure 2-2. Control, Status, and Data Registers (Sheet 5 of 8)

#### **Analog-to-Digital Converter (ADC)**

## 3.3.3 Conversion Time

Conversion starts after a write to the ADC status and control register (ADSCR). One conversion will take between 16 and 17 ADC clock cycles. The ADIVx and ADICLK bits should be set to provide a 1-MHz ADC clock frequency.

Conversion time =

$$\frac{16 \text{ to } 17 \text{ ADC cycles}}{\text{ADC frequency}}$$

Number of bus cycles = conversion time  $\times$  bus frequency

## 3.3.4 Conversion

In continuous conversion mode, the ADC data register will be filled with new data after each conversion. Data from the previous conversion will be overwritten whether that data has been read or not. Conversions will continue until the ADCO bit is cleared. The COCO bit is set after each conversion and will stay set until the next read of the ADC data register.

In single conversion mode, conversion begins with a write to the ADSCR. Only one conversion occurs between writes to the ADSCR.

When a conversion is in process and the ADCSCR is written, the current conversion data should be discarded to prevent an incorrect reading.

## 3.3.5 Accuracy and Precision

The conversion process is monotonic and has no missing codes.

#### 3.3.6 Result Justification

The conversion result may be formatted in four different ways:

- 1. Left justified

- 2. Right justified

- 3. Left Justified sign data mode

- 4. 8-bit truncation mode

All four of these modes are controlled using MODE0 and MODE1 bits located in the ADC clock register (ADCLK).

Left justification will place the eight most significant bits (MSB) in the corresponding ADC data register high, ADRH. This may be useful if the result is to be treated as an 8-bit result where the two least significant bits (LSB), located in the ADC data register low, ADRL, can be ignored. However, ADRL must be read after ADRH or else the interlocking will prevent all new conversions from being stored.

Right justification will place only the two MSBs in the corresponding ADC data register high, ADRH, and the eight LSBs in ADC data register low, ADRL. This mode of operation typically is used when a 10-bit unsigned result is desired.

Left justified sign data mode is similar to left justified mode with one exception. The MSB of the 10-bit result, AD9 located in ADRH, is complemented. This mode of operation is useful when a result, represented as a signed magnitude from mid-scale, is needed. Finally, 8-bit truncation mode will place the eight MSBs in the ADC data register low, ADRL. The two LSBs are dropped. This mode of operation

## VPR1 and VPR0 — VCO Power-of-Two Range Select Bits

These read/write bits control the VCO's hardware power-of-two range multiplier E that, in conjunction with L controls the hardware center-of-range frequency, f<sub>VRS</sub>. VPR1:VPR0 cannot be written when the PLLON bit is set. Reset clears these bits. (See 4.3.3 PLL Circuits, 4.3.6 Programming the PLL, and 4.5.5 PLL VCO Range Select Register.)

| Table 4-4. | . VPR1 | and | VPRO | Programming |

|------------|--------|-----|------|-------------|

|            |        |     |      |             |

| VPR1 and VPR0 | E                | VCO Power-of-Two<br>Range Multiplier |

|---------------|------------------|--------------------------------------|

| 00            | 0                | 1                                    |

| 01            | 1                | 2                                    |

| 10            | 2 <sup>(1)</sup> | 4                                    |

<sup>1.</sup> Do not program E to a value of 3.

## NOTE

Verify that the value of the VPR1 and VPR0 bits in the PCTL register are appropriate for the given reference and VCO clock frequencies before enabling the PLL. See 4.3.6 Programming the PLL for detailed instructions on selecting the proper value for these control bits.

## 4.5.2 PLL Bandwidth Control Register

The PLL bandwidth control register (PBWC):

- Selects automatic or manual (software-controlled) bandwidth control mode

- Indicates when the PLL is locked

- In automatic bandwidth control mode, indicates when the PLL is in acquisition or tracking mode

- In manual operation, forces the PLL into acquisition or tracking mode

Figure 4-5. PLL Bandwidth Control Register (PBWC)

## **AUTO** — Automatic Bandwidth Control Bit

This read/write bit selects automatic or manual bandwidth control. When initializing the PLL for manual operation (AUTO = 0), clear the  $\overline{ACQ}$  bit before turning on the PLL. Reset clears the AUTO bit.

- 1 = Automatic bandwidth control

- 0 = Manual bandwidth control

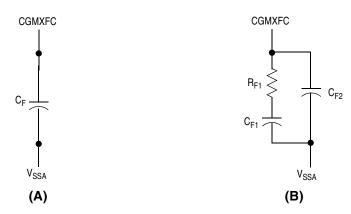

Figure 4-9. PLL Filter

**Table 4-5. Example Filter Component Values**

| f <sub>RCLK</sub> | C <sub>F1</sub> | C <sub>F2</sub> | R <sub>F1</sub> | C <sub>F</sub> |

|-------------------|-----------------|-----------------|-----------------|----------------|

| 1 MHz             | 8.2 nF          | 820 pF          | 2k              | 18 nF          |

| 2 MHz             | 4.7 nF          | 470 pF          | 2k              | 6.8 nF         |

| 3 MHz             | 3.3 nF          | 330 pF          | 2k              | 5.6 nF         |

| 4 MHz             | 2.2 nF          | 220 pF          | 2k              | 4.7 nF         |

| 5 MHz             | 1.8 nF          | 180 pF          | 2k              | 3.9 nF         |

| 6 MHz             | 1.5 nF          | 150 pF          | 2k              | 3.3 nF         |

| 7 MHz             | 1.2 nF          | 120 pF          | 2k              | 2.7 nF         |

| 8 MHz             | 1 nF            | 100 pF          | 2k              | 2.2 nF         |

**Central Processor Unit (CPU)**

## 7.7 Instruction Set Summary

Table 7-1 provides a summary of the M68HC08 instruction set.

Table 7-1. Instruction Set Summary (Sheet 1 of 6)

| Source                                                                                          | Operation                                            | Description                                              | E<br>on    |   |   | ec<br>CC |            |          | Address<br>Mode                                                                              | Opcode                                           | Operand                                         | les                                  |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------|------------|---|---|----------|------------|----------|----------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                            | ·                                                    |                                                          | ٧          | Н | I | N        | Z          | С        | Add                                                                                          | Орс                                              | Ope                                             | Cycles                               |

| ADC #opr<br>ADC opr<br>ADC opr<br>ADC opr,X<br>ADC opr,X<br>ADC, X<br>ADC opr,SP<br>ADC opr,SP  | Add with Carry                                       | A ← (A) + (M) + (C)                                      |            | ‡ | 1 | ‡        | 1          | <b>‡</b> | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | A9<br>B9<br>C9<br>D9<br>E9<br>F9<br>9EE9<br>9ED9 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff       | 2 3 4 4 3 2 4 5                      |

| ADD #opr<br>ADD opr<br>ADD opr,X<br>ADD opr,X<br>ADD opr,X<br>ADD opr,SP<br>ADD opr,SP          | Add without Carry                                    | $A \leftarrow (A) + (M)$                                 | 1          | Î | - | 1        | 1          | 1        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | AB<br>BB<br>CB<br>DB<br>EB<br>FB<br>9EEB<br>9EDB |                                                 | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| AIS #opr                                                                                        | Add Immediate Value (Signed) to SP                   | SP ← (SP) + (16 « M)                                     | -          | _ | _ | _        | -          | -        | IMM                                                                                          | A7                                               | ii                                              | 2                                    |

| AIX #opr                                                                                        | Add Immediate Value (Signed) to H:X                  | $H:X \leftarrow (H:X) + (16 \ll M)$                      | -          | - | _ | -        | -          | -        | IMM                                                                                          | AF                                               | ii                                              | 2                                    |

| AND #opr<br>AND opr<br>AND opr,<br>AND opr,X<br>AND opr,X<br>AND ,X<br>AND opr,SP<br>AND opr,SP | Logical AND                                          | A ← (A) & (M)                                            |            | - | - | 1        | 1          | _        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | A4<br>B4<br>C4<br>D4<br>E4<br>F4<br>9EE4<br>9ED4 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| ASL opr<br>ASLA<br>ASLX<br>ASL opr,X<br>ASL ,X<br>ASL opr,SP                                    | Arithmetic Shift Left<br>(Same as LSL)               | © <b>→</b> 0 b7 b0                                       | 1          | _ | - | <b>1</b> | 1          | 1        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                        | 38<br>48<br>58<br>68<br>78<br>9E68               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| ASR opr<br>ASRA<br>ASRX<br>ASR opr,X<br>ASR opr,X<br>ASR opr,SP                                 | Arithmetic Shift Right                               | b7 b0                                                    |            | _ | ı | 1        | ţ          | <b>‡</b> | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                        | 37<br>47<br>57<br>67<br>77<br>9E67               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| BCC rel                                                                                         | Branch if Carry Bit Clear                            | $PC \leftarrow (PC) + 2 + rel ? (C) = 0$                 | -          | _ | _ | -        | -          | -        | REL                                                                                          | 24                                               | rr                                              | 3                                    |

| BCLR n, opr                                                                                     | Clear Bit n in M                                     | Mn ← 0                                                   |            | _ | _ | _        | _          | _        | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 11<br>13<br>15<br>17<br>19<br>1B<br>1D<br>1F     | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd    | 4<br>4<br>4<br>4<br>4<br>4           |

| BCS rel                                                                                         | Branch if Carry Bit Set (Same as BLO)                | PC ← (PC) + 2 + rel? (C) = 1                             | -          | - | - | -        | -          | -        | REL                                                                                          | 25                                               | rr                                              | 3                                    |

| BEQ rel                                                                                         | Branch if Equal                                      | $PC \leftarrow (PC) + 2 + rel? (Z) = 1$                  | _          | _ | _ | _        | -          | _        | REL                                                                                          | 27                                               | rr                                              | 3                                    |

| BGE opr                                                                                         | Branch if Greater Than or Equal To (Signed Operands) | $PC \leftarrow (PC) + 2 + rel? (N \oplus V) = 0$         | _          | - | _ | _        | _          | -        | REL                                                                                          | 90                                               | rr                                              | 3                                    |

| BGT opr                                                                                         | Branch if Greater Than (Signed Operands)             | $PC \leftarrow (PC) + 2 + rel?(Z) \mid (N \oplus V) = 0$ | _          | - | _ | _        | _          | _        | REL                                                                                          | 92                                               | rr                                              | 3                                    |

| BHCC rel                                                                                        | Branch if Half Carry Bit Clear                       | $PC \leftarrow (PC) + 2 + rel? (H) = 0$                  | <u> </u> – | - | _ | _        | -          | -        | REL                                                                                          | 28                                               | rr                                              | 3                                    |

| BHCS rel                                                                                        | Branch if Half Carry Bit Set                         | $PC \leftarrow (PC) + 2 + rel? (H) = 1$                  | -          | _ | _ | _        | <u> </u> - | _        | REL                                                                                          | 29                                               | rr                                              | 3                                    |

| BHI rel                                                                                         | Branch if Higher                                     | $PC \leftarrow (PC) + 2 + rel? (C) \mid (Z) = 0$         | -          | - | _ | _        | -          | -        | REL                                                                                          | 22                                               | rr                                              | 3                                    |

# Chapter 11 Low-Voltage Inhibit (LVI)

## 11.1 Introduction

This section describes the low-voltage inhibit (LVI) module, which monitors the voltage on the  $V_{DD}$  pin and can force a reset when the  $V_{DD}$  voltage falls below the LVI trip falling voltage,  $V_{TRIPF}$ .

## 11.2 Features

Features of the LVI module include:

- Programmable LVI reset

- Selectable LVI trip voltage

- Programmable stop mode operation

## 11.3 Functional Description

Figure 11-1 shows the structure of the LVI module. The LVI is enabled out of reset. The LVI module contains a bandgap reference circuit and comparator. Clearing the LVI power disable bit, LVIPWRD, enables the LVI to monitor  $V_{DD}$  voltage. Clearing the LVI reset disable bit, LVIRSTD, enables the LVI module to generate a reset when  $V_{DD}$  falls below a voltage,  $V_{TRIPF}$ . Setting the LVI enable in stop mode bit, LVISTOP, enables the LVI to operate in stop mode. Setting the LVI 5-V or 3-V trip point bit, LVI5OR3, enables the trip point voltage,  $V_{TRIPF}$ , to be configured for 5-V operation. Clearing the LVI5OR3 bit enables the trip point voltage,  $V_{TRIPF}$ , to be configured for 3-V operation. The actual trip points are shown in Chapter 21 Electrical Specifications.

## **NOTE**

After a power-on reset (POR) the LVI's default mode of operation is 3 V. If a 5-V system is used, the user must set the LVI5OR3 bit to raise the trip point to 5-V operation. Note that this must be done after every power-on reset since the default will revert back to 3-V mode after each power-on reset. If the  $V_{DD}$  supply is below the 5-V mode trip voltage but above the 3-V mode trip voltage when POR is released, the part will operate because  $V_{TRIPF}$  defaults to 3-V mode after a POR. So, in a 5-V system care must be taken to ensure that  $V_{DD}$  is above the 5-V mode trip voltage after POR is released.

If the user requires 5-V mode and sets the LVI5OR3 bit after a power-on reset while the  $V_{DD}$  supply is not above the  $V_{TRIPR}$  for 5-V mode, the microcontroller unit (MCU) will immediately go into reset. The LVI in this case will hold the part in reset until either  $V_{DD}$  goes above the rising 5-V trip point,  $V_{TRIPR}$ , which will release reset or  $V_{DD}$  decreases to approximately 0 V which will re-trigger the power-on reset and reset the trip point to 3-V operation.

MC68HC908GZ16 • MC68HC908GZ8 Data Sheet, Rev. 4

## 11.3.3 Voltage Hysteresis Protection

Once the LVI has triggered (by having  $V_{DD}$  fall below  $V_{TRIPF}$ ), the LVI will maintain a reset condition until  $V_{DD}$  rises above the rising trip point voltage,  $V_{TRIPR}$ . This prevents a condition in which the MCU is continually entering and exiting reset if  $V_{DD}$  is approximately equal to  $V_{TRIPF}$ .  $V_{TRIPR}$  is greater than  $V_{TRIPF}$  by the hysteresis voltage,  $V_{HYS}$ .

## 11.3.4 LVI Trip Selection

The LVI5OR3 bit in the configuration register selects whether the LVI is configured for 5-V or 3-V protection.

#### NOTE

The microcontroller is guaranteed to operate at a minimum supply voltage. The trip point ( $V_{TRIPF}$  [5 V] or  $V_{TRIPF}$  [3 V]) may be lower than this. See Chapter 21 Electrical Specifications for the actual trip point voltages.

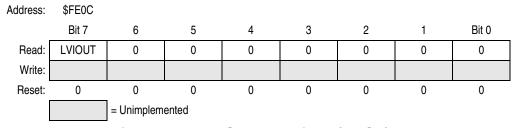

## 11.4 LVI Status Register

The LVI status register (LVISR) indicates if the  $V_{DD}$  voltage was detected below the  $V_{TRIPF}$  level.

Figure 11-3. LVI Status Register (LVISR)

## LVIOUT — LVI Output Bit

This read-only flag becomes set when the  $V_{DD}$  voltage falls below the  $V_{TRIPF}$  trip voltage (see Table 11-1). Reset clears the LVIOUT bit.

Table 11-1. LVIOUT Bit Indication

| V <sub>DD</sub>                                           | LVIOUT         |

|-----------------------------------------------------------|----------------|

| V <sub>DD</sub> > V <sub>TRIPR</sub>                      | 0              |

| $V_{DD} < V_{TRIPF}$                                      | 1              |

| V <sub>TRIPF</sub> < V <sub>DD</sub> < V <sub>TRIPR</sub> | Previous value |

## 11.5 LVI Interrupts

The LVI module does not generate interrupt requests.

#### **MSCAN08 Controller (MSCAN08)**

## WUPM — Wakeup Mode

This flag defines whether the integrated low-pass filter is applied to protect the MSCAN08 from spurious wakeups (see 12.8.5 Programmable Wakeup Function).

- 1 = MSCAN08 will wakeup the CPU only in cases of a dominant pulse on the bus which has a length of at least t<sub>wup</sub>.

- 0 = MSCAN08 will wakeup the CPU after any recessive-to-dominant edge on the CAN bus.

#### **CLKSRC** — Clock Source

This flag defines which clock source the MSCAN08 module is driven from (see 12.10 Clock System).

- 1 = The MSCAN08 clock source is CGMOUT (see Figure 12-8).

- 0 = The MSCAN08 clock source is CGMXCLK/2 (see Figure 12-8).

#### NOTE

The CMCR1 register can be written only if the SFTRES bit in the MSCAN08 module control register is set

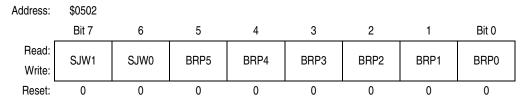

## 12.13.3 MSCAN08 Bus Timing Register 0

Figure 12-18. Bus Timing Register 0 (CBTR0)

## SJW1 and SJW0 — Synchronization Jump Width

The synchronization jump width (SJW) defines the maximum number of time quanta ( $T_q$ ) clock cycles by which a bit may be shortened, or lengthened, to achieve resynchronization on data transitions on the bus (see Table 12-6).

**Table 12-6. Synchronization Jump Width**

| SJW1 | SJW0 | Synchronization<br>Jump Width |

|------|------|-------------------------------|

| 0    | 0    | 1 T <sub>q</sub> cycle        |

| 0    | 1    | 2 T <sub>q</sub> cycle        |

| 1    | 0    | 3 T <sub>q</sub> cycle        |

| 1    | 1    | 4 T <sub>q</sub> cycle        |

## BRP5-BRP0 — Baud Rate Prescaler

These bits determine the time quanta  $(T_q)$  clock, which is used to build up the individual bit timing, according to Table 12-7.

| BRP5 | BRP4 | BRP3 | BRP2 | BRP1 | BRP0 | Prescaler<br>Value (P) |

|------|------|------|------|------|------|------------------------|

| 0    | 0    | 0    | 0    | 0    | 0    | 1                      |

| 0    | 0    | 0    | 0    | 0    | 1    | 2                      |

| 0    | 0    | 0    | 0    | 1    | 0    | 3                      |

| 0    | 0    | 0    | 0    | 1    | 1    | 4                      |

|      | :    | :    | :    | :    | :    | :                      |

| :    | :    | :    | :    | :    | :    | :                      |

| 1    | 1    | 1    | 1    | 1    | 1    | 64                     |

Table 12-7. Baud Rate Prescaler

## NOTE

The CBTR0 register can be written only if the SFTRES bit in the MSCAN08 module control register is set.

## 12.13.4 MSCAN08 Bus Timing Register 1

Figure 12-19. Bus Timing Register 1 (CBTR1)

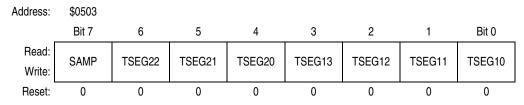

## SAMP — Sampling

This bit determines the number of serial bus samples to be taken per bit time. If set, three samples per bit are taken, the regular one (sample point) and two preceding samples, using a majority rule. For higher bit rates, SAMP should be cleared, which means that only one sample will be taken per bit.

- 1 =Three samples per bit $^{(1)}$

- 0 = One sample per bit

## TSEG22-TSEG10 — Time Segment

Time segments within the bit time fix the number of clock cycles per bit time and the location of the sample point. Time segment 1 (TSEG1) and time segment 2 (TSEG2) are programmable as shown in Table 12-8.

The bit time is determined by the oscillator frequency, the baud rate prescaler, and the number of time quanta  $(T_n)$  clock cycles per bit as shown in Table 12-4).

Bit time =

$$\frac{\text{Pres value}}{f_{\text{MSCANCLK}}} \bullet \text{number of time quanta}$$

## NOTE

The CBTR1 register can only be written if the SFTRES bit in the MSCAN08 module control register is set.

MC68HC908GZ16 • MC68HC908GZ8 Data Sheet, Rev. 4

<sup>1.</sup> In this case PHASE\_SEG1 must be at least 2 time quanta.

**Table 14-1. Interrupt Sources**

| Source                    | Flag                                                   | Mask <sup>(1)</sup>                                     | INT Register<br>Flag | Priority <sup>(2)</sup> | Vector<br>Address  |  |

|---------------------------|--------------------------------------------------------|---------------------------------------------------------|----------------------|-------------------------|--------------------|--|

| Reset                     | None                                                   | None                                                    | None                 | 0                       | \$FFFE—\$FFFF      |  |

| SWI instruction           | None                                                   | None                                                    | None                 | 0                       | \$FFFC—\$FFFD      |  |

| ĪRQ pin                   | IRQF                                                   | IMASK1                                                  | IF1                  | 1                       | \$FFFA—\$FFFB      |  |

| CGM change in lock        | PLLF                                                   | PLLIE                                                   | IF2                  | 2                       | \$FFF8-\$FFF9      |  |

| TIM1 channel 0            | CH0F                                                   | CH0IE                                                   | IF3                  | 3                       | \$FFF6-\$FFF7      |  |

| TIM1 channel 1            | CH1F                                                   | CH1IE                                                   | IF4                  | 4                       | \$FFF4-\$FFF5      |  |

| TIM1 overflow             | TOF                                                    | TOIE                                                    | IF5                  | 5                       | \$FFF2-\$FFF3      |  |

| TIM2 channel 0            | CH0F                                                   | CH0IE                                                   | IF6                  | 6                       | \$FFF0-\$FFF1      |  |

| TIM2 channel 1            | CH1F                                                   | CH1IE                                                   | IF7                  | 7                       | \$FFEE-\$FFEF      |  |

| TIM2 overflow             | TOF                                                    | TOIE                                                    | IF8                  | 8                       | \$FFEC-\$FFED      |  |

| SPI receiver full         | SPRF                                                   | SPRIE                                                   |                      |                         |                    |  |

| SPI overflow              | OVRF                                                   | ERRIE                                                   | IF9                  | 9                       | \$FFEA-\$FFEB      |  |

| SPI mode fault            | MODF                                                   | ERRIE                                                   |                      |                         |                    |  |

| SPI transmitter empty     | SPTE                                                   | SPTIE                                                   | IF10                 | 10                      | \$FFE8-\$FFE9      |  |

| SCI receiver overrun      | OR                                                     | ORIE                                                    |                      |                         |                    |  |

| SCI noise flag            | NF                                                     | NEIE                                                    | lea a                |                         | <b>45550 45557</b> |  |

| SCI framing error         | FE                                                     | FEIE                                                    | IF11                 | 11                      | \$FFE6-\$FFE7      |  |

| SCI parity error          | PE                                                     | PEIE                                                    |                      |                         |                    |  |

| SCI receiver full         | SCRF                                                   | SCRIE                                                   | 1540                 | 40                      | <b>45554 45555</b> |  |

| SCI input idle            | IDLE                                                   | ILIE                                                    | IF12                 | 12                      | \$FFE4-\$FFE5      |  |

| SCI transmitter empty     | SCTE                                                   | SCTIE                                                   | 1540                 | 40                      | ΦΕΕΕΟ ΦΕΕΕΟ        |  |

| SCI transmission complete | TC                                                     | TCIE                                                    | IF13                 | 13                      | \$FFE2-\$FFE3      |  |

| Keyboard pin              | KEYF                                                   | IMASKK                                                  | IF14                 | 14                      | \$FFE0-\$FFE1      |  |

| ADC conversion complete   | COCO                                                   | AIEN                                                    | IF15                 | 15                      | \$FFDE-\$FFDF      |  |

| Timebase                  | TBIF                                                   | TBIE                                                    | IF16                 | 16                      | \$FFDC-\$FFDD      |  |

| MSCAN08 receiver wakeup   | WUPIF                                                  | WUPIE                                                   | IF17                 | 17                      | \$FFDA-\$FFDB      |  |

| MSCAN08 error             | RWRNIF<br>TWRNIF<br>RERIF<br>TERRIF<br>BOFFIF<br>OVRIF | RWRNIE<br>TWRNIE<br>RERRIE<br>TERRIE<br>BOFFIE<br>OVRIE | IF18                 | 18                      | \$FFD8-\$FFD9      |  |

| MSCAN08 receiver          | RXF                                                    | RXFIE                                                   | IF19                 | 19                      | \$FFD6-\$FFD7      |  |

| MSCAN08 transmitter       | TXE2<br>TXE1<br>TXE0                                   | TXEIE2<br>TXEIE1<br>TXEIE0                              | IF20                 | 20                      | \$FFD4-\$FFD5      |  |

<sup>1.</sup> The I bit in the condition code register is a global mask for all interrupt sources except the SWI instruction. 2. 0 = highest priority

Bus Off bit (BOFFIF) — BOFFIF is set when the transmit error counter has exceeded 255 and MSCAN08 has gone to bus off state. The bus off interrupt enable bit, BOFFIE, enables BOFFIF to generate MSCAN08 error CPU interrupt requests. BOFFIF is in MSCAN08 receiver flag register. BOFFIE is in MSCAN08 receiver interrupt enable register.

## 14.3.3 Interrupt Status Registers

The flags in the interrupt status registers identify maskable interrupt sources. Table 14-2 summarizes the interrupt sources and the interrupt status register flags that they set. The interrupt status registers can be useful for debugging.

**Table 14-2. Interrupt Source Flags**

| Interrupt<br>Source     | Interrupt Status<br>Register Flag |

|-------------------------|-----------------------------------|

| Reset                   | _                                 |

| SWI instruction         | _                                 |

| ĪRQ pin                 | IF1                               |

| CGM change of lock      | IF2                               |

| TIM1 channel 0          | IF3                               |

| TIM1 channel 1          | IF4                               |

| TIM1 overflow           | IF5                               |

| TIM2 channel 0          | IF6                               |

| TIM2 channel 1          | IF7                               |

| TIM2 overflow           | IF8                               |

| SPI receive             | IF9                               |

| SPI transmit            | IF10                              |

| SCI error               | IF11                              |

| SCI receive             | IF12                              |

| SCI transmit            | IF13                              |

| Keyboard                | IF14                              |

| ADC conversion complete | IF15                              |

| Timebase                | IF16                              |

| MSCAN08 wakeup          | IF17                              |

| MSCAN08 error           | IF18                              |

| MSCAN08 receive         | IF19                              |

| MSCAN08 transmit        | IF20                              |

The maximum percent difference between the receiver count and the transmitter count of a slow 9-bit character with no errors is:

$$\left| \frac{170 - 163}{170} \right| \times 100 = 4.12\%$$

#### **Fast Data Tolerance**

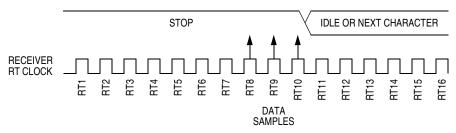

Figure 15-9 shows how much a fast received character can be misaligned without causing a noise error or a framing error. The fast stop bit ends at RT10 instead of RT16 but is still there for the stop bit data samples at RT8, RT9, and RT10.

Figure 15-9. Fast Data

For an 8-bit character, data sampling of the stop bit takes the receiver9 bit times  $\times$  16 RT cycles + 10 RT cycles = 154 RT cycles.

With the misaligned character shown in Figure 15-9, the receiver counts 154 RT cycles at the point when the count of the transmitting device is 10 bit times  $\times$  16 RT cycles = 160 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 8-bit character with no errors is

$$\left| \frac{154 - 160}{154} \right| \times 100 = 3.90\%.$$

For a 9-bit character, data sampling of the stop bit takes the receiver 10 bit times  $\times$  16 RT cycles + 10 RT cycles = 170 RT cycles.

With the misaligned character shown in Figure 15-9, the receiver counts 170 RT cycles at the point when the count of the transmitting device is 11 bit times  $\times$  16 RT cycles = 176 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 9-bit character with no errors is:

$$\left| \frac{170 - 176}{170} \right| \times 100 = 3.53\%.$$

## 15.4.3.6 Receiver Wakeup

So that the MCU can ignore transmissions intended only for other receivers in multiple-receiver systems, the receiver can be put into a standby state. Setting the receiver wakeup bit, RWU, in SCC2 puts the receiver into a standby state during which receiver interrupts are disabled.

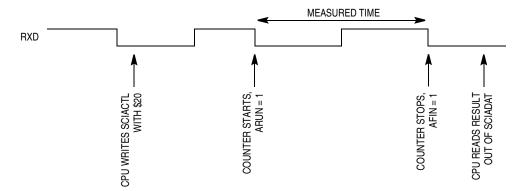

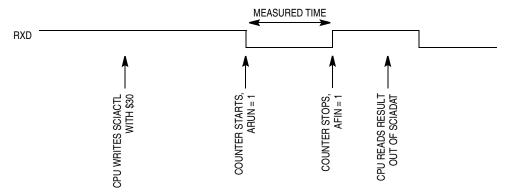

Figure 15-21. Bit Time Measurement with ACLK = 0

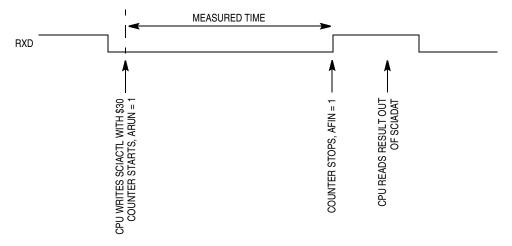

Figure 15-22. Bit Time Measurement with ACLK = 1, Scenario A

Figure 15-23. Bit Time Measurement with ACLK = 1, Scenario B

**System Integration Module (SIM)**

## 16.3 Reset and System Initialization

The MCU has these reset sources:

- Power-on reset module (POR)

- External reset pin (RST)

- Computer operating properly module (COP)

- Low-voltage inhibit module (LVI)

- Illegal opcode

- Illegal address

- Forced monitor mode entry reset (MODRST)

All of these resets produce the vector \$FFFE:\$FFFF (\$FEFE:\$FEFF in monitor mode) and assert the internal reset signal (IRST). IRST causes all registers to be returned to their default values and all modules to be returned to their reset states.

An internal reset clears the SIM counter (see 16.4 SIM Counter), but an external reset does not. Each of the resets sets a corresponding bit in the SIM reset status register (SRSR). See 16.7 SIM Registers.

## 16.3.1 External Pin Reset

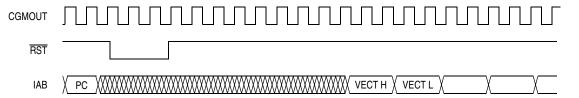

The RST pin circuit includes an internal pullup device. Pulling the asynchronous RST pin low halts all processing. The PIN bit of the SIM reset status register (SRSR) is set as long as RST is held low for a minimum of 67 CGMXCLK cycles, assuming that neither the POR nor the LVI was the source of the reset. See Table 16-2 for details. Figure 16-4 shows the relative timing.

Table 16-2. PIN Bit Set Timing

| Reset Type | Number of Cycles Required to Set PIN |

|------------|--------------------------------------|

| POR/LVI    | 4163 (4096 + 64 + 3)                 |

| All others | 67 (64 + 3)                          |

Figure 16-4. External Reset Timing

#### Serial Peripheral Interface (SPI) Module

- 1. Ports are software configurable with pullup device if input port.

- 2. Higher current drive port pins

- 3. Pin contains integrated pullup device

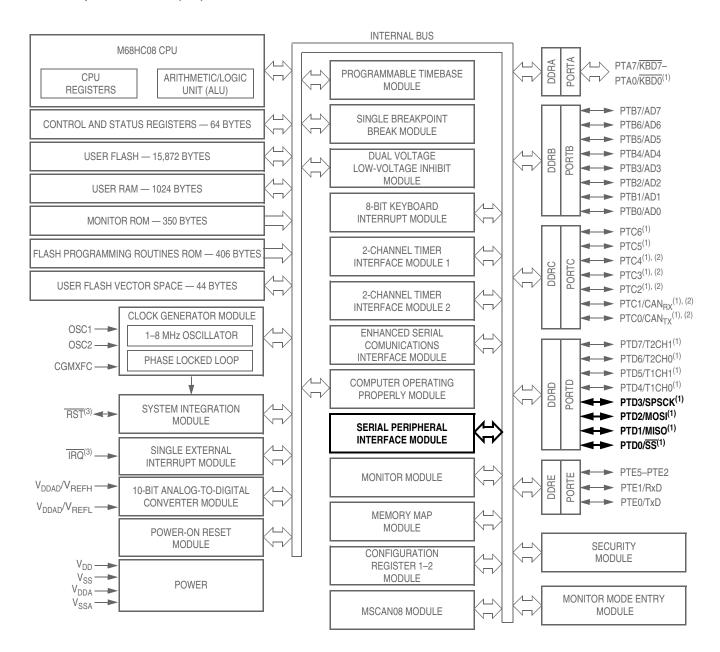

Figure 17-1. Block Diagram Highlighting SPI Block and Pins

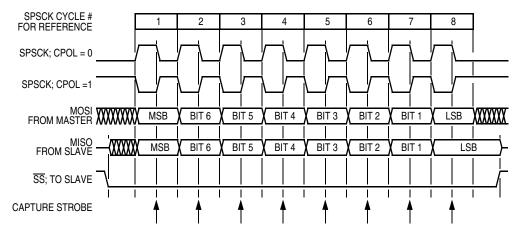

## 17.5.3 Transmission Format When CPHA = 1

Figure 17-7 shows an SPI transmission in which CPHA is logic 1. The figure should not be used as a replacement for data sheet parametric information. Two waveforms are shown for SPSCK: one for CPOL = 0 and another for CPOL = 1. The diagram may be interpreted as a master or slave timing diagram since the serial clock (SPSCK), master in/slave out (MISO), and master out/slave in (MOSI) pins are directly connected between the master and the slave. The MISO signal is the output from the slave, and the MOSI signal is the output from the master. The  $\overline{SS}$  line is the slave select input to the slave. The slave SPI drives its MISO output only when its slave select input  $(\overline{SS})$  is at logic 0, so that only the selected slave drives to the master. The  $\overline{SS}$  pin of the master is not shown but is assumed to be inactive. The  $\overline{SS}$ pin of the master must be high or must be reconfigured as general-purpose I/O not affecting the SPI. (See 17.7.2 Mode Fault Error.) When CPHA = 1, the master begins driving its MOSI pin on the first SPSCK edge. Therefore, the slave uses the first SPSCK edge as a start transmission signal. The SS pin can remain low between transmissions. This format may be preferable in systems having only one master and only one slave driving the MISO data line.

Figure 17-7. Transmission Format (CPHA = 1)

When CPHA = 1 for a slave, the first edge of the SPSCK indicates the beginning of the transmission. This causes the SPI to leave its idle state and begin driving the MISO pin with the MSB of its data. Once the transmission begins, no new data is allowed into the shift register from the transmit data register. Therefore, the SPI data register of the slave must be loaded with transmit data before the first edge of SPSCK. Any data written after the first edge is stored in the transmit data register and transferred to the shift register after the current transmission.

## 17.5.4 Transmission Initiation Latency

When the SPI is configured as a master (SPMSTR = 1), writing to the SPDR starts a transmission. CPHA has no effect on the delay to the start of the transmission, but it does affect the initial state of the SPSCK signal. When CPHA = 0, the SPSCK signal remains inactive for the first half of the first SPSCK cycle. When CPHA = 1, the first SPSCK cycle begins with an edge on the SPSCK line from its inactive to its active level. The SPI clock rate (selected by SPR1:SPR0) affects the delay from the write to SPDR and the start of the SPI transmission. (See Figure 17-8.)

MC68HC908GZ16 • MC68HC908GZ8 Data Sheet, Rev. 4 Freescale Semiconductor 237

#### Serial Peripheral Interface (SPI) Module

MODF generates a receiver/error CPU interrupt request if the error interrupt enable bit (ERRIE) is also set. The SPRF, MODF, and OVRF interrupts share the same CPU interrupt vector. (See Figure 17-12.) It is not possible to enable MODF or OVRF individually to generate a receiver/error CPU interrupt request. However, leaving MODFEN low prevents MODF from being set.

In a master SPI with the mode fault enable bit (MODFEN) set, the mode fault flag (MODF) is set if SS goes to logic 0. A mode fault in a master SPI causes the following events to occur:

- If ERRIE = 1, the SPI generates an SPI receiver/error CPU interrupt request.

- The SPE bit is cleared.

- The SPTE bit is set.

- The SPI state counter is cleared.

- The data direction register of the shared I/O port regains control of port drivers.

#### NOTE

To prevent bus contention with another master SPI after a mode fault error, clear all SPI bits of the data direction register of the shared I/O port before enabling the SPI.

When configured as a slave (SPMSTR = 0), the MODF flag is set if  $\overline{SS}$  goes high during a transmission. When CPHA = 0, a transmission begins when  $\overline{SS}$  goes low and ends once the incoming SPSCK goes back to its idle level following the shift of the eighth data bit. When CPHA = 1, the transmission begins when the SPSCK leaves its idle level and  $\overline{SS}$  is already low. The transmission continues until the SPSCK returns to its idle level following the shift of the last data bit. See 17.5 Transmission Formats.

#### NOTE

Setting the MODF flag does not clear the SPMSTR bit. The SPMSTR bit has no function when SPE = 0. Reading SPMSTR when MODF = 1 shows the difference between a MODF occurring when the SPI is a master and when it is a slave.

When CPHA = 0, a MODF occurs if a slave is selected ( $\overline{SS}$  is at logic 0) and later unselected ( $\overline{SS}$  is at logic 1) even if no SPSCK is sent to that slave. This happens because  $\overline{SS}$  at logic 0 indicates the start of the transmission (MISO driven out with the value of MSB) for CPHA = 0. When CPHA = 1, a slave can be selected and then later unselected with no transmission occurring. Therefore, MODF does not occur since a transmission was never begun.

In a slave SPI (MSTR = 0), the MODF bit generates an SPI receiver/error CPU interrupt request if the ERRIE bit is set. The MODF bit does not clear the SPE bit or reset the SPI in any way. Software can abort the SPI transmission by clearing the SPE bit of the slave.

#### NOTE

A logic 1 voltage on the  $\overline{SS}$  pin of a slave SPI puts the MISO pin in a high impedance state. Also, the slave SPI ignores all incoming SPSCK clocks, even if it was already in the middle of a transmission.

To clear the MODF flag, read the SPSCR with the MODF bit set and then write to the SPCR register. This entire clearing mechanism must occur with no MODF condition existing or else the flag is not cleared.

#### **Development Support**

Enter monitor mode with pin configuration shown in Table 20-1 by pulling  $\overline{RST}$  low and then high. The rising edge of  $\overline{RST}$  latches monitor mode. Once monitor mode is latched, the values on the specified pins can change.

Once out of reset, the MCU waits for the host to send eight security bytes (see 20.3.2 Security). After the security bytes, the MCU sends a break signal (10 consecutive logic 0s) to the host, indicating that it is ready to receive a command.

#### 20.3.1.1 Normal Monitor Mode

If  $V_{TST}$  is applied to  $\overline{IRQ}$  and PTB4 is low upon monitor mode entry, the bus frequency is a divide-by-two of the input clock. If PTB4 is high with  $V_{TST}$  applied to  $\overline{IRQ}$  upon monitor mode entry, the bus frequency will be a divide-by-four of the input clock. Holding the PTB4 pin low when entering monitor mode causes a bypass of a divide-by-two stage at the oscillator *only if*  $V_{TST}$  *is applied to*  $\overline{IRQ}$ . In this event, the CGMOUT frequency is equal to the CGMXCLK frequency, and the OSC1 input directly generates internal bus clocks. In this case, the OSC1 signal must have a 50% duty cycle at maximum bus frequency.

When monitor mode was entered with  $V_{TST}$  on  $\overline{IRQ}$ , the computer operating properly (COP) is disabled as long as  $V_{TST}$  is applied to either  $\overline{IRQ}$  or  $\overline{RST}$ .

This condition states that as long as  $V_{TST}$  is maintained on the  $\overline{IRQ}$  pin after entering monitor mode, or if  $V_{TST}$  is applied to  $\overline{RST}$  after the initial reset to get into monitor mode (when  $V_{TST}$  was applied to  $\overline{IRQ}$ ), then the COP will be disabled. In the latter situation, after  $V_{TST}$  is applied to the  $\overline{RST}$  pin,  $V_{TST}$  can be removed from the  $\overline{IRQ}$  pin in the interest of freeing the  $\overline{IRQ}$  for normal functionality in monitor mode.

#### 20.3.1.2 Forced Monitor Mode

If entering monitor mode without high voltage on  $\overline{IRQ}$ , then all port B pin requirements and conditions, including the PTB4 frequency divisor selection, are not in effect. This is to reduce circuit requirements when performing in-circuit programming.

#### NOTE

If the reset vector is blank and monitor mode is entered, the chip will see an additional reset cycle after the initial power-on reset (POR). Once the reset vector has been programmed, the traditional method of applying a voltage,  $V_{TST}$ , to  $\overline{IRQ}$  must be used to enter monitor mode.

An external oscillator of 8 MHz is required for a baud rate of 7200, as the internal bus frequency is automatically set to the external frequency divided by four.

When the forced monitor mode is entered the COP is always disabled regardless of the state of  $\overline{\text{IRQ}}$  or  $\overline{\text{RST}}$ .

## 20.3.1.3 Monitor Vectors

In monitor mode, the MCU uses different vectors for reset, SWI (software interrupt), and break interrupt than those for user mode. The alternate vectors are in the \$FE page instead of the \$FF page and allow code execution from the internal monitor firmware instead of user code.

Table 20-2 summarizes the differences between user mode and monitor mode.