Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 224 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f627a-e-ml |

#### **Table of Contents**

| 1.0 General Description                                                     | 7    |

|-----------------------------------------------------------------------------|------|

| 2.0 PIC16F627A/628A/648A Device Varieties                                   | 9    |

| 3.0 Architectural Overview                                                  | . 11 |

| 4.0 Memory Organization                                                     | 17   |

| 5.0 I/O Ports                                                               | . 33 |

| 6.0 Timer0 Module                                                           | 47   |

| 7.0 Timer1 Module                                                           | 50   |

| 8.0 Timer2 Module                                                           | . 54 |

| 9.0 Capture/Compare/PWM (CCP) Module                                        | . 57 |

| 10.0 Comparator Module                                                      |      |

| 11.0 Voltage Reference Module                                               | . 69 |

| 12.0 Universal Synchronous Asynchronous Receiver Transmitter (USART) Module | . 73 |

| 13.0 Data EEPROM Memory                                                     |      |

| 14.0 Special Features of the CPU                                            |      |

| 15.0 Instruction Set Summary                                                | 117  |

| 16.0 Development Support                                                    | 131  |

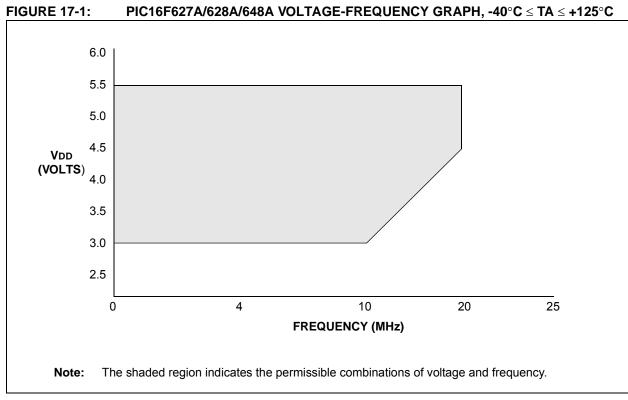

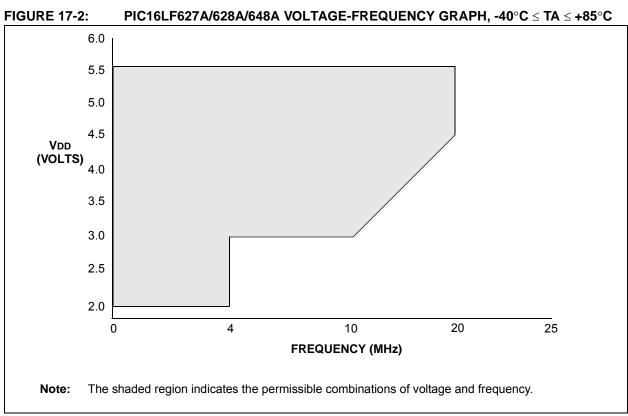

| 17.0 Electrical Specifications                                              | 135  |

| 18.0 DC and AC Characteristics Graphs and Tables                            | 151  |

| 19.0 Packaging Information                                                  | 163  |

| Appendix A: Data Sheet Revision History                                     |      |

| Appendix B: Device Differences                                              | 171  |

| Appendix C: Device Migrations                                               |      |

| Appendix D: Migrating from other PIC <sup>®</sup> Devices                   | 172  |

| The Microchip Web Site                                                      | 173  |

| Customer Change Notification Service                                        |      |

| Customer Support                                                            | 173  |

| Reader Response                                                             | 174  |

| Product Identification System                                               | 179  |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### 4.0 MEMORY ORGANIZATION

### 4.1 Program Memory Organization

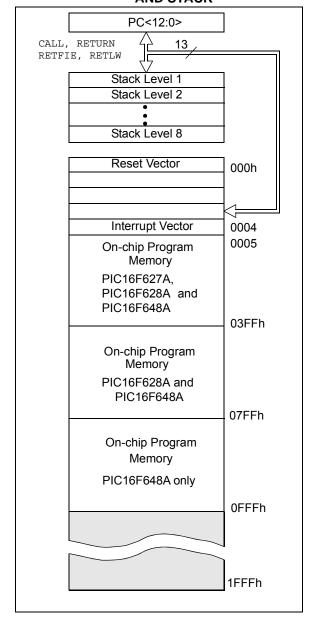

The PIC16F627A/628A/648A has a 13-bit program counter capable of addressing an  $8K \times 14$  program memory space. Only the first  $1K \times 14$  (0000h-03FFh) for the PIC16F627A,  $2K \times 14$  (0000h-07FFh) for the PIC16F628A and  $4K \times 14$  (0000h-0FFFh) for the PIC16F648A are physically implemented. Accessing a location above these boundaries will cause a wraparound within the first  $1K \times 14$  space (PIC16F627A),  $2K \times 14$  space (PIC16F628A) or  $4K \times 14$  space (PIC16F648A). The Reset vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1).

FIGURE 4-1: PROGRAM MEMORY MAP AND STACK

### 4.2 Data Memory Organization

The data memory (Figure 4-2 and Figure 4-3) is partitioned into four banks, which contain the General Purpose Registers (GPRs) and the Special Function Registers (SFRs). The SFRs are located in the first 32 locations of each bank. There are General Purpose Registers implemented as static RAM in each bank. Table 4-1 lists the General Purpose Register available in each of the four banks.

TABLE 4-1: GENERAL PURPOSE STATIC RAM REGISTERS

|       | PIC16F627A/628A      | PIC16F648A |

|-------|----------------------|------------|

| Bank0 | 20-7Fh               | 20-7Fh     |

| Bank1 | A0h-FF               | A0h-FF     |

| Bank2 | 120h-14Fh, 170h-17Fh | 120h-17Fh  |

| Bank3 | 1F0h-1FFh            | 1F0h-1FFh  |

Addresses F0h-FFh, 170h-17Fh and 1F0h-1FFh are implemented as common RAM and mapped back to addresses 70h-7Fh.

Table 4-2 lists how to access the four banks of registers via the Status register bits RP1 and RP0.

TABLE 4-2: ACCESS TO BANKS OF REGISTERS

| Bank | RP1 | RP0 |

|------|-----|-----|

| 0    | 0   | 0   |

| 1    | 0   | 1   |

| 2    | 1   | 0   |

| 3    | 1   | 1   |

### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 224 x 8 in the PIC16F627A/628A and 256 x 8 in the PIC16F648A. Each is accessed either directly or indirectly through the File Select Register (FSR), See **Section 4.4** "Indirect Addressing, INDF and FSR Registers".

FIGURE 4-3: **DATA MEMORY MAP OF THE PIC16F648A** File Address Indirect addr. (1) Indirect addr.(1) Indirect addr. (1) Indirect addr. (1) 100h 00h 80h 180h 101h OPTION TMR0 01h **OPTION** TMR0 81h 181h PCL 102h PCL 02h PCL 82h **PCL** 182h **STATUS** 103h **STATUS** 03h **STATUS STATUS** 83h 183h **FSR** 04h **FSR** 104h FSR 184h **FSR** 84h 105h **PORTA** 05h 185h **TRISA** 85h TRISB **PORTB PORTB** 06h 106h **TRISB** 86h 186h 07h 107h 87h 187h 08h 108h 88h 188h 09h 109h 189h 89h **PCLATH** 10Ah **PCLATH** 0Ah **PCLATH** 8Ah **PCLATH** 18Ah INTCON 0Bh INTCON 10Bh INTCON INTCON 8Bh 18Bh PIR1 0Ch 10Ch 18Ch PIE1 8Ch 10Dh 0Dh 18Dh 8Dh 10Eh TMR1L 0Eh **PCON** 8Eh 18Eh TMR1H 0Fh 10Fh 18Fh 8Fh T1CON 10h 90h TMR2 11h 91h T2CON 12h PR2 92h 13h 93h 14h 94h CCPR1L 15h 95h CCPR1H 16h 96h CCP1CON 17h 97h 18h **RCSTA TXSTA** 98h 19h 99h **TXREG** SPBRG EEDATA 1Ah **RCREG** 9Ah 1Bh **EEADR** 9Bh EECON1 1Ch 9Ch EECON2<sup>(1)</sup> 1Dh 9Dh 1Eh 9Eh 1Fh **CMCON VRCON** 9Fh 11Fh 20h 120h A0h General General General Purpose Purpose Purpose Register 80 Bytes Register Register 80 Bytes 80 Bytes 1EFh 6Fh **EFh** 16Fh 1F0h 70h F0h 170h accesses accesses accesses 16 Bytes 70h-7Fh 70h-7Fh 70h-7Fh 1FFh 7Fh FFh 17Fh Bank 1 Bank 2 Bank 3 Bank 0 Unimplemented data memory locations, read as '0'. Note 1: Not a physical register.

TABLE 5-3: PORTB FUNCTIONS

| Name                    | Function | Input Type | Output<br>Type | Description                                                                                                                                     |

|-------------------------|----------|------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT                 | RB0      | TTL        | CMOS           | Bidirectional I/O port. Can be software programmed for internal weak pull-up.                                                                   |

|                         | INT      | ST         |                | External interrupt                                                                                                                              |

| RB1/RX/DT               | RB1      | TTL        | CMOS           | Bidirectional I/O port. Can be software programmed for internal weak pull-up.                                                                   |

|                         | RX       | ST         | _              | USART Receive Pin                                                                                                                               |

|                         | DT       | ST         | CMOS           | Synchronous data I/O                                                                                                                            |

| RB2/TX/CK               | RB2      | TTL        | CMOS           | Bidirectional I/O port                                                                                                                          |

|                         | TX       | _          | CMOS           | USART Transmit Pin                                                                                                                              |

|                         | CK       | ST         | CMOS           | Synchronous Clock I/O. Can be software programmed for internal weak pull-up.                                                                    |

| RB3/CCP1                | RB3      | TTL        | CMOS           | Bidirectional I/O port. Can be software programmed for internal weak pull-up.                                                                   |

|                         | CCP1     | ST         | CMOS           | Capture/Compare/PWM/I/O                                                                                                                         |

| RB4/PGM                 | RB4      | TTL        | CMOS           | Bidirectional I/O port. Interrupt-on-pin change. Can be software programmed for internal weak pull-up.                                          |

|                         | PGM      | ST         | _              | Low-voltage programming input pin. When low-voltage programming is enabled, the interrupt-on-pin change and weak pull-up resistor are disabled. |

| RB5                     | RB5      | TTL        | CMOS           | Bidirectional I/O port. Interrupt-on-pin change. Can be software programmed for internal weak pull-up.                                          |

| RB6/T1OSO/T1CKI/<br>PGC | RB6      | TTL        | CMOS           | Bidirectional I/O port. Interrupt-on-pin change. Can be software programmed for internal weak pull-up.                                          |

|                         | T10S0    |            | XTAL           | Timer1 Oscillator Output                                                                                                                        |

|                         | T1CKI    | ST         | _              | Timer1 Clock Input                                                                                                                              |

|                         | PGC      | ST         | _              | ICSP <sup>™</sup> Programming Clock                                                                                                             |

| RB7/T1OSI/PGD           | RB7      | TTL        | CMOS           | Bidirectional I/O port. Interrupt-on-pin change. Can be software programmed for internal weak pull-up.                                          |

|                         | T1OSI    | XTAL       | _              | Timer1 Oscillator Input                                                                                                                         |

|                         | PGD      | ST         | CMOS           | ICSP Data I/O                                                                                                                                   |

**Legend:** O = Output CMOS = CMOS Output P = Power

— = Not used I = Input ST = Schmitt Trigger Input

TTL = TTL Input OD = Open Drain Output AN = Analog

### TABLE 5-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4              | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>Resets |

|-----------|--------|--------|--------|--------|--------------------|--------|--------|--------|--------|-----------------|---------------------------------|

| 06h, 106h | PORTB  | RB7    | RB6    | RB5    | RB4 <sup>(1)</sup> | RB3    | RB2    | RB1    | RB0    | xxxx xxxx       | uuuu uuuu                       |

| 86h, 186h | TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4             | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1111       | 1111 1111                       |

| 81h, 181h | OPTION | RBPU   | INTEDG | T0CS   | T0SE               | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

**Legend:** u = unchanged, x = unknown. Shaded cells are not used for PORTB.

Note 1: LVP configuration bit sets RB4 functionality.

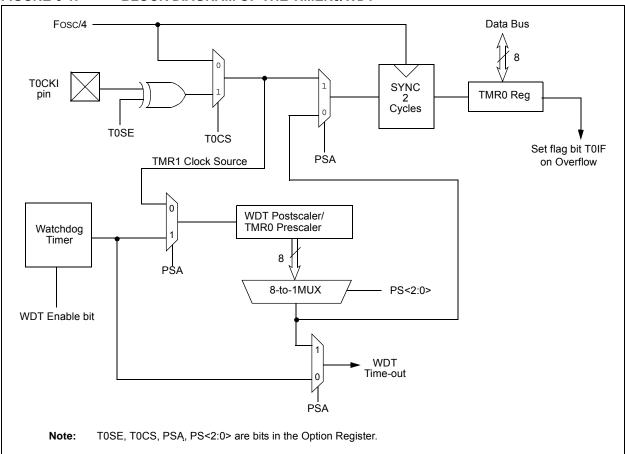

### 6.3 Timer0 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer. A prescaler assignment for the Timer0 module means that there is no postscaler for the Watchdog Timer, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

FIGURE 6-1: BLOCK DIAGRAM OF THE TIMERO/WDT

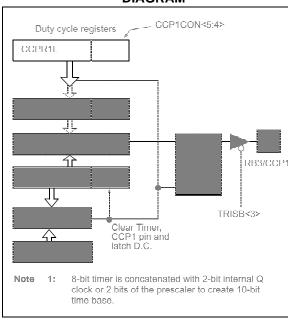

#### 9.3 PWM Mode

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTB data latch, the TRISB<3> bit must be cleared to make the CCP1 pin an output.

Note: Clearing the CCP1CON register will force the CCP1 PWM output latch to the default low level. This is not the PORTB I/O data latch.

Figure 9-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step by step procedure on how to set up the CCP module for PWM operation, see **Section 9.3.3 "Set-Up for PWM Operation"**.

FIGURE 9-3: SIMPLIFIED PWM BLOCK DIAGRAM

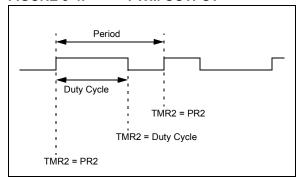

A PWM output (Figure 9-4) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (frequency = 1/period).

FIGURE 9-4: PWM OUTPUT

#### 9.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

$$PWM \ period = [(PR2) + 1] \cdot 4 \cdot Tosc \cdot TMR2 \ prescale$$

$value$

PWM frequency is defined as 1/[PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- · TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

Note: The Timer2 postscaler (see Section 8.0 "Timer2 Module") is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

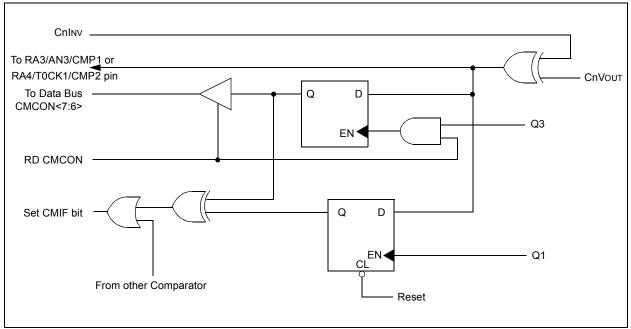

### 10.5 Comparator Outputs

The comparator outputs are read through the CMCON register. These bits are read-only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When the CM<2:0> = 110 or 001, multiplexors in the output path of the RA3 and RA4/T0CK1/CMP2 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 10-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA3/AN3/CMP1 and RA4/T0CK1/ CMP2 pins while in this mode.

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input, according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin that is defined as a digital input may cause the input buffer to consume more current than is specified.

### FIGURE 10-3: MODIFIED COMPARATOR OUTPUT BLOCK DIAGRAM

# 12.0 UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART) MODULE

The Universal Synchronous Asynchronous Receiver Transmitter (USART) is also known as a Serial Communications Interface (SCI). The USART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half-duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, Serial EEPROMs, etc.

The USART can be configured in the following modes:

- · Asynchronous (full-duplex)

- Synchronous Master (half-duplex)

- Synchronous Slave (half-duplex)

Bit SPEN (RCSTA<7>) and bits TRISB<2:1> have to be set in order to configure pins RB2/TX/CK and RB1/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

Register 12-1 shows the Transmit Status and Control Register (TXSTA) and Register 12-2 shows the Receive Status and Control Register (RCSTA).

### REGISTER 12-1: TXSTA - TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS: 98h)

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | R/W-0 | R-1  | R/W-0 |

|-------|-------|-------|-------|-----|-------|------|-------|

| CSRC  | TX9   | TXEN  | SYNC  | _   | BRGH  | TRMT | TX9D  |

| bit 7 |       |       |       |     |       |      | bit 0 |

bit 7 CSRC: Clock Source Select bit

Asynchronous mode

Don't care

Synchronous mode

- 1 = Master mode (Clock generated internally from BRG)

- 0 = Slave mode (Clock from external source)

- bit 6 **TX9**: 9-bit Transmit Enable bit

- 1 = Selects 9-bit transmission

- 0 = Selects 8-bit transmission

- bit 5 **TXEN**: Transmit Enable bit<sup>(1)</sup>

- 1 = Transmit enabled

- 0 = Transmit disabled

- bit 4 **SYNC**: USART Mode Select bit

- 1 = Synchronous mode

- 0 = Asynchronous mode

- bit 3 Unimplemented: Read as '0'

- bit 2 BRGH: High Baud Rate Select bit

Asynchronous mode

- 1 = High speed

- 0 = Low speed

Synchronous mode

Unused in this mode

bit 1 TRMT: Transmit Shift Register Status bit

- 1 = TSR empty

- 0 = TSR full

- bit 0 **TX9D**: 9th bit of transmit data. Can be parity bit.

Note 1: SREN/CREN overrides TXEN in SYNC mode.

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

TABLE 12-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD     | Fosc = 20 N |        |                    |       |        |                    |        |        |                    |  |  | 10 MHz |  | SPBRG |

|----------|-------------|--------|--------------------|-------|--------|--------------------|--------|--------|--------------------|--|--|--------|--|-------|

| RATE (K) | KBAUD       | ERROR  | value<br>(decimal) | KBAUD | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |  |  |        |  |       |

| 0.3      | NA          | _      | _                  | NA    | _      | _                  | NA     | _      | _                  |  |  |        |  |       |

| 1.2      | 1.221       | +1.73% | 255                | 1.202 | +0.16% | 207                | 1.202  | +0.16% | 129                |  |  |        |  |       |

| 2.4      | 2.404       | +0.16% | 129                | 2.404 | +0.16% | 103                | 2.404  | +0.16% | 64                 |  |  |        |  |       |

| 9.6      | 9.469       | -1.36% | 32                 | 9.615 | +0.16% | 25                 | 9.766  | +1.73% | 15                 |  |  |        |  |       |

| 19.2     | 19.53       | +1.73% | 15                 | 19.23 | +0.16% | 12                 | 19.53  | +1.73V | 7                  |  |  |        |  |       |

| 76.8     | 78.13       | +1.73% | 3                  | 83.33 | +8.51% | 2                  | 78.13  | +1.73% | 1                  |  |  |        |  |       |

| 96       | 104.2       | +8.51% | 2                  | NA    | _      | _                  | NA     | _      | _                  |  |  |        |  |       |

| 300      | 312.5       | +4.17% | 0                  | NA    | _      | _                  | NA     | _      | _                  |  |  |        |  |       |

| 500      | NA          | _      | _                  | NA    | _      | _                  | NA     | _      | _                  |  |  |        |  |       |

| HIGH     | 312.5       | _      | 0                  | 250   | _      | 0                  | 156.3  | _      | 0                  |  |  |        |  |       |

| LOW      | 1.221       | _      | 255                | 0.977 | _      | 255                | 0.6104 | _      | 255                |  |  |        |  |       |

| BAUD     | Fosc = 7.15 | 909 MHz | SPBRG              | 5.0688 MHz |        | SPBRG              | 4 MHz  |        | SPBRG              |

|----------|-------------|---------|--------------------|------------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD       | ERROR   | value<br>(decimal) | KBAUD      | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 0.3      | NA          | _       | _                  | 0.31       | +3.13% | 255                | 0.3005 | -0.17% | 207                |

| 1.2      | 1.203       | +0.23%  | 92                 | 1.2        | 0      | 65                 | 1.202  | +1.67% | 51                 |

| 2.4      | 2.380       | -0.83%  | 46                 | 2.4        | 0      | 32                 | 2.404  | +1.67% | 25                 |

| 9.6      | 9.322       | -2.90%  | 11                 | 9.9        | +3.13% | 7                  | NA     | _      | _                  |

| 19.2     | 18.64       | -2.90%  | 5                  | 19.8       | +3.13% | 3                  | NA     | _      | _                  |

| 76.8     | NA          | _       | _                  | 79.2       | +3.13% | 0                  | NA     | _      | _                  |

| 96       | NA          | _       | _                  | NA         | _      | _                  | NA     | _      | _                  |

| 300      | NA          | _       | _                  | NA         | _      | _                  | NA     | _      | _                  |

| 500      | NA          | _       | _                  | NA         | _      | _                  | NA     | _      | _                  |

| HIGH     | 111.9       | _       | 0                  | 79.2       | _      | 0                  | 62.500 | _      | 0                  |

| LOW      | 0.437       | _       | 255                | 0.3094     | _      | 255                | 3.906  | _      | 255                |

| BAUD     | Fosc = 3.57 | 9545 MHz | SPBRG              | 1 MHz  |        | SPBRG              | 32.768 kHz |         | SPBRG              |

|----------|-------------|----------|--------------------|--------|--------|--------------------|------------|---------|--------------------|

| RATE (K) | KBAUD       | ERROR    | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) | KBAUD      | ERROR   | value<br>(decimal) |

| 0.3      | 0.301       | +0.23%   | 185                | 0.300  | +0.16% | 51                 | 0.256      | -14.67% | 1                  |

| 1.2      | 1.190       | -0.83%   | 46                 | 1.202  | +0.16% | 12                 | NA         | _       | _                  |

| 2.4      | 2.432       | +1.32%   | 22                 | 2.232  | -6.99% | 6                  | NA         | _       | _                  |

| 9.6      | 9.322       | -2.90%   | 5                  | NA     | _      | _                  | NA         | _       | _                  |

| 19.2     | 18.64       | -2.90%   | 2                  | NA     | _      | _                  | NA         | _       | _                  |

| 76.8     | NA          | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| 96       | NA          | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| 300      | NA          | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| 500      | NA          | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| HIGH     | 55.93       | _        | 0                  | 15.63  | _      | 0                  | 0.512      | _       | 0                  |

| LOW      | 0.2185      | _        | 255                | 0.0610 | _      | 255                | 0.0020     | _       | 255                |

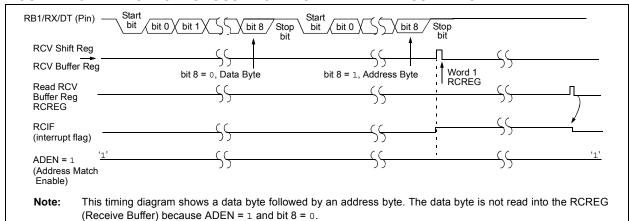

### FIGURE 12-5: ASYNCHRONOUS RECEPTION WITH ADDRESS DETECT

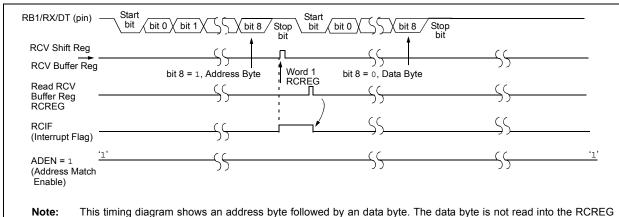

### FIGURE 12-6: ASYNCHRONOUS RECEPTION WITH ADDRESS BYTE FIRST

(receive buffer) because ADEN was not updated (still = 1) and bit 8 = 0.

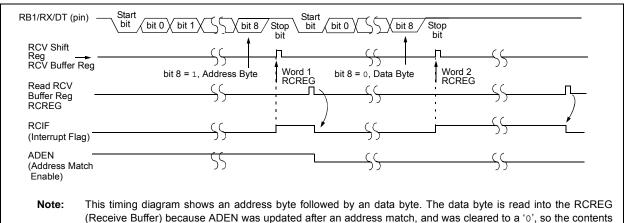

## FIGURE 12-7: ASYNCHRONOUS RECEPTION WITH ADDRESS BYTE FIRST FOLLOWED BY VALID DATA BYTE

of the Receive Shift Register (RSR) are read into the Receive Buffer regardless of the value of bit 8.

### 12.4.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>) or enable bit CREN (RCSTA<4>). Data is sampled on the RB1/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read-only bit which is reset by the hardware. In this case, it is reset when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a twodeep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full, then overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited, so it is essential to clear bit OERR if it is set. The 9th receive bit is buffered the same way as the receive data. Reading the RCREG register, will load bit RX9D with a new value, therefore it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old RX9D information.

Follow these steps when setting up a Synchronous Master Reception:

- TRISB<1> and TRISB<2> should both be set to '1' to configure the RB1/RX/DT and RB2/TX/CK pins as inputs. Output drive, when required, is controlled by the peripheral circuitry.

- Initialize the SPBRG register for the appropriate baud rate. (Section 12.1 "USART Baud Rate Generator (BRG)").

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- If interrupts are desired, then set enable bit RCIE.

- 6. If 9-bit reception is desired, then set bit RX9.

- If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register.

- 11. If an OERR error occurred, clear the error by clearing bit CREN.

TABLE 12-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Address | Name  | Bit 7   | Bit 6                       | Bit 5   | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR | Value on all other Resets |

|---------|-------|---------|-----------------------------|---------|--------|-------|--------|--------|--------|------------------|---------------------------|

| 0Ch     | PIR1  | EEIF    | CMIF                        | RCIF    | TXIF   |       | CCP1IF | TMR2IF | TMR1IF | 0000 -000        | 0000 -000                 |

| 18h     | RCSTA | SPEN    | RX9                         | SREN    | CREN   | ADEN  | FERR   | OERR   | RX9D   | 0000 000x        | 0000 000x                 |

| 1Ah     | RCREG | USART F | Receive                     | Data Re | gister |       |        |        |        | 0000 0000        | 0000 0000                 |

| 8Ch     | PIE1  | EPIE    | CMIE                        | RCIE    | TXIE   | _     | CCP1IE | TMR2IE | TMR1IE | -000 0000        | -000 -000                 |

| 98h     | TXSTA | CSRC    | TX9                         | TXEN    | SYNC   |       | BRGH   | TRMT   | TX9D   | 0000 -010        | 0000 -010                 |

| 99h     | SPBRG | Baud Ra | aud Rate Generator Register |         |        |       |        |        |        | 0000 0000        | 0000 0000                 |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous master reception.

| IORLW            | Inclusive OR Literal with W                                                                                     |

|------------------|-----------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] IORLW k                                                                                                 |

| Operands:        | $0 \leq k \leq 255$                                                                                             |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                    |

| Status Affected: | Z                                                                                                               |

| Encoding:        | 11 1000 kkkk kkkk                                                                                               |

| Description:     | The contents of the W register is OR'ed with the eight-bit literal 'k'. The result is placed in the W register. |

| Words:           | 1                                                                                                               |

| Cycles:          | 1                                                                                                               |

| Example          | IORLW 0x35                                                                                                      |

|                  | Before Instruction $W = 0x9A$ After Instruction $W = 0xBF$ $Z = 0$                                              |

| MOVLW            | Move L              | iteral to             | W                                        |      |

|------------------|---------------------|-----------------------|------------------------------------------|------|

| Syntax:          | [ label ]           | MOVL                  | W k                                      |      |

| Operands:        | $0 \leq k \leq 255$ |                       |                                          |      |

| Operation:       | $k \rightarrow (W)$ |                       |                                          |      |

| Status Affected: | None                |                       |                                          |      |

| Encoding:        | 11                  | 00xx                  | kkkk                                     | kkkk |

| Description:     | into W r            | egister. <sup>-</sup> | ral 'k' is lo<br>The "don'<br>nble as 'o | t    |

| Words:           | 1                   |                       |                                          |      |

| Cycles:          | 1                   |                       |                                          |      |

| <u>Example</u>   | MOVLW               | 0x5A                  |                                          |      |

|                  | After Ins<br>W      | struction<br>= 0x5/   | Ą                                        |      |

|                  |                     | GAG.                  | •                                        |      |

| IORWF            | Inclusive OR W with f                                                                                                                                           |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] IORWF f,d                                                                                                                                             |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                              |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (dest)                                                                                                                               |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |

| Encoding:        | 00 0100 dfff ffff                                                                                                                                               |  |  |  |

| Description:     | Inclusive OR the W register with register 'f'. If 'd' is 'o', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'. |  |  |  |

| Words:           | 1                                                                                                                                                               |  |  |  |

| Cycles:          | 1                                                                                                                                                               |  |  |  |

| <u>Example</u>   | IORWF REG1, 0                                                                                                                                                   |  |  |  |

|                  | Before Instruction  REG1 = 0x13  W = 0x91  After Instruction  REG1 = 0x13  W = 0x93  7 = 1                                                                      |  |  |  |

| MOVF             | Move f                                                                                                                                                                                                                                                      |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] MOVF f,d                                                                                                                                                                                                                                          |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                          |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                    |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                           |  |  |  |

| Encoding:        | 00 1000 dfff ffff                                                                                                                                                                                                                                           |  |  |  |

| Description:     | The contents of register 'f' is moved to a destination dependent upon the status of 'd'. If d = 0, destination is W register. If d = 1, the destination is file register f itself. d = 1 is useful to test a file register since status flag Z is affected. |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                           |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                           |  |  |  |

| <u>Example</u>   | MOVF REG1, 0                                                                                                                                                                                                                                                |  |  |  |

|                  | After Instruction  W = value in REG1 register  7 = 1                                                                                                                                                                                                        |  |  |  |

### 16.0 DEVELOPMENT SUPPORT

The PIC® microcontrollers and dsPIC® digital signal controllers are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB® IDE Software

- · Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C for Various Device Families

- MPASM™ Assembler

- MPLINK<sup>TM</sup> Object Linker/ MPLIB<sup>TM</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- · In-Circuit Debuggers

- MPLAB ICD 3

- PICkit™ 3 Debug Express

- · Device Programmers

- PICkit™ 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

### 16.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows® operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- · A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

### 17.0 ELECTRICAL SPECIFICATIONS

### **Absolute Maximum Ratings(†)**

| Ambient temperature under bias                                                                                             | 40 to +125°C                       |

|----------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Storage temperature                                                                                                        | 65°C to +150°C                     |

| Voltage on VDD with respect to Vss                                                                                         | 0.3 to +6.5V                       |

| Voltage on MCLR and RA4 with respect to Vss                                                                                | 0.3 to +14V                        |

| Voltage on all other pins with respect to Vss                                                                              | 0.3V to VDD + 0.3V                 |

| Total power dissipation <sup>(1)</sup>                                                                                     | 800 mW                             |

| Maximum current out of Vss pin                                                                                             | 300 mA                             |

| Maximum current into VDD pin                                                                                               | 250 mA                             |

| Input clamp current, IiK (VI < 0 or VI > VDD)                                                                              | ± 20 mA                            |

| Output clamp current, Iok (Vo < 0 or Vo >VDD)                                                                              | ± 20 mA                            |

| Maximum output current sunk by any I/O pin                                                                                 | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                                              | 25 mA                              |

| Maximum current sunk by PORTA and PORTB (Combined)                                                                         | 200 mA                             |

| Maximum current sourced by PORTA and PORTB (Combined)                                                                      | 200 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD $- \Sigma$ IOH} + $\Sigma$ {(VDD $- \Sigma$ ) | VOH) x IOH} + $\Sigma$ (VOI x IOL) |

**† NOTICE**: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Note: Voltage spikes below Vss at the  $\overline{\text{MCLR}}$  pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100  $\Omega$  should be used when applying a "low" level to the  $\overline{\text{MCLR}}$  pin rather than pulling this pin directly to Vss.

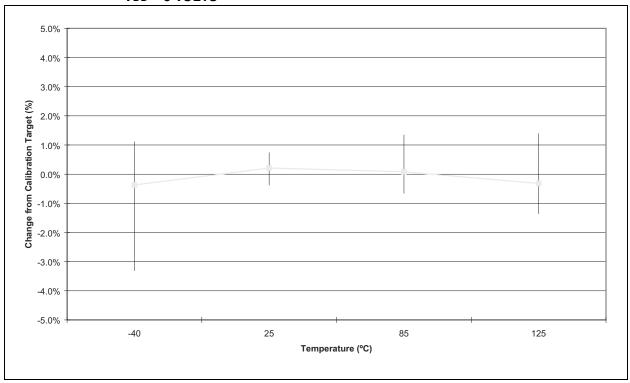

FIGURE 18-10: TYPICAL INTERNAL OSCILLATOR FREQUENCY vs. TEMPERATURE VDD = 3 VOLTS

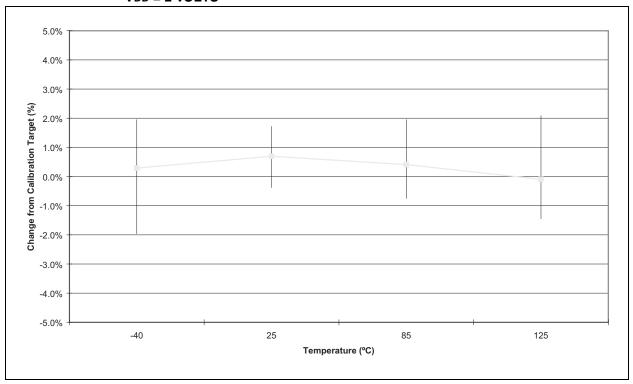

FIGURE 18-11: TYPICAL INTERNAL OSCILLATOR FREQUENCY vs. TEMPERATURE VDD = 2 VOLTS

### 19.0 PACKAGING INFORMATION

### 19.1 Package Marking Information

18-Lead PDIP

18-Lead SOIC (.300")

20-Lead SSOP

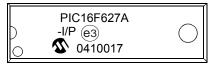

28-Lead QFN

Example

Example

Example

Example

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (e3)

can be found on the outer packaging for this package.

**ote**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

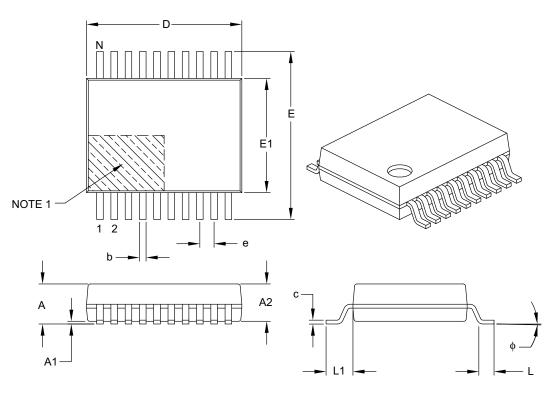

### 20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          | MILLIMETERS |      |  |

|--------------------------|------------------|----------|-------------|------|--|

|                          | Dimension Limits | MIN      | NOM         | MAX  |  |

| Number of Pins           | N                |          | 20          |      |  |

| Pitch                    | е                | 0.65 BSC |             |      |  |

| Overall Height           | A                | _        | _           | 2.00 |  |

| Molded Package Thickness | A2               | 1.65     | 1.75        | 1.85 |  |

| Standoff                 | A1               | 0.05     | _           | _    |  |

| Overall Width            | E                | 7.40     | 7.80        | 8.20 |  |

| Molded Package Width     | E1               | 5.00     | 5.30        | 5.60 |  |

| Overall Length           | D                | 6.90     | 7.20        | 7.50 |  |

| Foot Length              | L                | 0.55     | 0.75        | 0.95 |  |

| Footprint                | L1               | 1.25 REF |             |      |  |

| Lead Thickness           | С                | 0.09     | _           | 0.25 |  |

| Foot Angle               | ф                | 0°       | 4°          | 8°   |  |

| Lead Width               | b                | 0.22     | _           | 0.38 |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-072B

**NOTES:**

| INDEX                               |     | CCP2X:CCP2Y Bits                     | 57  |

|-------------------------------------|-----|--------------------------------------|-----|

| A                                   |     | Clocking Scheme/Instruction Cycle    | 15  |

| A                                   |     | CLRF Instruction                     |     |

| A/D                                 |     | CLRW Instruction                     |     |

| Special Event Trigger (CCP)         |     | CLRWDT Instruction                   |     |

| Absolute Maximum Ratings            |     | CMCON Register                       | 63  |

| ADDLW Instruction                   |     | Code Examples                        | 0.4 |

| ADDWF Instruction                   |     | Data EEPROM Refresh Routine          |     |

| ANDLW Instruction                   |     | Code ProtectionCOMF Instruction      |     |

| ANDWF Instruction                   |     | Comparator                           | 122 |

| Assembler                           | 11  | Block Diagrams                       |     |

| MPASM Assembler                     | 132 | I/O Operating Modes                  | 64  |

| WII AGW AGGINDICI                   | 102 | Modified Comparator Output           |     |

| В                                   |     | Comparator Module                    |     |

| Baud Rate Error                     | 75  | Configuration                        |     |

| Baud Rate Formula                   | 75  | Interrupts                           | 67  |

| BCF Instruction                     | 120 | Operation                            |     |

| Block Diagrams                      |     | Reference                            |     |

| Comparator                          |     | Compare (CCP Module)                 |     |

| I/O Operating Modes                 |     | Block Diagram                        |     |

| Modified Comparator Output          | 66  | CCP Pin Configuration                |     |

| I/O Ports                           |     | CCPR1H:CCPR1L Registers              |     |

| RB0/INT Pin                         |     | Software Interrupt                   |     |

| RB1/RX/DT Pin                       |     | Special Event Trigger                |     |

| RB2/TX/CK Pin                       |     | Timer1 Mode Selection                |     |

| RB3/CCP1 Pin<br>RB4/PGM Pin         |     | CONFIG Register                      |     |

| RB5 Pin                             |     | Configuration Bits Crystal Operation |     |

| RB6/T1OSO/T1CKI Pin                 |     | Customer Change Notification Service |     |

| RB7/T1OSI Pin                       |     | Customer Notification Service        |     |

| RC Oscillator Mode                  |     | Customer Support                     |     |

| USART Receive                       |     |                                      | 170 |

| USART Transmit                      |     | D                                    |     |

| BRGH bit                            | 75  | Data EEPROM Memory                   | 91  |

| Brown-Out Reset (BOR)               | 103 | EECON1 Register                      | 91  |

| BSF Instruction                     |     | EECON2 Register                      | 91  |

| BTFSC Instruction                   | 120 | Operation During Code Protection     |     |

| BTFSS Instruction                   | 121 | Reading                              |     |

| С                                   |     | Spurious Write Protection            |     |

|                                     |     | Using                                |     |

| C Compilers MPLAB C18               | 422 | Write Verify                         |     |

| CALL Instruction                    |     | Writing to  Data Memory Organization |     |

| Capture (CCP Module)                |     | DECF Instruction                     |     |

| Block Diagram                       |     | DECFSZ Instruction                   |     |

| CCP Pin Configuration               |     | Development Support                  |     |

| CCPR1H:CCPR1L Registers             |     | Device Differences                   |     |

| Changing Between Capture Prescalers |     | Device Migrations                    |     |

| Prescaler                           |     | Dual-speed Oscillator Modes          |     |

| Software Interrupt                  |     | ·                                    |     |

| Timer1 Mode Selection               | 58  | E                                    |     |

| Capture/Compare/PWM (CCP)           | 57  | EECON1 Register                      | 92  |

| Capture Mode. See Capture           |     | EECON1 register                      |     |

| CCP1                                |     | EECON2 register                      |     |

| CCPR1H Register                     |     | Errata                               |     |

| CCPR1L Register                     |     | External Crystal Oscillator Circuit  | 100 |

| CCP2                                | 57  | F                                    |     |

| Compare Mode. See Compare           |     | •                                    |     |

| PWM Mode. See PWM                   |     | Fuses. See Configuration Bits        |     |

| Timer Resources                     |     | G                                    |     |

| CCP1CON Register                    |     | General-Purpose Register File        | 17  |

| CCP1M Bits CCP1X:CCP1Y Bits         |     | GOTO Instruction                     |     |

| CCP2CON Register                    | ນາ  |                                      |     |

| CCD2M<2:2> Dita                     | 57  |                                      |     |