Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 224 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f627at-e-so |

#### 1.0 GENERAL DESCRIPTION

The PIC16F627A/628A/648A are 18-pin Flash-based members of the versatile PIC16F627A/628A/648A family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers.

All PIC® microcontrollers employ an advanced RISC architecture. The PIC16F627A/628A/648A have enhanced core features, an eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single-cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available, complemented by a large register set

PIC16F627A/628A/648A microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

PIC16F627A/628A/648A devices have integrated features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption.

The PIC16F627A/628A/648A has 8 oscillator configurations. The single-pin RC oscillator provides a low-cost solution. The LP oscillator minimizes power consumption, XT is a standard crystal, and INTOSC is a self-contained precision two-speed internal oscillator.

The HS mode is for High-Speed crystals. The EC mode is for an external clock source.

The Sleep (Power-down) mode offers power savings. Users can wake-up the chip from Sleep through several external interrupts, internal interrupts and Resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock-up.

Table 1-1 shows the features of the PIC16F627A/628A/648A mid-range microcontroller family.

A simplified block diagram of the PIC16F627A/628A/648A is shown in Figure 3-1.

The PIC16F627A/628A/648A series fits in applications ranging from battery chargers to low power remote sensors. The Flash technology makes customizing application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages makes this microcontroller series ideal for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16F627A/628A/648A very versatile.

#### 1.1 Development Support

The PIC16F627A/628A/648A family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low cost in-circuit debugger, a low cost development programmer and a full-featured programmer. A Third Party "C" compiler support tool is also available.

TABLE 1-1: PIC16F627A/628A/648A FAMILY OF DEVICES

|             |                                      | PIC16F627A                                         | PIC16F628A                                         | PIC16F648A                                         | PIC16LF627A                                        | PIC16LF628A                                        | PIC16LF648A                                        |

|-------------|--------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|

| Clock       | Maximum Frequency of Operation (MHz) | 20                                                 | 20                                                 | 20                                                 | 20                                                 | 20                                                 | 20                                                 |

|             | Flash Program<br>Memory (words)      | 1024                                               | 2048                                               | 4096                                               | 1024                                               | 2048                                               | 4096                                               |

| Memory      | RAM Data Memory (bytes)              | 224                                                | 224                                                | 256                                                | 224                                                | 224                                                | 256                                                |

|             | EEPROM Data<br>Memory (bytes)        | 128                                                | 128                                                | 256                                                | 128                                                | 128                                                | 256                                                |

|             | Timer module(s)                      | TMR0, TMR1,<br>TMR2                                |

|             | Comparator(s)                        | 2                                                  | 2                                                  | 2                                                  | 2                                                  | 2                                                  | 2                                                  |

| Peripherals | Capture/Compare/<br>PWM modules      | 1                                                  | 1                                                  | 1                                                  | 1                                                  | 1                                                  | 1                                                  |

|             | Serial Communications                | USART                                              | USART                                              | USART                                              | USART                                              | USART                                              | USART                                              |

|             | Internal Voltage<br>Reference        | Yes                                                | Yes                                                | Yes                                                | Yes                                                | Yes                                                | Yes                                                |

|             | Interrupt Sources                    | 10                                                 | 10                                                 | 10                                                 | 10                                                 | 10                                                 | 10                                                 |

|             | I/O Pins                             | 16                                                 | 16                                                 | 16                                                 | 16                                                 | 16                                                 | 16                                                 |

| Features    | Voltage Range (Volts)                | 3.0-5.5                                            | 3.0-5.5                                            | 3.0-5.5                                            | 2.0-5.5                                            | 2.0-5.5                                            | 2.0-5.5                                            |

|             | Brown-out Reset                      | Yes                                                | Yes                                                | Yes                                                | Yes                                                | Yes                                                | Yes                                                |

|             | Packages                             | 18-pin DIP,<br>SOIC, 20-pin<br>SSOP,<br>28-pin QFN |

All PIC® family devices have Power-on Reset, selectable Watchdog Timer, selectable code-protect and high I/O current capability. All PIC16F627A/628A/648A family devices use serial programming with clock pin RB6 and data pin RB7.

TABLE 3-2: PIC16F627A/628A/648A PINOUT DESCRIPTION

| Name               | Function | Input Type | Output Type | Description                                                                                                                                                    |

|--------------------|----------|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RA0/AN0            | RA0      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                         |

|                    | AN0      | AN         | _           | Analog comparator input                                                                                                                                        |

| RA1/AN1            | RA1      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                         |

|                    | AN1      | AN         | _           | Analog comparator input                                                                                                                                        |

| RA2/AN2/VREF       | RA2      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                         |

|                    | AN2      | AN         | _           | Analog comparator input                                                                                                                                        |

|                    | VREF     | _          | AN          | VREF output                                                                                                                                                    |

| RA3/AN3/CMP1       | RA3      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                         |

|                    | AN3      | AN         | _           | Analog comparator input                                                                                                                                        |

|                    | CMP1     | _          | CMOS        | Comparator 1 output                                                                                                                                            |

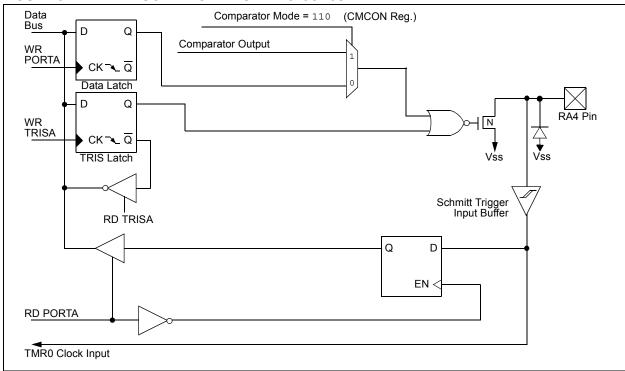

| RA4/T0CKI/CMP2     | RA4      | ST         | OD          | Bidirectional I/O port                                                                                                                                         |

|                    | T0CKI    | ST         | _           | Timer0 clock input                                                                                                                                             |

|                    | CMP2     | _          | OD          | Comparator 2 output                                                                                                                                            |

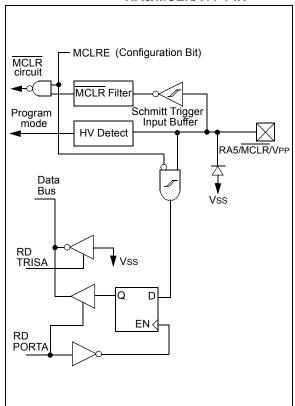

| RA5/MCLR/VPP       | RA5      | ST         | _           | Input port                                                                                                                                                     |

|                    | MCLR     | ST         | _           | Master clear. When configured as MCLR, this pin is an active low Reset to the device.  Voltage on MCLR/VPP must not exceed VDD during normal device operation. |

|                    | VPP      | _          | _           | Programming voltage input                                                                                                                                      |

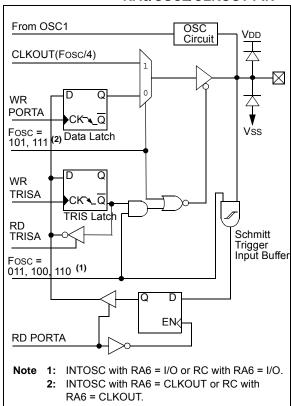

| RA6/OSC2/CLKOUT    | RA6      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                         |

|                    | OSC2     | _          | XTAL        | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode.                                                                        |

|                    | CLKOUT   | _          | CMOS        | In RC/INTOSC mode, OSC2 pin can output CLKOUT, which has 1/4 the frequency of OSC1.                                                                            |

| RA7/OSC1/CLKIN     | RA7      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                         |

|                    | OSC1     | XTAL       | _           | Oscillator crystal input                                                                                                                                       |

|                    | CLKIN    | ST         | _           | External clock source input. RC biasing pin.                                                                                                                   |

| RB0/INT            | RB0      | TTL        | CMOS        | Bidirectional I/O port. Can be software programmed for internal weak pull-up.                                                                                  |

|                    | INT      | ST         | _           | External interrupt                                                                                                                                             |

| RB1/RX/DT          | RB1      | TTL        | CMOS        | Bidirectional I/O port. Can be software programmed for internal weak pull-up.                                                                                  |

|                    | RX       | ST         | _           | USART receive pin                                                                                                                                              |

|                    | DT       | ST         | CMOS        | Synchronous data I/O                                                                                                                                           |

| RB2/TX/CK          | RB2      | TTL        | CMOS        | Bidirectional I/O port. Can be software programmed for internal weak pull-up.                                                                                  |

|                    | TX       | _          | CMOS        | USART transmit pin                                                                                                                                             |

|                    | CK       | ST         | CMOS        | Synchronous clock I/O                                                                                                                                          |

| RB3/CCP1           | RB3      | TTL        | CMOS        | Bidirectional I/O port. Can be software programmed for internal weak pull-up.                                                                                  |

|                    | CCP1     | ST         | CMOS        | Capture/Compare/PWM I/O                                                                                                                                        |

| Legend: O = Output |          | 01100      | MOS Output  | D = Dower                                                                                                                                                      |

**Legend:** O = Output CMOS = CMOS Output P = Power

— = Not used I = Input ST = Schmitt Trigger Input

TTL = TTL Input OD = Open Drain Output AN = Analog

FIGURE 5-4: BLOCK DIAGRAM OF RA4/T0CKI/CMP2 PIN

FIGURE 5-5: BLOCK DIAGRAM OF THE RA5/MCLR/VPP PIN

FIGURE 5-6: BLOCK DIAGRAM OF RA6/OSC2/CLKOUT PIN

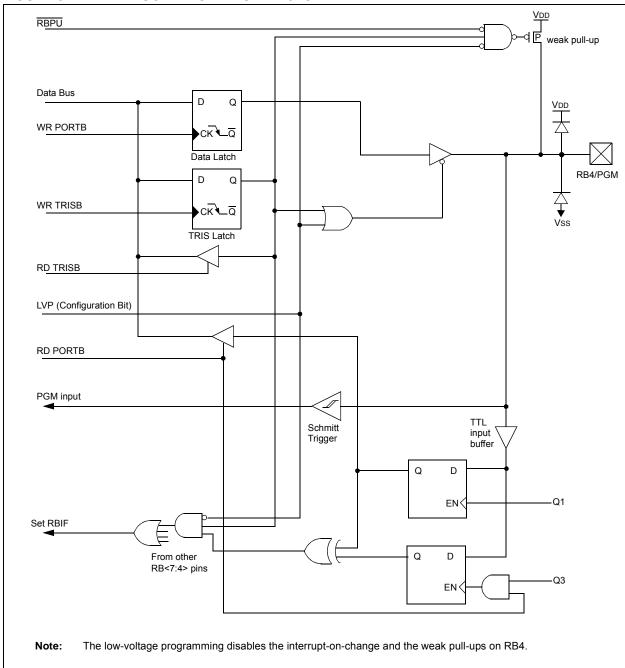

FIGURE 5-12: BLOCK DIAGRAM OF RB4/PGM PIN

**NOTES:**

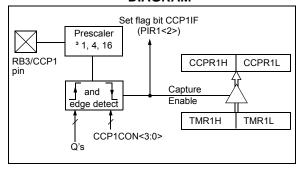

#### 9.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RB3/CCP1. An event is defined as:

- · Every falling edge

- · Every rising edge

- · Every 4th rising edge

- · Every 16th rising edge

An event is selected by control bits CCP1M<3:0> (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 9.1.1 CCP PIN CONFIGURATION

In Capture mode, the RB3/CCP1 pin should be configured as an input by setting the TRISB<3> bit.

**Note:** If the RB3/CCP1 is configured as an output, a write to the port can cause a capture condition.

# FIGURE 9-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 9.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 9.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in Operating mode.

#### 9.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M<3:0>. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 9-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

### EXAMPLE 9-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | G;Load the W reg with   |

|       |             | ; the new prescaler     |

|       |             | ; mode value and CCP ON |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ; value                 |

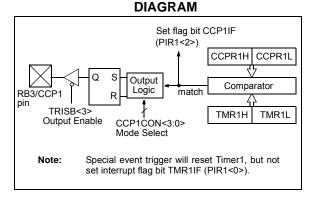

#### 9.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RB3/CCP1 pin is:

- · Driven high

- · Driven low

- · Remains unchanged

The action on the pin is based on the value of control bits CCP1M<3:0> (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

# FIGURE 9-2: COMPARE MODE OPERATION BLOCK

#### 10.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the RA0 through RA3 pins. The on-chip Voltage Reference (Section 11.0 "Voltage Reference Module") can also be an input to the comparators.

The CMCON register, shown in Register 10-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 10-1.

#### REGISTER 10-1: CMCON – COMPARATOR CONFIGURATION REGISTER (ADDRESS: 01Fh)

| R-0   | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| C2OUT | C1OUT | C2INV | C1INV | CIS   | CM2   | CM1   | CM0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7 C2OUT: Comparator 2 Output bit

When C2INV = 0:

1 = C2 VIN+ > C2 VIN-

0 = C2 VIN+ < C2 VIN-

When C2INV = 1:

1 = C2 VIN+ < C2 VIN-

0 = C2 VIN+ > C2 VIN-

bit 6 C10UT: Comparator 1 Output bit

When C1INV = 0:

1 = C1 VIN+ > C1 VIN-

0 = C1 VIN+ < C1 VIN-

When C1INV = 1:

1 = C1 VIN+ < C1 VIN-

0 = C1 VIN+ > C1 VIN-

bit 5 C2INV: Comparator 2 Output Inversion bit

1 = C2 Output inverted

0 = C2 Output not inverted

bit 4 C1INV: Comparator 1 Output Inversion bit

1 = C1 Output inverted

0 = C1 Output not inverted

bit 3 CIS: Comparator Input Switch bit

When CM<2:0>: = 001

Then:

1 = C1 VIN- connects to RA3

0 = C1 VIN- connects to RA0

When CM < 2:0 > = 010

Then:

1 = C1 VIN- connects to RA3

C2 VIN- connects to RA2

0 = C1 Vin- connects to RA0

C2 VIN- connects to RA1

bit 2-0 CM<2:0>: Comparator Mode bits

Figure 10-1 shows the comparator modes and CM<2:0> bit settings

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

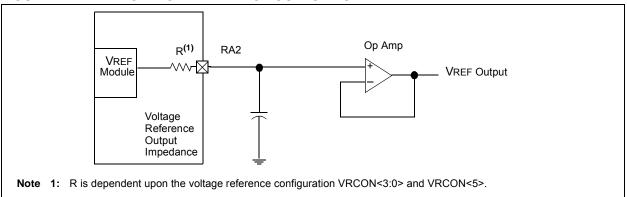

#### FIGURE 11-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

TABLE 11-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR | Value On<br>All Other<br>Resets |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 9Fh     | VRCON | VREN   | VROE   | VRR    | _      | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 1Fh     | CMCON | C2OUT  | C10UT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 85h     | TRISA | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

**Legend:** - = Unimplemented, read as '0'.

### 12.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 12-1 shows the formula for computation of the baud rate for different USART modes, which only apply in Master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 12-1. From this, the error in baud rate can be determined.

Example 12-1 shows the calculation of the baud rate error for the following conditions:

Fosc = 16 MHz

Desired Baud Rate = 9600

BRGH = 0

SYNC = 0

### EQUATION 12-1: CALCULATING BAUD RATE ERROR

Desired Baud Rate =

$$\frac{Fosc}{64(x+I)}$$

$$9600 = \frac{16000000}{64(x+1)}$$

$$x = 25.042$$

Calculated Baud Rate =

$$\frac{16000000}{64(25+1)}$$

= 9615

$$=\frac{9615-9600}{9600}=0.16\%$$

It may be advantageous to use the high baud rate (BRGH = 1) even for slower baud clocks. This is because the Fosc/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared) and ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

The data on the RB1/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

TABLE 12-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = Fosc/(4(X+1))   | NA                         |

**Legend:** X = value in SPBRG (0 to 255)

#### TABLE 12-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name  | Bit 7   | Bit 6     | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on POR | Value on all other Resets |

|---------|-------|---------|-----------|------------|-------|-------|-------|-------|-------|--------------|---------------------------|

| 98h     | TXSTA | CSRC    | TX9       | TXEN       | SYNC  | _     | BRGH  | TRMT  | TX9D  | 0000 -010    | 0000 -010                 |

| 18h     | RCSTA | SPEN    | RX9       | SREN       | CREN  | ADEN  | FERR  | OERR  | RX9D  | 0000 000x    | 0000 000x                 |

| 99h     | SPBRG | Baud Ra | te Genera | ator Regis | ster  |       |       |       |       | 0000 0000    | 0000 0000                 |

**Legend:** x = unknown, - = unimplemented read as '0'. Shaded cells are not used for the BRG.

# 13.8 Data EEPROM Operation During Code-Protect

When the device is code-protected, the CPU is able to read and write data to the data EEPROM.

TABLE 13-1: REGISTERS/BITS ASSOCIATED WITH DATA EEPROM

| Address | Name                  | Bit 7  | Bit 6                     | Bit 5     | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other<br>Resets |

|---------|-----------------------|--------|---------------------------|-----------|-------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| 9Ah     | EEDATA                | EEPROI | M Data R                  | egister   |       |       |       |       |       | xxxx xxxx                     | uuuu uuuu                       |

| 9Bh     | EEADR                 | EEPRO  | M Addres                  | s Registe | er    |       |       |       |       | xxxx xxxx                     | uuuu uuuu                       |

| 9Ch     | EECON1                |        | WRERR WREN WR RD          |           |       |       |       |       | x000  | q000                          |                                 |

| 9Dh     | EECON2 <sup>(1)</sup> | EEPROI | EEPROM Control Register 2 |           |       |       |       |       |       |                               |                                 |

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition.

Shaded cells are not used by data EEPROM.

Note 1: EECON2 is not a physical register.

| MOVWF            | Move W to f                                                                         |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [label] MOVWF f                                                                     |  |  |  |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                                                                 |  |  |  |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                                                               |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                |  |  |  |  |  |  |  |

| Encoding:        | 00 0000 lfff ffff                                                                   |  |  |  |  |  |  |  |

| Description:     | Move data from W register to register 'f'.                                          |  |  |  |  |  |  |  |

| Words:           | 1                                                                                   |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                   |  |  |  |  |  |  |  |

| <u>Example</u>   | MOVWF REG1                                                                          |  |  |  |  |  |  |  |

|                  | Before Instruction  REG1 = 0xFF  W = 0x4F  After Instruction  REG1 = 0x4F  W = 0x4F |  |  |  |  |  |  |  |

| OPTION               | Load Op                                                                                                                                                                                                                                                                       | otion Re | gister |      |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|------|--|--|--|

| Syntax:<br>Operands: | [ label ]<br>None                                                                                                                                                                                                                                                             | OPTIO    | N      |      |  |  |  |

| Operation:           | $(W) \rightarrow OPTION$                                                                                                                                                                                                                                                      |          |        |      |  |  |  |

| Status Affected:     | None                                                                                                                                                                                                                                                                          |          | 1      | ı    |  |  |  |

| Encoding:            | 00                                                                                                                                                                                                                                                                            | 0000     | 0110   | 0010 |  |  |  |

| Description:         | The contents of the W register are loaded in the OPTION register. This instruction is supported for code compatibility with PIC16C5X products. Since OPTION is a readable/writable register, the user can directly address it. Using only register instruction such as MOVWF. |          |        |      |  |  |  |

| Words:               | 1                                                                                                                                                                                                                                                                             |          |        |      |  |  |  |

| Cycles:              | 1                                                                                                                                                                                                                                                                             |          |        |      |  |  |  |

| <u>Example</u>       |                                                                                                                                                                                                                                                                               |          |        |      |  |  |  |

|                      | To maintain upward compatibility with future PIC® MCU products, do not use this instruction.                                                                                                                                                                                  |          |        |      |  |  |  |

| NOP              | No Ope    | eration |      |      |

|------------------|-----------|---------|------|------|

| Syntax:          | [ label ] | NOP     |      |      |

| Operands:        | None      |         |      |      |

| Operation:       | No oper   | ration  |      |      |

| Status Affected: | None      |         |      |      |

| Encoding:        | 00        | 0000    | 0xx0 | 0000 |

| Description:     | No oper   | ration. |      |      |

| Words:           | 1         |         |      |      |

| Cycles:          | 1         |         |      |      |

| Example Page 1   | NOP       |         |      |      |

|                  |           |         |      |      |

| RETFIE           | Return from Interrupt                                                                                                                                                                              |                            |      |      |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------|------|--|

| Syntax:          | [ label ] RETFIE                                                                                                                                                                                   |                            |      |      |  |

| Operands:        | None                                                                                                                                                                                               |                            |      |      |  |

| Operation:       | TOS → PC,<br>1 → GIE                                                                                                                                                                               |                            |      |      |  |

| Status Affected: | None                                                                                                                                                                                               |                            |      |      |  |

| Encoding:        | 00                                                                                                                                                                                                 | 0000                       | 0000 | 1001 |  |

| Description:     | Return from Interrupt. Stack is POPed and Top-of-Stack (TOS) is loaded in the PC. Interrupts are enabled by setting Global Interrupt Enable bit, GIE (INTCON<7>). This is a two-cycle instruction. |                            |      |      |  |

| Words:           | 1                                                                                                                                                                                                  |                            |      |      |  |

| Cycles:          | 2                                                                                                                                                                                                  |                            |      |      |  |

| Example          | RETFIE                                                                                                                                                                                             |                            |      |      |  |

|                  | -                                                                                                                                                                                                  | errupt<br>C = To<br>IE = 1 | os   |      |  |

| RETLW            | Return with Literal in W                                                                                                                                                |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                     |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                            |  |  |  |  |

| Status Affected: | None                                                                                                                                                                    |  |  |  |  |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                       |  |  |  |  |

| Description:     | The W register is loaded with the eight-bit literal 'k'. The program counter is loaded from the top of the stack (the return address). This is a two-cycle instruction. |  |  |  |  |

| Words:           | 1                                                                                                                                                                       |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                       |  |  |  |  |

| <u>Example</u>   | CALL TABLE;W contains table ;offset value • ;W now has table value •                                                                                                    |  |  |  |  |

| TABLE            | • ADDWF PC;W = offset RETLW k1;Begin table RETLW k2; • • • RETLW kn; End of table  Before Instruction W = 0x07  After Instruction W = value of k8                       |  |  |  |  |

| RLF              | Rotate Left f through Carry                                                                                                                                                                           |                     |       |      |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------|------|--|

| Syntax:          | [ label ]                                                                                                                                                                                             | RLF                 | f,d   |      |  |

| Operands:        | $0 \le f \le 12$ $d \in [0,1]$                                                                                                                                                                        |                     |       |      |  |

| Operation:       | See des                                                                                                                                                                                               | cription b          | pelow |      |  |

| Status Affected: | С                                                                                                                                                                                                     |                     |       |      |  |

| Encoding:        | 00                                                                                                                                                                                                    | 1101                | dfff  | ffff |  |

| Description:     | The contents of register 'f' are rotated one bit to the left through the Carry Flag. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is stored back in register 'f'. |                     |       |      |  |

| Words:           | 1                                                                                                                                                                                                     |                     |       |      |  |

| Cycles:          | 1                                                                                                                                                                                                     |                     |       |      |  |

| <u>Example</u>   | RLF                                                                                                                                                                                                   | REG1,               | 0     |      |  |

|                  | C<br>After Ins                                                                                                                                                                                        | <b>61</b> =1110 = 0 | 0110  |      |  |

#### RETURN Return from Subroutine

| Syntax:          | [label] RETURN                                                                                                                                 |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Operands:        | None                                                                                                                                           |  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC$                                                                                                                           |  |  |  |  |  |

| Status Affected: | None                                                                                                                                           |  |  |  |  |  |

| Encoding:        | 00 0000 0000 1000                                                                                                                              |  |  |  |  |  |

| Description:     | Return from subroutine. The stack is POPed and the top of the stack (TOS) is loaded into the program counter. This is a two-cycle instruction. |  |  |  |  |  |

| Words:           | 1                                                                                                                                              |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                              |  |  |  |  |  |

RETURN

After Interrupt PC = TOS

**Example**

| RRF                         | Rotate Right f through Carry                                                                                                                                                                                                                           | SUBLW                                   | Subtract W from Literal                                                                                                                    |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                     | [ label ] RRF f,d                                                                                                                                                                                                                                      | Syntax:                                 | [ label ] SUBLW k                                                                                                                          |

| Operands:                   | $0 \leq f \leq 127$                                                                                                                                                                                                                                    | Operands:                               | $0 \leq k \leq 255$                                                                                                                        |

|                             | $d \in [0,1]$                                                                                                                                                                                                                                          | Operation:                              | $k - (W) \rightarrow (W)$                                                                                                                  |

| Operation: Status Affected: | See description below C                                                                                                                                                                                                                                | Status<br>Affected:                     | C, DC, Z                                                                                                                                   |

| Encoding:                   | 00 1100 dfff ffff                                                                                                                                                                                                                                      | Encoding:                               | 11 110x kkkk kkkk                                                                                                                          |

| Description:                | The contents of register 'f' are rotated one bit to the right through the Carry Flag. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.                                                 | Description:  Words: Cycles: Example 1: | The W register is subtracted (2's complement method) from the eightbit literal 'k'. The result is placed in the W register.  1  SUBLW 0x02 |

| Words:                      | 1                                                                                                                                                                                                                                                      |                                         | Before Instruction                                                                                                                         |

| Cycles:                     | 1                                                                                                                                                                                                                                                      |                                         | W = 1                                                                                                                                      |

| Example                     | RRF REG1, 0                                                                                                                                                                                                                                            |                                         | C = ?                                                                                                                                      |

|                             | Before Instruction  REG1 = 1110 0110  C = 0  After Instruction                                                                                                                                                                                         |                                         | After Instruction  W = 1  C = 1; result is positive                                                                                        |

|                             | REG1 = 1110 0110<br>W = 0111 0011<br>C = 0                                                                                                                                                                                                             | Example 2:                              | Before Instruction  W = 2 C = ?  After Instruction                                                                                         |

| SLEEP                       |                                                                                                                                                                                                                                                        |                                         | W = 0<br>C = 1; result is zero                                                                                                             |

| Syntax:                     | [ label ] SLEEP                                                                                                                                                                                                                                        | Example 3:                              | Before Instruction                                                                                                                         |

| Operands:                   | None                                                                                                                                                                                                                                                   |                                         | W = 3                                                                                                                                      |

| Operation:                  | $00h \rightarrow WDT$ ,                                                                                                                                                                                                                                |                                         | C = ?                                                                                                                                      |

|                             | 0 → <u>WD</u> T prescaler,<br>1 → <del>TO</del> ,                                                                                                                                                                                                      |                                         | After Instruction                                                                                                                          |

|                             | $0 \to \frac{10}{PD}$                                                                                                                                                                                                                                  |                                         | W = 0xFF<br>C = 0; result is negative                                                                                                      |

| Status Affected:            | TO, PD                                                                                                                                                                                                                                                 |                                         | c, recall to riogative                                                                                                                     |

| Encoding:                   | 00 0000 0110 0011                                                                                                                                                                                                                                      |                                         |                                                                                                                                            |

| Description:                | The power-down Status bit, PD is cleared. Time out Status bit, TO is set. Watchdog Timer and its prescaler are cleared. The processor is put into Sleep mode with the oscillator stopped. See Section 14.8 "Power-Down Mode (Sleep)" for more details. |                                         |                                                                                                                                            |

| Words:                      | 1                                                                                                                                                                                                                                                      |                                         |                                                                                                                                            |

| Cycles:                     | 1                                                                                                                                                                                                                                                      |                                         |                                                                                                                                            |

| Example:                    | SLEEP                                                                                                                                                                                                                                                  |                                         |                                                                                                                                            |

TABLE 17-1: DC Characteristics: PIC16F627A/628A/648A (Industrial, Extended) PIC16LF627A/628A/648A (Industrial)

| DC CHARACTERISTICS    |                  | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial and $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended<br>Operating voltage VDD range as described in DC specification Table 17-2 and Table 17-3 |                               |                   |              |                 |                                                                    |

|-----------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------|--------------|-----------------|--------------------------------------------------------------------|

| Parameter No.         | Sym              | Characteristic                                                                                                                                                                                                                                                                                                                      | Min Typ† Max Units Conditions |                   |              |                 |                                                                    |

|                       |                  | Data EEPROM Memory                                                                                                                                                                                                                                                                                                                  |                               |                   |              |                 |                                                                    |

| D120<br>D120A<br>D121 | ED<br>ED<br>VDRW | Endurance Endurance VDD for read/write                                                                                                                                                                                                                                                                                              | 100K<br>10K<br>VMIN           | 1M<br>100K        | —<br>5.5     | E/W<br>E/W<br>V | -40°C ≤ TA ≤ 85°C<br>85°C ≤ TA ≤ 125°C<br>VMIN = Minimum operating |

| D122                  | TDEW             |                                                                                                                                                                                                                                                                                                                                     | VIVIIIV                       | 4                 | 8*           |                 | voltage                                                            |

| D123                  | TRETD            | Erase/Write cycle time<br>Characteristic Retention                                                                                                                                                                                                                                                                                  | 40                            | <del>4</del><br>— | <del>-</del> | ms<br>Year      | Provided no other specifications are violated                      |

| D124                  | TREF             | Number of Total Erase/Write Cycles before Refresh <sup>(1)</sup>                                                                                                                                                                                                                                                                    | 1M                            | 10M               | -            | E/W             | -40°C to +85°C                                                     |

|                       |                  | Program Flash Memory                                                                                                                                                                                                                                                                                                                |                               |                   |              |                 |                                                                    |

| D130                  | EР               | Endurance                                                                                                                                                                                                                                                                                                                           | 10K                           | 100K              |              | E/W             | $-40^{\circ}C \leq TA \leq 85^{\circ}C$                            |

| D130A                 | EP               | Endurance                                                                                                                                                                                                                                                                                                                           | 1000                          | 10K               |              | E/W             | 85°C ≤ TA ≤ 125°C                                                  |

| D131                  | VPR              | VDD for read                                                                                                                                                                                                                                                                                                                        | VMIN                          | _                 | 5.5          | V               | VMIN = Minimum operating voltage                                   |

| D132                  | VIE              | VDD for Block erase                                                                                                                                                                                                                                                                                                                 | 4.5                           | _                 | 5.5          | V               |                                                                    |

| D132A                 | VPEW             | VDD for write                                                                                                                                                                                                                                                                                                                       | VMIN                          | _                 | 5.5          | V               | Vміn = Minimum operating voltage                                   |

| D133                  | TIE              | Block Erase cycle time                                                                                                                                                                                                                                                                                                              | _                             | 4                 | 8*           | ms              | VDD > 4.5V                                                         |

| D133A                 | TPEW             | Write cycle time                                                                                                                                                                                                                                                                                                                    |                               | 2                 | 4*           | ms              | Book that are affect                                               |

| D134                  | TRETP            | Characteristic Retention                                                                                                                                                                                                                                                                                                            | 40                            |                   | _            | year            | Provided no other specifications are violated                      |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: Refer to Section 13.7 "Using the Data EEPROM" for a more detailed discussion on data EEPROM endurance.

<sup>†</sup> Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

NOTES:

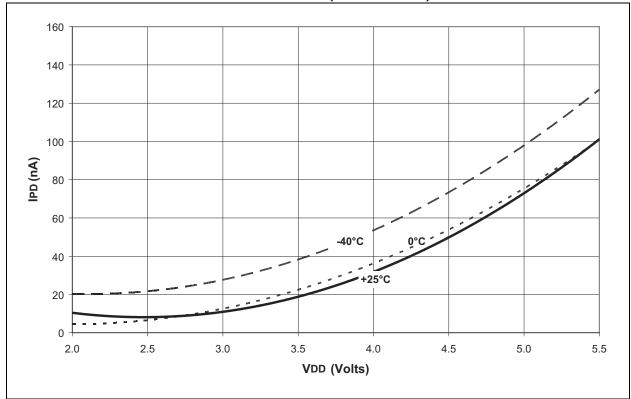

#### 18.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for design guidance and are not tested.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

The data presented in this section is a **statistical summary** of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at  $25^{\circ}$ C. 'Max' or 'Min' represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation, over the whole temperature range.

#### 19.0 PACKAGING INFORMATION

#### 19.1 Package Marking Information

18-Lead PDIP

18-Lead SOIC (.300")

20-Lead SSOP

28-Lead QFN

Example

Example

Example

Example

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

Pb-free JEDEC designator for Matte Tin (Sn)

\* This package is Pb-free. The Pb-free JEDEC designator (e3)

can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

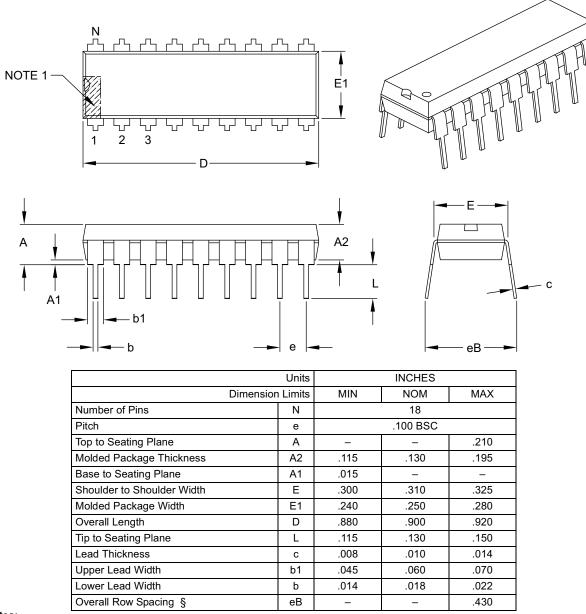

#### 18-Lead Plastic Dual In-Line (P) - 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-007B

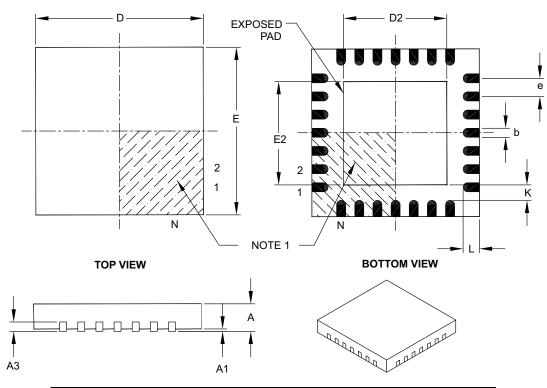

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units    |          | MILLIMETERS |      |

|------------------------|----------|----------|-------------|------|

| Dimensio               | n Limits | MIN      | NOM         | MAX  |

| Number of Pins         | N        | 28       |             |      |

| Pitch                  | е        | 0.65 BSC |             |      |

| Overall Height         | Α        | 0.80     | 0.90        | 1.00 |

| Standoff               | A1       | 0.00     | 0.02        | 0.05 |

| Contact Thickness      | A3       |          | 0.20 REF    |      |

| Overall Width          | Е        |          | 6.00 BSC    |      |

| Exposed Pad Width      | E2       | 3.65     | 3.70        | 4.20 |

| Overall Length         | D        | 6.00 BSC |             |      |

| Exposed Pad Length     | D2       | 3.65     | 3.70        | 4.20 |

| Contact Width          | b        | 0.23     | 0.30        | 0.35 |

| Contact Length         | L        | 0.50     | 0.55        | 0.70 |

| Contact-to-Exposed Pad | K        | 0.20     | _           | 1    |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

| Q                                                               |         | External Clock Input                                                |          |

|-----------------------------------------------------------------|---------|---------------------------------------------------------------------|----------|

| Q-Clock                                                         | 61      | External Clock Input Timing                                         |          |

| Quick-Turnaround-Production (QTP) Devices                       |         | Oscillator                                                          |          |

|                                                                 |         | Prescaler                                                           |          |

| R                                                               |         | Resetting Timer1                                                    |          |

| RC Oscillator                                                   | 101     | Resetting Timer1 Registers                                          |          |

| RC Oscillator Mode                                              |         | Special Event Trigger (CCP)                                         |          |

| Block Diagram                                                   | 101     | Synchronized Counter Mode                                           |          |

| Reader Response                                                 |         | Timer Mode                                                          |          |

| Registers                                                       |         | TMR1H                                                               |          |

| CCP1CON (CCP Operation)                                         | 57      | TMR1L                                                               | 52       |

| CMCON (Comparator Configuration)                                | 63      | Timer2                                                              | _        |

| CONFIG (Configuration Word)                                     | 98      | Block Diagram                                                       |          |

| EECON1 (EEPROM Control Register 1)                              | 92      | Postscaler                                                          |          |

| INTCON (Interrupt Control)                                      | 26      | PR2 register                                                        |          |

| Maps                                                            |         | Prescaler                                                           | -        |

| PIC16F627A                                                      | 18, 19  | Timer2 Module                                                       |          |

| PIC16F628A                                                      | 18, 19  | TMR2 output                                                         |          |

| OPTION_REG (Option)                                             | 25      | TMR2 to PR2 Match Interrupt                                         | 60       |

| PCON (Power Control)                                            |         | Timing Diagrams                                                     | 4.4-     |

| PIE1 (Peripheral Interrupt Enable 1)                            |         | Timer0                                                              |          |

| PIR1 (Peripheral Interrupt Register 1)                          |         | Timer1                                                              | 147      |

| Status                                                          |         | USART                                                               | 01       |

| T1CON Timer1 Control)                                           | 50      | Asynchronous Receiver                                               |          |

| T2CON Timer2 Control)                                           |         | USART Asynchronous Master Transmission USART Asynchronous Reception |          |

| Reset                                                           |         |                                                                     |          |

| RETFIE Instruction                                              |         | USART Synchronous Reception                                         |          |

| RETLW Instruction                                               |         | USART Synchronous Transmission Timing Diagrams and Specifications   |          |

| RETURN Instruction                                              |         | TMR0 Interrupt                                                      |          |

| Revision History                                                |         | TMR1CS bit                                                          |          |

| RLF Instruction                                                 |         | TMR10N bit                                                          |          |

| RRF Instruction                                                 | 128     | TMR2ON bit                                                          |          |

| S                                                               |         | TOUTPS0 bit                                                         |          |

|                                                                 | · HCADT | TOUTPS1 bit                                                         |          |

| Serial Communication Interface (SCI) Module, Se                 |         | TOUTPS2 bit                                                         |          |

| Serialized Quick-Turnaround-Production (SQTP) SLEEP Instruction |         | TOUTPS3 bit                                                         |          |

| Software Simulator (MPLAB SIM)                                  |         | TRIS Instruction                                                    |          |

| Special Event Trigger. See Compare                              | 133     | TRISA                                                               |          |

| Special Features of the CPU                                     | 97      | TRISB                                                               |          |

| Special Function Registers                                      |         |                                                                     |          |

| Status Register                                                 |         | U                                                                   |          |

| SUBLW Instruction                                               |         | Universal Synchronous Asynchronous Receiver Tra                     | ansmitte |