Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 224 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f627at-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 GENERAL DESCRIPTION

The PIC16F627A/628A/648A are 18-pin Flash-based members of the versatile PIC16F627A/628A/648A family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers.

All PIC<sup>®</sup> microcontrollers employ an advanced RISC architecture. The PIC16F627A/628A/648A have enhanced core features, an eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single-cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available, complemented by a large register set.

PIC16F627A/628A/648A microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

PIC16F627A/628A/648A devices have integrated features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption.

The PIC16F627A/628A/648A has 8 oscillator configurations. The single-pin RC oscillator provides a low-cost solution. The LP oscillator minimizes power consumption, XT is a standard crystal, and INTOSC is a self-contained precision two-speed internal oscillator.

The HS mode is for High-Speed crystals. The EC mode is for an external clock source.

The Sleep (Power-down) mode offers power savings. Users can wake-up the chip from Sleep through several external interrupts, internal interrupts and Resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock-up.

Table 1-1 shows the features of the PIC16F627A/628A/ 648A mid-range microcontroller family.

A simplified block diagram of the PIC16F627A/628A/ 648A is shown in Figure 3-1.

The PIC16F627A/628A/648A series fits in applications ranging from battery chargers to low power remote sensors. The Flash technology makes customizing application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages makes this microcontroller series ideal for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16F627A/628A/648A very versatile.

# 1.1 Development Support

The PIC16F627A/628A/648A family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low cost in-circuit debugger, a low cost development programmer and a full-featured programmer. A Third Party "C" compiler support tool is also available.

|             |                                      | PIC16F627A                                         | PIC16F628A                                         | PIC16F648A                                         | PIC16LF627A                                        | PIC16LF628A                                        | PIC16LF648A                                        |

|-------------|--------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|

| Clock       | Maximum Frequency of Operation (MHz) | 20                                                 | 20                                                 | 20                                                 | 20                                                 | 20                                                 | 20                                                 |

|             | Flash Program<br>Memory (words)      | 1024                                               | 2048                                               | 4096                                               | 1024                                               | 2048                                               | 4096                                               |

| Memory      | RAM Data Memory<br>(bytes)           | 224                                                | 224                                                | 256                                                | 224                                                | 224                                                | 256                                                |

|             | EEPROM Data<br>Memory (bytes)        | 128                                                | 128                                                | 256                                                | 128                                                | 128                                                | 256                                                |

|             | Timer module(s)                      | TMR0, TMR1,<br>TMR2                                |

|             | Comparator(s)                        | 2                                                  | 2                                                  | 2                                                  | 2                                                  | 2                                                  | 2                                                  |

| Peripherals | Capture/Compare/<br>PWM modules      | 1                                                  | 1                                                  | 1                                                  | 1                                                  | 1                                                  | 1                                                  |

|             | Serial Communications                | USART                                              | USART                                              | USART                                              | USART                                              | USART                                              | USART                                              |

|             | Internal Voltage<br>Reference        | Yes                                                | Yes                                                | Yes                                                | Yes                                                | Yes                                                | Yes                                                |

|             | Interrupt Sources                    | 10                                                 | 10                                                 | 10                                                 | 10                                                 | 10                                                 | 10                                                 |

|             | I/O Pins                             | 16                                                 | 16                                                 | 16                                                 | 16                                                 | 16                                                 | 16                                                 |

| Features    | Voltage Range (Volts)                | 3.0-5.5                                            | 3.0-5.5                                            | 3.0-5.5                                            | 2.0-5.5                                            | 2.0-5.5                                            | 2.0-5.5                                            |

|             | Brown-out Reset                      | Yes                                                | Yes                                                | Yes                                                | Yes                                                | Yes                                                | Yes                                                |

|             | Packages                             | 18-pin DIP,<br>SOIC, 20-pin<br>SSOP,<br>28-pin QFN |

TABLE 1-1: PIC16F627A/628A/648A FAMILY OF DEVICES

All PIC<sup>®</sup> family devices have Power-on Reset, selectable Watchdog Timer, selectable code-protect and high I/O current capability. All PIC16F627A/628A/648A family devices use serial programming with clock pin RB6 and data pin RB7.

# 4.0 MEMORY ORGANIZATION

# 4.1 Program Memory Organization

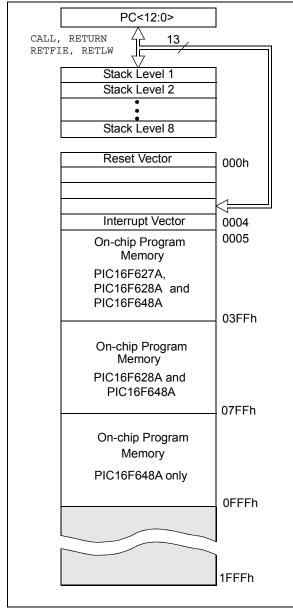

The PIC16F627A/628A/648A has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 1K x 14 (0000h-03FFh) for the PIC16F627A, 2K x 14 (0000h-07FFh) for the PIC16F628A and 4K x 14 (0000h-0FFFh) for the PIC16F648A are physically implemented. Accessing a location above these boundaries will cause a wraparound within the first 1K x 14 space (PIC16F627A), 2K x 14 space (PIC16F628A) or 4K x 14 space (PIC16F648A). The Reset vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1).

# 4.2 Data Memory Organization

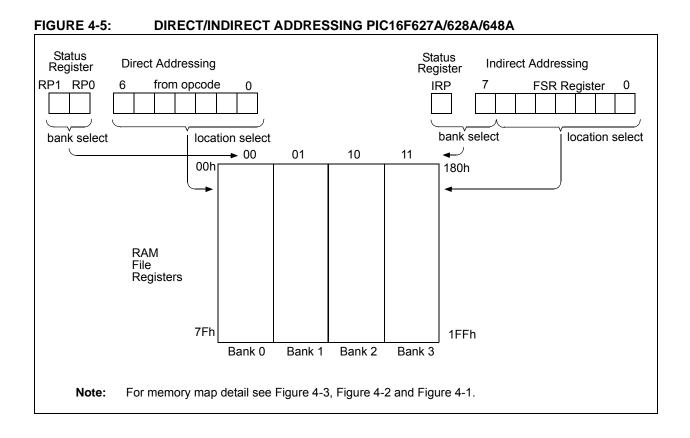

The data memory (Figure 4-2 and Figure 4-3) is partitioned into four banks, which contain the General Purpose Registers (GPRs) and the Special Function Registers (SFRs). The SFRs are located in the first 32 locations of each bank. There are General Purpose Registers implemented as static RAM in each bank. Table 4-1 lists the General Purpose Register available in each of the four banks.

| TABLE 4-1: | GENERAL PURPOSE STATIC |

|------------|------------------------|

|            | RAM REGISTERS          |

|       | PIC16F627A/628A      | PIC16F648A |

|-------|----------------------|------------|

| Bank0 | 20-7Fh               | 20-7Fh     |

| Bank1 | A0h-FF               | A0h-FF     |

| Bank2 | 120h-14Fh, 170h-17Fh | 120h-17Fh  |

| Bank3 | 1F0h-1FFh            | 1F0h-1FFh  |

Addresses F0h-FFh, 170h-17Fh and 1F0h-1FFh are implemented as common RAM and mapped back to addresses 70h-7Fh.

Table 4-2 lists how to access the four banks of registers via the Status register bits RP1 and RP0.

# TABLE 4-2: ACCESS TO BANKS OF REGISTERS

| Bank | RP1 | RP0 |

|------|-----|-----|

| 0    | 0   | 0   |

| 1    | 0   | 1   |

| 2    | 1   | 0   |

| 3    | 1   | 1   |

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $224 \times 8$  in the PIC16F627A/628A and  $256 \times 8$  in the PIC16F648A. Each is accessed either directly or indirectly through the File Select Register (FSR), See **Section 4.4** "Indirect Addressing, INDF and FSR Registers".

#### FIGURE 4-3: DATA MEMORY MAP OF THE PIC16F648A

| ndirect addr. <sup>(1)</sup> | 00h | Indirect addr. <sup>(1)</sup> | 80h  | Indirect addr. <sup>(1)</sup> | 100h   | Indirect addr. <sup>(1)</sup> |

|------------------------------|-----|-------------------------------|------|-------------------------------|--------|-------------------------------|

| TMR0                         | 01h | OPTION                        | 81h  | TMR0                          | 101h   | OPTION                        |

| PCL                          | 02h | PCL                           | 82h  | PCL                           | 102h   | PCL                           |

| STATUS                       | 03h | STATUS                        | 83h  | STATUS                        | 103h   | STATUS                        |

| FSR                          | 04h | FSR                           | 84h  | FSR                           | 104h   | FSR                           |

| PORTA                        | 05h | TRISA                         | 85h  | -                             | 105h   |                               |

| PORTB                        | 06h | TRISB                         | 86h  | PORTB                         | 106h   | TRISB                         |

|                              | 07h |                               | 87h  |                               | 107h   |                               |

|                              | 08h |                               | 88h  |                               | 108h   |                               |

|                              | 09h |                               | 89h  |                               | 109h   |                               |

| PCLATH                       | 0Ah | PCLATH                        | 8Ah  | PCLATH                        | 10Ah   | PCLATH                        |

| INTCON                       | 0Bh | INTCON                        | 8Bh  | INTCON                        | 10Bh   | INTCON                        |

| PIR1                         | 0Ch | PIE1                          | 8Ch  |                               | 10Ch   |                               |

|                              | 0Dh |                               | 8Dh  |                               | 10Dh   |                               |

| TMR1L                        | 0Eh | PCON                          | 8Eh  |                               | 10Eh   |                               |

| TMR1H                        | 0Fh |                               | 8Fh  |                               | 10Fh   |                               |

| T1CON                        | 10h |                               | 90h  |                               | 1      |                               |

| TMR2                         | 11h |                               | 91h  |                               |        |                               |

| T2CON                        | 12h | PR2                           | 92h  |                               |        |                               |

|                              | 13h |                               | 93h  |                               |        |                               |

|                              | 14h |                               | 94h  |                               |        |                               |

| CCPR1L                       | 15h |                               | 95h  |                               |        |                               |

| CCPR1H                       | 16h |                               | 96h  |                               |        |                               |

| CCP1CON                      | 17h |                               | 97h  |                               |        |                               |

| RCSTA                        | 18h | TXSTA                         | 98h  |                               |        |                               |

| TXREG                        | 19h | SPBRG                         | 99h  |                               |        |                               |

| RCREG                        | 1Ah | EEDATA                        | 9Ah  |                               |        |                               |

|                              | 1Bh | EEADR                         | 9Bh  |                               |        |                               |

|                              | 1Ch | EECON1                        | 9Ch  |                               |        |                               |

|                              | 1Dh | EECON2 <sup>(1)</sup>         | 9Dh  |                               |        |                               |

|                              | 1Eh |                               | 9Eh  |                               |        |                               |

| CMCON                        | 1Fh | VRCON                         | 9Fh  |                               | 11Fh   |                               |

|                              | 20h |                               | A0h  |                               | 120h   |                               |

| General                      |     | General                       | 7011 | General                       |        |                               |

| Purpose                      |     | Purpose                       |      | Purpose                       |        |                               |

| Register                     |     | Register<br>80 Bytes          |      | Register<br>80 Bytes          |        |                               |

| 80 Bytes                     |     | ou bytes                      |      | 00 09100                      |        |                               |

|                              | 6Fh |                               | EFh  |                               | 16Fh   |                               |

|                              | 70h |                               | F0h  |                               | 170h   |                               |

| 16 Bytes                     |     | accesses                      |      | accesses<br>70h-7Fh           |        | accesses<br>70h-7Fh           |

|                              | 755 | 70h-7Fh                       | 55h  |                               | 17Fh   | 7011-771                      |

| Bank 0                       | 7Fh | Bank 1                        | FFh  | Bank 2                        | • 17FH | Bank 3                        |

|                              |     |                               |      |                               |        |                               |

© 2009 Microchip Technology Inc.

#### 4.2.2.1 Status Register

The Status register, shown in Register 4-1, contains the arithmetic status of the ALU; the Reset status and the bank select bits for data memory (SRAM).

The Status register can be the destination for any instruction, like any other register. If the Status register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are non-writable. Therefore, the result of an instruction with the Status register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the Status register as "000uu1uu" (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the Status register because these instructions do not affect any Status bit. For other instructions, not affecting any Status bits, see the "Instruction Set Summary".

| Note: | The C and DC bits operate as a Borrow      |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | and Digit Borrow out bit, respectively, in |  |  |  |  |  |  |  |  |

|       | subtraction. See the SUBLW and SUBWF       |  |  |  |  |  |  |  |  |

|       | instructions for examples.                 |  |  |  |  |  |  |  |  |

#### REGISTER 4-1: STATUS – STATUS REGISTER (ADDRESS: 03h, 83h, 103h, 183h)

|         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0                                                                                                                                                                   | R/W-0   | R-1          | R-1            | R/W-x     | R/W-x          | R/W-x  |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------|----------------|-----------|----------------|--------|--|--|--|

|         | IRP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RP1                                                                                                                                                                     | RP0     | TO           | PD             | Z         | DC             | С      |  |  |  |

|         | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                         |         |              |                |           |                | bit 0  |  |  |  |

| bit 7   | <b>IRP</b> : Register Bank Select bit (used for indirect addressing)<br>1 = Bank 2, 3 (100h-1FFh)<br>0 = Bank 0, 1 (00h-FFh)                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                         |         |              |                |           |                |        |  |  |  |

| bit 6-5 | <b>RP&lt;1:0&gt;</b> : 1<br>00 = Bank<br>01 = Bank<br>10 = Bank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RP<1:0>: Register Bank Select bits (used for direct addressing)<br>00 = Bank 0 (00h-7Fh)<br>01 = Bank 1 (80h-FFh)<br>10 = Bank 2 (100h-17Fh)<br>11 = Bank 3 (180h-1FFh) |         |              |                |           |                |        |  |  |  |

| bit 4   | 1 = After p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TO: Time Out bit<br>1 = After power-up, CLRWDT instruction or SLEEP instruction<br>0 = A WDT time out occurred                                                          |         |              |                |           |                |        |  |  |  |

| bit 3   | 1 = After p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>PD</b> : Power-down bit 1 = After power-up or by the CLRWDT instruction 0 = By execution of the SLEEP instruction                                                    |         |              |                |           |                |        |  |  |  |

| bit 2   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                                                                                                                                                                       |         |              |                |           |                |        |  |  |  |

| bit 1   | <b>DC</b> : Digit Carry/Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for Borrow the polarity is reversed)<br>1 = A carry-out from the 4th low order bit of the result occurred                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                         |         |              |                |           |                |        |  |  |  |

| bit 0   | <ul> <li>0 = No carry-out from the 4th low order bit of the result</li> <li>C: Carry/Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)</li> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> <li>Note: For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.</li> </ul> |                                                                                                                                                                         |         |              |                |           |                |        |  |  |  |

|         | Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                         |         |              |                |           |                |        |  |  |  |

|         | R = Reada                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                         | VV = V  | Vritable bit | U = Unimple    | emented b | oit, read as ' | יכ     |  |  |  |

|         | -n = Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | at POR                                                                                                                                                                  | '1' = E | Bit is set   | '0' = Bit is c | leared    | x = Bit is ur  | nknown |  |  |  |

# 4.3 PCL and PCLATH

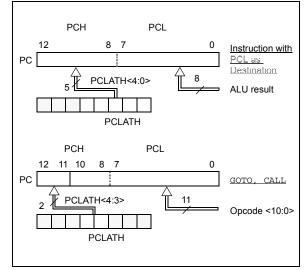

The Program Counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 4-4 shows the two situations for loading the PC. The upper example in Figure 4-4 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 4-4 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 4-4: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the Application Note AN556 "*Implementing a Table Read*" (DS00556).

# 4.3.2 STACK

The PIC16F627A/628A/648A family has an 8-level deep x 13-bit wide hardware stack (Figure 4-1). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth PUSH overwrites the value that was stored from the first PUSH. The tenth PUSH overwrites the second PUSH (and so on).

| Note 1: | There are no Status bits to indicate stack |

|---------|--------------------------------------------|

|         | overflow or stack underflow conditions.    |

2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

# 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-5.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 4-1.

|      | MOVLW | 0x20  | ;initialize pointer  |

|------|-------|-------|----------------------|

|      | MOVWF | FSR   | ;to RAM              |

| NEXT | CLRF  | INDF  | clear INDF register; |

|      | INCF  | FSR   | ;inc pointer         |

|      | BTFSS | FSR,4 | ;all done?           |

|      | GOTO  | NEXT  | ;no clear next       |

|      |       |       | ;yes continue        |

|      |       |       |                      |

NOTES:

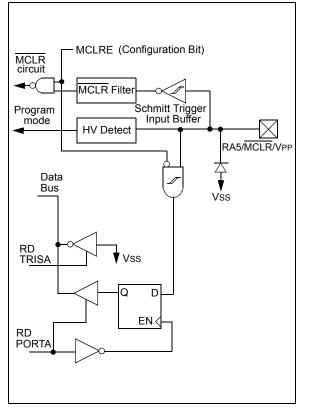

#### FIGURE 5-5: BLO<u>CK DIA</u>GRAM OF THE RA5/MCLR/VPP PIN

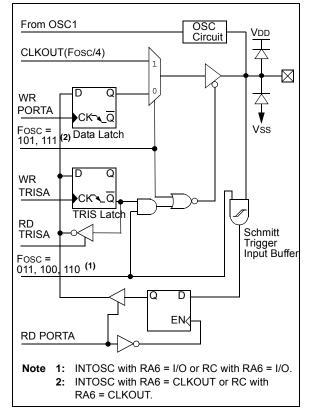

#### BLOCK DIAGRAM OF RA6/OSC2/CLKOUT PIN

### 9.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available: the CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

*PWM duty cycle* =

(CCPR1L:CCP1CON<5:4>) · Tosc · TMR2 prescale value

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2 concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

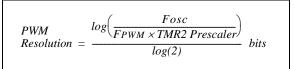

Maximum PWM resolution (bits) for a given PWM frequency:

Note: If the PWM duty cycle value is longer than the PWM period the CCP1 pin will not be cleared.

For an example PWM period and duty cycle calculation, see the *PIC<sup>®</sup> Mid-Range Reference Manual* (DS33023).

#### 9.3.3 SET-UP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- Make the CCP1 pin an output by clearing the TRISB<3> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

# TABLE 9-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 6.5       |

#### TABLE 9-4: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address                 | Name    | Bit 7                                | Bit 6                           | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0     | Value on<br>POR | Value on<br>all other<br>Resets |

|-------------------------|---------|--------------------------------------|---------------------------------|---------|---------|---------|--------|---------|-----------|-----------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON  | GIE                                  | PEIE                            | TOIE    | INTE    | RBIE    | T0IF   | INTF    | RBIF      | 0000 000x       | 0000 000u                       |

| 0Ch                     | PIR1    | EEIF                                 | CMIF                            | RCIF    | TXIF    | _       | CCP1IF | TMR2IF  | TMR1IF    | 0000 -000       | 0000 -000                       |

| 8Ch                     | PIE1    | EEIE                                 | CMIE                            | RCIE    | TXIE    | _       | CCP1IE | TMR2IE  | TMR1IE    | 0000 -000       | 0000 -000                       |

| 86h, 186h               | TRISB   | TRISB7                               | TRISB6                          | TRISB5  | TRISB4  | TRISB3  | TRISB2 | TRISB1  | TRISB0    | 1111 1111       | 1111 1111                       |

| 11h                     | TMR2    | Timer2 M                             | Timer2 Module's Register        |         |         |         |        |         |           | 0000 0000       | 0000 0000                       |

| 92h                     | PR2     | Timer2 M                             | Timer2 Module's Period Register |         |         |         |        |         |           | 1111 1111       | 1111 1111                       |

| 12h                     | T2CON   | _                                    | TOUTPS3                         | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0   | -000 0000       | uuuu uuuu                       |

| 15h                     | CCPR1L  | Capture/Compare/PWM Register 1 (LSB) |                                 |         |         |         |        |         | xxxx xxxx | uuuu uuuu       |                                 |

| 16h                     | CCPR1H  | Capture/Compare/PWM Register 1 (MSB) |                                 |         |         |         |        |         |           | xxxx xxxx       | uuuu uuuu                       |

| 17h                     | CCP1CON | _                                    | —                               | CCP1X   | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0    | 00 0000         | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PWM and Timer2.

NOTES:

# **10.0 COMPARATOR MODULE**

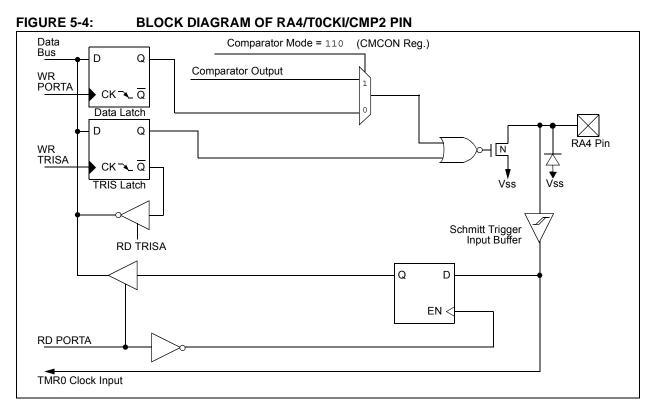

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the RA0 through RA3 pins. The on-chip Voltage Reference (Section 11.0 "Voltage Reference Module") can also be an input to the comparators.

The CMCON register, shown in Register 10-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 10-1.

|         | R-0                            | R-0                                                        | R/W-0       | R/W-0       | R/W-0         | R/W-0    | R/W-0 | ,<br>R/W-0 |

|---------|--------------------------------|------------------------------------------------------------|-------------|-------------|---------------|----------|-------|------------|

|         | C2OUT                          | C10UT                                                      | C2INV       | C1INV       | CIS           | CM2      | CM1   | CM0        |

|         | bit 7                          |                                                            |             | •           |               | •        |       | bit 0      |

|         |                                |                                                            |             |             |               |          |       |            |

| bit 7   |                                | omparator 2                                                | Output bit  |             |               |          |       |            |

|         | <u>When C2I</u>                |                                                            |             |             |               |          |       |            |

|         |                                | I+ > C2 VIN-<br>I+ < C2 VIN-                               |             |             |               |          |       |            |

|         |                                |                                                            |             |             |               |          |       |            |

|         | <u>When C2I</u><br>1 = C2 V(n) | <u>NV = 1:</u><br>I+ < C2 VIN-                             |             |             |               |          |       |            |

|         | -                              | 1+ < C2 VIN-<br>1+ > C2 VIN-                               |             |             |               |          |       |            |

| bit 6   | <b>C1OUT</b> : C               | omparator 1                                                | Output bit  |             |               |          |       |            |

|         | When C1I                       | -                                                          |             |             |               |          |       |            |

|         |                                | + > C1 VIN-                                                |             |             |               |          |       |            |

|         | 0 = C1 VIN                     | ı+ < C1 Vin-                                               |             |             |               |          |       |            |

|         | When C1I                       |                                                            |             |             |               |          |       |            |

|         | -                              | I+ < C1 VIN-<br>I+ > C1 VIN-                               |             |             |               |          |       |            |

| bit 5   |                                |                                                            |             | reion hit   |               |          |       |            |

| DIL 5   |                                | omparator 2 (<br>tput inverted                             |             |             |               |          |       |            |

|         |                                | tput not inve                                              |             |             |               |          |       |            |

| bit 4   | C1INV: Co                      | mparator 1 (                                               | Output Inve | rsion bit   |               |          |       |            |

|         |                                | tput inverted                                              |             |             |               |          |       |            |

|         |                                | tput not inve                                              |             |             |               |          |       |            |

| bit 3   |                                | parator Input                                              |             |             |               |          |       |            |

|         | Then:                          | < <u>2:0&gt;: = 001</u>                                    | -           |             |               |          |       |            |

|         | -                              | I- connects to                                             | o RA3       |             |               |          |       |            |

|         | 0 = C1 VIN                     | I- connects to                                             | o RA0       |             |               |          |       |            |

|         | When CM                        | < <u>2:0&gt; = 010</u>                                     |             |             |               |          |       |            |

|         | Then:                          |                                                            |             |             |               |          |       |            |

|         |                                | <ul> <li>I- connects to</li> <li>N- connects to</li> </ul> |             |             |               |          |       |            |

|         |                                | - connects to                                              |             |             |               |          |       |            |

|         | C2 Vit                         | N- connects t                                              | o RA1       |             |               |          |       |            |

| bit 2-0 |                                | Comparator                                                 |             |             |               |          |       |            |

|         | Figure 10-                     | 1 shows the                                                | comparato   | r modes and | CM<2:0> bit s | settings |       |            |

|         | Logond                         |                                                            |             |             |               |          |       |            |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented I  | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# **10.6 Comparator Interrupts**

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be reset by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

| Note: | If a change in the CMCON register          |

|-------|--------------------------------------------|

|       | (C1OUT or C2OUT) should occur when a       |

|       | read operation is being executed (start of |

|       | the Q2 cycle), then the CMIF (PIR1<6>)     |

|       | interrupt flag may not get set.            |

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any write or read of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition and allow flag bit CMIF to be cleared.

### 10.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from Sleep mode when enabled. While the comparator is powered-up, higher Sleep currents than shown in the power-down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators, CM<2:0> = 111, before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

# 10.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state. This forces the Comparator module to be in the comparator Reset mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at Reset time. The comparators will be powered-down during the Reset interval.

# 10.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 10-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

| TER 12-2: | RCSTA – RECEIVE STATUS AND CONTROL REGISTER (ADDRESS: 18h)                                                 |                                                |              |                |                  |              |                  |             |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------|----------------|------------------|--------------|------------------|-------------|--|--|--|

|           | R/W-0                                                                                                      | R/W-0                                          | R/W-0        | R/W-0          | R/W-0            | R-0          | R-0              | R-x         |  |  |  |

|           | SPEN                                                                                                       | RX9                                            | SREN         | CREN           | ADEN             | FERR         | OERR             | RX9D        |  |  |  |

|           | bit 7                                                                                                      |                                                |              |                |                  |              |                  | bit 0       |  |  |  |

| bit 7     | SPEN: Ser                                                                                                  | rial Port Ena                                  | ıble bit     |                |                  |              |                  |             |  |  |  |

|           | 1 = Serial                                                                                                 | s RB1/RX/D<br>port enablec<br>port disable     | ł            | TX/CK pins a   | as serial port p | ins when bit | s TRISB<2        | 1> are set) |  |  |  |

| bit 6     | <b>RX9</b> : 9-bit                                                                                         | Receive En                                     | able bit     |                |                  |              |                  |             |  |  |  |

|           |                                                                                                            | s 9-bit recep<br>s 8-bit recep                 |              |                |                  |              |                  |             |  |  |  |

| bit 5     | SREN: Sin                                                                                                  | gle Receive                                    | Enable bit   |                |                  |              |                  |             |  |  |  |

|           | -                                                                                                          | ous mode:                                      |              |                |                  |              |                  |             |  |  |  |

|           | Don't ca<br>Synchrono                                                                                      | ire<br>i <u>us mode - r</u>                    | nastor:      |                |                  |              |                  |             |  |  |  |

|           |                                                                                                            | bles single r                                  |              |                |                  |              |                  |             |  |  |  |

|           |                                                                                                            | bles single                                    |              |                |                  |              |                  |             |  |  |  |

|           |                                                                                                            | is cleared at<br>ous mode - s                  |              | n is complet   | e.               |              |                  |             |  |  |  |

|           |                                                                                                            | in this mode                                   |              |                |                  |              |                  |             |  |  |  |

| bit 4     | CREN: Continuous Receive Enable bit                                                                        |                                                |              |                |                  |              |                  |             |  |  |  |

|           | Asynchronous mode:                                                                                         |                                                |              |                |                  |              |                  |             |  |  |  |

|           | 1 = Enables continuous receive                                                                             |                                                |              |                |                  |              |                  |             |  |  |  |

|           | 0 = Disables continuous receive                                                                            |                                                |              |                |                  |              |                  |             |  |  |  |

|           | Synchronous mode:<br>1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN) |                                                |              |                |                  |              |                  |             |  |  |  |

|           |                                                                                                            | ables continu                                  |              |                |                  |              |                  | ,           |  |  |  |

| bit 3     | ADEN: Ad                                                                                                   | dress Detec                                    | t Enable bit |                |                  |              |                  |             |  |  |  |

|           | -                                                                                                          | ous mode 9                                     |              |                |                  |              | h (( )           |             |  |  |  |

|           | 1 = Enar<br>is se                                                                                          |                                                | detection, e | enable Interr  | upt and load of  | the receive  | e butter whe     | N KSK<8>    |  |  |  |

|           | 0 = Disables address detection, all bytes are received, and ninth bit can be used as parity bit            |                                                |              |                |                  |              |                  |             |  |  |  |

|           | Asynchronous mode 8-bit (RX9 = 0):                                                                         |                                                |              |                |                  |              |                  |             |  |  |  |

|           |                                                                                                            | Unused in this mode<br><u>Synchronous mode</u> |              |                |                  |              |                  |             |  |  |  |

|           | -                                                                                                          | in this mode                                   | e            |                |                  |              |                  |             |  |  |  |

| bit 2     | FERR: Fra                                                                                                  | ming Error I                                   | oit          |                |                  |              |                  |             |  |  |  |

|           | 1 = Framin<br>0 = No frar                                                                                  |                                                | n be update  | d by reading   | RCREG regis      | ster and rec | eive next va     | alid byte)  |  |  |  |

| bit 1     | OERR: Ov                                                                                                   | errun Error                                    | bit          |                |                  |              |                  |             |  |  |  |

|           | 1 = Overru<br>0 = No ove                                                                                   |                                                | n be cleared | l by clearing  | bit CREN)        |              |                  |             |  |  |  |

| bit 0     | <b>RX9D</b> : 9th                                                                                          | bit of receiv                                  | ed data (Ca  | an be parity l | oit)             |              |                  |             |  |  |  |

|           | Legend:                                                                                                    |                                                |              |                |                  |              |                  | ]           |  |  |  |

|           | R = Reada                                                                                                  | ble bit                                        | VV = V       | Vritable bit   | U = Unimp        | lemented b   | it, read as '    | 0'          |  |  |  |

|           |                                                                                                            |                                                |              |                |                  |              | <b>D</b> · · · · |             |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

## 12.3 USART Address Detect Function

#### 12.3.1 USART 9-BIT RECEIVER WITH ADDRESS DETECT

When the RX9 bit is set in the RCSTA register, 9 bits are received and the ninth bit is placed in the RX9D bit of the RCSTA register. The USART module has a special provision for multiprocessor communication. Multiprocessor communication is enabled by setting the ADEN bit (RCSTA<3>) along with the RX9 bit. The port is now programmed such that when the last bit is received, the contents of the Receive Shift Register (RSR) are transferred to the receive buffer, the ninth bit of the RSR (RSR<8>) is transferred to RX9D, and the receive interrupt is set if and only if RSR<8> = 1. This feature can be used in a multiprocessor system as follows:

A master processor intends to transmit a block of data to one of many slaves. It must first send out an address byte that identifies the target slave. An address byte is identified by setting the ninth bit (RSR<8>) to a '1' (instead of a '0' for a data byte). If the ADEN and RX9 bits are set in the slave's RCSTA register, enabling multiprocessor communication, all data bytes will be ignored. However, if the ninth received bit is equal to a '1', indicating that the received byte is an address, the slave will be interrupted and the contents of the RSR register will be transferred into the receive buffer. This allows the slave to be interrupted only by addresses, so that the slave can examine the received byte to see if it is being addressed. The addressed slave will then clear its ADEN bit and prepare to receive data bytes from the master.

When ADEN is enabled (= 1), all data bytes are ignored. Following the Stop bit, the data will not be loaded into the receive buffer, and no interrupt will occur. If another byte is shifted into the RSR register, the previous data byte will be lost. The ADEN bit will only take effect when the receiver is configured in 9-bit mode (RX9 = 1). When ADEN is disabled (= 0), all data bytes are received and the 9th bit can be used as the parity bit.

The receive block diagram is shown in Figure 12-4.

Reception is enabled by setting bit CREN (RCSTA<4>).

#### 12.3.1.1 Setting up 9-bit mode with Address Detect

Follow these steps when setting up Asynchronous Reception with Address Detect Enabled:

- 1. TRISB<1> and TRISB<2> should both be set to '1' to configure the RB1/RX/DT and RB2/TX/CK pins as inputs. Output drive, when required, is controlled by the peripheral circuitry.

- 2. Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH.

- 3. Enable asynchronous communication by setting or clearing bit SYNC and setting bit SPEN.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. Set bit RX9 to enable 9-bit reception.

- 6. Set ADEN to enable address detect.

- 7. Enable the reception by setting enable bit CREN or SREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 9. Read the 8-bit received data by reading the RCREG register to determine if the device is being addressed.

- 10. If an OERR error occurred, clear the error by clearing enable bit CREN if it was already set.

- 11. If the device has been addressed (RSR<8> = 1 with address match enabled), clear the ADEN and RCIF bits to allow data bytes and address bytes to be read into the receive buffer and interrupt the CPU.

| Address | Name                               | Bit 7 | Bit 6                       | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR | Value on<br>all other<br>Resets |

|---------|------------------------------------|-------|-----------------------------|-------|-------|-------|--------|--------|-----------|-----------------|---------------------------------|

| 0Ch     | PIR1                               | EEIF  | CMIF                        | RCIF  | TXIF  | _     | CCP1IF | TMR2IF | TMR1IF    | 0000 -000       | 0000 -000                       |

| 18h     | RCSTA                              | SPEN  | RX9                         | SREN  | CREN  | ADEN  | FERR   | OERR   | RX9D      | 0000 000x       | 0000 000x                       |

| 1Ah     | RCREG                              | USART | USART Receive Data Register |       |       |       |        |        |           | 0000 0000       | 0000 0000                       |

| 8Ch     | PIE1                               | EEIE  | CMIE                        | RCIE  | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE    | 0000 -000       | 0000 -000                       |

| 98h     | TXSTA                              | CSRC  | TX9                         | TXEN  | SYNC  | _     | BRGH   | TRMT   | TX9D      | 0000 -010       | 0000 -010                       |

| 99h     | SPBRG Baud Rate Generator Register |       |                             |       |       |       |        |        | 0000 0000 | 0000 0000       |                                 |

#### TABLE 12-8: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

**Legend:** x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

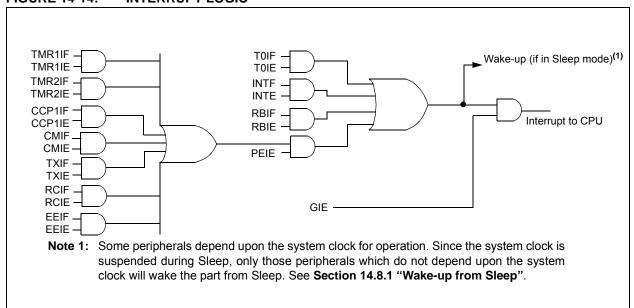

### 14.5 Interrupts

The PIC16F627A/628A/648A has 10 sources of interrupt:

- External Interrupt RB0/INT

- TMR0 Overflow Interrupt

- PORTB Change Interrupts (pins RB<7:4>)

- Comparator Interrupt

- USART Interrupt TX

- USART Interrupt RX

- CCP Interrupt

- TMR1 Overflow Interrupt

- TMR2 Match Interrupt

- Data EEPROM Interrupt

The Interrupt Control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A Global Interrupt Enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on Reset.

The "return-from-interrupt" instruction, RETFIE, exits interrupt routine as well as sets the GIE bit, which reenables RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag is contained in the special register PIR1. The corresponding interrupt enable bit is contained in special registers PIE1.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/ INT recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 14-15). The latency is the same for one or two-cycle instructions. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

#### FIGURE 14-14: INTERRUPT LOGIC

NOTES:

### 17.1 DC Characteristics: PIC16F627A/628A/648A (Industrial, Extended) PIC16LF627A/628A/648A (Industrial)

| (Industrial)          |      |                                               | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le Ta \le +85^{\circ}C$ for industrial                                                          |      |      |       |                                                                                                                                                                            |  |  |

|-----------------------|------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                       |      |                                               | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le Ta \le +85^{\circ}C$ for industrial and $-40^{\circ}C \le Ta \le +125^{\circ}C$ for extended |      |      |       |                                                                                                                                                                            |  |  |

| Param<br>No.          | Sym  | Characteristic/Device                         | Min                                                                                                                                                                                         | Тур† | Мах  | Units | Conditions                                                                                                                                                                 |  |  |

|                       | Vdd  | Supply Voltage                                |                                                                                                                                                                                             |      |      |       |                                                                                                                                                                            |  |  |

| D001 PIC16LF627A/628A |      | PIC16LF627A/628A/648A                         | 2.0                                                                                                                                                                                         |      | 5.5  | V     |                                                                                                                                                                            |  |  |

|                       |      | PIC16F627A/628A/648A                          | 3.0                                                                                                                                                                                         | _    | 5.5  | V     |                                                                                                                                                                            |  |  |

| D002                  | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>  | —                                                                                                                                                                                           | 1.5* | _    | V     | Device in Sleep mode                                                                                                                                                       |  |  |

| D003                  | VPOR | VDD Start Voltage<br>to ensure Power-on Reset | _                                                                                                                                                                                           | Vss  | _    | V     | See Section 14.4 "Power-<br>on Reset (POR), Power-up<br>Timer (PWRT), Oscillator<br>Start-up Timer (OST) and<br>Brown-out Reset<br>(BOR)"on Power-on Reset<br>for details  |  |  |

| D004                  | SVDD | VDD Rise Rate<br>to ensure Power-on Reset     | 0.05*                                                                                                                                                                                       | _    | _    | V/ms  | See Section 14.4 "Power-<br>on Reset (POR), Power-up<br>Timer (PWRT), Oscillator<br>Start-up Timer (OST) and<br>Brown-out Reset (BOR)"<br>on Power-on Reset for<br>details |  |  |

| D005                  | VBOR | Brown-out Reset Voltage                       | 3.65                                                                                                                                                                                        | 4.0  | 4.35 | V     | BOREN configuration bit is set                                                                                                                                             |  |  |

|                       |      |                                               | 3.65                                                                                                                                                                                        | 4.0  | 4.4  | V     | BOREN configuration bit is<br>set, Extended                                                                                                                                |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.              | x <u>/xx xxx</u>                                                                                                                                                                                                                                                                      | Examples:                                                                                                                                                                                                                                    |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|