Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 224 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f628a-e-so |

#### **Table of Contents**

| 1.0 General Description                                                     | 7    |

|-----------------------------------------------------------------------------|------|

| 2.0 PIC16F627A/628A/648A Device Varieties                                   | 9    |

| 3.0 Architectural Overview                                                  | . 11 |

| 4.0 Memory Organization                                                     | 17   |

| 5.0 I/O Ports                                                               | . 33 |

| 6.0 Timer0 Module                                                           | 47   |

| 7.0 Timer1 Module                                                           | 50   |

| 8.0 Timer2 Module                                                           | . 54 |

| 9.0 Capture/Compare/PWM (CCP) Module                                        | . 57 |

| 10.0 Comparator Module                                                      |      |

| 11.0 Voltage Reference Module                                               | . 69 |

| 12.0 Universal Synchronous Asynchronous Receiver Transmitter (USART) Module | . 73 |

| 13.0 Data EEPROM Memory                                                     |      |

| 14.0 Special Features of the CPU                                            |      |

| 15.0 Instruction Set Summary                                                | 117  |

| 16.0 Development Support                                                    | 131  |

| 17.0 Electrical Specifications                                              | 135  |

| 18.0 DC and AC Characteristics Graphs and Tables                            | 151  |

| 19.0 Packaging Information                                                  | 163  |

| Appendix A: Data Sheet Revision History                                     |      |

| Appendix B: Device Differences                                              | 171  |

| Appendix C: Device Migrations                                               |      |

| Appendix D: Migrating from other PIC <sup>®</sup> Devices                   | 172  |

| The Microchip Web Site                                                      | 173  |

| Customer Change Notification Service                                        |      |

| Customer Support                                                            | 173  |

| Reader Response                                                             | 174  |

| Product Identification System                                               | 179  |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

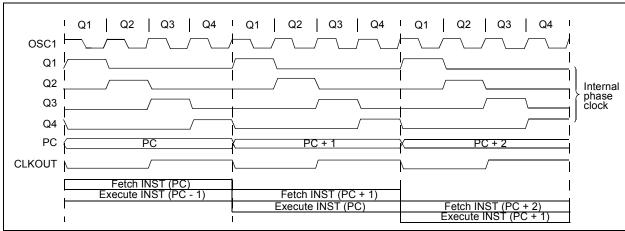

### 3.1 Clocking Scheme/Instruction Cycle

The clock input (RA7/OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the Program Counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

#### 3.2 Instruction Flow/Pipelining

An instruction cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

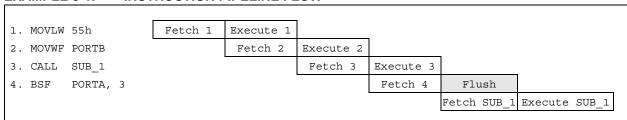

#### **EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW**

**Note:** All instructions are single cycle except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

NOTES:

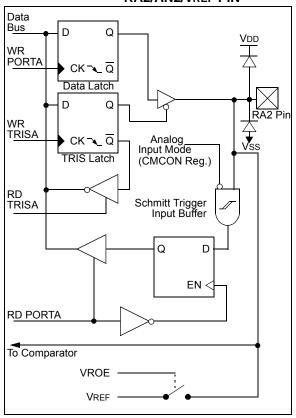

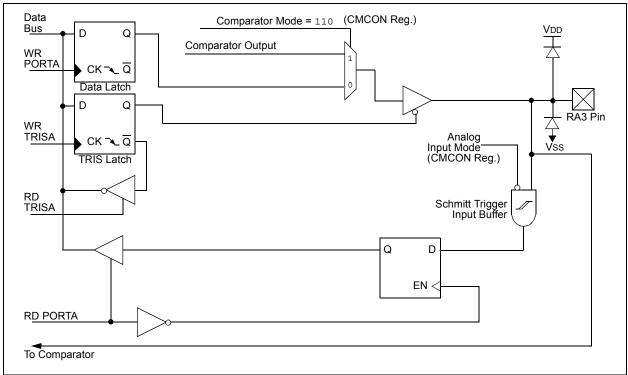

FIGURE 5-2: BLOCK DIAGRAM OF RA2/AN2/VREF PIN

#### FIGURE 5-3: BLOCK DIAGRAM OF THE RA3/AN3/CMP1 PIN

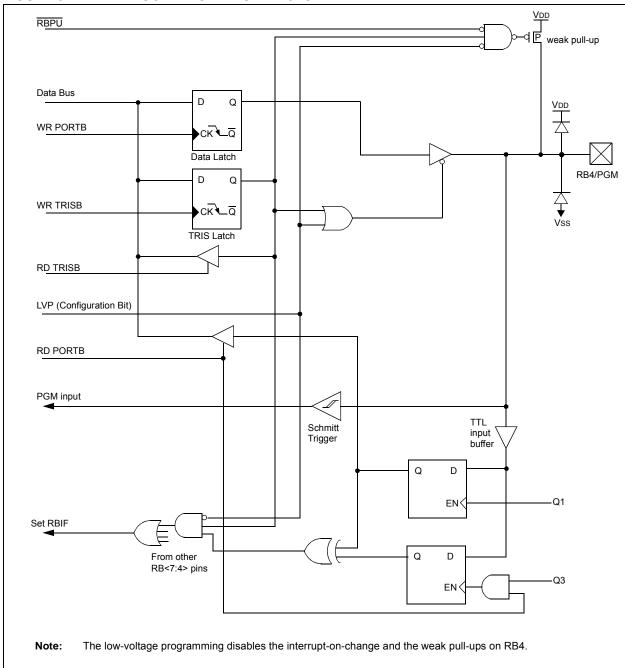

FIGURE 5-12: BLOCK DIAGRAM OF RB4/PGM PIN

#### 10.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the RA0 through RA3 pins. The on-chip Voltage Reference (Section 11.0 "Voltage Reference Module") can also be an input to the comparators.

The CMCON register, shown in Register 10-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 10-1.

#### REGISTER 10-1: CMCON – COMPARATOR CONFIGURATION REGISTER (ADDRESS: 01Fh)

| R-0   | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| C2OUT | C10UT | C2INV | C1INV | CIS   | CM2   | CM1   | CM0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7 C2OUT: Comparator 2 Output bit

When C2INV = 0:

1 = C2 VIN+ > C2 VIN-

0 = C2 VIN+ < C2 VIN-

When C2INV = 1:

1 = C2 VIN+ < C2 VIN-

0 = C2 VIN+ > C2 VIN-

bit 6 C10UT: Comparator 1 Output bit

When C1INV = 0:

1 = C1 VIN+ > C1 VIN-

0 = C1 VIN+ < C1 VIN-

When C1INV = 1:

1 = C1 VIN+ < C1 VIN-

0 = C1 VIN+ > C1 VIN-

bit 5 C2INV: Comparator 2 Output Inversion bit

1 = C2 Output inverted

0 = C2 Output not inverted

bit 4 C1INV: Comparator 1 Output Inversion bit

1 = C1 Output inverted

0 = C1 Output not inverted

bit 3 CIS: Comparator Input Switch bit

When CM<2:0>: = 001

Then:

1 = C1 VIN- connects to RA3

0 = C1 VIN- connects to RA0

When CM<2:0> = 010

Then:

1 = C1 VIN- connects to RA3

C2 VIN- connects to RA2

0 = C1 Vin- connects to RA0

C2 VIN- connects to RA1

bit 2-0 CM<2:0>: Comparator Mode bits

Figure 10-1 shows the comparator modes and CM<2:0> bit settings

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

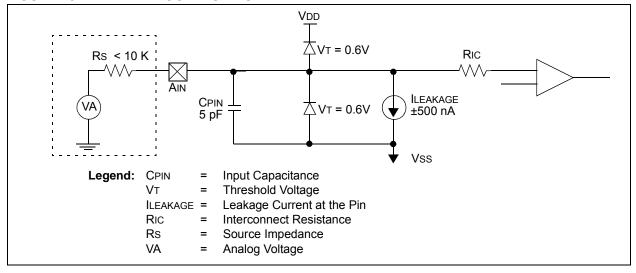

FIGURE 10-4: ANALOG INPUT MODE

TABLE 10-1: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

| Address                 | Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>Resets |

|-------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 1Fh                     | CMCON  | C2OUT  | C1OUT  | C2INV  | C1NV   | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE    | PEIE   | TOIE   | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 0Ch                     | PIR1   | EEIF   | CMIF   | RCIF   | TXIF   | _      | CCP1IF | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                       |

| 8Ch                     | PIE1   | EEIE   | CMIE   | RCIE   | TXIE   | _      | CCP1IE | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                       |

| 85h                     | TRISA  | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

**Legend:** x = Unknown, u = Unchanged, - = Unimplemented, read as '0'

TABLE 12-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD     | Fosc = 20 N | ИНZ    | SPBRG              | 16 MHz |        | SPBRG              | 10 MHz |        | SPBRG              |

|----------|-------------|--------|--------------------|--------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD       | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 0.3      | NA          | _      | _                  | NA     | _      | _                  | NA     | _      | _                  |

| 1.2      | 1.221       | +1.73% | 255                | 1.202  | +0.16% | 207                | 1.202  | +0.16% | 129                |

| 2.4      | 2.404       | +0.16% | 129                | 2.404  | +0.16% | 103                | 2.404  | +0.16% | 64                 |

| 9.6      | 9.469       | -1.36% | 32                 | 9.615  | +0.16% | 25                 | 9.766  | +1.73% | 15                 |

| 19.2     | 19.53       | +1.73% | 15                 | 19.23  | +0.16% | 12                 | 19.53  | +1.73V | 7                  |

| 76.8     | 78.13       | +1.73% | 3                  | 83.33  | +8.51% | 2                  | 78.13  | +1.73% | 1                  |

| 96       | 104.2       | +8.51% | 2                  | NA     | _      | _                  | NA     | _      | _                  |

| 300      | 312.5       | +4.17% | 0                  | NA     | _      | _                  | NA     | _      | _                  |

| 500      | NA          | _      | _                  | NA     | _      | _                  | NA     | _      | _                  |

| HIGH     | 312.5       | _      | 0                  | 250    | _      | 0                  | 156.3  | _      | 0                  |

| LOW      | 1.221       | _      | 255                | 0.977  | _      | 255                | 0.6104 | _      | 255                |

| BAUD     | Fosc = 7.15 | 909 MHz | SPBRG              | 5.0688 MHz |        | SPBRG              | 4 MHz  |        | SPBRG              |

|----------|-------------|---------|--------------------|------------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD       | ERROR   | value<br>(decimal) | KBAUD      | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 0.3      | NA          | _       | _                  | 0.31       | +3.13% | 255                | 0.3005 | -0.17% | 207                |

| 1.2      | 1.203       | +0.23%  | 92                 | 1.2        | 0      | 65                 | 1.202  | +1.67% | 51                 |

| 2.4      | 2.380       | -0.83%  | 46                 | 2.4        | 0      | 32                 | 2.404  | +1.67% | 25                 |

| 9.6      | 9.322       | -2.90%  | 11                 | 9.9        | +3.13% | 7                  | NA     | _      | _                  |

| 19.2     | 18.64       | -2.90%  | 5                  | 19.8       | +3.13% | 3                  | NA     | _      | _                  |

| 76.8     | NA          | _       | _                  | 79.2       | +3.13% | 0                  | NA     | _      | _                  |

| 96       | NA          | _       | _                  | NA         | _      | _                  | NA     | _      | _                  |

| 300      | NA          | _       | _                  | NA         |        | _                  | NA     | _      | _                  |

| 500      | NA          | _       | _                  | NA         | _      | _                  | NA     | _      | _                  |

| HIGH     | 111.9       | _       | 0                  | 79.2       | _      | 0                  | 62.500 | _      | 0                  |

| LOW      | 0.437       | _       | 255                | 0.3094     | _      | 255                | 3.906  | _      | 255                |

| BAUD     | Fosc = 3.57 | 9545 MHz | SPBRG              | 1 MHz  |        | SPBRG              | 32.768 kHz |         | SPBRG              |

|----------|-------------|----------|--------------------|--------|--------|--------------------|------------|---------|--------------------|

| RATE (K) | KBAUD       | ERROR    | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) | KBAUD      | ERROR   | value<br>(decimal) |

| 0.3      | 0.301       | +0.23%   | 185                | 0.300  | +0.16% | 51                 | 0.256      | -14.67% | 1                  |

| 1.2      | 1.190       | -0.83%   | 46                 | 1.202  | +0.16% | 12                 | NA         | _       | _                  |

| 2.4      | 2.432       | +1.32%   | 22                 | 2.232  | -6.99% | 6                  | NA         | _       | _                  |

| 9.6      | 9.322       | -2.90%   | 5                  | NA     | _      | _                  | NA         | _       | _                  |

| 19.2     | 18.64       | -2.90%   | 2                  | NA     | _      | _                  | NA         | _       | _                  |

| 76.8     | NA          | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| 96       | NA          | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| 300      | NA          | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| 500      | NA          | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| HIGH     | 55.93       | _        | 0                  | 15.63  | _      | 0                  | 0.512      | _       | 0                  |

| LOW      | 0.2185      | _        | 255                | 0.0610 | _      | 255                | 0.0020     | _       | 255                |

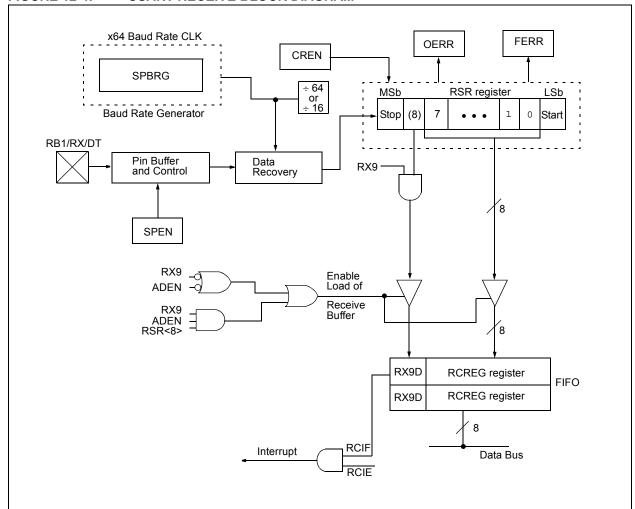

### 12.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 12-4. The data is received on the RB1/RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc.

When Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the Receive (serial) Shift Register (RSR). After sampling the Stop bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read-only bit, which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a

double buffered register (i.e., it is a two-deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte begin shifting to the RSR register. On the detection of the Stop bit of the third byte, if the RCREG register is still full, then overrun error bit OERR (RCSTA<1>) will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited, so it is essential to clear error bit OERR if it is set. Framing error bit FERR (RCSTA<2>) is set if a Stop bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG, will load bits RX9D and FERR with new values, therefore it is essential for the user to read the RCSTA register before reading RCREG register in order not to lose the old FERR and RX9D information.

FIGURE 12-4: USART RECEIVE BLOCK DIAGRAM

TABLE 12-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address | Name  | Bit 7    | Bit 6                        | Bit 5   | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on POR | Value on all other Resets |

|---------|-------|----------|------------------------------|---------|--------|-------|--------|--------|--------|--------------|---------------------------|

| 0Ch     | PIR1  | EEIF     | CMIF                         | RCIF    | TXIF   | _     | CCP1IF | TMR2IF | TMR1IF | 0000 -000    | 0000 -000                 |

| 18h     | RCSTA | SPEN     | RX9                          | SREN    | CREN   | ADEN  | FERR   | OERR   | RX9D   | 0000 000x    | 0000 000x                 |

| 19h     | TXREG | USART 1  | ransmit                      | Data Re | gister |       |        |        |        | 0000 0000    | 0000 0000                 |

| 8Ch     | PIE1  | EEIE     | CMIE                         | RCIE    | TXIE   |       | CCP1IE | TMR2IE | TMR1IE | 0000 -000    | 0000 -000                 |

| 98h     | TXSTA | CSRC     | TX9                          | TXEN    | SYNC   |       | BRGH   | TRMT   | TX9D   | 0000 -010    | 0000 -010                 |

| 99h     | SPBRG | Baud Rat | Baud Rate Generator Register |         |        |       |        |        |        |              | 0000 0000                 |

**Legend:** x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

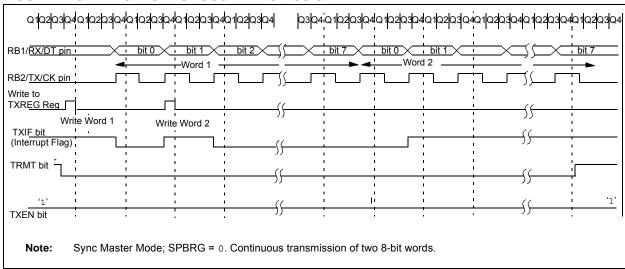

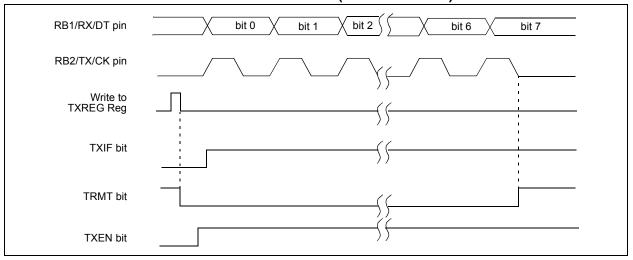

#### FIGURE 12-8: SYNCHRONOUS TRANSMISSION

FIGURE 12-9: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

### 12.5.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical except in the case of the Sleep mode. Also, bit SREN is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during Sleep. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Follow these steps when setting up a Synchronous Slave Reception:

- TRISB<1> and TRISB<2> should both be set to '1' to configure the RB1/RX/DT and RB2/TX/CK pins as inputs. Output drive, when required, is controlled by the peripheral circuitry.

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. To enable reception, set enable bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- If an OERR error occurred, clear the error by clearing bit CREN.

#### TABLE 12-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Address | Name  | Bit 7   | Bit 6                        | Bit 5   | Bit 4   | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on POR | Value on all other Resets |

|---------|-------|---------|------------------------------|---------|---------|-------|--------|--------|--------|--------------|---------------------------|

| 0Ch     | PIR1  | EEIF    | CMIF                         | RCIF    | TXIF    | _     | CCP1IF | TMR2IF | TMR1IF | 0000 -000    | 0000 -000                 |

| 18h     | RCSTA | SPEN    | RX9                          | SREN    | CREN    | ADEN  | FERR   | OERR   | RX9D   | 0000 000x    | 0000 000x                 |

| 19h     | TXREG | USART   | Fransmit                     | Data Re | egister |       |        |        |        | 0000 0000    | 0000 0000                 |

| 8Ch     | PIE1  | EEIE    | CMIE                         | RCIE    | TXIE    | _     | CCP1IE | TMR2IE | TMR1IE | 0000 -000    | 0000 -000                 |

| 98h     | TXSTA | CSRC    | TX9                          | TXEN    | SYNC    |       | BRGH   | TRMT   | TX9D   | 0000 -010    | 0000 -010                 |

| 99h     | SPBRG | Baud Ra | Baud Rate Generator Register |         |         |       |        |        |        | 0000 0000    | 0000 0000                 |

**Legend:** x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous slave transmission.

#### TABLE 12-12: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address | Name  | Bit 7                        | Bit 6   | Bit 5   | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on POR | Value on all other Resets |

|---------|-------|------------------------------|---------|---------|--------|-------|--------|--------|--------|--------------|---------------------------|

| 0Ch     | PIR1  | EEIF                         | CMIF    | RCIF    | TXIF   | _     | CCP1IF | TMR2IF | TMR1IF | 0000 -000    | 0000 -000                 |

| 18h     | RCSTA | SPEN                         | RX9     | SREN    | CREN   | ADEN  | FERR   | OERR   | RX9D   | 0000 000x    | 0000 000x                 |

| 1Ah     | RCREG | USART F                      | Receive | Data Re | gister |       |        |        |        | 0000 0000    | 0000 0000                 |

| 8Ch     | PIE1  | EEIE                         | CMIE    | RCIE    | TXIE   | _     | CCP1IE | TMR2IE | TMR1IE | 0000 -000    | 0000 -000                 |

| 98h     | TXSTA | CSRC                         | TX9     | TXEN    | SYNC   | _     | BRGH   | TRMT   | TX9D   | 0000 -010    | 0000 -010                 |

| 99h     | SPBRG | Baud Rate Generator Register |         |         |        |       |        |        |        | 0000 0000    | 0000 0000                 |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous slave reception.

NOTES:

TABLE 15-2: PIC16F627A/628A/648A INSTRUCTION SET

| Mnem   | onic, | Description                  | Cycles           |        | 14-Bit | Opcode | )    | Status   | Notes   |

|--------|-------|------------------------------|------------------|--------|--------|--------|------|----------|---------|

| Opera  | ınds  | Description                  | Cycles           | MSb    |        |        | LSb  | Affected | Notes   |

|        |       | BYTE-ORIENTED FILE REGIS     | STER OPER        | RATION | IS     |        |      |          |         |

| ADDWF  | f, d  | Add W and f                  | 1                | 0.0    | 0111   | dfff   | ffff | C,DC,Z   | 1, 2    |

| ANDWF  | f, d  | AND W with f                 | 1                | 00     | 0101   | dfff   | ffff | Z        | 1, 2    |

| CLRF   | f     | Clear f                      | 1                | 00     | 0001   | lfff   | ffff | Z        | 2       |

| CLRW   | _     | Clear W                      | 1                | 00     | 0001   | 0xxx   | xxxx | Z        |         |

| COMF   | f, d  | Complement f                 | 1                | 00     | 1001   | dfff   | ffff | Z        | 1, 2    |

| DECF   | f, d  | Decrement f                  | 1                | 00     | 0011   | dfff   | ffff | Z        | 1, 2    |

| DECFSZ | f, d  | Decrement f, Skip if 0       | 1 <sup>(2)</sup> | 00     | 1011   | dfff   | ffff |          | 1, 2, 3 |

| INCF   | f, d  | Increment f                  | 1                | 00     | 1010   | dfff   | ffff | Z        | 1, 2    |

| INCFSZ | f, d  | Increment f, Skip if 0       | 1(2)             | 00     | 1111   | dfff   | ffff |          | 1, 2, 3 |

| IORWF  | f, d  | Inclusive OR W with f        | 1                | 0.0    | 0100   | dfff   | ffff | Z        | 1, 2    |

| MOVF   | f, d  | Move f                       | 1                | 00     | 1000   | dfff   | ffff | Z        | 1, 2    |

| MOVWF  | f     | Move W to f                  | 1                | 0.0    | 0000   | lfff   | ffff |          |         |

| NOP    | _     | No Operation                 | 1                | 0.0    | 0000   | 0xx0   | 0000 |          |         |

| RLF    | f, d  | Rotate Left f through Carry  | 1                | 0.0    | 1101   | dfff   | ffff | С        | 1, 2    |

| RRF    | f, d  | Rotate Right f through Carry | 1                | 0.0    | 1100   | dfff   | ffff | С        | 1, 2    |

| SUBWF  | f, d  | Subtract W from f            | 1                | 0.0    | 0010   | dfff   | ffff | C,DC,Z   | 1, 2    |

| SWAPF  | f, d  | Swap nibbles in f            | 1                | 0.0    | 1110   | dfff   | ffff |          | 1, 2    |

| XORWF  | f, d  | Exclusive OR W with f        | 1                | 00     | 0110   | dfff   | ffff | Z        | 1, 2    |

|        |       | BIT-ORIENTED FILE REGIS      | TER OPER         | ATIONS | 3      |        |      |          |         |

| BCF    | f, b  | Bit Clear f                  | 1                | 01     | 0 0bb  | bfff   | ffff |          | 1, 2    |

| BSF    | f, b  | Bit Set f                    | 1                | 01     | 01bb   | bfff   | ffff |          | 1, 2    |

| BTFSC  | f, b  | Bit Test f, Skip if Clear    | 1(2)             | 01     | 10bb   | bfff   | ffff |          | 3       |

| BTFSS  | f, b  | Bit Test f, Skip if Set      | 1 <sup>(2)</sup> | 01     | 11bb   | bfff   | ffff |          | 3       |

|        |       | LITERAL AND CONTROL          | OPERATION        | ONS    |        |        |      | 1        |         |

| ADDLW  | k     | Add literal and W            | 1                | 11     | 111x   | kkkk   | kkkk | C,DC,Z   |         |

| ANDLW  | k     | AND literal with W           | 1                | 11     | 1001   | kkkk   | kkkk | Z        |         |

| CALL   | k     | Call subroutine              | 2                | 10     | 0kkk   | kkkk   | kkkk |          |         |

| CLRWDT | _     | Clear Watchdog Timer         | 1                | 0.0    | 0000   | 0110   | 0100 | TO,PD    |         |

| GOTO   | k     | Go to address                | 2                | 10     | 1kkk   | kkkk   | kkkk | <u> </u> |         |

| IORLW  | k     | Inclusive OR literal with W  | 1                | 11     | 1000   | kkkk   | kkkk | Z        |         |

| MOVLW  | k     | Move literal to W            | 1                | 11     | 00xx   | kkkk   | kkkk |          |         |

| RETFIE | _     | Return from interrupt        | 2                | 00     | 0000   | 0000   | 1001 |          |         |

| RETLW  | k     | Return with literal in W     | 2                | 11     | 01xx   | kkkk   | kkkk |          |         |

| RETURN | _     | Return from Subroutine       | 2                | 00     | 0000   | 0000   | 1000 |          |         |

| SLEEP  | _     | Go into Standby mode         | 1                | 00     | 0000   | 0110   | 0011 | TO,PD    |         |

| SUBLW  | k     | Subtract W from literal      | 1                | 11     | 110x   | kkkk   | kkkk | C,DC,Z   |         |

| XORLW  | k     | Exclusive OR literal with W  | 1                | 11     | 1010   | kkkk   | kkkk | Z        |         |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

<sup>2:</sup> If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the

<sup>3:</sup> If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| BCF              | Bit Clear f                                                  |          |             |      |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------|----------|-------------|------|--|--|--|--|--|--|

| Syntax:          | [ label ]                                                    | BCF 1    | f,b         |      |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$ $0 \le b \le 7$                            |          |             |      |  |  |  |  |  |  |

| Operation:       | $0 \rightarrow (f <$                                         | b>)      |             |      |  |  |  |  |  |  |

| Status Affected: | None                                                         |          |             |      |  |  |  |  |  |  |

| Encoding:        | 01                                                           | 00bb     | bfff        | ffff |  |  |  |  |  |  |

| Description:     | Bit 'b' in                                                   | register | 'f' is clea | red. |  |  |  |  |  |  |

| Words:           | 1                                                            |          |             |      |  |  |  |  |  |  |

| Cycles:          | 1                                                            |          |             |      |  |  |  |  |  |  |

| <u>Example</u>   | BCF                                                          | REG1,    | 7           |      |  |  |  |  |  |  |

|                  | Before Instruction REG1 = 0xC7 After Instruction REG1 = 0x47 |          |             |      |  |  |  |  |  |  |

| BSF              | Bit Set f                                                           |       |      |      |  |  |

|------------------|---------------------------------------------------------------------|-------|------|------|--|--|

| Syntax:          | [ label ] BSF f,b                                                   |       |      |      |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |       |      |      |  |  |

| Operation:       | 1 → (f<                                                             | b>)   |      |      |  |  |

| Status Affected: | None                                                                |       |      |      |  |  |

| Encoding:        | 01                                                                  | 01bb  | bfff | ffff |  |  |

| Description:     | Bit 'b' in register 'f' is set.                                     |       |      |      |  |  |

| Words:           | 1                                                                   |       |      |      |  |  |

| Cycles:          | 1                                                                   |       |      |      |  |  |

| <u>Example</u>   | BSF                                                                 | REG1, | 7    |      |  |  |

|                  | Before Instruction  REG1 = 0x0A  After Instruction  REG1 = 0x8A     |       |      |      |  |  |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                                                 |                         |                |        |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------|--------|--|--|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                                                       |                         |                |        |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                                       |                         |                |        |  |  |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                                                   |                         |                |        |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                      |                         |                |        |  |  |

| Encoding:        | 01                                                                                                                                                                                                                                                        | 10bb                    | bfff           | ffff   |  |  |

| Description:     | If bit 'b' in register 'f' is '0', then the next instruction is skipped.  If bit 'b' is '0', then the next instruction fetched during the current instruction execution is discarded, and a NOP is executed instead, making this a two-cycle instruction. |                         |                |        |  |  |

| Words:           | 1                                                                                                                                                                                                                                                         |                         |                |        |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                      |                         |                |        |  |  |

| <u>Example</u>   | HERE<br>FALSE<br>TRUE                                                                                                                                                                                                                                     | BTFSC<br>GOTO<br>•<br>• | REG1<br>PROCES | S_CODE |  |  |

|                  | Before Instruction PC = address HERE  After Instruction if REG<1> = 0, PC = address TRUE if REG<1> = 1, PC = address FALSE                                                                                                                                |                         |                |        |  |  |

#### 16.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB® IDE Software

- · Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C for Various Device Families

- MPASM™ Assembler

- MPLINK<sup>TM</sup> Object Linker/ MPLIB<sup>TM</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- · In-Circuit Debuggers

- MPLAB ICD 3

- PICkit™ 3 Debug Express

- · Device Programmers

- PICkit™ 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

### 16.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows® operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- · A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

### 16.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

### 16.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

#### 16.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

#### 16.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 16.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command line interface

- · Rich directive set

- · Flexible macro language

- MPLAB IDE compatibility

### 17.1 DC Characteristics: PIC16F627A/628A/648A (Industrial, Extended) PIC16LF627A/628A/648A (Industrial)

| PIC16LF627A/628A/648A<br>(Industrial)          |      |                                                                                                                                                                                                                                        | Standard Operating Conditions (unless otherwise stated) Operating temperature -40°C ≤ Ta ≤ +85°C for industrial |            |             |       |                                                                                                                                                                            |  |

|------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------|-------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PIC16F627A/628A/648A<br>(Industrial, Extended) |      | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for industrial and $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for extended |                                                                                                                 |            |             |       |                                                                                                                                                                            |  |

| Param<br>No.                                   | Sym  | Characteristic/Device                                                                                                                                                                                                                  | Min                                                                                                             | Typ†       | Max         | Units | Conditions                                                                                                                                                                 |  |

| VDD Supply Voltage                             |      |                                                                                                                                                                                                                                        |                                                                                                                 |            |             |       |                                                                                                                                                                            |  |

| D001                                           |      | PIC16LF627A/628A/648A                                                                                                                                                                                                                  | 2.0                                                                                                             |            | 5.5         | V     |                                                                                                                                                                            |  |

|                                                |      | PIC16F627A/628A/648A                                                                                                                                                                                                                   | 3.0                                                                                                             |            | 5.5         | V     |                                                                                                                                                                            |  |

| D002                                           | VDR  | RAM Data Retention Voltage <sup>(1)</sup>                                                                                                                                                                                              | _                                                                                                               | 1.5*       | _           | V     | Device in Sleep mode                                                                                                                                                       |  |

| D003                                           | VPOR | VDD Start Voltage<br>to ensure Power-on Reset                                                                                                                                                                                          | _                                                                                                               | Vss        | _           | V     | See Section 14.4 "Power-<br>on Reset (POR), Power-up<br>Timer (PWRT), Oscillator<br>Start-up Timer (OST) and<br>Brown-out Reset<br>(BOR)"on Power-on Reset<br>for details  |  |

| D004                                           | SVDD | VDD Rise Rate<br>to ensure Power-on Reset                                                                                                                                                                                              | 0.05*                                                                                                           | _          | _           | V/ms  | See Section 14.4 "Power-<br>on Reset (POR), Power-up<br>Timer (PWRT), Oscillator<br>Start-up Timer (OST) and<br>Brown-out Reset (BOR)"<br>on Power-on Reset for<br>details |  |

| D005                                           | VBOR | Brown-out Reset Voltage                                                                                                                                                                                                                | 3.65<br>3.65                                                                                                    | 4.0<br>4.0 | 4.35<br>4.4 | V     | BOREN configuration bit is set BOREN configuration bit is set, Extended                                                                                                    |  |

**Legend:** Rows with standard voltage device data only are shaded for improved readability.

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

TABLE 17-8: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym       | Characteristic                                                                      |                             | Min                                        | Typ†                                    | Max                 | Units | Conditions                             |                                       |

|--------------|-----------|-------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------|-----------------------------------------|---------------------|-------|----------------------------------------|---------------------------------------|

| 40           | Тт0Н      | Toora riigirr aloo waar                                                             |                             | No Prescaler                               | 0.5Tcy + 20*                            | _                   | _     | ns                                     |                                       |

|              |           |                                                                                     |                             | With Prescaler                             | 10*                                     | _                   | _     | ns                                     |                                       |

| 41           | TT0L      |                                                                                     |                             | No Prescaler                               | 0.5Tcy + 20*                            | _                   | _     | ns                                     |                                       |

|              |           |                                                                                     |                             | With Prescaler                             | 10*                                     | _                   | _     | ns                                     |                                       |

| 42           | Тт0Р      | T0CKI Period                                                                        |                             | Greater of:<br>20 or <u>Tcy + 40*</u><br>N | _                                       | _                   | ns    | N = prescale<br>value (2, 4,<br>, 256) |                                       |

| 45           | T⊤1H      |                                                                                     | h Synchronous, No Prescaler |                                            | 0.5Tcy + 20*                            | _                   | —     | ns                                     |                                       |

|              |           | Time                                                                                | Synchronous, with Prescaler | PIC16F62XA                                 | 15*                                     | _                   | —     | ns                                     |                                       |

|              |           |                                                                                     |                             |                                            | 25*                                     | _                   |       | ns                                     |                                       |

|              |           |                                                                                     | Asynchronous                | PIC16F62XA                                 | 30*                                     | _                   | _     | ns                                     |                                       |

|              |           |                                                                                     |                             | PIC16LF62XA                                | 50*                                     | _                   |       | ns                                     |                                       |

| 46           | TT1L      | T1CKI Low<br>Time                                                                   | Synchronous,                |                                            | 0.5Tcy + 20*                            | _                   |       | ns                                     |                                       |

|              |           |                                                                                     | Synchronous,                | PIC16F62XA                                 | 15*                                     | _                   | _     | ns                                     |                                       |

|              |           |                                                                                     |                             | PIC16LF62XA                                | 25*                                     | _                   |       | ns                                     |                                       |

|              |           | Asynchronous PIC16F62XA                                                             |                             | 30*                                        | _                                       |                     | ns    |                                        |                                       |

|              |           |                                                                                     | PIC16LF62XA                 | 50*                                        |                                         |                     | ns    |                                        |                                       |

| 47           | T⊤1P      | T1CKI input period                                                                  | out Synchronous             | PIC16F62XA                                 | Greater of: 20 or <u>Tcy + 40*</u> N    | _                   | _     | ns                                     | N = prescale<br>value (1, 2,<br>4, 8) |

|              |           |                                                                                     |                             | PIC16LF62XA                                | Greater of: 20 or <u>Tcy + 40*</u><br>N | _                   | _     | _                                      |                                       |

|              |           |                                                                                     | Asynchronous                | PIC16F62XA                                 | 60*                                     | _                   | _     | ns                                     |                                       |

|              |           |                                                                                     |                             | PIC16LF62XA                                | 100*                                    | _                   | _     | ns                                     |                                       |

|              | FT1       | Timer1 oscillator input frequency range (oscillator enabled by setting bit T1OSCEN) |                             |                                            | _                                       | 32.7 <sup>(1)</sup> | _     | kHz                                    |                                       |

| 48           | TCKEZTMR1 | Delay from external clock edge to timer increment                                   |                             |                                            | 2Tosc                                   | _                   | 7Tosc | _                                      |                                       |

<sup>\*</sup> These parameters are characterized but not tested.

**Note 1:** This oscillator is intended to work only with 32.768 kHz watch crystals and their manufactured tolerances. Higher value crystal frequencies may not be compatible with this crystal driver.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

NOTES:

| Q                                                               |         | External Clock Input                                                |          |

|-----------------------------------------------------------------|---------|---------------------------------------------------------------------|----------|

| Q-Clock                                                         | 61      | External Clock Input Timing                                         |          |

| Quick-Turnaround-Production (QTP) Devices                       |         | Oscillator                                                          |          |

|                                                                 |         | Prescaler                                                           |          |

| R                                                               |         | Resetting Timer1                                                    |          |

| RC Oscillator                                                   | 101     | Resetting Timer1 Registers                                          |          |

| RC Oscillator Mode                                              |         | Special Event Trigger (CCP)                                         |          |

| Block Diagram                                                   | 101     | Synchronized Counter Mode                                           |          |

| Reader Response                                                 |         | Timer Mode                                                          |          |

| Registers                                                       |         | TMR1H                                                               |          |

| CCP1CON (CCP Operation)                                         | 57      | TMR1L                                                               | 52       |

| CMCON (Comparator Configuration)                                | 63      | Timer2                                                              | _        |

| CONFIG (Configuration Word)                                     | 98      | Block Diagram                                                       |          |

| EECON1 (EEPROM Control Register 1)                              | 92      | Postscaler                                                          |          |

| INTCON (Interrupt Control)                                      | 26      | PR2 register                                                        |          |

| Maps                                                            |         | Prescaler                                                           | -        |

| PIC16F627A                                                      | 18, 19  | Timer2 Module                                                       |          |

| PIC16F628A                                                      | 18, 19  | TMR2 output                                                         |          |

| OPTION_REG (Option)                                             | 25      | TMR2 to PR2 Match Interrupt                                         | 60       |

| PCON (Power Control)                                            |         | Timing Diagrams                                                     | 4.4-     |

| PIE1 (Peripheral Interrupt Enable 1)                            |         | Timer0                                                              |          |

| PIR1 (Peripheral Interrupt Register 1)                          |         | Timer1                                                              | 147      |

| Status                                                          |         | USART                                                               | 01       |

| T1CON Timer1 Control)                                           | 50      | Asynchronous Receiver                                               |          |

| T2CON Timer2 Control)                                           |         | USART Asynchronous Master Transmission USART Asynchronous Reception |          |

| Reset                                                           |         |                                                                     |          |

| RETFIE Instruction                                              |         | USART Synchronous Reception                                         |          |

| RETLW Instruction                                               |         | USART Synchronous Transmission Timing Diagrams and Specifications   |          |

| RETURN Instruction                                              |         | TMR0 Interrupt                                                      |          |

| Revision History                                                |         | TMR1CS bit                                                          |          |

| RLF Instruction                                                 |         | TMR10N bit                                                          |          |

| RRF Instruction                                                 | 128     | TMR2ON bit                                                          |          |

| S                                                               |         | TOUTPS0 bit                                                         |          |

|                                                                 | · HCADT | TOUTPS1 bit                                                         |          |

| Serial Communication Interface (SCI) Module, Se                 |         | TOUTPS2 bit                                                         |          |

| Serialized Quick-Turnaround-Production (SQTP) SLEEP Instruction |         | TOUTPS3 bit                                                         |          |

| Software Simulator (MPLAB SIM)                                  |         | TRIS Instruction                                                    |          |

| Special Event Trigger. See Compare                              | 133     | TRISA                                                               |          |

| Special Features of the CPU                                     | 97      | TRISB                                                               |          |

| Special Function Registers                                      |         |                                                                     |          |

| Status Register                                                 |         | U                                                                   |          |

| SUBLW Instruction                                               |         | Universal Synchronous Asynchronous Receiver Tra                     | ansmitte |

| SUBWF Instruction                                               |         | (USART)                                                             | 73       |

| SWAPF Instruction                                               |         | Asynchronous Receiver                                               |          |

|                                                                 |         | Setting Up Reception                                                | 85       |

| Т                                                               |         | Asynchronous Receiver Mode                                          |          |

| T1CKPS0 bit                                                     | 50      | Address Detect                                                      | 85       |

| T1CKPS1 bit                                                     | 50      | Block Diagram                                                       | 85       |

| T1CON Register                                                  | 50      | USART                                                               |          |

| T1OSCEN bit                                                     | 50      | Asynchronous Mode                                                   |          |

| T2CKPS0 bit                                                     | 55      | Asynchronous Receiver                                               |          |

| T2CKPS1 bit                                                     | 55      | Asynchronous Reception                                              |          |

| T2CON Register                                                  | 55      | Asynchronous Transmission                                           |          |

| Timer0                                                          |         | Asynchronous Transmitter                                            |          |

| Block Diagrams                                                  |         | Baud Rate Generator (BRG)                                           | 75       |

| Timer0/WDT                                                      |         | Block Diagrams                                                      |          |

| External Clock Input                                            |         | Transmit                                                            |          |

| Interrupt                                                       | 47      | USART Receive                                                       |          |

| Prescaler                                                       |         | BRGH bit                                                            |          |

| Switching Prescaler Assignment                                  | 49      | Sampling7                                                           |          |

| Timer0 Module                                                   | 47      | Synchronous Master Mode                                             |          |

| Timer1                                                          |         | Synchronous Master Reception                                        |          |

| Asynchronous Counter Mode                                       |         | Synchronous Master Transmission                                     |          |

| Capacitor Selection                                             | 53      | Synchronous Slave Mode                                              |          |

|                                                                 |         | Synchronous Slave Reception                                         | 90       |