Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 224 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f628a-e-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

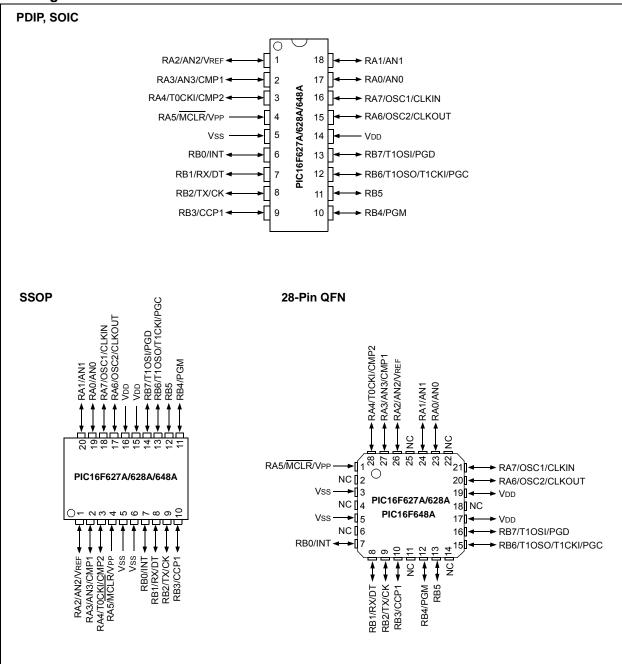

### **Pin Diagrams**

NOTES:

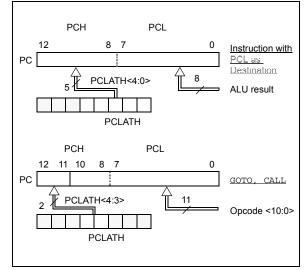

## 4.3 PCL and PCLATH

The Program Counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 4-4 shows the two situations for loading the PC. The upper example in Figure 4-4 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 4-4 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

### FIGURE 4-4: LOADING OF PC IN DIFFERENT SITUATIONS

### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the Application Note AN556 "*Implementing a Table Read*" (DS00556).

## 4.3.2 STACK

The PIC16F627A/628A/648A family has an 8-level deep x 13-bit wide hardware stack (Figure 4-1). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth PUSH overwrites the value that was stored from the first PUSH. The tenth PUSH overwrites the second PUSH (and so on).

| Note 1: | There are no Status bits to indicate stack |

|---------|--------------------------------------------|

|         | overflow or stack underflow conditions.    |

2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

# 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-5.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 4-1.

|      | MOVLW | 0x20  | ;initialize pointer  |

|------|-------|-------|----------------------|

|      | MOVWF | FSR   | ;to RAM              |

| NEXT | CLRF  | INDF  | clear INDF register; |

|      | INCF  | FSR   | ;inc pointer         |

|      | BTFSS | FSR,4 | ;all done?           |

|      | GOTO  | NEXT  | ;no clear next       |

|      |       |       | ;yes continue        |

|      |       |       |                      |

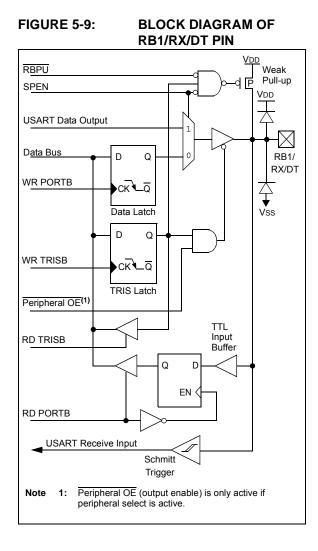

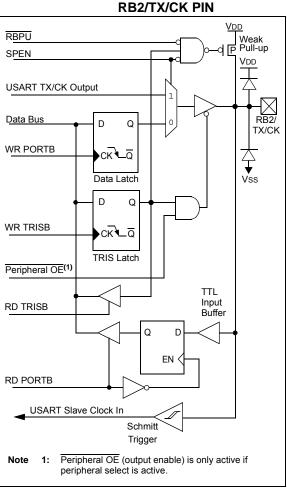

## FIGURE 5-10: BLOCK DIAGRAM OF

## 7.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L) which are readable and writable. The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The Timer1 Interrupt, if enabled, is generated on overflow of the TMR1 register pair which latches the interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing the Timer1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- As a timer

- As a counter

The Operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

-n = Value at POR

In Timer mode, the TMR1 register pair value increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "Reset input". This Reset can be generated by the CCP module (Section 9.0 "Capture/Compare/PWM (CCP) Module"). Register 7-1 shows the Timer1 control register.

For the PIC16F627A/628A/648A, when the Timer1 oscillator is enabled (T1OSCEN is set), the RB7/T1OSI/PGD and RB6/T1OSO/T1CKI/PGC pins become inputs. That is, the TRISB<7:6> value is ignored.

| TER 7-1: | T1CON – TIN                                                                                    | IER1 C                 | ONTROLI         | REGISTER       | (ADDRESS:       | 10h)        |                |             |

|----------|------------------------------------------------------------------------------------------------|------------------------|-----------------|----------------|-----------------|-------------|----------------|-------------|

|          | U-0                                                                                            | U-0                    | R/W-0           | R/W-0          | R/W-0           | R/W-0       | R/W-0          | R/W-0       |

|          | —                                                                                              |                        | T1CKPS1         | T1CKPS0        | T1OSCEN         | T1SYNC      | TMR1CS         | TMR10N      |

|          | bit 7                                                                                          |                        |                 |                |                 |             |                | bit 0       |

| bit 7-6  | Unimplement                                                                                    | ed: Read               | <b>d as</b> 'o' |                |                 |             |                |             |

| bit 5-4  | T1CKPS<1:0>                                                                                    | : Timer1               | Input Clock     | k Prescale Se  | elect bits      |             |                |             |

|          | 11 = 1:8 Preso<br>10 = 1:4 Preso<br>01 = 1:2 Preso<br>00 = 1:1 Preso                           | cale valu<br>cale valu | e               |                |                 |             |                |             |

| bit 3    | T1OSCEN: Tir                                                                                   | mer1 Oso               | cillator Enab   | ole Control bi | t               |             |                |             |

|          | 1 = Oscillator i<br>0 = Oscillator i                                                           |                        |                 |                |                 |             |                |             |

| bit 2    | T1SYNC: Time                                                                                   | er1 Exter              | nal Clock Ir    | nput Synchro   | nization Contro | ol bit      |                |             |

|          | <u>TMR1CS = 1</u><br>1 = Do not syr<br>0 = Synchroniz<br><u>TMR1CS = 0</u><br>This bit is igno | ze exterr              | al clock inp    | out            | ck when TMR1    | CS = 0.     |                |             |

| bit 1    | TMR1CS: Tim                                                                                    | er1 Cloc               | k Source Se     | elect bit      |                 |             |                |             |

|          | 1 = External cl<br>0 = Internal clo                                                            |                        |                 | 10SO/T1CKI     | /PGC (on the r  | ising edge  | )              |             |

| bit 0    | TMR1ON: Tim                                                                                    | er1 On b               | bit             |                |                 |             |                |             |

|          | 1 = Enables T<br>0 = Stops Time                                                                |                        |                 |                |                 |             |                |             |

|          | Note 1: Th                                                                                     | e oscillat             | tor inverter a  | and feedback   | resistor are tu | rned off to | eliminate po   | ower drain. |

|          | Legend:                                                                                        |                        |                 |                |                 |             |                |             |

|          | R = Readable                                                                                   | bit                    | VV = V          | Vritable bit   | U = Unimple     | emented bi  | it, read as '( | <b>)</b> '  |

'1' = Bit is set

'0' = Bit is cleared

REGISTER 7-1: T1CON – TIMER1 CONTROL REGISTER (ADDRESS: 10h)

x = Bit is unknown

NOTES:

The code example in Example 10-1 depicts the steps required to configure the Comparator module. RA3 and RA4 are configured as digital output. RA0 and RA1 are configured as the V- inputs and RA2 as the V+ input to both comparators.

| EXAMPLE 10-1: | INITIALIZING      |

|---------------|-------------------|

|               | COMPARATOR MODULE |

| FLAG_REG | EQU          | 0X20                          |

|----------|--------------|-------------------------------|

| CLRF     | FLAG_REG     | ;Init flag register           |

| CLRF     | PORTA        | ;Init PORTA                   |

| MOVF     | CMCON, W     | ;Load comparator bits         |

| ANDLW    | 0xC0         | ;Mask comparator bits         |

| IORWF    | FLAG_REG,F   | ;Store bits in flag register  |

| MOVLW    | 0x03         | ;Init comparator mode         |

| MOVWF    | CMCON        | ;CM<2:0> = 011                |

| BSF      | STATUS, RPO  | ;Select Bank1                 |

| MOVLW    | 0x07         | ;Initialize data direction    |

| MOVWF    | TRISA        | ;Set RA<2:0> as inputs        |

|          |              | ;RA<4:3> as outputs           |

|          |              | ;TRISA<7:5> always read `0'   |

| BCF      | STATUS, RPO  | ;Select Bank 0                |

| CALL     | DELAY10      | ;10Ms delay                   |

| MOVF     | CMCON, F     | ;Read CMCONto end change      |

|          |              | ;condition                    |

| BCF      | PIR1,CMIF    | ;Clear pending interrupts     |

| BSF      | STATUS, RPO  | ;Select Bank 1                |

| BSF      | PIE1,CMIE    | ;Enable comparator interrupts |

| BCF      | STATUS, RPO  | ;Select Bank 0                |

| BSF      | INTCON, PEIE | ;Enable peripheral interrupts |

| BSF      | INTCON, GIE  | ;Global interrupt enable      |

|          |              | 8                             |

## **10.2** Comparator Operation

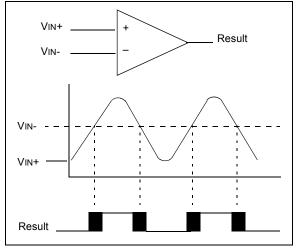

A single comparator is shown in Figure 10-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 10-2 represent the uncertainty due to input offsets and response time. See Table 17-2 for Common Mode voltage.

## 10.3 Comparator Reference

An external or internal reference signal may be used depending on the comparator Operating mode. The analog signal that is present at VIN- is compared to the signal at VIN+, and the digital output of the comparator is adjusted accordingly (Figure 10-2).

#### FIGURE 10-2:

SINGLE COMPARATOR

### 10.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the Comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between Vss and VDD, and can be applied to either pin of the comparator(s).

### 10.3.2 INTERNAL REFERENCE SIGNAL

The Comparator module also allows the selection of an internally generated voltage reference for the comparators. **Section 11.0 "Voltage Reference Module"**, contains a detailed description of the Voltage Reference module that provides this signal. The internal reference signal is used when the comparators are in mode CM<2:0> = 010 (Figure 10-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

## 10.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output is to have a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (Table 17-2, page 142).

## 14.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real-time applications are what sets a microcontroller apart from other processors. The PIC16F627A/628A/648A family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. Reset

- 3. Power-on Reset (POR)

- 4. Power-up Timer (PWRT)

- 5. Oscillator Start-Up Timer (OST)

- 6. Brown-out Reset (BOR)

- 7. Interrupts

- 8. Watchdog Timer (WDT)

- 9. Sleep

- 10. Code protection

- 11. ID Locations

- 12. In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

The PIC16F627A/628A/648A has a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in Reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs. With these three functions on-chip, most applications need no external Reset circuitry.

The Sleep mode is designed to offer a very low current Power-down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

## 14.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special configuration memory space (2000h-3FFFh), which can be accessed only during programming. See *"PIC16F627A/628A/648A EEPROM Memory*"

*Programming Specification*" (DS41196) for additional information.

### 14.4 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST) and Brown-out Reset (BOR)

#### 14.4.1 POWER-ON RESET (POR)

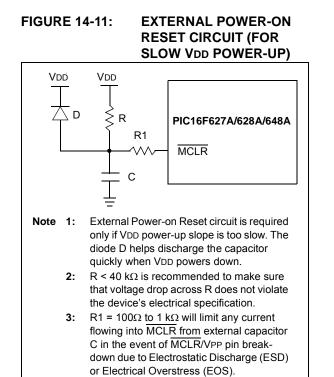

The on-chip POR holds the part in Reset until a VDD rise is detected (in the range of 1.2-1.7V). A maximum rise time for VDD is required. See **Section 17.0 "Electrical Specifications"** for details.

The POR circuit does not produce an internal Reset when VDD declines.

When the device starts normal operation (exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure proper operation. If these conditions are not met, the device must be held in Reset via MCLR, BOR or PWRT until the operating conditions are met.

For additional information, refer to Application Note AN607 "*Power-up Trouble Shooting*" (DS00607).

#### 14.4.2 POWER-UP TIMER (PWRT)

The PWRT provides a fixed 72 ms (nominal) time out on power-up (POR) or if enabled from a Brown-out Reset. The PWRT operates on an internal RC oscillator. The chip is kept in Reset as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the PWRT. It is recommended that the PWRT be enabled when Brown-out Reset is enabled.

The power-up time delay will vary from chip-to-chip and due to VDD, temperature and process variation. See DC parameters Table 17-7 for details.

### 14.4.3 OSCILLATOR START-UP TIMER (OST)

The OST provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. Program execution will not start until the OST time out is complete. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from Sleep. See Table 17-7.

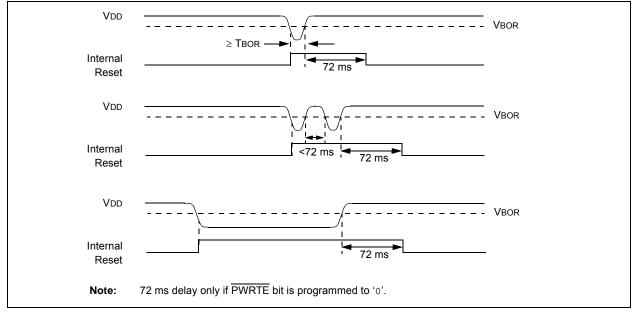

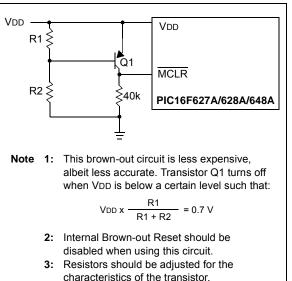

#### 14.4.4 BROWN-OUT RESET (BOR)

The PIC16F627A/628A/648A have on-chip BOR circuitry. A configuration bit, BOREN, can disable (if clear/programmed) or enable (if set) the BOR circuitry. If VDD falls below VBOR for longer than TBOR, the brown-out situation will reset the chip. A Reset is not assured if VDD falls below VBOR for shorter than TBOR. VBOR and TBOR are defined in Table 17-2 and Table 17-7, respectively.

On any Reset (Power-on, Brown-out, Watchdog, etc.), the chip will remain in Reset until VDD rises above VBOR (see Figure 14-7). The Power-up Timer will now be invoked, if enabled, and will keep the chip in Reset an additional 72 ms.

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-Up Timer will execute a 72 ms Reset. Figure 14-7 shows typical brown-out situations.

#### FIGURE 14-7: BROWN-OUT SITUATIONS WITH PWRT ENABLED

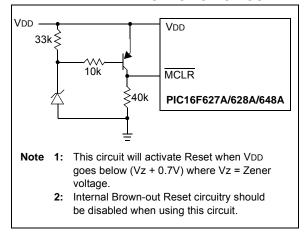

FIGURE 14-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

### FIGURE 14-13: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

|                         |        |       | -     | -     |       |       | -      |        |        |                       |                                                |

|-------------------------|--------|-------|-------|-------|-------|-------|--------|--------|--------|-----------------------|------------------------------------------------|

| Address                 | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR Reset | Value on all<br>other<br>Resets <sup>(1)</sup> |

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE   | PEIE  | TOIE  | INTE  | RBIE  | TOIF   | INTF   | RBIF   | 0000 000x             | 0000 000u                                      |

| 0Ch                     | PIR1   | EEIF  | CMIF  | RCIF  | TXIF  | _     | CCP1IF | TMR2IF | TMR1IF | 0000 -000             | 0000 -000                                      |

| 8Ch                     | PIE1   | EEIE  | CMIE  | RCIE  | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE | 0000 -000             | 0000 -000                                      |

TABLE 14-8:SUMMARY OF INTERRUPT REGISTERS

Note 1: Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

### 14.6 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W register and Status register). This must be implemented in software.

Example 14-1 stores and restores the Status and W registers. The user register, W\_TEMP, must be defined in a common memory location (i.e., W\_TEMP is defined at 0x70 in Bank 0 and is therefore, accessible at 0xF0, 0x170 and 0x1F0). The Example 14-1:

- · Stores the W register

- · Stores the Status register

- Executes the ISR code

- Restores the Status (and bank select bit register)

- Restores the W register

#### EXAMPLE 14-1: SAVING THE STATUS AND W REGISTERS IN RAM

| MOVWF            | W_TEMP      | ;copy W to temp register,<br>;could be in any bank   |

|------------------|-------------|------------------------------------------------------|

| SWAPF            | STATUS,W    | ;swap status to be saved<br>;into W                  |

| BCF              | STATUS, RPO | ;change to bank 0<br>;regardless of current<br>;bank |

| MOVWF            | STATUS_TEME | ?;save status to bank 0<br>;register                 |

| :                |             |                                                      |

| :(1              | ISR)        |                                                      |

| :                |             |                                                      |

| SWAPF<br>registe | _           | P,W;swap STATUS_TEMP                                 |

|                  |             | ;into W, sets bank to                                |

| origina          | al          |                                                      |

| MOVWF            | STATUS      | ;state<br>;move W into STATUS<br>;register           |

| SWAPF            | W_TEMP,F    | ;swap W_TEMP                                         |

| SWAPF            | W_TEMP,W    | ;swap W_TEMP into W                                  |

|                  |             |                                                      |

### 14.7 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the CLKIN pin. That means that the WDT will run, even if the clock on the OSC1 and OSC2 pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time out generates a device Reset. If the device is in Sleep mode, a WDT time out causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming the configuration Bits").

### 14.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC Specifications, Table 17-7). If longer timeout periods are desired, a postscaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device Reset.

The  $\overline{\text{TO}}$  bit in the Status register will be cleared upon a Watchdog Timer time out.

#### 14.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler) it may take several seconds before a WDT time out occurs.

AND Literal with W

ANDLW

| ADDLW            | Add Literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Encoding:        | 11 111x kkkk kkkk                                                                                                          |

| Description:     | The contents of the W register<br>are added to the eight bit literal<br>'k' and the result is placed in the<br>W register. |

| Words:           | 1                                                                                                                          |

| Cycles:          | 1                                                                                                                          |

| Example          | ADDLW 0x15                                                                                                                 |

|                  | Before Instruction<br>W = 0x10<br>After Instruction<br>W = 0x25                                                            |

| Curstand                                                |                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                 | [ <i>label</i> ] ANDLW k                                                                                                                                                                                                                                                                                                                                  |

| Operands:                                               | $0 \le k \le 255$                                                                                                                                                                                                                                                                                                                                         |

| Operation:                                              | (W) .AND. (k) $\rightarrow$ (W)                                                                                                                                                                                                                                                                                                                           |

| Status Affected:                                        | Z                                                                                                                                                                                                                                                                                                                                                         |

| Encoding:                                               | 11 1001 kkkk kkkk                                                                                                                                                                                                                                                                                                                                         |

| Description:                                            | The contents of W register are<br>AND'ed with the eight bit literal<br>'k'. The result is placed in the W<br>register.                                                                                                                                                                                                                                    |

| Words:                                                  | 1                                                                                                                                                                                                                                                                                                                                                         |

| Cycles:                                                 | 1                                                                                                                                                                                                                                                                                                                                                         |

| Example                                                 | ANDLW 0x5F                                                                                                                                                                                                                                                                                                                                                |

|                                                         | Before Instruction<br>W = 0xA3<br>After Instruction                                                                                                                                                                                                                                                                                                       |

|                                                         | W = 0x03                                                                                                                                                                                                                                                                                                                                                  |

| ANDWF                                                   | AND W with f                                                                                                                                                                                                                                                                                                                                              |

| Syntax:                                                 | [label] ANDWF f,d                                                                                                                                                                                                                                                                                                                                         |

| Operands:                                               | $0 \le f \le 127$                                                                                                                                                                                                                                                                                                                                         |

|                                                         | $d \in [0,1]$                                                                                                                                                                                                                                                                                                                                             |

| Operation:                                              | d ∈ [0,1]<br>(W) .AND. (f) → (dest)                                                                                                                                                                                                                                                                                                                       |

| Operation:<br>Status Affected:                          |                                                                                                                                                                                                                                                                                                                                                           |

| •                                                       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                                                                                                                                                                                        |

| Status Affected:                                        | (W) .AND. (f) $\rightarrow$ (dest)<br>Z                                                                                                                                                                                                                                                                                                                   |

| Status Affected:<br>Encoding:                           | (W) .AND. (f) $\rightarrow$ (dest)<br>Z<br>00 0101 dfff ffff<br>AND the W register with register<br>'f'. If 'd' is '0', the result is stored<br>in the W register. If 'd' is '1', the<br>result is stored back in register                                                                                                                                |

| Status Affected:<br>Encoding:<br>Description:           | $\begin{array}{c c} (W) \ . AND. \ (f) \rightarrow (dest) \\ \hline Z \\ \hline 00 & 0101 & dfff & ffff \\ \hline AND \ the \ W \ register \ with \ register \\ \ 'f'. \ If \ 'd' \ is \ '0', \ the \ result \ is \ stored \\ in \ the \ W \ register. \ If \ 'd' \ is \ '1', \ the \\ result \ is \ stored \ back \ in \ register \\ \ 'f'. \end{array}$ |

| Status Affected:<br>Encoding:<br>Description:<br>Words: | (W) .AND. (f) $\rightarrow$ (dest)<br>Z<br>00 0101 dfff ffff<br>AND the W register with register<br>'f'. If 'd' is '0', the result is stored<br>in the W register. If 'd' is '1', the<br>result is stored back in register<br>'f'.<br>1                                                                                                                   |

| ADDWF            | Add W and f                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                        |

| Operation:       | (W) + (f) $\rightarrow$ (dest)                                                                                                                                                     |

| Status Affected: | C, DC, Z                                                                                                                                                                           |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                                  |

| Description:     | Add the contents of the W<br>register with register 'f'. If 'd' is<br>'0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

| Words:           | 1                                                                                                                                                                                  |

| Cycles:          | 1                                                                                                                                                                                  |

| Example          | ADDWF REG1, 0                                                                                                                                                                      |

|                  | Before Instruction<br>W = 0x17<br>REG1 = 0xC2<br>After Instruction<br>W = 0xD9<br>REG1 = 0xC2<br>Z = 0<br>C = 0<br>DC = 0                                                          |

| MOVWF            | Move W to f                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] MOVWF f                                                                                       |

| Operands:        | $0 \leq f \leq 127$                                                                                   |

| Operation:       | $(W) \rightarrow (f)$                                                                                 |

| Status Affected: | None                                                                                                  |

| Encoding:        | 00 0000 1fff ffff                                                                                     |

| Description:     | Move data from W register to register 'f'.                                                            |

| Words:           | 1                                                                                                     |

| Cycles:          | 1                                                                                                     |

| Example          | MOVWF REG1                                                                                            |

|                  | Before Instruction<br>REG1 = $0xFF$<br>W = $0x4F$<br>After Instruction<br>REG1 = $0x4F$<br>W = $0x4F$ |

| OPTION                 | Load Op                                                                                                             | otion Re                                                                | gister                                                                                               |                                                        |

|------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Syntax:                | [label] OPTION                                                                                                      |                                                                         |                                                                                                      |                                                        |

| Operands:              | None                                                                                                                |                                                                         |                                                                                                      |                                                        |

| Operation:             | $(W) \rightarrow C$                                                                                                 | PTION                                                                   |                                                                                                      |                                                        |

| Status Affected:       | None                                                                                                                |                                                                         |                                                                                                      |                                                        |

| Encoding:              | 00                                                                                                                  | 0000                                                                    | 0110                                                                                                 | 0010                                                   |

| Description:<br>Words: | loaded ir<br>This inst<br>code cor<br>products<br>readable<br>user can                                              | n the OP<br>ruction is<br>npatibilit<br>Since (<br>writable<br>directly | he W regi<br>TION reg<br>s support<br>y with PIC<br>OPTION i<br>register,<br>address i<br>ruction su | jister.<br>ed for<br>C16C5X<br>is a<br>the<br>t. Using |

| Cycles:                | 1                                                                                                                   |                                                                         |                                                                                                      |                                                        |

| Example                | To main                                                                                                             |                                                                         | ward aam                                                                                             | notibil                                                |

|                        | To maintain upward compatibil-<br>ity with future PIC <sup>®</sup> MCU<br>products, do not use this<br>instruction. |                                                                         |                                                                                                      |                                                        |

|                        |                                                                                                                     |                                                                         |                                                                                                      |                                                        |

| NOP              | No Operation |        |      |      |

|------------------|--------------|--------|------|------|

| Syntax:          | [label] NOP  |        |      |      |

| Operands:        | None         |        |      |      |

| Operation:       | No operation |        |      |      |

| Status Affected: | None         |        |      |      |

| Encoding:        | 00           | 0000   | 0xx0 | 0000 |

| Description:     | No oper      | ation. |      |      |

| Words:           | 1            |        |      |      |

| Cycles:          | 1            |        |      |      |

| Example          | NOP          |        |      |      |

| RETFIE           | Return from Interrupt                                               |                                                        |             |                        |

|------------------|---------------------------------------------------------------------|--------------------------------------------------------|-------------|------------------------|

| Syntax:          | [ label ]                                                           | RETF                                                   | IE          |                        |

| Operands:        | None                                                                |                                                        |             |                        |

| Operation:       | $\begin{array}{c} TOS \rightarrow \\ 1 \rightarrow GIE \end{array}$ | - ,                                                    |             |                        |

| Status Affected: | None                                                                |                                                        |             |                        |

| Encoding:        | 00                                                                  | 0000                                                   | 0000        | 1001                   |

| Description:     | POPed a<br>is loaded<br>are enat<br>Interrupt                       | and Top<br>d in the<br>bled by s<br>Enable<br>N<7>). T | This is a t | (TOS)<br>rupts<br>obal |

| Words:           | 1                                                                   |                                                        |             |                        |

| Cycles:          | 2                                                                   |                                                        |             |                        |

| Example          | RETFIE                                                              |                                                        |             |                        |

|                  |                                                                     | errupt<br>C = T(<br>IE = 1                             | OS          |                        |

| RETLW             | Return with Literal in W                                                                                                                                                               | RLF               | Rotate Left f through Carry                                                                                                                                                                                          |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:           | [ <i>label</i> ] RETLW k                                                                                                                                                               | Syntax:           | [ <i>label</i> ] RLF f,d                                                                                                                                                                                             |  |  |  |

| Operands:         | $0 \le k \le 255$                                                                                                                                                                      | Operands:         | $0 \leq f \leq 127$                                                                                                                                                                                                  |  |  |  |

| Operation:        | $k \rightarrow (W);$                                                                                                                                                                   |                   | d ∈ [0,1]                                                                                                                                                                                                            |  |  |  |

|                   | $TOS \rightarrow PC$                                                                                                                                                                   | Operation:        | See description below                                                                                                                                                                                                |  |  |  |

| Status Affected:  | None                                                                                                                                                                                   | Status Affected:  | С                                                                                                                                                                                                                    |  |  |  |

| Encoding:         | 11 01xx kkkk kkkk                                                                                                                                                                      | Encoding:         | 00 1101 dfff ffff                                                                                                                                                                                                    |  |  |  |

| Description:      | The W register is loaded with<br>the eight-bit literal 'k'. The<br>program counter is loaded from<br>the top of the stack (the return<br>address). This is a two-cycle<br>instruction. | Description:      | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is stored<br>back in register 'f'. |  |  |  |

| Words:            | 1                                                                                                                                                                                      |                   |                                                                                                                                                                                                                      |  |  |  |

| Cycles:           | 2                                                                                                                                                                                      | Marda.            | 1                                                                                                                                                                                                                    |  |  |  |

| Example           | CALL TABLE;W contains table                                                                                                                                                            | Words:<br>Cycles: | 1                                                                                                                                                                                                                    |  |  |  |

|                   | ;offset value<br>• ;W now has table value                                                                                                                                              | Example           | RLF REG1, 0                                                                                                                                                                                                          |  |  |  |

| TABLE             | <pre>ADDWF PC;W = offset RETLW k1;Begin table RETLW k2;  RETLW kn; End of table Before Instruction W = 0x07 After Instruction W = value of k8</pre>                                    |                   | Before Instruction<br>REG1=1110 0110<br>C = 0<br>After Instruction<br>REG1=1110 0110<br>W = 1100 1100<br>C = 1                                                                                                       |  |  |  |

| RETURN<br>Syntax: | Return from Subroutine                                                                                                                                                                 |                   |                                                                                                                                                                                                                      |  |  |  |

| Syntax:          | [ label ]                                                                                                                                                  | RETU              | RN   |      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|------|

| Operands:        | None                                                                                                                                                       | 11210             |      |      |

| Operation:       | TOS $\rightarrow$                                                                                                                                          | PC                |      |      |

| Status Affected: | None                                                                                                                                                       |                   |      |      |

| Encoding:        | 00                                                                                                                                                         | 0000              | 0000 | 1000 |

| Description:     | Return from subroutine. The<br>stack is POPed and the top of<br>the stack (TOS) is loaded into<br>the program counter. This is a<br>two-cycle instruction. |                   |      |      |

| Words:           | 1                                                                                                                                                          |                   |      |      |

| Cycles:          | 2                                                                                                                                                          |                   |      |      |

| Example          | RETURN                                                                                                                                                     |                   |      |      |

|                  | After Int<br>P                                                                                                                                             | terrupt<br>C = TO | S    |      |

### 17.1 DC Characteristics: PIC16F627A/628A/648A (Industrial, Extended) PIC16LF627A/628A/648A (Industrial)

| <b>PIC16L</b><br>(Industri                     |      | 628A/648A                                            |       | l <b>Operatin</b><br>g temperati | -    | •     | ss otherwise stated)<br>+85°C for industrial                                                                                                                               |

|------------------------------------------------|------|------------------------------------------------------|-------|----------------------------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIC16F627A/628A/648A<br>(Industrial, Extended) |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |       |                                  |      |       |                                                                                                                                                                            |

| Param<br>No.                                   | Sym  | Characteristic/Device                                | Min   | Тур†                             | Мах  | Units | Conditions                                                                                                                                                                 |

|                                                | Vdd  | Supply Voltage                                       |       |                                  |      |       |                                                                                                                                                                            |

| D001                                           |      | PIC16LF627A/628A/648A                                | 2.0   |                                  | 5.5  | V     |                                                                                                                                                                            |

|                                                |      | PIC16F627A/628A/648A                                 | 3.0   | _                                | 5.5  | V     |                                                                                                                                                                            |

| D002                                           | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>         | _     | 1.5*                             | _    | V     | Device in Sleep mode                                                                                                                                                       |

| D003                                           | VPOR | VDD Start Voltage<br>to ensure Power-on Reset        | _     | Vss                              | _    | V     | See Section 14.4 "Power-<br>on Reset (POR), Power-up<br>Timer (PWRT), Oscillator<br>Start-up Timer (OST) and<br>Brown-out Reset<br>(BOR)"on Power-on Reset<br>for details  |

| D004                                           | SVDD | VDD Rise Rate<br>to ensure Power-on Reset            | 0.05* | _                                | _    | V/ms  | See Section 14.4 "Power-<br>on Reset (POR), Power-up<br>Timer (PWRT), Oscillator<br>Start-up Timer (OST) and<br>Brown-out Reset (BOR)"<br>on Power-on Reset for<br>details |

| D005                                           | VBOR | Brown-out Reset Voltage                              | 3.65  | 4.0                              | 4.35 | V     | BOREN configuration bit is set                                                                                                                                             |

|                                                |      |                                                      | 3.65  | 4.0                              | 4.4  | V     | BOREN configuration bit is<br>set, Extended                                                                                                                                |

Legend: Rows with standard voltage device data only are shaded for improved readability.

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

## 17.5 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| Z. TPPS  |                                        |     |                |  |

|----------|----------------------------------------|-----|----------------|--|

| т        |                                        |     |                |  |

| F        | Frequency                              | Т   | Time           |  |

| Lowercas | se subscripts (pp) and their meanings: |     |                |  |

| рр       |                                        |     |                |  |

| ck       | CLKOUT                                 | OSC | OSC1           |  |

| io       | I/O port                               | tO  | TOCKI          |  |

| mc       | MCLR                                   |     |                |  |

| Uppercas | se letters and their meanings:         |     |                |  |

| S        |                                        |     |                |  |

| F        | Fall                                   | Р   | Period         |  |

| Н        | High                                   | R   | Rise           |  |

| I        | Invalid (High-impedance)               | V   | Valid          |  |

| L        | Low                                    | Z   | High-Impedance |  |

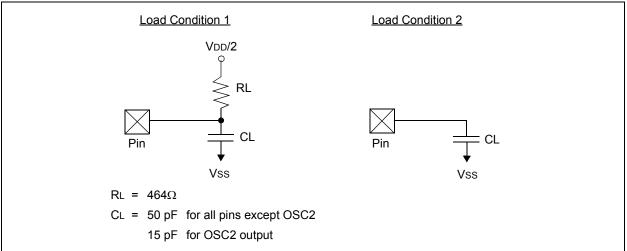

### FIGURE 17-3: LOAD CONDITIONS

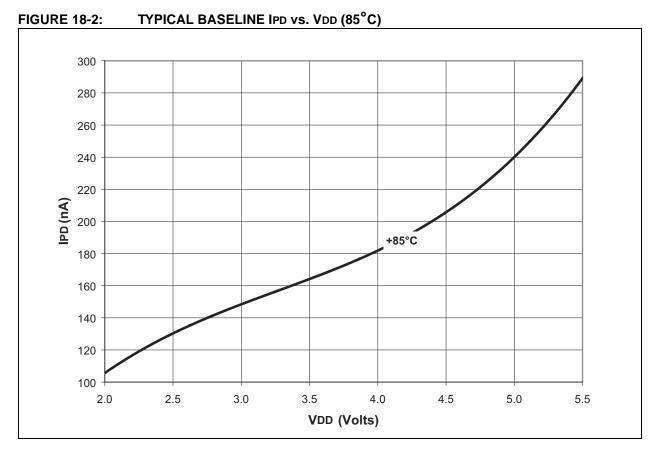

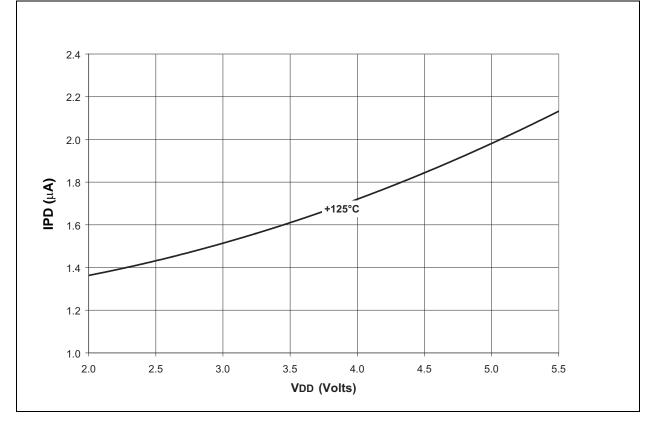

FIGURE 18-3: TYPICAL BASELINE CURRENT IPD vs. VDD (125°C)

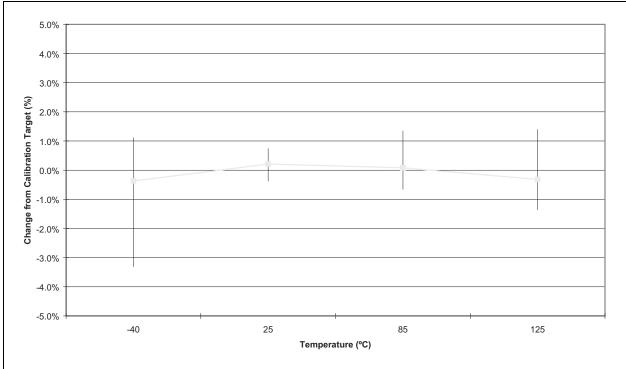

FIGURE 18-10: TYPICAL INTERNAL OSCILLATOR FREQUENCY vs. TEMPERATURE VDD = 3 VOLTS

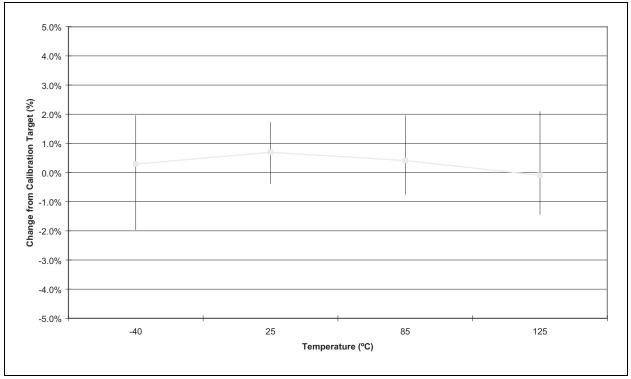

FIGURE 18-11: TYPICAL INTERNAL OSCILLATOR FREQUENCY vs. TEMPERATURE VDD = 2 VOLTS

NOTES:

## **19.0 PACKAGING INFORMATION**

## **19.1 Package Marking Information**

### 18-Lead PDIP

#### 20-Lead SSOP

### 28-Lead QFN

Example

### Example

#### Example

### Example

| Legend: | XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                                | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| l       | Note: In the event the full Microchip part number cannot be marked on one line, it be carried over to the next line, thus limiting the number of availa characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                |