Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | UART/USART                                                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 224 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

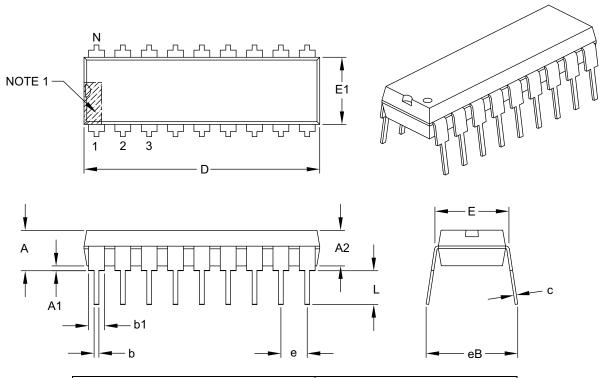

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 18-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f628a-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 18-pin Flash-Based, 8-Bit CMOS Microcontrollers with nanoWatt Technology

# **High-Performance RISC CPU:**

- Operating speeds from DC 20 MHz

- · Interrupt capability

- 8-level deep hardware stack

- Direct, Indirect and Relative Addressing modes

- 35 single-word instructions:

- All instructions single cycle except branches

# **Special Microcontroller Features:**

- · Internal and external oscillator options:

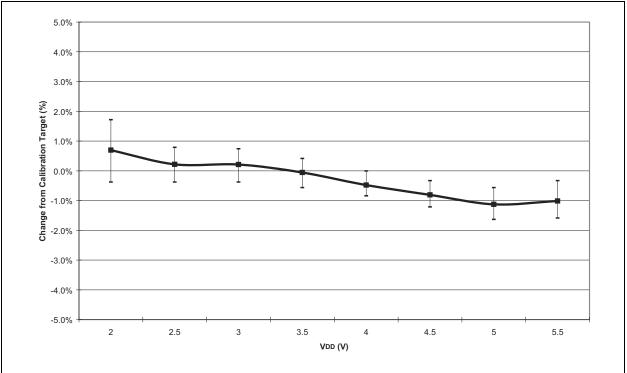

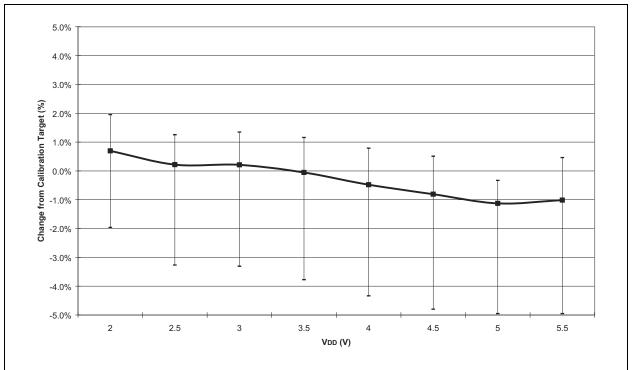

- Precision internal 4 MHz oscillator factory calibrated to  $\pm 1\%$

- Low-power internal 48 kHz oscillator

- External Oscillator support for crystals and resonators

- Power-saving Sleep mode

- · Programmable weak pull-ups on PORTB

- Multiplexed Master Clear/Input-pin

- Watchdog Timer with independent oscillator for reliable operation

- Low-voltage programming

- In-Circuit Serial Programming<sup>™</sup> (via two pins)

- Programmable code protection

- Brown-out Reset

- Power-on Reset

- · Power-up Timer and Oscillator Start-up Timer

- Wide operating voltage range (2.0-5.5V)

- Industrial and extended temperature range

- High-Endurance Flash/EEPROM cell:

- 100,000 write Flash endurance

- 1,000,000 write EEPROM endurance

- 40 year data retention

# Low-Power Features:

- · Standby Current:

- 100 nA @ 2.0V, typical

- · Operating Current:

- 12 μA @ 32 kHz, 2.0V, typical

- 120 μA @ 1 MHz, 2.0V, typical

- Watchdog Timer Current:

- 1 μA @ 2.0V, typical

- Timer1 Oscillator Current:

- 1.2 μA @ 32 kHz, 2.0V, typical

- Dual-speed Internal Oscillator:

- Run-time selectable between 4 MHz and 48 kHz

- 4 µs wake-up from Sleep, 3.0V, typical

# **Peripheral Features:**

- 16 I/O pins with individual direction control

- High current sink/source for direct LED drive

- · Analog comparator module with:

- Two analog comparators

- Programmable on-chip voltage reference (VREF) module

- Selectable internal or external reference

- Comparator outputs are externally accessible

- Timer0: 8-bit timer/counter with 8-bit programmable prescaler

- Timer1: 16-bit timer/counter with external crystal/ clock capability

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

- · Capture, Compare, PWM module:

- 16-bit Capture/Compare

- 10-bit PWM

- Addressable Universal Synchronous/Asynchronous Receiver/Transmitter USART/SCI

| Device     | Program<br>Memory | Data N          | lemory            | 1/0 | ССР   | USART | Comparators | Timers   |  |

|------------|-------------------|-----------------|-------------------|-----|-------|-------|-------------|----------|--|

| Device     | Flash<br>(words)  | SRAM<br>(bytes) | EEPROM<br>(bytes) | I/O | (PWM) | USART | Comparators | 8/16-bit |  |

| PIC16F627A | 1024              | 224             | 128               | 16  | 1     | Y     | 2           | 2/1      |  |

| PIC16F628A | 2048              | 224             | 128               | 16  | 1     | Y     | 2           | 2/1      |  |

| PIC16F648A | 4096              | 256             | 256               | 16  | 1     | Y     | 2           | 2/1      |  |

# 2.0 PIC16F627A/628A/648A DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16F627A/628A/648A Product Identification System, at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

# 2.1 Flash Devices

Flash devices can be erased and re-programmed electrically. This allows the same device to be used for prototype development, pilot programs and production.

A further advantage of the electrically erasable Flash is that it can be erased and reprogrammed in-circuit, or by device programmers, such as Microchip's PICSTART<sup>®</sup> Plus or PRO MATE<sup>®</sup> II programmers.

# 2.2 Quick-Turnaround-Production (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who chose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are standard Flash devices, but with all program locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

# 2.3 Serialized Quick-Turnaround-Production (SQTP<sup>SM</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number, which can serve as an entry-code, password or ID number.

### 4.2.2.1 Status Register

The Status register, shown in Register 4-1, contains the arithmetic status of the ALU; the Reset status and the bank select bits for data memory (SRAM).

The Status register can be the destination for any instruction, like any other register. If the Status register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are non-writable. Therefore, the result of an instruction with the Status register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the Status register as "000uu1uu" (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the Status register because these instructions do not affect any Status bit. For other instructions, not affecting any Status bits, see the "Instruction Set Summary".

| Note: | The C and DC bits operate as a Borrow      |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | and Digit Borrow out bit, respectively, in |  |  |  |  |  |  |  |  |

|       | subtraction. See the SUBLW and SUBWF       |  |  |  |  |  |  |  |  |

|       | instructions for examples.                 |  |  |  |  |  |  |  |  |

## REGISTER 4-1: STATUS – STATUS REGISTER (ADDRESS: 03h, 83h, 103h, 183h)

|         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0                                          | R/W-0         | R-1           | R-1              | R/W-x     | R/W-x          | R/W-x       |  |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------|---------------|------------------|-----------|----------------|-------------|--|--|--|--|

|         | IRP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RP1                                            | RP0           | TO            | PD               | Z         | DC             | С           |  |  |  |  |

|         | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                |               |               |                  |           |                | bit 0       |  |  |  |  |

| bit 7   | 1 = Bank 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ter Bank Sel<br>2, 3 (100h-1F<br>), 1 (00h-FFh | Fh)           | d for indirec | t addressing)    |           |                |             |  |  |  |  |

| bit 6-5 | <b>RP&lt;1:0&gt;</b> : 1<br>00 = Bank<br>01 = Bank<br>10 = Bank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •                                              | ik Select bit | ts (used for  | direct addressir | ng)       |                |             |  |  |  |  |

| bit 4   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ower-up, CLI                                   |               | ction or SLI  | EEP instruction  |           |                |             |  |  |  |  |

| bit 3   | <ul> <li>0 = A WDT time out occurred</li> <li>PD: Power-down bit</li> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                |               |               |                  |           |                |             |  |  |  |  |

| bit 2   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | sult of an arit                                |               |               |                  |           |                |             |  |  |  |  |

| bit 1   | is reversed<br>1 = A carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1)<br>/-out from the                           | e 4th low or  | der bit of th | e result occurre |           | for Borrow t   | he polarity |  |  |  |  |

| bit 0   | <ul> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> <li>DC: Digit Carry/Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for Borrow the polarity is reversed)</li> <li>1 = A carry-out from the 4th low order bit of the result occurred</li> <li>0 = No carry-out from the 4th low order bit of the result</li> <li>C: Carry/Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)</li> <li>1 = A carry-out from the 4th low order bit of the result</li> <li>C: Carry/Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)</li> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> <li>No carry-out from the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.</li> </ul> |                                                |               |               |                  |           |                |             |  |  |  |  |

|         | Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                |               |               |                  |           |                |             |  |  |  |  |

|         | R = Reada                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                | VV = V        | Vritable bit  | U = Unimple      | emented b | oit, read as ' | יכ          |  |  |  |  |

|         | -n = Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | at POR                                         | '1' = E       | Bit is set    | '0' = Bit is c   | leared    | x = Bit is ur  | nknown      |  |  |  |  |

| Name                                       | Function | Input<br>Type | Output<br>Type | Description                                                                                                                                                |  |  |  |  |

|--------------------------------------------|----------|---------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RA0/AN0                                    | RA0      | ST            | CMOS           | Bidirectional I/O port                                                                                                                                     |  |  |  |  |

|                                            | AN0      | AN            | _              | Analog comparator input                                                                                                                                    |  |  |  |  |

| RA1/AN1                                    | RA1      | ST            | CMOS           | Bidirectional I/O port                                                                                                                                     |  |  |  |  |

|                                            | AN1      | AN            | _              | Analog comparator input                                                                                                                                    |  |  |  |  |

| RA2/AN2/VREF                               | RA2      | ST            | CMOS           | Bidirectional I/O port                                                                                                                                     |  |  |  |  |

|                                            | AN2      | AN            |                | Analog comparator input                                                                                                                                    |  |  |  |  |

|                                            | VREF     |               | AN             | VREF output                                                                                                                                                |  |  |  |  |

| RA3/AN3/CMP1                               | RA3      | ST            | CMOS           | Bidirectional I/O port                                                                                                                                     |  |  |  |  |

|                                            | AN3      | AN            |                | Analog comparator input                                                                                                                                    |  |  |  |  |

|                                            | CMP1     |               | CMOS           | Comparator 1 output                                                                                                                                        |  |  |  |  |

| RA4/T0CKI/CMP2                             | RA4      | ST            | OD             | Bidirectional I/O port. Output is open drain type.                                                                                                         |  |  |  |  |

|                                            | T0CKI    | ST            |                | External clock input for TMR0 or comparator output                                                                                                         |  |  |  |  |

|                                            | CMP2     |               | OD             | Comparator 2 output                                                                                                                                        |  |  |  |  |

| RA5/MCLR/Vpp                               | RA5      | ST            | _              | Input port                                                                                                                                                 |  |  |  |  |

|                                            | MCLR     | ST            | _              | Master clear. When configured as MCLR, this pin is an active low Reset to the device. Voltage on MCLR/VPP munot exceed VDD during normal device operation. |  |  |  |  |

|                                            | Vpp      | HV            | _              | Programming voltage input                                                                                                                                  |  |  |  |  |

| RA6/OSC2/CLKOUT                            | RA6      | ST            | CMOS           | Bidirectional I/O port                                                                                                                                     |  |  |  |  |

|                                            | OSC2     | _             | XTAL           | Oscillator crystal output. Connects to crystal resonator in Crystal Oscillator mode.                                                                       |  |  |  |  |

|                                            | CLKOUT   | —             | CMOS           | In RC or INTOSC mode. OSC2 pin can output CLKOUT, which has 1/4 the frequency of OSC1.                                                                     |  |  |  |  |

| RA7/OSC1/CLKIN                             | RA7      | ST            | CMOS           | Bidirectional I/O port                                                                                                                                     |  |  |  |  |

|                                            | OSC1     | XTAL          | _              | Oscillator crystal input. Connects to crystal resonator in Crystal Oscillator mode.                                                                        |  |  |  |  |

|                                            | CLKIN    | ST            | _              | External clock source input. RC biasing pin.                                                                                                               |  |  |  |  |

| Legend: O = Outp<br>— = Not u<br>TTL = TTL | used     | CN<br>I<br>OE | = Inp          | IOS OutputP = PowerOutST = Schmitt Trigger InputDen Drain OutputAN = Analog                                                                                |  |  |  |  |

TABLE 5-1: PORTA FUNCTIONS

| TABLE 5-2:         SUMMARY OF REGISTERS ASSOCIATED WITH PORTA |

|---------------------------------------------------------------|

|---------------------------------------------------------------|

| Address | Name  | Bit 7  | Bit 6  | Bit 5              | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>Resets |

|---------|-------|--------|--------|--------------------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 05h     | PORTA | RA7    | RA6    | RA5 <sup>(1)</sup> | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx 0000       | qqqu 0000                       |

| 85h     | TRISA | TRISA7 | TRISA6 | TRISA5             | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

| 1Fh     | CMCON | C2OUT  | C10UT  | C2INV              | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 9Fh     | VRCON | VREN   | VROE   | VRR                | _      | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

Legend: - = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition. Shaded cells are not used for PORTA.

Note 1: MCLRE configuration bit sets RA5 functionality.

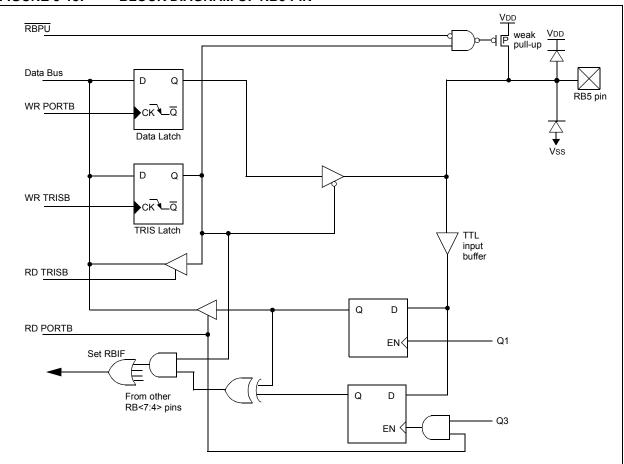

### FIGURE 5-13: BLOCK DIAGRAM OF RB5 PIN

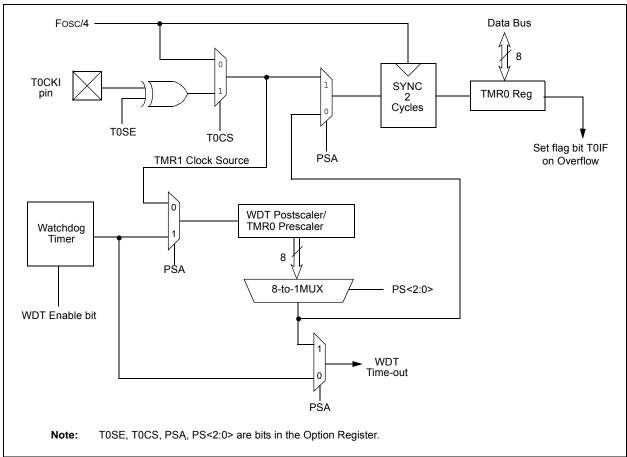

# 6.3 Timer0 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer. A prescaler assignment for the Timer0 module means that there is no postscaler for the Watchdog Timer, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x...etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

FIGURE 6-1: BLOCK DIAGRAM OF THE TIMER0/WDT

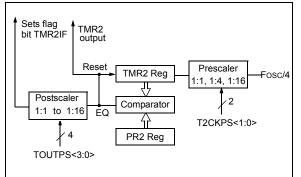

# 8.0 TIMER2 MODULE

Timer2 is an 8-bit timer with a prescaler and a postscaler. It can be used as the PWM time base for PWM mode of the CCP module. The TMR2 register is readable and writable, and is cleared on any device Reset.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS<1:0> (T2CON<1:0>).

The Timer2 module has an 8-bit period register PR2. The TMR2 register value increments from 00h until it matches the PR2 register value and then resets to 00h on the next increment cycle. The PR2 register is a readable and writable register. The PR2 register is initialized to FFh upon Reset.

The match output of Timer2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a Timer2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

Timer2 can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Register 8-1 shows the Timer2 control register.

### 8.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- · a write to the T2CON register

- any device Reset (Power-on Reset, MCLR Reset, Watchdog Timer Reset or Brown-out Reset)

The TMR2 register is not cleared when T2CON is written.

# 8.2 TMR2 Output

The TMR2 output (before the postscaler) is fed to the Synchronous Serial Port module which optionally uses it to generate shift clock.

#### FIGURE 8-1: TIMER2 BLOCK DIAGRAM

| REGISTER 8-1: | T2CO                                                     | N – TIMER2                                       | CONTRO      | L REGISTE      | R (ADDRES  | S: 12h)     |                |         |  |  |  |  |  |

|---------------|----------------------------------------------------------|--------------------------------------------------|-------------|----------------|------------|-------------|----------------|---------|--|--|--|--|--|

|               | U-0                                                      | R/W-0                                            | R/W-0       | R/W-0          | R/W-0      | R/W-0       | R/W-0          | R/W-0   |  |  |  |  |  |

|               | —                                                        | TOUTPS3                                          | TOUTPS2     | TOUTPS1        | TOUTPS0    | TMR2ON      | T2CKPS1        | T2CKPS0 |  |  |  |  |  |

|               | bit 7                                                    |                                                  |             |                |            |             |                | bit 0   |  |  |  |  |  |

| bit 7         | Unimplem                                                 | ented: Read                                      | as '0'      |                |            |             |                |         |  |  |  |  |  |

| bit 6-3       | -                                                        | TOUTPS<3:0>: Timer2 Output Postscale Select bits |             |                |            |             |                |         |  |  |  |  |  |

|               | 0000 = 1:1 Postscale Value<br>0001 = 1:2 Postscale Value |                                                  |             |                |            |             |                |         |  |  |  |  |  |

|               |                                                          |                                                  |             |                |            |             |                |         |  |  |  |  |  |

|               | •                                                        |                                                  |             |                |            |             |                |         |  |  |  |  |  |

|               | •                                                        |                                                  |             |                |            |             |                |         |  |  |  |  |  |

|               | 1111 <b>= 1</b> :1                                       | 6 Postscale                                      |             |                |            |             |                |         |  |  |  |  |  |

| bit 2         | TMR2ON:                                                  | Timer2 On bi                                     | it          |                |            |             |                |         |  |  |  |  |  |

|               | 1 = Timer2<br>0 = Timer2                                 |                                                  |             |                |            |             |                |         |  |  |  |  |  |

| bit 1-0       |                                                          | 1:0>: Timer2                                     | Clock Presc | ale Select bit | s          |             |                |         |  |  |  |  |  |

|               |                                                          | rescaler Valu                                    |             |                | -          |             |                |         |  |  |  |  |  |

|               | 01 <b>= 1:4 P</b>                                        | rescaler Valu                                    | е           |                |            |             |                |         |  |  |  |  |  |

|               | 1x = 1:16                                                | Prescaler Val                                    | ue          |                |            |             |                |         |  |  |  |  |  |

|               | Legend:                                                  |                                                  |             |                |            |             |                |         |  |  |  |  |  |

|               | R = Reada                                                | able bit                                         | W = W       | /ritable bit   | U = Unimpl | emented bit | t, read as '0' |         |  |  |  |  |  |

# TABLE 8-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

-n = Value at POR

| Address                 | Name                              | Bit 7       | Bit 6       | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR | Value on<br>all other<br>Resets |

|-------------------------|-----------------------------------|-------------|-------------|---------|---------|---------|--------|---------|---------|-----------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON                            | GIE         | PEIE        | TOIE    | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x       | 0000 000u                       |

| 0Ch                     | PIR1                              | EEIF        | CMIF        | RCIF    | TXIF    | 1       | CCP1IF | TMR2IF  | TMR1IF  | 0000 -000       | 0000 -000                       |

| 8Ch                     | PIE1                              | EEIE        | CMIE        | RCIE    | TXIE    | _       | CCP1IE | TMR2IE  | TMR1IE  | 0000 -000       | 0000 -000                       |

| 11h                     | 11h TMR2 Timer2 Module's Register |             |             |         |         |         |        |         |         |                 | 0000 0000                       |

| 12h                     | T2CON                             | _           | TOUTPS3     | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000       | -000 0000                       |

| 92h                     | PR2                               | Timer2 Peri | od Register |         |         |         |        |         |         | 1111 1111       | 1111 1111                       |

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

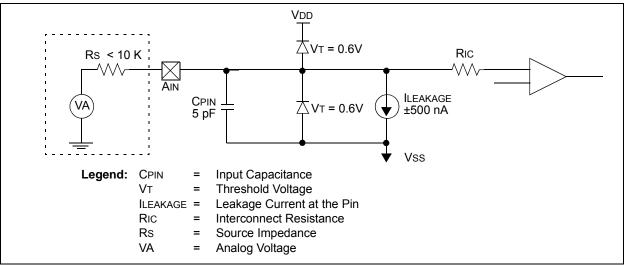

## FIGURE 10-4: ANALOG INPUT MODE

| Address                 | Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>Resets |

|-------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 1Fh                     | CMCON  | C2OUT  | C10UT  | C2INV  | C1NV   | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE    | PEIE   | T0IE   | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 0Ch                     | PIR1   | EEIF   | CMIF   | RCIF   | TXIF   | _      | CCP1IF | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                       |

| 8Ch                     | PIE1   | EEIE   | CMIE   | RCIE   | TXIE   | _      | CCP1IE | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                       |

| 85h                     | TRISA  | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

**Legend:** x = Unknown, u = Unchanged, - = Unimplemented, read as '0'

| BAUD     | Fosc = 20 MHz |        | SPBRG | 16 MHz |                    | SPBRG | 10 MHz |                    | SPBRG |

|----------|---------------|--------|-------|--------|--------------------|-------|--------|--------------------|-------|

| RATE (K) | KBAUD         | ERROR  |       |        | value<br>(decimal) | KBAUD | ERROR  | value<br>(decimal) |       |

| 0.3      | NA            | _      | _     | NA     | _                  | _     | NA     | _                  | _     |

| 1.2      | NA            | _      | _     | NA     | _                  | _     | NA     | _                  | —     |

| 2.4      | NA            | _      | _     | NA     | _                  | _     | NA     | _                  | _     |

| 9.6      | NA            | _      | _     | NA     | _                  | _     | 9.766  | +1.73%             | 255   |

| 19.2     | 19.53         | +1.73% | 255   | 19.23  | +0.16%             | 207   | 19.23  | +0.16%             | 129   |

| 76.8     | 76.92         | +0.16% | 64    | 76.92  | +0.16%             | 51    | 75.76  | -1.36%             | 32    |

| 96       | 96.15         | +0.16% | 51    | 95.24  | -0.79%             | 41    | 96.15  | +0.16%             | 25    |

| 300      | 294.1         | -1.96  | 16    | 307.69 | +2.56%             | 12    | 312.5  | +4.17%             | 7     |

| 500      | 500           | 0      | 9     | 500    | 0                  | 7     | 500    | 0                  | 4     |

| HIGH     | 5000          | _      | 0     | 4000   | _                  | 0     | 2500   | _                  | 0     |

| LOW      | 19.53         | _      | 255   | 15.625 | _                  | 255   | 9.766  |                    | 255   |

# TABLE 12-3: BAUD RATES FOR SYNCHRONOUS MODE

| BAUD     | Fosc = 7.15909 MHz |        | SPBRG              | 5.0688 MHz |        |                    | SPBRG  |        |                    |

|----------|--------------------|--------|--------------------|------------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD              | ERROR  | value<br>(decimal) | KBAUD      | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 0.3      | NA                 |        | _                  | NA         |        | _                  | NA     | _      | _                  |

| 1.2      | NA                 | _      | _                  | NA         | _      | _                  | NA     | _      | _                  |

| 2.4      | NA                 | _      | _                  | NA         | _      | _                  | NA     | _      | _                  |

| 9.6      | 9.622              | +0.23% | 185                | 9.6        | 0      | 131                | 9.615  | +0.16% | 103                |

| 19.2     | 19.24              | +0.23% | 92                 | 19.2       | 0      | 65                 | 19.231 | +0.16% | 51                 |

| 76.8     | 77.82              | +1.32  | 22                 | 79.2       | +3.13% | 15                 | 75.923 | +0.16% | 12                 |

| 96       | 94.20              | -1.88  | 18                 | 97.48      | +1.54% | 12                 | 1000   | +4.17% | 9                  |

| 300      | 298.3              | -0.57  | 5                  | 316.8      | 5.60%  | 3                  | NA     |        | _                  |

| 500      | NA                 | _      | _                  | NA         | _      | _                  | NA     | _      | _                  |

| HIGH     | 1789.8             |        | 0                  | 1267       |        | 0                  | 100    |        | 0                  |

| LOW      | 6.991              | _      | 255                | 4.950      | _      | 255                | 3.906  | _      | 255                |

| BAUD     | Fosc = 3.57 | 9545 MHz | SPBRG              | 1 MHz  |        | SPBRG              | 32.768 kHz |        | SPBRG              |

|----------|-------------|----------|--------------------|--------|--------|--------------------|------------|--------|--------------------|

| RATE (K) | KBAUD       | ERROR    | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) | KBAUD      | ERROR  | value<br>(decimal) |

| 0.3      | NA          | _        | _                  | NA     |        | _                  | 0.303      | +1.14% | 26                 |

| 1.2      | NA          | _        | _                  | 1.202  | +0.16% | 207                | 1.170      | -2.48% | 6                  |

| 2.4      | NA          | —        | —                  | 2.404  | +0.16% | 103                | NA         | _      | _                  |

| 9.6      | 9.622       | +0.23%   | 92                 | 9.615  | +0.16% | 25                 | NA         |        | _                  |

| 19.2     | 19.04       | -0.83%   | 46                 | 19.24  | +0.16% | 12                 | NA         | _      | _                  |

| 76.8     | 74.57       | -2.90%   | 11                 | 83.34  | +8.51% | 2                  | NA         |        | _                  |

| 96       | 99.43       | +3.57%   | 8                  | NA     | _      | _                  | NA         | _      | _                  |

| 300      | 298.3       | 0.57%    | 2                  | NA     | _      | _                  | NA         | _      | _                  |

| 500      | NA          | _        | —                  | NA     | _      | —                  | NA         |        | —                  |

| HIGH     | 894.9       | _        | 0                  | 250    | _      | 0                  | 8.192      | _      | 0                  |

| LOW      | 3.496       | _        | 255                | 0.9766 | _      | 255                | 0.032      |        | 255                |

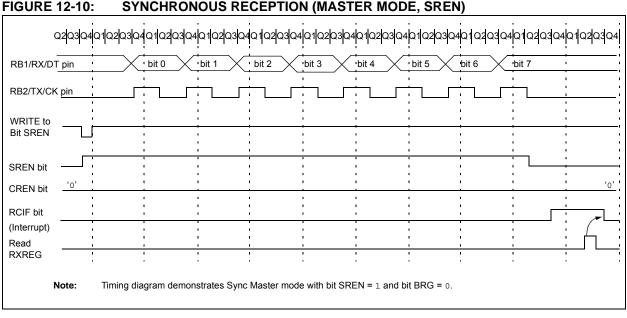

# 12.5 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RB2/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in Sleep mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 12.5.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from Sleep and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Follow these steps when setting up a Synchronous Slave Transmission:

- 1. TRISB<1> and TRISB<2> should both be set to '1' to configure the RB1/RX/DT and RB2/TX/CK pins as inputs. Output drive, when required, is controlled by the peripheral circuitry.

- Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 3. Clear bits CREN and SREN.

- 4. If interrupts are desired, then set enable bit TXIE.

- 5. If 9-bit transmission is desired, then set bit TX9.

- 6. Enable the transmission by setting enable bit TXEN.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 8. Start transmission by loading data to the TXREG register.

#### 12.5.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical except in the case of the Sleep mode. Also, bit SREN is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during Sleep. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Follow these steps when setting up a Synchronous Slave Reception:

- 1. TRISB<1> and TRISB<2> should both be set to '1' to configure the RB1/RX/DT and RB2/TX/CK pins as inputs. Output drive, when required, is controlled by the peripheral circuitry.

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. To enable reception, set enable bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If an OERR error occurred, clear the error by clearing bit CREN.

| IADLE I | ABLE 12-11. REGISTERS ASSOCIATED WITH STINCHRONOUS SLAVE TRANSMISSION |                              |          |         |         |       |        |           |           |                 |                           |

|---------|-----------------------------------------------------------------------|------------------------------|----------|---------|---------|-------|--------|-----------|-----------|-----------------|---------------------------|

| Address | Name                                                                  | Bit 7                        | Bit 6    | Bit 5   | Bit 4   | Bit 3 | Bit 2  | Bit 1     | Bit 0     | Value on<br>POR | Value on all other Resets |

| 0Ch     | PIR1                                                                  | EEIF                         | CMIF     | RCIF    | TXIF    | _     | CCP1IF | TMR2IF    | TMR1IF    | 0000 -000       | 0000 -000                 |

| 18h     | RCSTA                                                                 | SPEN                         | RX9      | SREN    | CREN    | ADEN  | FERR   | OERR      | RX9D      | 0000 000x       | 0000 000x                 |

| 19h     | TXREG                                                                 | USART 1                      | Transmit | Data Re | egister |       |        |           |           | 0000 0000       | 0000 0000                 |

| 8Ch     | PIE1                                                                  | EEIE                         | CMIE     | RCIE    | TXIE    | _     | CCP1IE | TMR2IE    | TMR1IE    | 0000 -000       | 0000 -000                 |

| 98h     | TXSTA                                                                 | CSRC                         | TX9      | TXEN    | SYNC    |       | BRGH   | TRMT      | TX9D      | 0000 -010       | 0000 -010                 |

| 99h     | SPBRG                                                                 | Baud Rate Generator Register |          |         |         |       |        | 0000 0000 | 0000 0000 |                 |                           |

|         |                                                                       |                              |          |         |         |       |        |           |           |                 |                           |

#### TABLE 12-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous slave transmission.

## TABLE 12-12: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address | Name  | Bit 7                        | Bit 6   | Bit 5   | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on all other Resets |

|---------|-------|------------------------------|---------|---------|--------|-------|--------|--------|--------|-----------------|---------------------------|

| 0Ch     | PIR1  | EEIF                         | CMIF    | RCIF    | TXIF   |       | CCP1IF | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                 |

| 18h     | RCSTA | SPEN                         | RX9     | SREN    | CREN   | ADEN  | FERR   | OERR   | RX9D   | 0000 000x       | 0000 000x                 |

| 1Ah     | RCREG | USART F                      | Receive | Data Re | gister |       |        |        |        | 0000 0000       | 0000 0000                 |

| 8Ch     | PIE1  | EEIE                         | CMIE    | RCIE    | TXIE   | _     | CCP1IE | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                 |

| 98h     | TXSTA | CSRC                         | TX9     | TXEN    | SYNC   |       | BRGH   | TRMT   | TX9D   | 0000 -010       | 0000 -010                 |

| 99h     | SPBRG | Baud Rate Generator Register |         |         |        |       |        |        |        | 0000 0000       | 0000 0000                 |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous slave reception.

# 13.8 Data EEPROM Operation During Code-Protect

When the device is code-protected, the CPU is able to read and write data to the data EEPROM.

#### TABLE 13-1: REGISTERS/BITS ASSOCIATED WITH DATA EEPROM

| Address | Name                  | Bit 7                                         | Bit 6                   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other<br>Resets |

|---------|-----------------------|-----------------------------------------------|-------------------------|-------|-------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| 9Ah     | EEDATA                | EEPRO                                         | EEPROM Data Register    |       |       |       |       |       |       | xxxx xxxx                     | uuuu uuuu                       |

| 9Bh     | EEADR                 | EEPRO                                         | EEPROM Address Register |       |       |       |       |       |       | xxxx xxxx                     | uuuu uuuu                       |

| 9Ch     | EECON1                | —                                             | _                       | —     | —     | WRERR | WREN  | WR    | RD    | x000                          | q000                            |

| 9Dh     | EECON2 <sup>(1)</sup> | CON2 <sup>(1)</sup> EEPROM Control Register 2 |                         |       |       |       |       |       |       |                               |                                 |

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by data EEPROM.

**Note 1:** EECON2 is not a physical register.

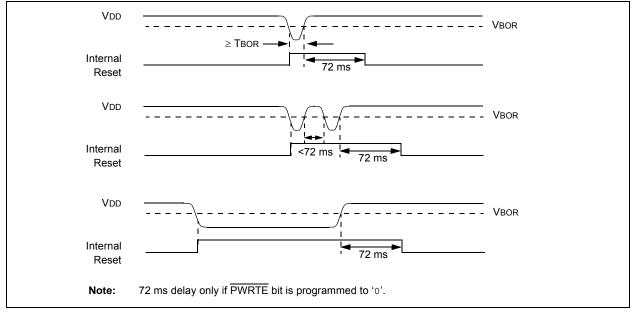

# 14.4 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST) and Brown-out Reset (BOR)

#### 14.4.1 POWER-ON RESET (POR)

The on-chip POR holds the part in Reset until a VDD rise is detected (in the range of 1.2-1.7V). A maximum rise time for VDD is required. See **Section 17.0 "Electrical Specifications"** for details.

The POR circuit does not produce an internal Reset when VDD declines.

When the device starts normal operation (exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure proper operation. If these conditions are not met, the device must be held in Reset via MCLR, BOR or PWRT until the operating conditions are met.

For additional information, refer to Application Note AN607 "*Power-up Trouble Shooting*" (DS00607).

#### 14.4.2 POWER-UP TIMER (PWRT)

The PWRT provides a fixed 72 ms (nominal) time out on power-up (POR) or if enabled from a Brown-out Reset. The PWRT operates on an internal RC oscillator. The chip is kept in Reset as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the PWRT. It is recommended that the PWRT be enabled when Brown-out Reset is enabled.

The power-up time delay will vary from chip-to-chip and due to VDD, temperature and process variation. See DC parameters Table 17-7 for details.

#### 14.4.3 OSCILLATOR START-UP TIMER (OST)

The OST provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. Program execution will not start until the OST time out is complete. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from Sleep. See Table 17-7.

#### 14.4.4 BROWN-OUT RESET (BOR)

The PIC16F627A/628A/648A have on-chip BOR circuitry. A configuration bit, BOREN, can disable (if clear/programmed) or enable (if set) the BOR circuitry. If VDD falls below VBOR for longer than TBOR, the brown-out situation will reset the chip. A Reset is not assured if VDD falls below VBOR for shorter than TBOR. VBOR and TBOR are defined in Table 17-2 and Table 17-7, respectively.

On any Reset (Power-on, Brown-out, Watchdog, etc.), the chip will remain in Reset until VDD rises above VBOR (see Figure 14-7). The Power-up Timer will now be invoked, if enabled, and will keep the chip in Reset an additional 72 ms.

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-Up Timer will execute a 72 ms Reset. Figure 14-7 shows typical brown-out situations.

#### FIGURE 14-7: BROWN-OUT SITUATIONS WITH PWRT ENABLED

NOTES:

| IORLW            | Inclusive OR Literal with W                                                                                              |  |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                 |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                        |  |  |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                             |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                        |  |  |  |  |  |  |  |

| Encoding:        | 11 1000 kkkk kkkk                                                                                                        |  |  |  |  |  |  |  |

| Description:     | The contents of the W register is<br>OR'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                        |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                        |  |  |  |  |  |  |  |

| Example          | IORLW 0x35                                                                                                               |  |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x9A<br>After Instruction<br>W = 0xBF<br>Z = 0                                                 |  |  |  |  |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                    |  |  |  |  |  |  |  |

| MOVLW            | Move Literal to W                                                                                   |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                            |  |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                 |  |  |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                                 |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                |  |  |  |  |  |  |  |

| Encoding:        | 11 00xx kkkk kkkk                                                                                   |  |  |  |  |  |  |  |

| Description:     | The eight bit literal 'k' is loaded<br>into W register. The "don't<br>cares" will assemble as '0's. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                   |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                   |  |  |  |  |  |  |  |

| <u>Example</u>   | MOVLW 0x5A                                                                                          |  |  |  |  |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                                       |  |  |  |  |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                       |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                           |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (dest)                                                                                                                                           |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |  |

| Encoding:        | 00 0100 dfff ffff                                                                                                                                                           |  |  |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result<br>is placed in the W register. If 'd'<br>is '1', the result is placed back in<br>register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                           |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                           |  |  |  |  |  |

| Example          | IORWF REG1, 0                                                                                                                                                               |  |  |  |  |  |

|                  | Before Instruction<br>REG1 = 0x13<br>W = 0x91<br>After Instruction<br>REG1 = 0x13<br>W = 0x93<br>Z = 1                                                                      |  |  |  |  |  |

| MOVF             | Move f                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Encoding:        | 00 1000 dfff ffff                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Description:     | The contents of register 'f' is<br>moved to a destination<br>dependent upon the status of<br>'d'. If $d = 0$ , destination is W<br>register. If $d = 1$ , the destination<br>is file register f itself. $d = 1$ is<br>useful to test a file register since<br>status flag Z is affected. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Example          | MOVF REG1, 0                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                  | After Instruction<br>W= value in REG1 register<br>Z = 1                                                                                                                                                                                                                                  |  |  |  |  |  |  |

# 16.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

# 16.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

# 16.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

# 16.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 16.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB IDE compatibility

# 16.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 16.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 16.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).