Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 224 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f628a-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

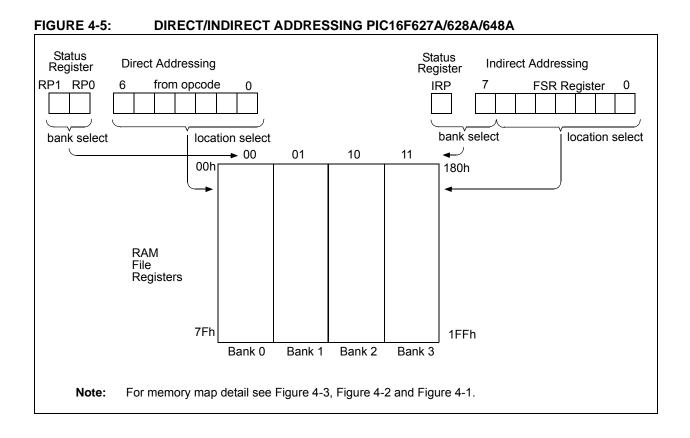

### FIGURE 4-2: DATA MEMORY MAP OF THE PIC16F627A AND PIC16F628A

| direct addr. <sup>(1)</sup> | 00h | Indirect addr. <sup>(1)</sup> | 80h | Indirect addr. <sup>(1)</sup> | 100h | Indirect addr. <sup>(1)</sup> |

|-----------------------------|-----|-------------------------------|-----|-------------------------------|------|-------------------------------|

| TMR0                        | 01h | OPTION                        | 81h | TMR0                          | 101h | OPTION                        |

| PCL                         | 02h | PCL                           | 82h | PCL                           | 102h | PCL                           |

| STATUS                      | 03h | STATUS                        | 83h | STATUS                        | 103h | STATUS                        |

| FSR                         | 04h | FSR                           | 84h | FSR                           | 104h | FSR                           |

| PORTA                       | 05h | TRISA                         | 85h |                               | 105h |                               |

| PORTB                       | 06h | TRISB                         | 86h | PORTB                         | 106h | TRISB                         |

|                             | 07h |                               | 87h |                               | 107h |                               |

|                             | 08h |                               | 88h |                               | 108h |                               |

|                             | 09h |                               | 89h |                               | 109h |                               |

| PCLATH                      | 0Ah | PCLATH                        | 8Ah | PCLATH                        | 10Ah | PCLATH                        |

| INTCON                      | 0Bh | INTCON                        | 8Bh | INTCON                        | 10Bh | INTCON                        |

| PIR1                        | 0Ch | PIE1                          | 8Ch |                               | 10Ch |                               |

|                             | 0Dh |                               | 8Dh |                               | 10Dh |                               |

| TMR1L                       | 0Eh | PCON                          | 8Eh |                               | 10Eh |                               |

| TMR1H                       | 0Fh |                               | 8Fh |                               | 10Fh |                               |

| T1CON                       | 10h |                               | 90h |                               |      |                               |

| TMR2                        | 11h |                               | 91h |                               |      |                               |

| T2CON                       | 12h | PR2                           | 92h |                               |      |                               |

|                             | 13h |                               | 93h |                               |      |                               |

|                             | 14h |                               | 94h |                               |      |                               |

| CCPR1L                      | 15h |                               | 95h |                               |      |                               |

| CCPR1H                      | 16h |                               | 96h |                               |      |                               |

| CCP1CON                     | 17h |                               | 97h |                               |      |                               |

| RCSTA                       | 18h | TXSTA                         | 98h |                               |      |                               |

| TXREG                       | 19h | SPBRG                         | 99h |                               |      |                               |

| RCREG                       | 1Ah | EEDATA                        | 9Ah |                               |      |                               |

|                             | 1Bh | EEADR                         | 9Bh |                               |      |                               |

|                             | 1Ch | EECON1                        | 9Ch |                               |      |                               |

|                             | 1Dh | EECON2 <sup>(1)</sup>         | 9Dh |                               |      |                               |

|                             | 1Eh |                               | 9Eh |                               |      |                               |

| CMCON                       | 1Fh | VRCON                         | 9Fh |                               | 11Fh |                               |

|                             | 20h |                               | A0h | General<br>Purpose            | 120h |                               |

| General                     |     | General                       |     | Register                      |      |                               |

| Purpose<br>Register         |     | Purpose<br>Register           |     | 48 Bytes                      | 14Fh |                               |

| •                           |     | 80 Bytes                      |     |                               | 150h |                               |

| 80 Bytes                    |     |                               |     |                               |      |                               |

|                             | 6Fh |                               | EFh |                               | 16Fh |                               |

| 16 Bytes                    | 70h | accesses                      | F0h | accesses                      | 170h | accesses                      |

| IO Dyles                    |     | 70h-7Fh                       |     | 70h-7Fh                       |      | 70h-7Fh                       |

|                             | 7Fh |                               | FFh |                               | 17Fh |                               |

| Bank 0                      |     | Bank 1                        |     | Bank 2                        |      | Bank 3                        |

| <b>-</b>                    | 4 4 | a memory locations, r         |     | ,                             |      |                               |

### 4.2.2.2 OPTION Register

The Option register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT (PSA = 1). See Section 6.3.1 "Switching Prescaler Assignment".

### **REGISTER 4-2:** OPTION\_REG – OPTION REGISTER (ADDRESS: 81h, 181h)

|         |                        |                                  |               |                  |                              | , , , , , , , , , , , , , , , , , , , , |       |       |

|---------|------------------------|----------------------------------|---------------|------------------|------------------------------|-----------------------------------------|-------|-------|

|         | R/W-1                  | R/W-1                            | R/W-1         | R/W-1            | R/W-1                        | R/W-1                                   | R/W-1 | R/W-1 |

|         | RBPU                   | INTEDG                           | TOCS          | T0SE             | PSA                          | PS2                                     | PS1   | PS0   |

|         | bit 7                  |                                  |               |                  |                              |                                         |       | bit 0 |

| bit 7   | <b>RBPU</b> : PC       | )RTB Pull-up                     | Enable bit    |                  |                              |                                         |       |       |

|         |                        | B pull-ups ar<br>B pull-ups ar   |               | by individual    | port latch valu              | es                                      |       |       |

| bit 6   | INTEDG:                | Interrupt Edg                    | e Select bit  | t                |                              |                                         |       |       |

|         |                        | pt on rising e<br>pt on falling  | 0             |                  |                              |                                         |       |       |

| bit 5   | <b>T0CS</b> : TM       | R0 Clock So                      | urce Selec    | t bit            |                              |                                         |       |       |

|         |                        | tion on RA4/<br>al instruction   |               | •                |                              |                                         |       |       |

| bit 4   | TOSE: TM               | R0 Source E                      | dge Select    | bit              |                              |                                         |       |       |

|         |                        | •                                |               |                  | 4/T0CKI/CMP2<br>4/T0CKI/CMP2 | •                                       |       |       |

| bit 3   | PSA: Pres              | caler Assign                     | ment bit      |                  |                              |                                         |       |       |

|         |                        | aler is assign<br>aler is assign |               |                  | le                           |                                         |       |       |

| bit 2-0 | <b>PS&lt;2:0&gt;</b> : | Prescaler Ra                     | ate Select b  | its              |                              |                                         |       |       |

|         |                        | Bit Value T                      | MR0 Rate      | WDT Rate         |                              |                                         |       |       |

|         | -                      | 000                              | 1:2           | 1:1              |                              |                                         |       |       |

|         |                        | 001<br>010                       | 1:4<br>1:8    | 1:2<br>1:4       |                              |                                         |       |       |

|         |                        | 010                              | 1:16          | 1:8              |                              |                                         |       |       |

|         |                        | 100                              | 1:32          | 1:16             |                              |                                         |       |       |

|         |                        | 101                              | 1:64<br>1:128 | 1 : 32<br>1 : 64 |                              |                                         |       |       |

|         |                        | 110                              | 1.120         | 1 04             |                              |                                         |       |       |

110

1:128

1:64

111

1:256

1:128

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

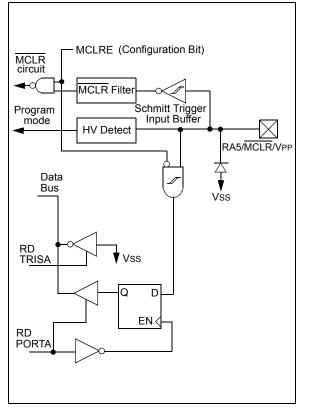

### FIGURE 5-5: BLO<u>CK DIA</u>GRAM OF THE RA5/MCLR/VPP PIN

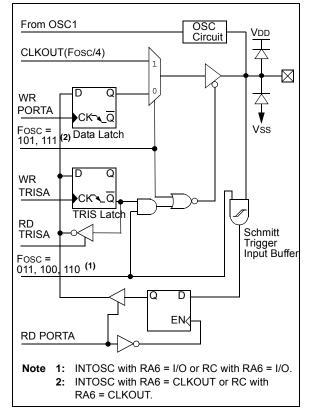

### BLOCK DIAGRAM OF RA6/OSC2/CLKOUT PIN

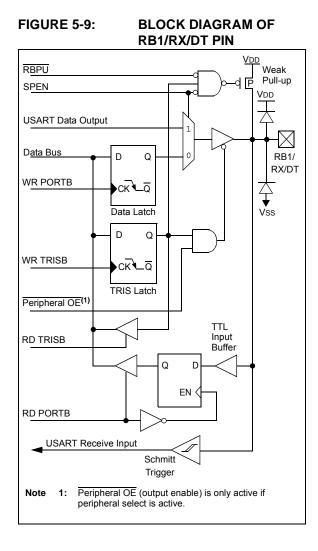

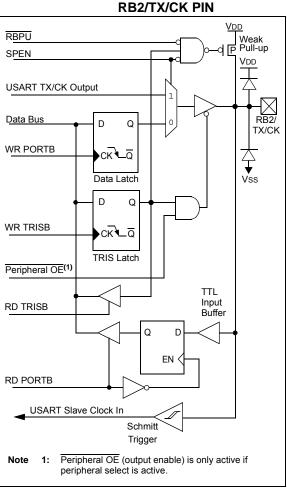

# FIGURE 5-10: BLOCK DIAGRAM OF

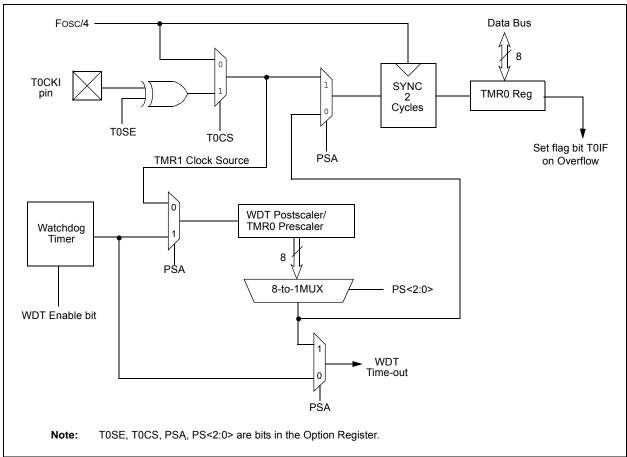

# 6.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Read/write capabilities

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module. Additional information is available in the *"PIC<sup>®</sup> Mid-Range MCU Family Reference Manual"* (DS33023).

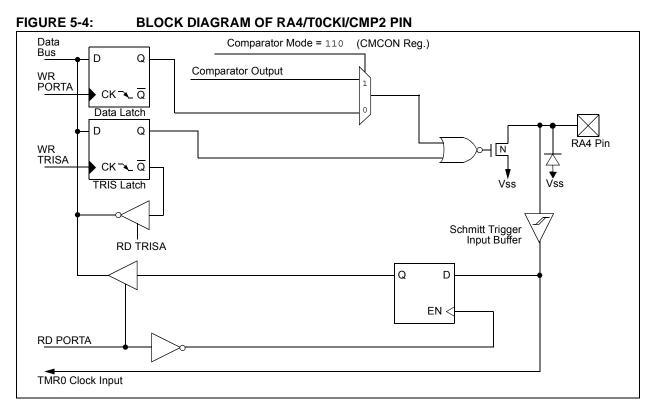

Timer mode is selected by clearing the TOCS bit (OPTION<5>). In Timer mode, the TMR0 register value will increment every instruction cycle (without prescaler). If the TMR0 register is written to, the increment is inhibited for the following two cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit. In this mode the TMR0 register value will increment either on every rising or falling edge of pin RA4/T0CKI/CMP2. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in **Section 6.2 "Using Timer0 with External Clock"**.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4,..., 1:256 are selectable. **Section 6.3 "Timer0 Prescaler**" details the operation of the prescaler.

# 6.1 Timer0 Interrupt

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before reenabling this interrupt. The Timer0 interrupt cannot wake the processor from Sleep since the timer is shut off during Sleep.

# 6.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-1). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device. See Table 17-8.

## 6.3 Timer0 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer. A prescaler assignment for the Timer0 module means that there is no postscaler for the Watchdog Timer, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x...etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

FIGURE 6-1: BLOCK DIAGRAM OF THE TIMER0/WDT

| Address | Name  | Bit 7   | Bit 6                        | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on all other Resets |

|---------|-------|---------|------------------------------|-------|-------|-------|--------|--------|--------|-----------------|---------------------------|

| 0Ch     | PIR1  | EEIF    | CMIF                         | RCIF  | TXIF  | _     | CCP1IF | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                 |

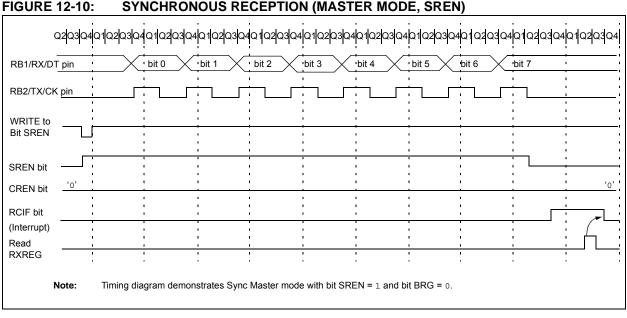

| 18h     | RCSTA | SPEN    | RX9                          | SREN  | CREN  | ADEN  | FERR   | OERR   | RX9D   | 0000 000x       | 0000 000x                 |

| 19h     | TXREG | USART 1 | JSART Transmit Data Register |       |       |       |        |        |        | 0000 0000       | 0000 0000                 |

| 8Ch     | PIE1  | EEIE    | CMIE                         | RCIE  | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                 |

| 98h     | TXSTA | CSRC    | TX9                          | TXEN  | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010       | 0000 -010                 |

| 99h     | SPBRG | Baud Ra | aud Rate Generator Register  |       |       |       |        |        |        | 0000 0000       | 0000 0000                 |

### TABLE 12-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

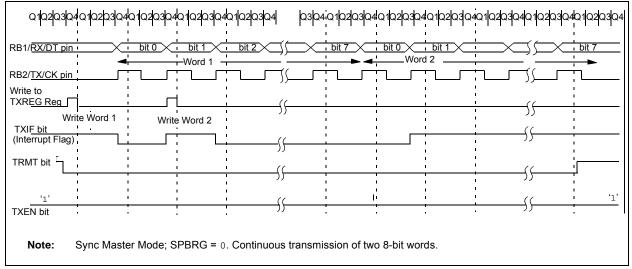

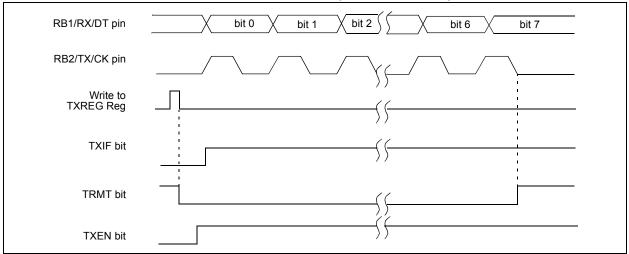

### FIGURE 12-8: SYNCHRONOUS TRANSMISSION

### FIGURE 12-9: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

# 12.5 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RB2/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in Sleep mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

### 12.5.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from Sleep and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Follow these steps when setting up a Synchronous Slave Transmission:

- 1. TRISB<1> and TRISB<2> should both be set to '1' to configure the RB1/RX/DT and RB2/TX/CK pins as inputs. Output drive, when required, is controlled by the peripheral circuitry.

- Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 3. Clear bits CREN and SREN.

- 4. If interrupts are desired, then set enable bit TXIE.

- 5. If 9-bit transmission is desired, then set bit TX9.

- 6. Enable the transmission by setting enable bit TXEN.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 8. Start transmission by loading data to the TXREG register.

### 13.1 EEADR

The PIC16F648A EEADR register addresses 256 bytes of data EEPROM. All eight bits in the register (EEADR<7:0>) are required.

The PIC16F627A/628A EEADR register addresses only the first 128 bytes of data EEPROM so only seven of the eight bits in the register (EEADR<6:0>) are required. The upper bit is address decoded. This means that this bit should always be '0' to ensure that the address is in the 128 byte memory space.

## 13.2 EECON1 and EECON2 Registers

EECON1 is the control register with four low order bits physically implemented. The upper-four bits are non-existent and read as '0's.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a  $\overline{\text{MCLR}}$  Reset or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and rewrite the location. The data and address will be unchanged in the EEDATA and EEADR registers.

Interrupt flag bit EEIF in the PIR1 register is set when write is complete. This bit must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence.

### REGISTER 13-3: EECON1 – EEPROM CONTROL REGISTER 1 (ADDRESS: 9Ch)

| U-0   | U-0 | U-0 | U-0 | R/W-x | R/W-0 | ,<br>R/S-0 | R/S-0 |

|-------|-----|-----|-----|-------|-------|------------|-------|

| 0-0   | 0-0 | 0-0 | 0-0 | 1     | -     |            |       |

| —     | —   |     | —   | WRERR | WREN  | WR         | RD    |

| bit 7 |     |     |     |       |       |            | bit 0 |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                                                                                                             |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | WRERR: EEPROM Error Flag bit                                                                                                                                                                                           |

|         | <ul> <li>1 = A write operation is prematurely terminated (any MCLR Reset, any WDT Reset during<br/>normal operation or BOR Reset)</li> <li>a The write operation completed</li> </ul>                                  |

|         | 0 = The write operation completed                                                                                                                                                                                      |

| bit 2   | WREN: EEPROM Write Enable bit                                                                                                                                                                                          |

|         | <ul> <li>1 = Allows write cycles</li> <li>0 = Inhibits write to the data EEPROM</li> </ul>                                                                                                                             |

| bit 1   | WR: Write Control bit                                                                                                                                                                                                  |

|         | <ul> <li>1 = initiates a write cycle. (The bit is cleared by hardware once write is complete. The WR bit can only be set (not cleared) in software.</li> <li>0 = Write cycle to the data EEPROM is complete</li> </ul> |

| bit 0   | RD: Read Control bit                                                                                                                                                                                                   |

|         | <ul> <li>1 = Initiates an EEPROM read (read takes one cycle. RD is cleared in hardware. The RD bit<br/>can only be set (not cleared) in software).</li> </ul>                                                          |

|         | 0 = Does not initiate an EEPROM read                                                                                                                                                                                   |

|         | [· ·                                                                                                                                                                                                                   |

|         | Legend:                                                                                                                                                                                                                |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented I  | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

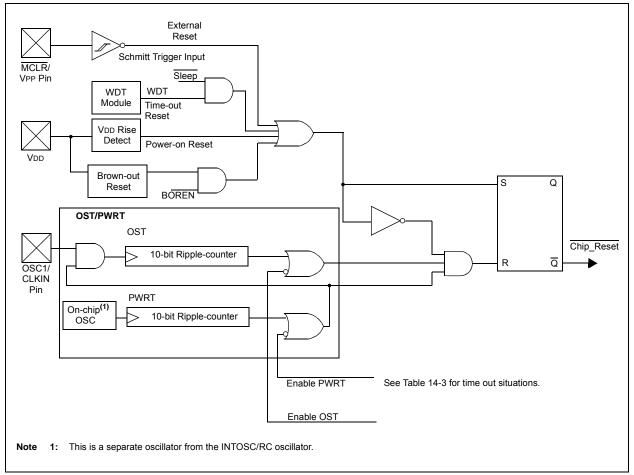

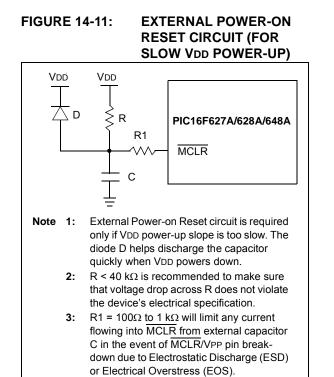

### FIGURE 14-6: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

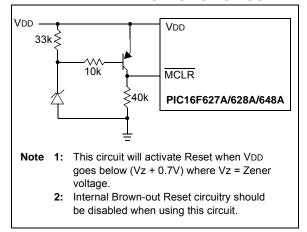

FIGURE 14-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

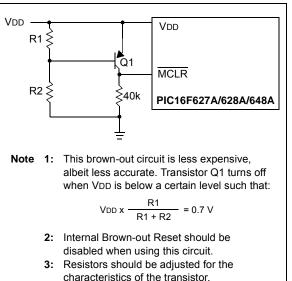

### FIGURE 14-13: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

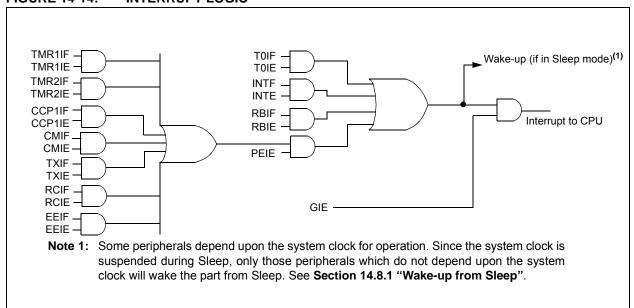

## 14.5 Interrupts

The PIC16F627A/628A/648A has 10 sources of interrupt:

- External Interrupt RB0/INT

- TMR0 Overflow Interrupt

- PORTB Change Interrupts (pins RB<7:4>)

- Comparator Interrupt

- USART Interrupt TX

- USART Interrupt RX

- CCP Interrupt

- TMR1 Overflow Interrupt

- TMR2 Match Interrupt

- Data EEPROM Interrupt

The Interrupt Control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A Global Interrupt Enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on Reset.

The "return-from-interrupt" instruction, RETFIE, exits interrupt routine as well as sets the GIE bit, which reenables RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag is contained in the special register PIR1. The corresponding interrupt enable bit is contained in special registers PIE1.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/ INT recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 14-15). The latency is the same for one or two-cycle instructions. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

### FIGURE 14-14: INTERRUPT LOGIC

| Address                 | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR Reset | Value on all<br>other<br>Resets <sup>(1)</sup> |

|-------------------------|--------|-------|-------|-------|-------|-------|--------|--------|--------|-----------------------|------------------------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE   | PEIE  | TOIE  | INTE  | RBIE  | T0IF   | INTF   | RBIF   | 0000 000x             | 0000 000u                                      |

| 0Ch                     | PIR1   | EEIF  | CMIF  | RCIF  | TXIF  | _     | CCP1IF | TMR2IF | TMR1IF | 0000 -000             | 0000 -000                                      |

| 8Ch                     | PIE1   | EEIE  | CMIE  | RCIE  | TXIE  |       | CCP1IE | TMR2IE | TMR1IE | 0000 -000             | 0000 -000                                      |

TABLE 14-8:SUMMARY OF INTERRUPT REGISTERS

Note 1: Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

## 14.6 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W register and Status register). This must be implemented in software.

Example 14-1 stores and restores the Status and W registers. The user register, W\_TEMP, must be defined in a common memory location (i.e., W\_TEMP is defined at 0x70 in Bank 0 and is therefore, accessible at 0xF0, 0x170 and 0x1F0). The Example 14-1:

- · Stores the W register

- · Stores the Status register

- Executes the ISR code

- Restores the Status (and bank select bit register)

- Restores the W register

#### EXAMPLE 14-1: SAVING THE STATUS AND W REGISTERS IN RAM

| MOVWF            | W_TEMP      | ;copy W to temp register,<br>;could be in any bank   |

|------------------|-------------|------------------------------------------------------|

| SWAPF            | STATUS,W    | ;swap status to be saved<br>;into W                  |

| BCF              | STATUS, RPO | ;change to bank 0<br>;regardless of current<br>;bank |

| MOVWF            | STATUS_TEME | ?;save status to bank 0<br>;register                 |

| :                |             |                                                      |

| :(1              | ISR)        |                                                      |

| :                |             |                                                      |

| SWAPF<br>registe | _           | P,W;swap STATUS_TEMP                                 |

|                  |             | ;into W, sets bank to                                |

| origina          | al          |                                                      |

| MOVWF            | STATUS      | ;state<br>;move W into STATUS<br>;register           |

| SWAPF            | W_TEMP,F    | ;swap W_TEMP                                         |

| SWAPF            | W_TEMP,W    | ;swap W_TEMP into W                                  |

|                  |             |                                                      |

# 14.7 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the CLKIN pin. That means that the WDT will run, even if the clock on the OSC1 and OSC2 pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time out generates a device Reset. If the device is in Sleep mode, a WDT time out causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming the configuration Bits").

### 14.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC Specifications, Table 17-7). If longer timeout periods are desired, a postscaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device Reset.

The  $\overline{\text{TO}}$  bit in the Status register will be cleared upon a Watchdog Timer time out.

### 14.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler) it may take several seconds before a WDT time out occurs.

| XORLW                       | Exclusive OR Literal with W                                                                                                | XORWF                               |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| Syntax:                     | [ <i>label</i> ] XORLW k                                                                                                   | Syntax:                             |

| Operands:                   | $0 \le k \le 255$                                                                                                          | Operands:                           |

| Operation:                  | (W) .XOR. $k \rightarrow (W)$                                                                                              |                                     |

| Status Affected:            | Z                                                                                                                          | Operation:                          |

| Encoding:                   | 11 1010 kkkk kkkk                                                                                                          | Status Affected:                    |

| Description:                | The contents of the W register<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed in<br>the W register. | Encoding:<br>Description:           |

| Words:                      | 1                                                                                                                          |                                     |

| Cycles:<br><u>Example</u> : | 1<br>XORLW  0xAF<br>Before Instruction<br>W = 0xB5<br>After Instruction<br>W = 0x1A                                        | Words:<br>Cycles:<br><u>Example</u> |

| ORWF            | Exclusive OR W with f                                                                                                                                                           |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vntax:          | [ label ] XORWF f,d                                                                                                                                                             |

| perands:        | $0 \le f \le 127$                                                                                                                                                               |

|                 | d ∈ [0,1]                                                                                                                                                                       |

| peration:       | (W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                                              |

| tatus Affected: | Z                                                                                                                                                                               |

| ncoding:        | 00 0110 dfff ffff                                                                                                                                                               |

| escription:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

| /ords:          | 1                                                                                                                                                                               |

| ycles:          | 1                                                                                                                                                                               |

| <u>xample</u>   | XORWF REG1, 1                                                                                                                                                                   |

|                 | Before Instruction                                                                                                                                                              |

|                 | REG1 = 0xAF<br>W = 0xB5                                                                                                                                                         |

|                 | After Instruction                                                                                                                                                               |

|                 | REG1 = 0x1A $W = 0xB5$                                                                                                                                                          |

#### DC Characteristics: PIC16F627A/628A/648A (Industrial, Extended) 17.4 PIC16LF627A/628A/648A (Industrial)

| DC CHA                        | RACTERI | STICS                                                                                                | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |             |                                            |                      |                                                                                                                                                                                                                                                                   |  |  |

|-------------------------------|---------|------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------|--------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param.<br>No.                 | Sym     | Characteristic/Device                                                                                | Min                                                  | Тур†        | Мах                                        | Unit                 | Conditions                                                                                                                                                                                                                                                        |  |  |

|                               | VIL     | Input Low Voltage                                                                                    |                                                      |             |                                            |                      |                                                                                                                                                                                                                                                                   |  |  |

| D030                          |         | I/O ports<br>with TTL buffer                                                                         | Vss<br>Vss                                           | _           | 0.8<br>0.15 Vdd                            | V<br>V               | VDD = 4.5V to 5.5V<br>otherwise                                                                                                                                                                                                                                   |  |  |

| D031<br>D032                  |         | with Schmitt Trigger input <sup>(4)</sup><br>MCLR, RA4/T0CKI,OSC1                                    | VSS<br>VSS<br>VSS                                    | _<br>_<br>_ | 0.15 VDD<br>0.2 VDD<br>0.2 VDD             | V<br>V<br>V          | (Note1)                                                                                                                                                                                                                                                           |  |  |

| D033                          |         | (in RC mode)<br>OSC1 (in HS)<br>OSC1 (in LP and XT)                                                  | Vss<br>Vss                                           | _           | 0.3 Vdd<br>0.6                             | V<br>V               |                                                                                                                                                                                                                                                                   |  |  |

|                               | Vih     | Input High Voltage                                                                                   | •                                                    |             |                                            |                      |                                                                                                                                                                                                                                                                   |  |  |

| D040                          |         | I/O ports<br>with TTL buffer                                                                         | 2.0V<br>.25 VDD + 0.8V                               |             | Vdd<br>Vdd                                 | V<br>V               | VDD = 4.5V to 5.5V<br>otherwise                                                                                                                                                                                                                                   |  |  |

| D041<br>D042<br>D043<br>D043A |         | with Schmitt Trigger input <sup>(4)</sup><br>MCLR RA4/T0CKI<br>OSC1 (XT and LP)<br>OSC1 (in RC mode) | 0.8 VDD<br>0.8 VDD<br>1.3<br>0.9 VDD                 |             | VDD<br>VDD<br>VDD<br>VDD                   | V<br>V<br>V<br>V     | (Note1)                                                                                                                                                                                                                                                           |  |  |

| D043B                         |         | OSC1 (in HS mode)                                                                                    | 0.7 Vdd                                              |             | Vdd                                        | V                    | · ,                                                                                                                                                                                                                                                               |  |  |

| D070                          | IPURB   | PORTB weak pull-up<br>current                                                                        | 50                                                   | 200         | 400                                        | μA                   | VDD = 5.0V, VPIN = VSS                                                                                                                                                                                                                                            |  |  |

|                               | ١L      | Input Leakage Current <sup>(2), (3)</sup>                                                            |                                                      |             |                                            |                      |                                                                                                                                                                                                                                                                   |  |  |

| D060<br>D061<br>D063          |         | I/O ports (Except PORTA)<br>PORTA <sup>(4)</sup><br>RA4/T0CKI<br>OSC1, MCLR                          | <br>                                                 |             | $\pm 1.0 \\ \pm 0.5 \\ \pm 1.0 \\ \pm 5.0$ | μΑ<br>μΑ<br>μΑ<br>μΑ | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \ pin \ at \ high-impedance \\ VSS \leq VPIN \leq VDD, \ pin \ at \ high-impedance \\ VSS \leq VPIN \leq VDD \\ VSS \leq VPIN \leq VDD, \ XT, \ HS \ and \ LP \\ oscillator \ configuration \end{array}$ |  |  |

|                               | Vol     | Output Low Voltage                                                                                   |                                                      |             |                                            |                      |                                                                                                                                                                                                                                                                   |  |  |

| D080                          |         | I/O ports <sup>(4)</sup>                                                                             |                                                      | _           | 0.6<br>0.6                                 | V<br>V               | IOL = 8.5 mA, VDD = 4.5 V, -40° to +85°C<br>IOL = 7.0 mA, VDD = 4.5 V, +85° to<br>+125°C                                                                                                                                                                          |  |  |

|                               | Voн     | Output High Voltage <sup>(3)</sup>                                                                   |                                                      |             |                                            |                      | •                                                                                                                                                                                                                                                                 |  |  |

| D090                          |         | I/O ports (Except RA4 <sup>(4)</sup> )                                                               | VDD - 0.7<br>VDD - 0.7                               | _           | _                                          | V<br>V               | IOH = -3.0 mA, VDD = 4.5 V, -40° to +85°C<br>IOH = -2.5 mA, VDD = 4.5 V, +85° to<br>+125°C                                                                                                                                                                        |  |  |

| D150                          | Vod     | Open-Drain High Voltage                                                                              | —                                                    | —           | 8.5*                                       | V                    | RA4 pin PIC16F627A/628A/648A,<br>PIC16LF627A/628A/648A                                                                                                                                                                                                            |  |  |

|                               |         | Capacitive Loading Specs on Output Pins                                                              |                                                      |             |                                            |                      |                                                                                                                                                                                                                                                                   |  |  |

| D100*                         | COSC2   | OSC2 pin                                                                                             | _                                                    | _           | 15                                         | pF                   | In XT, HS and LP modes when external<br>clock used to drive OSC1.                                                                                                                                                                                                 |  |  |

| D101*                         | Cio     | All I/O pins/OSC2 (in RC mode)                                                                       | not tested.                                          | —           | 50                                         | pF                   | 1                                                                                                                                                                                                                                                                 |  |  |

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC16F627A/628A/648A be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

4: Includes OSC1 and OSC2 when configured as I/O pins, CLKIN or CLKOUT.

| Parameter<br>No. | Sym     | Characteristic                              | Min  | Тур | Max  | Units | Conditions                                                                                                                                                              |

|------------------|---------|---------------------------------------------|------|-----|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F10              | Fiosc   | Oscillator Center frequency                 | _    | 4   | _    | MHz   |                                                                                                                                                                         |

| F13              | ∆losc   | Oscillator Accuracy                         | 3.96 | 4   | 4.04 | MHz   | VDD = 3.5 V, 25°C                                                                                                                                                       |

|                  |         |                                             | 3.92 | 4   | 4.08 | MHz   | $2.0V \le VDD \le 5.5V$<br>$0^{\circ}C \le TA \le +85^{\circ}C$                                                                                                         |

|                  |         |                                             | 3.80 | 4   | 4.20 | MHz   | $\begin{array}{l} 2.0V \leq VDD \leq 5.5V \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ (IND)} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ (EXT)} \end{array}$ |

| F14 <sup>*</sup> | TIOSCST | Oscillator Wake-up from Sleep start-up time |      | 6   | 8    | μS    | VDD = 2.0V, -40°C to +85°C                                                                                                                                              |

|                  |         |                                             |      | 4   | 6    | μS    | VDD = 3.0V, -40°C to +85°C                                                                                                                                              |

|                  |         |                                             |      | 3   | 5    | μS    | VDD = 5.0V, -40°C to +85°C                                                                                                                                              |

TABLE 17-5: PRECISION INTERNAL OSCILLATOR PARAMETERS

Legend: TBD = To Be Determined.

\* Characterized but not tested.

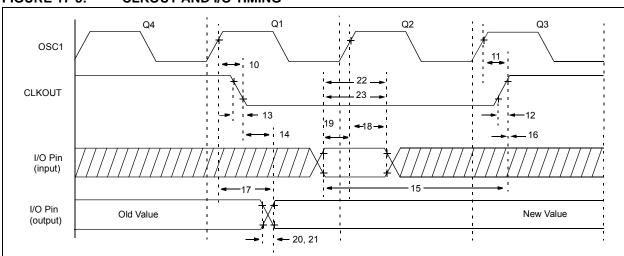

### FIGURE 17-5: CLKOUT AND I/O TIMING

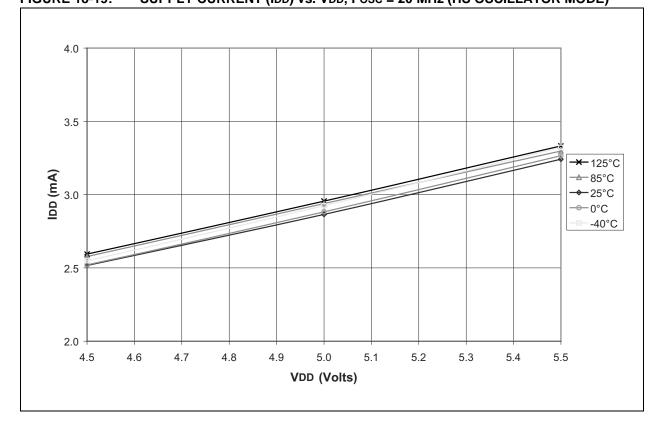

FIGURE 18-19: SUPPLY CURRENT (IDD) vs. VDD, FOSC = 20 MHz (HS OSCILLATOR MODE)

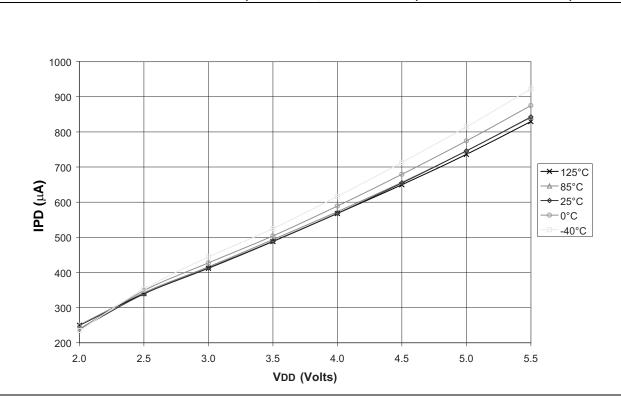

FIGURE 18-18: SUPPLY CURRENT (IDD vs. VDD, Fosc = 4 MHz (XT OSCILLATOR MODE)

# **19.0 PACKAGING INFORMATION**

# **19.1 Package Marking Information**

### 18-Lead PDIP

### 20-Lead SSOP

### 28-Lead QFN

Example

# Example

### Example

### Example

| Legend: | XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                                   | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| l       | In the event the full Microchip part number cannot be marked on one line, it w<br>be carried over to the next line, thus limiting the number of availab<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                |