Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 224 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f628a-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                  | Function | Input Type | Output Type                           | Description                                                                                                                                              |  |

|-------------------------------------------------------|----------|------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RB4/PGM                                               | RB4      | TTL        | CMOS                                  | Bidirectional I/O port. Interrupt-on-pin change.<br>Can be software programmed for internal<br>weak pull-up.                                             |  |

|                                                       | PGM      | ST         | _                                     | Low-voltage programming input pin. When<br>low-voltage programming is enabled, the<br>interrupt-on-pin change and weak pull-up<br>resistor are disabled. |  |

| RB5                                                   | RB5      | TTL        | CMOS                                  | Bidirectional I/O port. Interrupt-on-pin change.<br>Can be software programmed for internal<br>weak pull-up.                                             |  |

| RB6/T1OSO/T1CKI/PGC                                   | RB6      | TTL        | CMOS                                  | Bidirectional I/O port. Interrupt-on-pin change<br>Can be software programmed for internal<br>weak pull-up.                                              |  |

|                                                       | T10S0    | —          | XTAL                                  | Timer1 oscillator output                                                                                                                                 |  |

|                                                       | T1CKI    | ST         | —                                     | Timer1 clock input                                                                                                                                       |  |

|                                                       | PGC      | ST         | —                                     | ICSP™ programming clock                                                                                                                                  |  |

| RB7/T1OSI/PGD                                         | RB7      | TTL        | CMOS                                  | Bidirectional I/O port. Interrupt-on-pin change.<br>Can be software programmed for internal<br>weak pull-up.                                             |  |

|                                                       | T10SI    | XTAL       | _                                     | Timer1 oscillator input                                                                                                                                  |  |

|                                                       | PGD      | ST         | CMOS                                  | ICSP data I/O                                                                                                                                            |  |

| Vss                                                   | Vss      | Power      | —                                     | Ground reference for logic and I/O pins                                                                                                                  |  |

| Vdd                                                   | Vdd      | Power      | —                                     | Positive supply for logic and I/O pins                                                                                                                   |  |

| Legend: O = Output<br>— = Not used<br>TTL = TTL Input |          | l = Ir     | MOS Output<br>iput<br>ipen Drain Outj | P = Power<br>ST = Schmitt Trigger Input<br>AN = Analog                                                                                                   |  |

## TABLE 3-2: PIC16F627A/628A/648A PINOUT DESCRIPTION (CONTINUED)

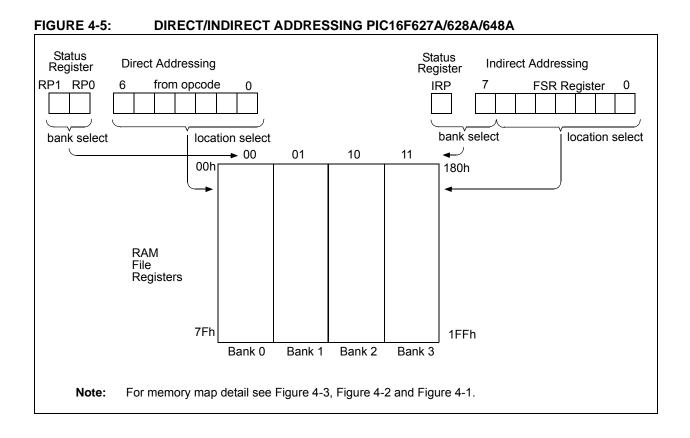

### 4.2.2 SPECIAL FUNCTION REGISTERS

The SFRs are registers used by the CPU and Peripheral functions for controlling the desired operation of the device (Table 4-3). These registers are static RAM.

The special registers can be classified into two sets (core and peripheral). The SFRs associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address | Name    | Bit 7      | Bit 6                                                                       | Bit 5         | Bit 4          | Bit 3          | Bit 2         | Bit 1      | Bit 0   | Value on<br>POR<br>Reset <sup>(1)</sup> | Details<br>on Page |

|---------|---------|------------|-----------------------------------------------------------------------------|---------------|----------------|----------------|---------------|------------|---------|-----------------------------------------|--------------------|

| Bank 0  |         |            |                                                                             |               | •              |                |               |            |         |                                         |                    |

| 00h     | INDF    | Addressi   | ng this locatio                                                             | al register)  | xxxx xxxx      | 30             |               |            |         |                                         |                    |

| 01h     | TMR0    | Timer0 M   | lodule's Regi                                                               | ster          |                |                |               |            |         | xxxx xxxx                               | 47                 |

| 02h     | PCL     | Program    | Counter's (P                                                                | C) Least Sig  | nificant Byte  |                |               |            |         | 0000 0000                               | 30                 |

| 03h     | STATUS  | IRP        | RP1                                                                         | RP0           | TO             | PD             | Z             | DC         | С       | 0001 1xxx                               | 24                 |

| 04h     | FSR     | Indirect D | Data Memory                                                                 | Address Poi   | nter           | •              | •             |            |         | xxxx xxxx                               | 30                 |

| 05h     | PORTA   | RA7        | RA6                                                                         | RA5           | RA4            | RA3            | RA2           | RA1        | RA0     | xxxx 0000                               | 33                 |

| 06h     | PORTB   | RB7        | RB6                                                                         | RB5           | RB4            | RB3            | RB2           | RB1        | RB0     | xxxx xxxx                               | 38                 |

| 07h     | _       | Unimpler   | nented                                                                      |               |                |                |               |            |         | _                                       | _                  |

| 08h     | _       | Unimpler   | nented                                                                      |               |                |                |               |            |         | -                                       | _                  |

| 09h     | _       | Unimpler   | nented                                                                      |               |                |                |               |            |         | _                                       | _                  |

| 0Ah     | PCLATH  | _          | _                                                                           | _             | Write Buffer   | for upper 5 l  | bits of Progr | am Counter |         | 0 0000                                  | 30                 |

| 0Bh     | INTCON  | GIE        | PEIE                                                                        | T0IE          | INTE           | RBIE           | T0IF          | INTF       | RBIF    | 0000 000x                               | 26                 |

| 0Ch     | PIR1    | EEIF       | CMIF                                                                        | RCIF          | TXIF           | _              | CCP1IF        | TMR2IF     | TMR1IF  | 0000 -000                               | 28                 |

| 0Dh     | _       | Unimpler   | nented                                                                      |               |                |                |               |            |         | _                                       | _                  |

| 0Eh     | TMR1L   | Holding F  | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |               |                |                |               |            |         |                                         | 50                 |

| 0Fh     | TMR1H   | Holding F  | Register for th                                                             | ne Most Sign  | ificant Byte o | f the 16-bit T | MR1 Registe   | er         |         | xxxx xxxx                               | 50                 |

| 10h     | T1CON   | -          | —                                                                           | T1CKPS1       | T1CKPS0        | T1OSCEN        | T1SYNC        | TMR1CS     | TMR10N  | 00 0000                                 | 50                 |

| 11h     | TMR2    | TMR2 M     | odule's Regis                                                               | ter           | •              | •              | •             |            |         | 0000 0000                               | 54                 |

| 12h     | T2CON   | —          | TOUTPS3                                                                     | TOUTPS2       | TOUTPS1        | TOUTPS0        | TMR2ON        | T2CKPS1    | T2CKPS0 | -000 0000                               | 54                 |

| 13h     | _       | Unimpler   | nented                                                                      |               |                |                |               |            |         | _                                       | _                  |

| 14h     | _       | Unimpler   | nented                                                                      |               |                |                |               |            |         | _                                       | _                  |

| 15h     | CCPR1L  | Capture/   | Compare/PW                                                                  | 'M Register ( | LSB)           |                |               |            |         | XXXX XXXX                               | 57                 |

| 16h     | CCPR1H  | Capture/   | Compare/PW                                                                  | 'M Register ( | MSB)           |                |               |            |         | XXXX XXXX                               | 57                 |

| 17h     | CCP1CON | _          | _                                                                           | CCP1X         | CCP1Y          | CCP1M3         | CCP1M2        | CCP1M1     | CCP1M0  | 00 0000                                 | 57                 |

| 18h     | RCSTA   | SPEN       | RX9                                                                         | SREN          | CREN           | ADEN           | FERR          | OERR       | RX9D    | 0000 000x                               | 74                 |

| 19h     | TXREG   | USART 1    | Fransmit Data                                                               | Register      |                |                |               |            |         | 0000 0000                               | 79                 |

| 1Ah     | RCREG   | USART F    | JSART Receive Data Register                                                 |               |                |                |               |            |         | 0000 0000                               | 82                 |

| 1Bh     | —       | Unimpler   | Unimplemented                                                               |               |                |                |               |            |         |                                         | _                  |

| 1Ch     | —       | Unimpler   | Unimplemented —                                                             |               |                |                |               |            |         |                                         | _                  |

| 1Dh     | —       | Unimpler   | Jnimplemented —                                                             |               |                |                |               |            |         |                                         | _                  |

| 1Eh     | _       | Unimpler   | mented                                                                      |               |                |                |               |            |         | —                                       | _                  |

| 1Fh     | CMCON   | C2OUT      | C1OUT                                                                       | C2INV         | C1INV          | CIS            | CM2           | CM1        | CM0     | 0000 0000                               | 63                 |

|  | TABLE 4-3: | SPECIAL REGISTERS SUMMARY BANKO |

|--|------------|---------------------------------|

|--|------------|---------------------------------|

Legend:- = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplementedNote1:For the initialization condition for registers tables, refer to Table 14-6 and Table 14-7.

NOTES:

## 7.3 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 7.3.2 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | In Asynchronous Counter mode, Timer1      |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|

|       | cannot be used as a time base for capture |  |  |  |  |  |

|       | or compare operations.                    |  |  |  |  |  |

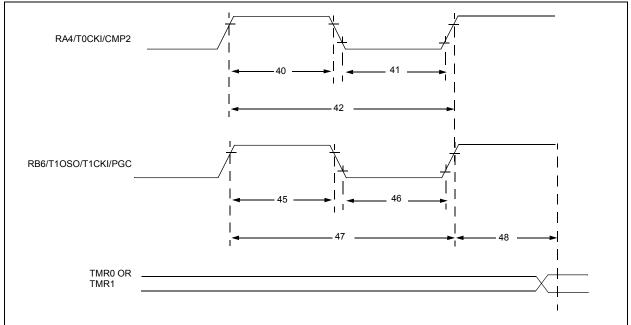

#### 7.3.1 EXTERNAL CLOCK INPUT TIMING WITH UNSYNCHRONIZED CLOCK

If control bit  $\overline{\text{T1SYNC}}$  is set, the timer will increment completely asynchronously. The input clock must meet certain minimum high and low time requirements. Refer to Table 17-8 in the Electrical Specifications Section, timing parameters 45, 46 and 47.

#### 7.3.2 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading the TMR1H or TMR1L register, while the timer is running from an external asynchronous clock, will produce a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself poses certain problems since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Example 7-1 is an example routine to read the 16-bit timer value. This is useful if the timer cannot be stopped.

#### EXAMPLE 7-1: READING A 16-BIT FREE-RUNNING TIMER

|   | All inte | rrupts are d | lisabled                |

|---|----------|--------------|-------------------------|

| , | MOVF     | TMR1H, W     |                         |

|   | MOVWF    |              | , kedd high byte        |

|   |          |              |                         |

|   | MOVF     | ,            | ;Read low byte          |

|   | MOVWF    | TMPL         | ;                       |

|   | MOVF     | TMR1H, W     | ;Read high byte         |

|   | SUBWF    | TMPH, W      | ;Sub 1st read with      |

|   |          |              | ;2nd read               |

|   | BTFSC    | STATUS, Z    | ;Is result = 0          |

|   | GOTO     | CONTINUE     | ;Good 16-bit read       |

| ; |          |              |                         |

| ; | TMR1L ma | v have rolle | ed over between the     |

| ; |          | -            | l low bytes. Reading    |

| ' |          | 5            |                         |

| ; | 5        | and low byc  | es now will read a good |

| ; | value.   |              |                         |

| ; |          |              |                         |

|   | MOVF     | TMR1H, W     | ;Read high byte         |

|   | MOVWF    | TMPH         | ;                       |

|   | MOVF     | TMR1L, W     | ;Read low byte          |

|   | MOVWF    | TMPL         | i                       |

| ; | Re-enabl | e the Intern | rupts (if required)     |

|   | ONTINUE  |              | ;Continue with your     |

|   |          |              | ; code                  |

|   |          |              | , coue                  |

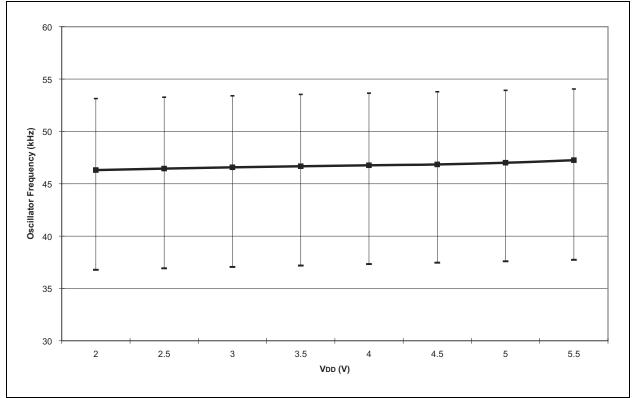

## 7.4 Timer1 Oscillator

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). It will continue to run during Sleep. It is primarily intended for a 32.768 kHz watch crystal. Table 7-1 shows the capacitor selection for the Timer1 oscillator.

The user must provide a software time delay to ensure proper oscillator start-up.

TABLE 7-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Freq       | C1    | C2    |

|------------|-------|-------|

| 32.768 kHz | 15 pF | 15 pF |

**Note:** These values are for design guidance only. Consult Application Note AN826 "*Crystal Oscillator Basics and Crystal Selection for rfPIC*<sup>®</sup> *and PIC*<sup>®</sup> *Devices*" (DS00826) for further information on Crystal/Capacitor Selection.

## 7.5 Resetting Timer1 Using a CCP Trigger Output

If the CCP1 module is configured in Compare mode to generate a "special event trigger" (CCP1M<3:0> = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |    |  |  |  |  |  |

|-------|------------------------------------------|----|--|--|--|--|--|

|       | module will not set interrupt flag b     | it |  |  |  |  |  |

|       | TMR1IF (PIR1<0>).                        |    |  |  |  |  |  |

Timer1 must be configured for either timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

### 7.6 Resetting Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR or any other Reset except by the CCP1 special event triggers (see **Section 9.2.4** "**Special Event Trigger**").

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other Resets, the register is unaffected.

## 7.7 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

#### TABLE 7-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address                 | Name   | Bit 7     | Bit 6                                                                       | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR | Value on<br>all other<br>Resets |

|-------------------------|--------|-----------|-----------------------------------------------------------------------------|---------|---------|---------|--------|--------|-----------|-----------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE       | PEIE                                                                        | TOIE    | INTE    | RBIE    | TOIF   | INTF   | RBIF      | 0000 000x       | 0000 000u                       |

| 0Ch                     | PIR1   | EEIF      | CMIF                                                                        | RCIF    | TXIF    | _       | CCP1IF | TMR2IF | TMR1IF    | 0000 -000       | 0000 -000                       |

| 8Ch                     | PIE1   | EEIE      | CMIE                                                                        | RCIE    | TXIE    |         | CCP1IE | TMR2IE | TMR1IE    | 0000 -000       | 0000 -000                       |

| 0Eh                     | TMR1L  | Holding R | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |         |         |         |        |        |           | XXXX XXXX       | uuuu uuuu                       |

| 0Fh                     | TMR1H  | Holding R | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register  |         |         |         |        |        | XXXX XXXX | uuuu uuuu       |                                 |

| 10h                     | T1CON  | _         | —                                                                           | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N    | 00 0000         | uu uuuu                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer1 module.

NOTES:

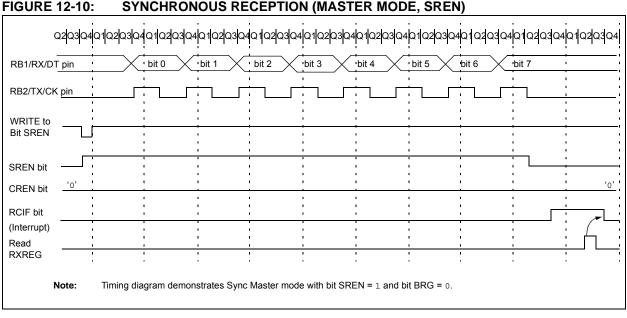

## 12.0 UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART) MODULE

The Universal Synchronous Asynchronous Receiver Transmitter (USART) is also known as a Serial Communications Interface (SCI). The USART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half-duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, Serial EEPROMs, etc. The USART can be configured in the following modes:

- Asynchronous (full-duplex)

- Synchronous Master (half-duplex)

- Synchronous Slave (half-duplex)

Bit SPEN (RCSTA<7>) and bits TRISB<2:1> have to be set in order to configure pins RB2/TX/CK and RB1/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

Register 12-1 shows the Transmit Status and Control Register (TXSTA) and Register 12-2 shows the Receive Status and Control Register (RCSTA).

#### **REGISTER 12-1:** TXSTA – TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS: 98h)

|       | R/W-0                           | R/W-0                            | R/W-0                | R/W-0                          | U-0       | R/W-0 | R-1  | R/W-0 |

|-------|---------------------------------|----------------------------------|----------------------|--------------------------------|-----------|-------|------|-------|

|       | CSRC                            | TX9                              | TXEN                 | SYNC                           | _         | BRGH  | TRMT | TX9D  |

|       | bit 7                           |                                  |                      |                                |           |       |      | bit 0 |

|       |                                 |                                  |                      |                                |           |       |      |       |

| bit 7 | CSRC: Clo                       | ck Source S                      | Select bit           |                                |           |       |      |       |

|       | <u>Asynchron</u><br>Don't ca    |                                  |                      |                                |           |       |      |       |

|       | Synchrono                       | <u>us mode</u>                   |                      |                                |           |       |      |       |

|       |                                 |                                  |                      | ted internally<br>ernal source |           | )     |      |       |

| bit 6 | <b>TX9</b> : 9-bit <sup>-</sup> | Transmit En                      | able bit             |                                |           |       |      |       |

|       |                                 | s 9-bit transr<br>s 8-bit transr |                      |                                |           |       |      |       |

| bit 5 | TXEN: Trai                      | nsmit Enabl                      | e bit <sup>(1)</sup> |                                |           |       |      |       |

|       | 1 = Transm                      |                                  |                      |                                |           |       |      |       |

|       | 0 = Transm                      |                                  |                      |                                |           |       |      |       |

| bit 4 |                                 | ART Mode S                       |                      |                                |           |       |      |       |

|       |                                 | onous mode                       |                      |                                |           |       |      |       |

| bit 3 | •                               | ented: Rea                       |                      |                                |           |       |      |       |

| bit 2 | BRGH: Hig                       | h Baud Rat                       | e Select bit         |                                |           |       |      |       |

|       | Asynchrone                      |                                  |                      |                                |           |       |      |       |

|       | 1 = High<br>0 = Low             |                                  |                      |                                |           |       |      |       |

|       | Synchrono                       |                                  |                      |                                |           |       |      |       |

|       |                                 | in this mode                     | ;                    |                                |           |       |      |       |

| bit 1 | TRMT: Tran                      | nsmit Shift F                    | Register Stat        | us bit                         |           |       |      |       |

|       | 1 = TSR er                      |                                  |                      |                                |           |       |      |       |

|       | 0 = TSR fu                      |                                  |                      |                                |           |       |      |       |

| bit 0 |                                 |                                  |                      | be parity bi                   |           |       |      |       |

|       | Note 1:                         | SREN/CRE                         | EN overrides         | S TXEN in S                    | YNC mode. |       |      |       |

|       |                                 |                                  |                      |                                |           |       |      |       |

|       | Legend:                         |                                  |                      |                                |           |       |      |       |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 12.5 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RB2/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in Sleep mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 12.5.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from Sleep and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Follow these steps when setting up a Synchronous Slave Transmission:

- 1. TRISB<1> and TRISB<2> should both be set to '1' to configure the RB1/RX/DT and RB2/TX/CK pins as inputs. Output drive, when required, is controlled by the peripheral circuitry.

- Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 3. Clear bits CREN and SREN.

- 4. If interrupts are desired, then set enable bit TXIE.

- 5. If 9-bit transmission is desired, then set bit TX9.

- 6. Enable the transmission by setting enable bit TXEN.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 8. Start transmission by loading data to the TXREG register.

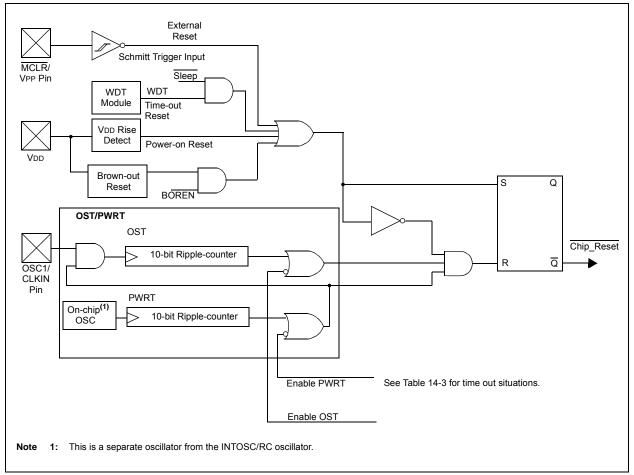

#### FIGURE 14-6: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

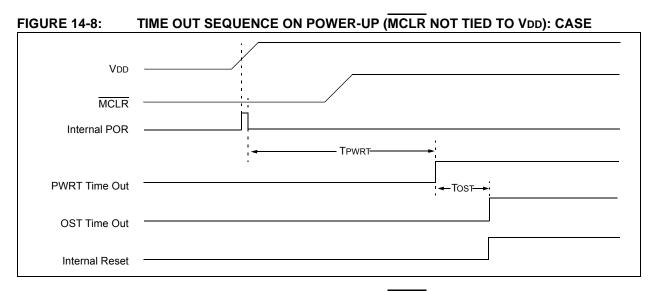

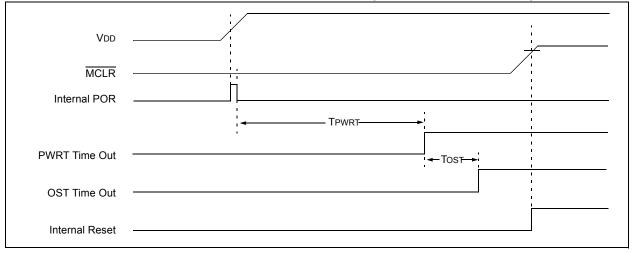

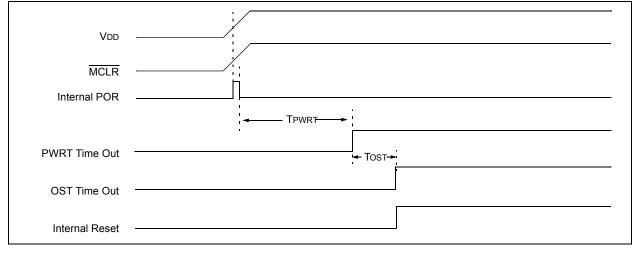

### 14.4 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST) and Brown-out Reset (BOR)

#### 14.4.1 POWER-ON RESET (POR)

The on-chip POR holds the part in Reset until a VDD rise is detected (in the range of 1.2-1.7V). A maximum rise time for VDD is required. See **Section 17.0 "Electrical Specifications"** for details.

The POR circuit does not produce an internal Reset when VDD declines.

When the device starts normal operation (exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure proper operation. If these conditions are not met, the device must be held in Reset via MCLR, BOR or PWRT until the operating conditions are met.

For additional information, refer to Application Note AN607 "*Power-up Trouble Shooting*" (DS00607).

#### 14.4.2 POWER-UP TIMER (PWRT)

The PWRT provides a fixed 72 ms (nominal) time out on power-up (POR) or if enabled from a Brown-out Reset. The PWRT operates on an internal RC oscillator. The chip is kept in Reset as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the PWRT. It is recommended that the PWRT be enabled when Brown-out Reset is enabled.

The power-up time delay will vary from chip-to-chip and due to VDD, temperature and process variation. See DC parameters Table 17-7 for details.

#### 14.4.3 OSCILLATOR START-UP TIMER (OST)

The OST provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. Program execution will not start until the OST time out is complete. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from Sleep. See Table 17-7.

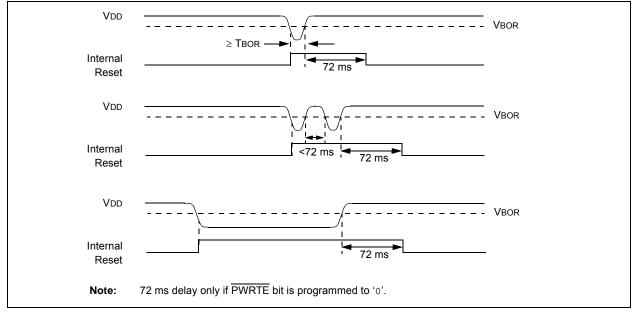

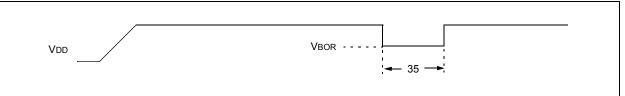

#### 14.4.4 BROWN-OUT RESET (BOR)

The PIC16F627A/628A/648A have on-chip BOR circuitry. A configuration bit, BOREN, can disable (if clear/programmed) or enable (if set) the BOR circuitry. If VDD falls below VBOR for longer than TBOR, the brown-out situation will reset the chip. A Reset is not assured if VDD falls below VBOR for shorter than TBOR. VBOR and TBOR are defined in Table 17-2 and Table 17-7, respectively.

On any Reset (Power-on, Brown-out, Watchdog, etc.), the chip will remain in Reset until VDD rises above VBOR (see Figure 14-7). The Power-up Timer will now be invoked, if enabled, and will keep the chip in Reset an additional 72 ms.

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-Up Timer will execute a 72 ms Reset. Figure 14-7 shows typical brown-out situations.

#### FIGURE 14-7: BROWN-OUT SITUATIONS WITH PWRT ENABLED

#### FIGURE 14-10: TIME OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

1

CLRF

REG1 **Before Instruction**

After Instruction

Ζ

REG1 = 0x5A

REG1 = 0x00= 1

Cycles:

Example

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                                            | CALL             | Call Subroutine                                                                                                                                                                                                                                    |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSS f,b                                                                                                                                                                                                         | Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                            |

| Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                  | Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                               |

|                  | 0 ≤ b < 7                                                                                                                                                                                                                          | Operation:       | (PC)+ 1 $\rightarrow$ TOS,                                                                                                                                                                                                                         |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                                            |                  | $k \rightarrow PC < 10:0>,$                                                                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                               |                  | $(PCLATH<4:3>) \rightarrow PC<12:11>$                                                                                                                                                                                                              |

| Encoding:        | 01 11bb bfff ffff                                                                                                                                                                                                                  | Status Affected: | None                                                                                                                                                                                                                                               |

| Description:     | If bit 'b' in register 'f' is '1', then                                                                                                                                                                                            | Encoding:        | 10 0kkk kkkk kkkk                                                                                                                                                                                                                                  |

|                  | the next instruction is skipped.<br>If bit 'b' is '1', then the next<br>instruction fetched during the<br>current instruction execution, is<br>discarded and a NOP is executed<br>instead, making this a two-cycle<br>instruction. | Description:     | Call Subroutine. First, return<br>address (PC + 1) is pushed onto<br>the stack. The eleven bit imme-<br>diate address is loaded into PC<br>bits <10:0>. The upper bits of<br>the PC are loaded from<br>PCLATH. CALL is a two-cycle<br>instruction. |

| Words:           | 1                                                                                                                                                                                                                                  | \A/a asla -      |                                                                                                                                                                                                                                                    |

| Cycles:          | 1(2)                                                                                                                                                                                                                               | Words:           | 1                                                                                                                                                                                                                                                  |

| <u>Example</u>   | HERE BTFSS REG1<br>FALSE GOTO PROCESS CODE                                                                                                                                                                                         | Cycles:          | 2                                                                                                                                                                                                                                                  |

|                  | FALSE GOTO PROCESS_CODE<br>TRUE                                                                                                                                                                                                    | Example          | HERE CALL THERE<br>Before Instruction<br>PC = Address HERE<br>After Instruction<br>PC = Address THERE<br>TOO                                                                                                                                       |

|                  | After Instruction                                                                                                                                                                                                                  |                  | TOS = Address HERE+1                                                                                                                                                                                                                               |

|                  | if FLAG<1> = 0,<br>PC = address FALSE                                                                                                                                                                                              |                  |                                                                                                                                                                                                                                                    |

|                  | if FLAG<1> = 1,                                                                                                                                                                                                                    | CLRF             | Clear f                                                                                                                                                                                                                                            |

|                  | PC = address TRUE                                                                                                                                                                                                                  | Syntax:          | [ <i>label</i> ] CLRF f                                                                                                                                                                                                                            |

|                  |                                                                                                                                                                                                                                    | Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                                  |

|                  |                                                                                                                                                                                                                                    | Operation:       | $00h \rightarrow (f)$                                                                                                                                                                                                                              |

|                  |                                                                                                                                                                                                                                    |                  | $1 \rightarrow Z$                                                                                                                                                                                                                                  |

|                  |                                                                                                                                                                                                                                    | Status Affected: | Z                                                                                                                                                                                                                                                  |

|                  |                                                                                                                                                                                                                                    | Encoding:        | 00 0001 1fff ffff                                                                                                                                                                                                                                  |

|                  |                                                                                                                                                                                                                                    | Description:     | The contents of register 'f' are cleared and the Z bit is set.                                                                                                                                                                                     |

|                  |                                                                                                                                                                                                                                    | Words:           | 1                                                                                                                                                                                                                                                  |

| SUBWF               | Subtract W from f                                                                                                                                                                           |  |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:             | [label] SUBWF f,d                                                                                                                                                                           |  |  |  |  |  |

| Operands:           | $0 \leq f \leq 127$                                                                                                                                                                         |  |  |  |  |  |

| <b>0</b> <i>1</i>   | d ∈ [0,1]                                                                                                                                                                                   |  |  |  |  |  |

| Operation:          | (f) - (W) $\rightarrow$ (dest)                                                                                                                                                              |  |  |  |  |  |

| Status<br>Affected: | C, DC, Z                                                                                                                                                                                    |  |  |  |  |  |

| Encoding:           | 00 0010 dfff ffff                                                                                                                                                                           |  |  |  |  |  |

| Description:        | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is<br>'0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |  |

| Words:              | 1                                                                                                                                                                                           |  |  |  |  |  |

| Cycles:             | 1                                                                                                                                                                                           |  |  |  |  |  |

| Example 1:          | SUBWF REG1, 1                                                                                                                                                                               |  |  |  |  |  |

|                     | Before Instruction                                                                                                                                                                          |  |  |  |  |  |

|                     | REG1 = 3<br>W = 2<br>C = ?                                                                                                                                                                  |  |  |  |  |  |

|                     | After Instruction                                                                                                                                                                           |  |  |  |  |  |

|                     | REG1 = 1<br>W = 2<br>C = 1; result is positive<br>DC = 1<br>Z = 0                                                                                                                           |  |  |  |  |  |

| Example 2:          | Before Instruction                                                                                                                                                                          |  |  |  |  |  |

|                     | REG1 = 2<br>W = 2                                                                                                                                                                           |  |  |  |  |  |

|                     | C = ?                                                                                                                                                                                       |  |  |  |  |  |

|                     | After Instruction<br>REG1 = 0<br>W = 2<br>C = 1; result is zero<br>Z = DC = 1                                                                                                               |  |  |  |  |  |

| Example 3:          | Before Instruction                                                                                                                                                                          |  |  |  |  |  |

|                     | REG1 = 1<br>W = 2<br>C = ?                                                                                                                                                                  |  |  |  |  |  |

|                     | After Instruction                                                                                                                                                                           |  |  |  |  |  |

|                     | REG1 = 0xFF $W = 2$ $C = 0; result is negative$ $Z = DC = 0$                                                                                                                                |  |  |  |  |  |

| Swap Nibbles in f                                                                                                                                                                  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| [label] SWAPF f,d                                                                                                                                                                  |  |  |  |  |  |

| $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                  |  |  |  |  |  |

| (f<3:0>) → (dest<7:4>),<br>(f<7:4>) → (dest<3:0>)                                                                                                                                  |  |  |  |  |  |

| None                                                                                                                                                                               |  |  |  |  |  |

| 00 1110 dfff ffff                                                                                                                                                                  |  |  |  |  |  |

| The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is<br>'0', the result is placed in W<br>register. If 'd' is '1', the result is<br>placed in register 'f'.     |  |  |  |  |  |

| 1                                                                                                                                                                                  |  |  |  |  |  |

| 1                                                                                                                                                                                  |  |  |  |  |  |

| SWAPF REG1, 0                                                                                                                                                                      |  |  |  |  |  |

| Before Instruction                                                                                                                                                                 |  |  |  |  |  |

| REG1 = 0xA5                                                                                                                                                                        |  |  |  |  |  |

| After Instruction                                                                                                                                                                  |  |  |  |  |  |

| REG1 = 0xA5<br>W = 0x5A                                                                                                                                                            |  |  |  |  |  |

| Load TRIS Register                                                                                                                                                                 |  |  |  |  |  |

| [ <i>label</i> ] TRIS f                                                                                                                                                            |  |  |  |  |  |

| $5 \le f \le 7$                                                                                                                                                                    |  |  |  |  |  |

| (W) $\rightarrow$ TRIS register f;                                                                                                                                                 |  |  |  |  |  |

| None                                                                                                                                                                               |  |  |  |  |  |

| 00 0000 0110 Offf                                                                                                                                                                  |  |  |  |  |  |

| The instruction is supported for<br>code compatibility with the<br>PIC16C5X products. Since TRIS<br>registers are readable and<br>writable, the user can directly<br>address them. |  |  |  |  |  |

| 1                                                                                                                                                                                  |  |  |  |  |  |

| 1                                                                                                                                                                                  |  |  |  |  |  |

|                                                                                                                                                                                    |  |  |  |  |  |

| To maintain upward compatibil-<br>ity with future PIC <sup>®</sup> MCU<br>products, do not use this<br>instruction.                                                                |  |  |  |  |  |

|                                                                                                                                                                                    |  |  |  |  |  |

### 16.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

## 16.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

## 16.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

### 16.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 16.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB IDE compatibility

#### 17.3 DC Characteristics: PIC16F627A/628A/648A (Extended)

| DC CHARACTERISTICSStandard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le Ta \le +125^{\circ}C$ for extended |                                                 |      |       |     |       |            |                                 |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------|-------|-----|-------|------------|---------------------------------|--|

| Param Device Characteristics                                                                                                                            |                                                 |      | _     |     |       | Conditions |                                 |  |

| No.                                                                                                                                                     | Device Characteristics                          | Min† | Тур   | Max | Units | Vdd        | Note                            |  |

| Supply V                                                                                                                                                | oltage (VDD)                                    |      |       |     |       |            |                                 |  |

| D001                                                                                                                                                    | —                                               | 3.0  | _     | 5.5 | V     |            |                                 |  |

| Power-do                                                                                                                                                | own Base Current (IPD)                          |      |       |     |       |            |                                 |  |

| D020E                                                                                                                                                   | —                                               |      | 0.01  | 4   | μA    | 3.0        | WDT, BOR, Comparators, VREF and |  |

|                                                                                                                                                         |                                                 |      | 0.02  | 8   | μA    | 5.0        | T1OSC: disabled                 |  |

| Periphera                                                                                                                                               | al Module Current (∆Iмо <b>D</b> ) <sup>(</sup> | 1)   |       |     |       |            |                                 |  |

| D021E                                                                                                                                                   | —                                               |      | 2     | 9   | μA    | 3.0        | WDT Current                     |  |

| DUZIL                                                                                                                                                   |                                                 | —    | 9     | 20  | μA    | 5.0        |                                 |  |

| D022E                                                                                                                                                   | —                                               |      | 29    | 52  | μA    | 4.5        | BOR Current                     |  |

| DUZZL                                                                                                                                                   |                                                 | —    | 30    | 55  | μA    | 5.0        |                                 |  |

| D023E                                                                                                                                                   | —                                               |      | 22    | 37  | μA    | 3.0        | Comparator Current              |  |

| DUZJE                                                                                                                                                   |                                                 |      | 44    | 68  | μA    | 5.0        | (Both comparators enabled)      |  |

| D024E                                                                                                                                                   | —                                               |      | 50    | 75  | μA    | 3.0        | VREF Current                    |  |

| DUZAL                                                                                                                                                   |                                                 | —    | 83    | 110 | μA    | 5.0        |                                 |  |

| D025E                                                                                                                                                   | —                                               | _    | 1.3   | 4   | μA    | 3.0        | T1OSC Current                   |  |

|                                                                                                                                                         |                                                 |      | 1.8   | 6   | μA    | 5.0        |                                 |  |

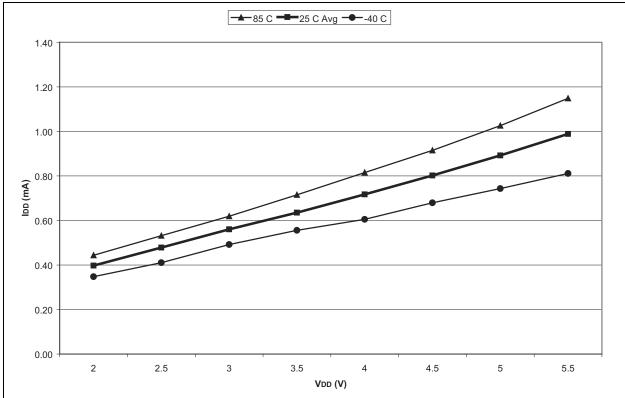

| Supply C                                                                                                                                                | urrent (IDD)                                    | 1    |       |     |       |            |                                 |  |

| D010E                                                                                                                                                   | —                                               |      | 15    | 28  | μA    | 3.0        | Fosc = 32 kHz                   |  |

| DOTOL                                                                                                                                                   |                                                 | —    | 28    | 54  | μA    | 5.0        | LP Oscillator Mode              |  |

| D011E                                                                                                                                                   | —                                               |      | 175   | 340 | μA    | 3.0        | Fosc = 1 MHz                    |  |

| Done                                                                                                                                                    |                                                 | _    | 320   | 520 | μA    | 5.0        | XT Oscillator Mode              |  |

| D012E                                                                                                                                                   | —                                               |      | 450   | 650 | μA    | 3.0        | Fosc = 4 MHz                    |  |

|                                                                                                                                                         |                                                 | —    | 0.710 | 1.1 | mA    | 5.0        | XT Oscillator Mode              |  |

| D012AE                                                                                                                                                  | —                                               |      | 565   | 785 | μA    | 3.0        | Fosc = 4 MHz                    |  |

|                                                                                                                                                         |                                                 | —    | 0.895 | 1.3 | mA    | 5.0        | INTOSC                          |  |

| D013E                                                                                                                                                   | —                                               |      | 2.5   | 2.9 | mA    | 4.5        | Fosc = 20 MHz                   |  |

| DOIDE                                                                                                                                                   |                                                 | —    | 2.75  | 3.5 | mA    | 5.0        | HS Oscillator Mode              |  |

Note 1: The "△" current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement. Max values should be used when calculating total current consumption.

## TABLE 17-1: DC Characteristics: PIC16F627A/628A/648A (Industrial, Extended) PIC16LF627A/628A/648A (Industrial) PIC16LF627A/628A/648A (Industrial)

| DC CHARACTERISTICS |          |                                                                     | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial and<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extendedOperating voltage VDD range as described in DC specification<br>Table 17-2 and Table 17-3 |            |     |            |                                                                                                           |  |

|--------------------|----------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|------------|-----------------------------------------------------------------------------------------------------------|--|

| Parameter<br>No.   | Sym      | Characteristic                                                      | Min                                                                                                                                                                                                                                                                                     | Тур†       | Max | Units      | Conditions                                                                                                |  |

|                    |          | Data EEPROM Memory                                                  |                                                                                                                                                                                                                                                                                         |            |     |            |                                                                                                           |  |

| D120<br>D120A      | ED<br>ED | Endurance<br>Endurance                                              | 100K<br>10K                                                                                                                                                                                                                                                                             | 1M<br>100K | _   | E/W<br>E/W | $\begin{array}{l} -40^\circ C \leq TA \leq 85^\circ C \\ 85^\circ C \leq TA \leq 125^\circ C \end{array}$ |  |

| D121               | Vdrw     | VDD for read/write                                                  | Vmin                                                                                                                                                                                                                                                                                    | _          | 5.5 | V          | VMIN = Minimum operating voltage                                                                          |  |

| D122               | TDEW     | Erase/Write cycle time                                              | —                                                                                                                                                                                                                                                                                       | 4          | 8*  | ms         |                                                                                                           |  |

| D123               | TRETD    | Characteristic Retention                                            | 40                                                                                                                                                                                                                                                                                      |            | —   | Year       | Provided no other<br>specifications are violated                                                          |  |

| D124               | TREF     | Number of Total Erase/Write<br>Cycles before Refresh <sup>(1)</sup> | 1M                                                                                                                                                                                                                                                                                      | 10M        | —   | E/W        | -40°C to +85°C                                                                                            |  |