Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 224 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f628at-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0 General Description                                                     | 7    |

|-----------------------------------------------------------------------------|------|

| 2.0 PIC16F627A/628A/648A Device Varieties                                   | 9    |

| 3.0 Architectural Overview                                                  | . 11 |

| 4.0 Memory Organization                                                     | 17   |

| 5.0 I/O Ports                                                               |      |

| 6.0 Timer0 Module                                                           | 47   |

| 7.0 Timer1 Module                                                           | 50   |

| 8.0 Timer2 Module                                                           | . 54 |

| 9.0 Capture/Compare/PWM (CCP) Module                                        | . 57 |

| 10.0 Comparator Module                                                      | . 63 |

| 11.0 Voltage Reference Module                                               | . 69 |

| 12.0 Universal Synchronous Asynchronous Receiver Transmitter (USART) Module |      |

| 13.0 Data EEPROM Memory                                                     | 91   |

| 14.0 Special Features of the CPU                                            |      |

| 15.0 Instruction Set Summary                                                | 117  |

| 16.0 Development Support                                                    | 131  |

| 17.0 Electrical Specifications                                              | 135  |

| 18.0 DC and AC Characteristics Graphs and Tables                            | 151  |

| 19.0 Packaging Information                                                  | 163  |

| Appendix A: Data Sheet Revision History                                     | 171  |

| Appendix B: Device Differences                                              | 171  |

| Appendix C: Device Migrations                                               | 172  |

| Appendix D: Migrating from other PIC <sup>®</sup> Devices                   | 172  |

| The Microchip Web Site                                                      | 173  |

| Customer Change Notification Service                                        | 173  |

| Customer Support                                                            | 173  |

| Reader Response                                                             |      |

| Product Identification System                                               | 179  |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

- To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# 1.0 GENERAL DESCRIPTION

The PIC16F627A/628A/648A are 18-pin Flash-based members of the versatile PIC16F627A/628A/648A family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers.

All PIC<sup>®</sup> microcontrollers employ an advanced RISC architecture. The PIC16F627A/628A/648A have enhanced core features, an eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single-cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available, complemented by a large register set.

PIC16F627A/628A/648A microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

PIC16F627A/628A/648A devices have integrated features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption.

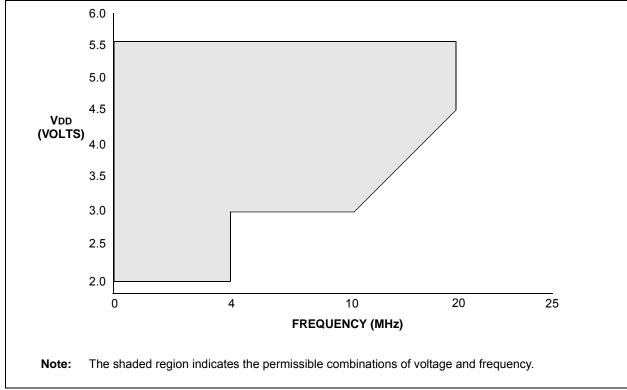

The PIC16F627A/628A/648A has 8 oscillator configurations. The single-pin RC oscillator provides a low-cost solution. The LP oscillator minimizes power consumption, XT is a standard crystal, and INTOSC is a self-contained precision two-speed internal oscillator.

The HS mode is for High-Speed crystals. The EC mode is for an external clock source.

The Sleep (Power-down) mode offers power savings. Users can wake-up the chip from Sleep through several external interrupts, internal interrupts and Resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock-up.

Table 1-1 shows the features of the PIC16F627A/628A/ 648A mid-range microcontroller family.

A simplified block diagram of the PIC16F627A/628A/ 648A is shown in Figure 3-1.

The PIC16F627A/628A/648A series fits in applications ranging from battery chargers to low power remote sensors. The Flash technology makes customizing application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages makes this microcontroller series ideal for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16F627A/628A/648A very versatile.

# 1.1 Development Support

The PIC16F627A/628A/648A family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low cost in-circuit debugger, a low cost development programmer and a full-featured programmer. A Third Party "C" compiler support tool is also available.

|             |                                      | PIC16F627A                                         | PIC16F628A                                         | PIC16F648A                                         | PIC16LF627A                                        | PIC16LF628A                                        | PIC16LF648A                                        |

|-------------|--------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|

| Clock       | Maximum Frequency of Operation (MHz) | 20                                                 | 20                                                 | 20                                                 | 20                                                 | 20                                                 | 20                                                 |

|             | Flash Program<br>Memory (words)      | 1024                                               | 2048                                               | 4096                                               | 1024                                               | 2048                                               | 4096                                               |

| Memory      | RAM Data Memory<br>(bytes)           | 224                                                | 224                                                | 256                                                | 224                                                | 224                                                | 256                                                |

|             | EEPROM Data<br>Memory (bytes)        | 128                                                | 128                                                | 256                                                | 128                                                | 128                                                | 256                                                |

|             | Timer module(s)                      | TMR0, TMR1,<br>TMR2                                |

|             | Comparator(s)                        | 2                                                  | 2                                                  | 2                                                  | 2                                                  | 2                                                  | 2                                                  |

| Peripherals | Capture/Compare/<br>PWM modules      | 1                                                  | 1                                                  | 1                                                  | 1                                                  | 1                                                  | 1                                                  |

|             | Serial Communications                | USART                                              | USART                                              | USART                                              | USART                                              | USART                                              | USART                                              |

|             | Internal Voltage<br>Reference        | Yes                                                | Yes                                                | Yes                                                | Yes                                                | Yes                                                | Yes                                                |

|             | Interrupt Sources                    | 10                                                 | 10                                                 | 10                                                 | 10                                                 | 10                                                 | 10                                                 |

|             | I/O Pins                             | 16                                                 | 16                                                 | 16                                                 | 16                                                 | 16                                                 | 16                                                 |

| Features    | Voltage Range (Volts)                | 3.0-5.5                                            | 3.0-5.5                                            | 3.0-5.5                                            | 2.0-5.5                                            | 2.0-5.5                                            | 2.0-5.5                                            |

|             | Brown-out Reset                      | Yes                                                | Yes                                                | Yes                                                | Yes                                                | Yes                                                | Yes                                                |

|             | Packages                             | 18-pin DIP,<br>SOIC, 20-pin<br>SSOP,<br>28-pin QFN |

TABLE 1-1: PIC16F627A/628A/648A FAMILY OF DEVICES

All PIC<sup>®</sup> family devices have Power-on Reset, selectable Watchdog Timer, selectable code-protect and high I/O current capability. All PIC16F627A/628A/648A family devices use serial programming with clock pin RB6 and data pin RB7.

# 2.0 PIC16F627A/628A/648A DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16F627A/628A/648A Product Identification System, at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

# 2.1 Flash Devices

Flash devices can be erased and re-programmed electrically. This allows the same device to be used for prototype development, pilot programs and production.

A further advantage of the electrically erasable Flash is that it can be erased and reprogrammed in-circuit, or by device programmers, such as Microchip's PICSTART<sup>®</sup> Plus or PRO MATE<sup>®</sup> II programmers.

# 2.2 Quick-Turnaround-Production (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who chose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are standard Flash devices, but with all program locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

# 2.3 Serialized Quick-Turnaround-Production (SQTP<sup>SM</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number, which can serve as an entry-code, password or ID number.

### FIGURE 4-2: DATA MEMORY MAP OF THE PIC16F627A AND PIC16F628A

| direct addr.(1)     | 00h | Indirect addr. <sup>(1)</sup> | 80h | Indirect addr. <sup>(1)</sup> | 100h | Indirect addr. <sup>(1)</sup> |

|---------------------|-----|-------------------------------|-----|-------------------------------|------|-------------------------------|

| TMR0                | 01h | OPTION                        | 81h | TMR0                          | 101h | OPTION                        |

| PCL                 | 02h | PCL                           | 82h | PCL                           | 102h | PCL                           |

| STATUS              | 03h | STATUS                        | 83h | STATUS                        | 103h | STATUS                        |

| FSR                 | 04h | FSR                           | 84h | FSR                           | 104h | FSR                           |

| PORTA               | 05h | TRISA                         | 85h |                               | 105h |                               |

| PORTB               | 06h | TRISB                         | 86h | PORTB                         | 106h | TRISB                         |

|                     | 07h |                               | 87h |                               | 107h |                               |

|                     | 08h |                               | 88h |                               | 108h |                               |

|                     | 09h |                               | 89h |                               | 109h |                               |

| PCLATH              | 0Ah | PCLATH                        | 8Ah | PCLATH                        | 10Ah | PCLATH                        |

| INTCON              | 0Bh | INTCON                        | 8Bh | INTCON                        | 10Bh | INTCON                        |

| PIR1                | 0Ch | PIE1                          | 8Ch |                               | 10Ch |                               |

|                     | 0Dh |                               | 8Dh |                               | 10Dh |                               |

| TMR1L               | 0Eh | PCON                          | 8Eh |                               | 10Eh |                               |

| TMR1H               | 0Fh |                               | 8Fh |                               | 10Fh |                               |

| T1CON               | 10h |                               | 90h |                               |      |                               |

| TMR2                | 11h |                               | 91h |                               |      |                               |

| T2CON               | 12h | PR2                           | 92h |                               |      |                               |

|                     | 13h |                               | 93h |                               |      |                               |

|                     | 14h |                               | 94h |                               |      |                               |

| CCPR1L              | 15h |                               | 95h |                               |      |                               |

| CCPR1H              | 16h |                               | 96h |                               |      |                               |

| CCP1CON             | 17h |                               | 97h |                               |      |                               |

| RCSTA               | 18h | TXSTA                         | 98h |                               |      |                               |

| TXREG               | 19h | SPBRG                         | 99h |                               |      |                               |

| RCREG               | 1Ah | EEDATA                        | 9Ah |                               |      |                               |

|                     | 1Bh | EEADR                         | 9Bh |                               |      |                               |

|                     | 1Ch | EECON1                        | 9Ch |                               |      |                               |

|                     | 1Dh | EECON2 <sup>(1)</sup>         | 9Dh |                               |      |                               |

|                     | 1Eh |                               | 9Eh |                               |      |                               |

| CMCON               | 1Fh | VRCON                         | 9Fh |                               | 11Fh |                               |

|                     | 20h |                               | A0h | General<br>Purpose            | 120h |                               |

| General             |     | General                       |     | Register                      |      |                               |

| Purpose<br>Register |     | Purpose<br>Register           |     | 48 Bytes                      | 14Fh |                               |

| •                   |     | 80 Bytes                      |     |                               | 150h |                               |

| 80 Bytes            |     |                               |     |                               |      |                               |

|                     | 6Fh |                               | EFh |                               | 16Fh |                               |

| 16 Bytes            | 70h | accesses                      | F0h | accesses                      | 170h | accesses                      |

| IO Dyles            |     | 70h-7Fh                       |     | 70h-7Fh                       |      | 70h-7Fh                       |

|                     | 7Fh |                               | FFh |                               | 17Fh |                               |

| Bank 0              |     | Bank 1                        |     | Bank 2                        |      | Bank 3                        |

| <b>-</b>            | 4 4 | a memory locations, r         |     | ,                             |      |                               |

### 4.2.2.6 PCON Register

The PCON register contains flag bits to differentiate between a Power-on Reset, an external MCLR Reset, WDT Reset or a Brown-out Reset.

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if BOR is cleared, indicating a brown-out has occurred. The BOR Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BOREN bit in the Configuration Word).

### REGISTER 4-6:

### PCON – POWER CONTROL REGISTER (ADDRESS: 8Eh)

| U-0   | U-0 | U-0 | U-0 | R/W-1 | U-0 | R/W-0 | R/W-x |

|-------|-----|-----|-----|-------|-----|-------|-------|

| _     | —   | _   | _   | OSCF  |     | POR   | BOR   |

| bit 7 |     |     |     |       |     |       | bit 0 |

- bit 7-4 Unimplemented: Read as '0'

- bit 3 OSCF: INTOSC Oscillator Frequency bit

- 1 = 4 MHz typical

- 0 = 48 kHz typical

- bit 2 Unimplemented: Read as '0'

- bit 1 **POR**: Power-on Reset Status bit

- 1 = No Power-on Reset occurred

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

- bit 0 BOR: Brown-out Reset Status bit

- 1 = No Brown-out Reset occurred

- 0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

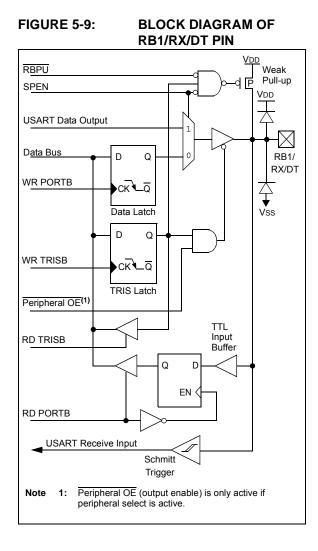

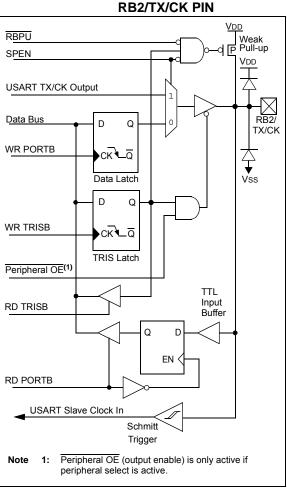

# FIGURE 5-10: BLOCK DIAGRAM OF

# 5.3 I/O Programming Considerations

### 5.3.1 BIDIRECTIONAL I/O PORTS

Any instruction that writes operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit 5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit 5 and PORTB is written to the output latches. If another bit of PORTB is used as a bidirectional I/O pin (e.g., bit 0) and is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit 0 is switched into Output mode later on, the content of the data latch may now be unknown.

Reading a port register reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-2 shows the effect of two sequential read-modify-write instructions (ex.,  ${\tt BCF}, {\tt BSF},$  etc.) on an I/O port

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-OR", "wired-AND"). The resulting high output currents may damage the chip.

### EXAMPLE 5-2: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

| ;Initial PORT settings:     | :PORTB<7:4> Inputs    |

|-----------------------------|-----------------------|

| ;                           | PORTB<3:0> Outputs    |

| ;PORTB<7:6> have extern     | nal pull-up and are   |

| ;not connected to other     | c circuitry           |

| ;                           |                       |

| ;                           | PORT latchPORT Pins   |

|                             |                       |

| BCF STATUS, RPO             | ;                     |

| BCF PORTB, 7                | ;01pp pppp 11pp pppp  |

| BSF STATUS, RPO             | ;                     |

|                             | ;10pp pppp 11pp pppp  |

| BCF TRISB, 6                | ;10pp pppp 10pp pppp  |

| ;                           | , the sets - set fore |

| ,<br>Note that the user may | v have expected the   |

| ; pin values to be 00pp     | -                     |

| ; caused RB7 to be latch    |                       |

| ; (High).                   | ica ab che più value  |

| , (111911).                 |                       |

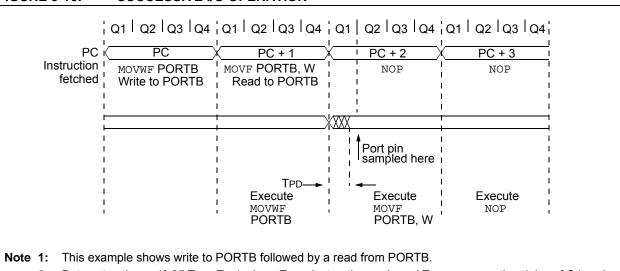

### 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-16). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction, which causes that file to be read into the CPU, is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

2: Data setup time = (0.25 TCY - TPD) where TCY = instruction cycle and TPD = propagation delay of Q1 cycle to output valid. Therefore, at higher clock frequencies, a write followed by a read may be problematic.

# FIGURE 5-16: SUCCESSIVE I/O OPERATION

# 7.3 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 7.3.2 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | In Asynchronous Counter mode, Timer1      |

|-------|-------------------------------------------|

|       | cannot be used as a time base for capture |

|       | or compare operations.                    |

### 7.3.1 EXTERNAL CLOCK INPUT TIMING WITH UNSYNCHRONIZED CLOCK

If control bit  $\overline{\text{T1SYNC}}$  is set, the timer will increment completely asynchronously. The input clock must meet certain minimum high and low time requirements. Refer to Table 17-8 in the Electrical Specifications Section, timing parameters 45, 46 and 47.

### 7.3.2 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading the TMR1H or TMR1L register, while the timer is running from an external asynchronous clock, will produce a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself poses certain problems since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Example 7-1 is an example routine to read the 16-bit timer value. This is useful if the timer cannot be stopped.

### EXAMPLE 7-1: READING A 16-BIT FREE-RUNNING TIMER

|   | All inte | rrupts are d | lisabled                |

|---|----------|--------------|-------------------------|

| , | MOVF     | TMR1H, W     |                         |

|   | MOVWF    |              | , kedd high byte        |

|   |          |              |                         |

|   | MOVF     | ,            | ;Read low byte          |

|   | MOVWF    | TMPL         | ;                       |

|   | MOVF     | TMR1H, W     | ;Read high byte         |

|   | SUBWF    | TMPH, W      | ;Sub 1st read with      |

|   |          |              | ;2nd read               |

|   | BTFSC    | STATUS, Z    | ;Is result = 0          |

|   | GOTO     | CONTINUE     | ;Good 16-bit read       |

| ; |          |              |                         |

| ; | TMR1L ma | v have rolle | ed over between the     |

| ; |          | -            | l low bytes. Reading    |

| ' |          | 5            |                         |

| ; | 5        | and low byc  | es now will read a good |

| ; | value.   |              |                         |

| ; |          |              |                         |

|   | MOVF     | TMR1H, W     | ;Read high byte         |

|   | MOVWF    | TMPH         | ;                       |

|   | MOVF     | TMR1L, W     | ;Read low byte          |

|   | MOVWF    | TMPL         | i                       |

| ; | Re-enabl | e the Intern | rupts (if required)     |

|   | ONTINUE  |              | ;Continue with your     |

|   |          |              | ; code                  |

|   |          |              | , coue                  |

# PIC16F627A/628A/648A

NOTES:

### **REGISTER 14-1: CONFIG – CONFIGURATION WORD REGISTER**

| CP          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _            |           | CPD       | LVP | BOREN    | MCLRE         | FOSC2         | PWRTE    | WDTE        | F0SC1 | F0SC0 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------|-----------|-----|----------|---------------|---------------|----------|-------------|-------|-------|

| bit 13      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |           |           |     |          |               |               |          |             |       | bit 0 |

| bit 13:     | CP: Flash Program Memory Code Protection bit <sup>(2)</sup> (PIC16F648A)         1 = Code protection off         0 = 0000h to 0FFFh code-protected         (PIC16F628A)         1 = Code protection off         0 = 0000h to 07FFh code-protected         (PIC16F627A)         1 = Code protection off         0 = 0000h to 03FFh code-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |           |           |     |          |               |               |          |             |       |       |

| bit 12-9:   | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ted: Read as | ʻ0'       |           |     |          |               |               |          |             |       |       |

| bit 8:      | <b>CPD</b> : Data Code Protection bit <sup>(3)</sup><br>1 = Data memory code protection off<br>0 = Data memory code-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |           |           |     |          |               |               |          |             |       |       |

| bit 7:      | <b>LVP</b> : Low-Voltage Programming Enable bit<br>1 = RB4/PGM pin has PGM functio <u>n, low</u> -voltage programming enabled<br>0 = RB4/PGM is digital I/O, HV on MCLR must be used for programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |           |           |     |          |               |               |          |             |       |       |

| bit 6:      | BOREN: Brown-out Reset Enable bit <sup>(1)</sup><br>1 = BOR Reset enabled<br>0 = BOR Reset disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |           |           |     |          |               |               |          |             |       |       |

| bit 5:      | MCLRE: RA5/MCLR/VPP Pin Function Select bit<br>1 = RA5/MCLR/VPP pin function is MCLR<br>0 = RA5/MCLR/VPP pin function is digital Input, MCLR internally tied to VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |           |           |     |          |               |               |          |             |       |       |

| bit 3:      | <b>PWRTE</b> : Power-up Timer Enable bit <sup>(1)</sup><br>1 = PWRT disabled<br>0 = PWRT enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |           |           |     |          |               |               |          |             |       |       |

| bit 2:      | WDTE: Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |           |           |     |          |               |               |          |             |       |       |

| bit 4, 1-0: | FOSC<2:0>: Oscillator Selection bits <sup>(4)</sup><br>111 = RC oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, Resistor and Capacitor on RA7/OSC1/CLKIN<br>110 = RC oscillator: I/O function on RA6/OSC2/CLKOUT pin, Resistor and Capacitor on RA7/OSC1/CLKIN<br>101 = INTOSC oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN<br>101 = INTOSC oscillator: I/O function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN<br>101 = EC: I/O function on RA6/OSC2/CLKOUT pin, CLKIN on RA7/OSC1/CLKIN<br>101 = HS oscillator: High-speed crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN<br>102 = XT oscillator: Crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN<br>103 = LP oscillator: Low-power crystal on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN |              |           |           |     |          |               |               |          |             |       |       |

|             | <ol> <li>Enabling Brown-out Reset does not automatically enable the Power-up Timer (PWRT) the way it does on the<br/>PIC16F627/628 devices.</li> <li>The code protection scheme has changed from the code protection scheme used on the PIC16F627/628 devices. The<br/>entire Flash program memory needs to be bulk erased to set the CP bit, turning the code protection off. See<br/>"PIC16F627A/628A/648A EEPROM Memory Programming Specification" (DS41196) for details.</li> <li>The entire data EEPROM needs to be bulk erased to set the CPD bit, turning the code protection off. See "PIC16F627A/<br/>628A/648A EEPROM Memory Programming Specification" (DS41196) for details.</li> <li>When MCLR is asserted in INTOSC mode, the internal clock oscillator is disabled.</li> </ol>              |              |           |           |     |          |               |               |          |             |       |       |

|             | Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |           |           |     |          |               |               |          |             |       |       |

|             | R = Readable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | e bit        | W = Wri   | table bit |     | U = Ur   | nimplement    | ted bit, read | d as '0' |             |       |       |

|             | -n = Value at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | POR          | '1' = bit | is set    |     | '0' = bi | it is cleared | l             | x =      | bit is unkn | own   |       |

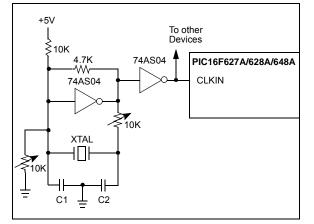

### 14.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used; one with series resonance, or one with parallel resonance.

Figure 14-2 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180° phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This could be used for external oscillator designs.

### FIGURE 14-2: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

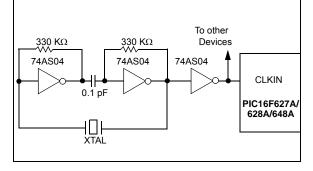

Figure 14-3 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180° phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

### FIGURE 14-3: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

### 14.2.4 PRECISION INTERNAL 4 MHz OSCILLATOR

The internal precision oscillator provides a fixed 4 MHz (nominal) system clock at VDD = 5V and  $25^{\circ}C$ . See **Section 17.0 "Electrical Specifications"**, for information on variation over voltage and temperature.

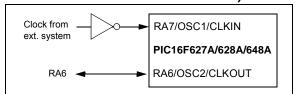

### 14.2.5 EXTERNAL CLOCK IN

For applications where a clock is already available elsewhere, users may directly drive the PIC16F627A/ 628A/648A provided that this external clock source meets the AC/DC timing requirements listed in **Section 17.6 "Timing Diagrams and Specifications"**. Figure 14-4 below shows how an external clock circuit should be configured.

FIGURE 14-4:

### EXTERNAL CLOCK INPUT OPERATION (EC, HS, XT OR LP OSC CONFIGURATION)

### 14.4.5 TIME OUT SEQUENCE

On power-up, the time out sequence is as follows: First PWRT time-out is invoked after POR has expired. Then OST is activated. The total time out will vary based on oscillator configuration and <u>PWRTE</u> bit Status. For example, in RC mode with <u>PWRTE</u> bit set (PWRT disabled), there will be no time out at all. Figure 14-8, Figure 14-11 and Figure 14-12 depict time out sequences.

Since the time outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 14-11). This is useful for testing purposes or to synchronize more than one PIC16F627A/628A/ 648A device operating in parallel.

Table 14-6 shows the Reset conditions for some special registers, while Table 14-7 shows the Reset conditions for all the registers.

### 14.4.6 POWER CONTROL (PCON) STATUS REGISTER

The PCON/Status register, PCON (address 8Eh), has two bits.

Bit 0 is  $\overline{\text{BOR}}$  (Brown-out Reset).  $\overline{\text{BOR}}$  is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if  $\overline{\text{BOR}} = 0$ indicating that a brown-out has occurred. The  $\overline{\text{BOR}}$ Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (by setting BOREN bit = 0 in the Configuration Word).

Bit 1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent Reset if POR is '0', it will indicate that a Power-on Reset must have occurred (VDD may have gone too low).

| Oscillator Configuration | Power-up Timer       |                  | Brown-o              | Wake-up from     |           |

|--------------------------|----------------------|------------------|----------------------|------------------|-----------|

| Oscillator Configuration | <b>PWRTE</b> = 0     | <b>PWRTE</b> = 1 | <b>PWRTE</b> = 0     | <b>PWRTE</b> = 1 | Sleep     |

| XT, HS, LP               | 72 ms +<br>1024•Tosc | 1024•Tosc        | 72 ms +<br>1024•Tosc | 1024•Tosc        | 1024•Tosc |

| RC, EC                   | 72 ms                | —                | 72 ms                | _                | —         |

| INTOSC                   | 72 ms                | —                | 72 ms                | —                | 6 μs      |

| TABLE 14-3. THE OUT IN VARIOUS SITUATIONS | TABLE 14-3: | TIME OUT IN VARIOUS SITUATIONS |

|-------------------------------------------|-------------|--------------------------------|

|-------------------------------------------|-------------|--------------------------------|

# TABLE 14-4: STATUS/PCON BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD | Condition                          |

|-----|-----|----|----|------------------------------------|

| 0   | Х   | 1  | 1  | Power-on Reset                     |

| 0   | Х   | 0  | Х  | Illegal, TO is set on POR          |

| 0   | Х   | Х  | 0  | Illegal, PD is set on POR          |

| 1   | 0   | Х  | Х  | Brown-out Reset                    |

| 1   | 1   | 0  | u  | WDT Reset                          |

| 1   | 1   | 0  | 0  | WDT Wake-up                        |

| 1   | 1   | u  | u  | MCLR Reset during normal operation |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep            |

**Legend:** u = unchanged, x = unknown

| TABLE 14-5:         SUMMARY OF REGISTERS ASSOCIATED WITH BROWN-OUT RESET |  |

|--------------------------------------------------------------------------|--|

|--------------------------------------------------------------------------|--|

| Address                 | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR Reset | Value on all<br>other<br>Resets <sup>(1)</sup> |

|-------------------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|------------------------------------------------|

| 03h, 83h,<br>103h, 183h | STATUS | IRP   | RP1   | RPO   | TO    | PD    | Z     | DC    | С     | 0001 1xxx             | 000q quuu                                      |

| 8Eh                     | PCON   | _     | -     |       |       | OSCF  |       | POR   | BOR   | 1-0x                  | u-uq                                           |

x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Legend:

Shaded cells are not used by Brown-out Reset.

Note 1: Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

#### **INITIALIZATION CONDITION FOR SPECIAL REGISTERS TABLE 14-6:**

| Condition                          | Program<br>Counter    | Status<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 1-0x             |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | 1-uu             |

| MCLR Reset during Sleep            | 000h                  | 0001 0uuu          | 1-uu             |

| WDT Reset                          | 000h                  | 0000 uuuu          | 1-uu             |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | u-uu             |

| Brown-out Reset                    | 000h                  | 000x xuuu          | 1-u0             |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | u-uu             |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'. **Note 1:** When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

# PIC16F627A/628A/648A

NOTES:

| Mnem     | onic, | Description                  | Cycles           |        | 14-Bit | Opcode | Status | N        |         |

|----------|-------|------------------------------|------------------|--------|--------|--------|--------|----------|---------|

| Operands |       | Description                  |                  | MSb    |        |        | LSb    | Affected | Notes   |

|          |       | BYTE-ORIENTED FILE F         | REGISTER OPER    | RATION | IS     |        |        |          |         |

| ADDWF    | f, d  | Add W and f                  | 1                | 00     | 0111   | dfff   | ffff   | C,DC,Z   | 1, 2    |

| ANDWF    | f, d  | AND W with f                 | 1                | 00     | 0101   | dfff   | ffff   | Z        | 1, 2    |

| CLRF     | f     | Clear f                      | 1                | 00     | 0001   | lfff   | ffff   | Z        | 2       |

| CLRW     | _     | Clear W                      | 1                | 00     | 0001   | 0xxx   | xxxx   | Z        |         |

| COMF     | f, d  | Complement f                 | 1                | 00     | 1001   | dfff   | ffff   | Z        | 1, 2    |

| DECF     | f, d  | Decrement f                  | 1                | 00     | 0011   | dfff   | ffff   | Z        | 1, 2    |

| DECFSZ   | f, d  | Decrement f, Skip if 0       | 1 <sup>(2)</sup> | 00     | 1011   | dfff   | ffff   |          | 1, 2, 3 |

| INCF     | f, d  | Increment f                  | 1                | 00     | 1010   | dfff   | ffff   | Z        | 1, 2    |

| INCFSZ   | f, d  | Increment f, Skip if 0       | 1 <sup>(2)</sup> | 00     | 1111   | dfff   | ffff   |          | 1, 2, 3 |

| IORWF    | f, d  | Inclusive OR W with f        | 1                | 00     | 0100   | dfff   | ffff   | Z        | 1, 2    |

| MOVF     | f, d  | Move f                       | 1                | 00     | 1000   | dfff   | ffff   | Z        | 1, 2    |

| MOVWF    | f     | Move W to f                  | 1                | 00     | 0000   | lfff   | ffff   |          |         |

| NOP      | —     | No Operation                 | 1                | 00     | 0000   | 0xx0   | 0000   |          |         |

| RLF      | f, d  | Rotate Left f through Carry  | 1                | 00     | 1101   | dfff   | ffff   | С        | 1, 2    |

| RRF      | f, d  | Rotate Right f through Carry | 1                | 00     | 1100   | dfff   | ffff   | С        | 1, 2    |

| SUBWF    | f, d  | Subtract W from f            | 1                | 00     | 0010   | dfff   | ffff   | C,DC,Z   | 1, 2    |

| SWAPF    | f, d  | Swap nibbles in f            | 1                | 00     | 1110   | dfff   | ffff   |          | 1, 2    |

| XORWF    | f, d  | Exclusive OR W with f        | 1                | 00     | 0110   | dfff   | ffff   | Z        | 1, 2    |

|          |       | BIT-ORIENTED FILE R          | EGISTER OPER     | ATIONS | 3      |        |        |          |         |

| BCF      | f, b  | Bit Clear f                  | 1                | 01     | 00bb   | bfff   | ffff   |          | 1, 2    |

| BSF      | f, b  | Bit Set f                    | 1                | 01     | 01bb   | bfff   | ffff   |          | 1, 2    |

| BTFSC    | f, b  | Bit Test f, Skip if Clear    | 1 <sup>(2)</sup> | 01     | 10bb   | bfff   | ffff   |          | 3       |

| BTFSS    | f, b  | Bit Test f, Skip if Set      | 1 <sup>(2)</sup> | 01     | 11bb   | bfff   | ffff   |          | 3       |

|          |       | LITERAL AND CON              | TROL OPERATIO    | ONS    |        |        |        |          |         |

| ADDLW    | k     | Add literal and W            | 1                | 11     | 111x   | kkkk   | kkkk   | C,DC,Z   |         |

| ANDLW    | k     | AND literal with W           | 1                | 11     | 1001   | kkkk   | kkkk   | Z        |         |

| CALL     | k     | Call subroutine              | 2                | 10     | 0kkk   | kkkk   | kkkk   |          |         |

| CLRWDT   | _     | Clear Watchdog Timer         | 1                | 00     | 0000   | 0110   | 0100   | TO,PD    |         |

| GOTO     | k     | Go to address                | 2                | 10     | 1kkk   | kkkk   | kkkk   |          |         |

| IORLW    | k     | Inclusive OR literal with W  | 1                | 11     | 1000   | kkkk   | kkkk   | Z        |         |

| MOVLW    | k     | Move literal to W            | 1                | 11     | 00xx   | kkkk   | kkkk   |          |         |

| RETFIE   | _     | Return from interrupt        | 2                | 00     | 0000   | 0000   | 1001   |          |         |

| RETLW    | k     | Return with literal in W     | 2                | 11     | 01xx   | kkkk   | kkkk   |          |         |

| RETURN   | _     | Return from Subroutine       | 2                | 00     | 0000   | 0000   | 1000   |          |         |

| SLEEP    | _     | Go into Standby mode         | 1                | 00     | 0000   | 0110   | 0011   | TO,PD    |         |

| SUBLW    | k     | Subtract W from literal      | 1                | 11     | 110x   | kkkk   | kkkk   | C,DC,Z   |         |

| XORLW    | k     | Exclusive OR literal with W  | 1                | 11     | 1010   | kkkk   | kkkk   | Z        |         |

### TABLE 15-2: PIC16F627A/628A/648A INSTRUCTION SET

**Note** 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

# PIC16F627A/628A/648A

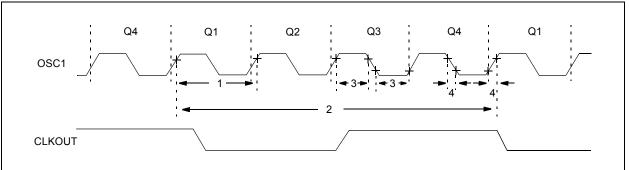

#### 17.6 **Timing Diagrams and Specifications**

#### **FIGURE 17-4: EXTERNAL CLOCK TIMING**

| TABLE 17-4: | EXTERNAL CLOCK TIMING REQUIREMENTS |

|-------------|------------------------------------|

|             |                                    |

| Parameter<br>No. | Sym           | Characteristic                                   | Min     | Тур† | Мах    | Units | Conditions                         |

|------------------|---------------|--------------------------------------------------|---------|------|--------|-------|------------------------------------|

|                  | Fosc          | External CLKIN Frequency <sup>(1)</sup>          | DC      | —    | 4      | MHz   | XT and RC Osc mode,<br>VDD = 5.0 V |

|                  |               |                                                  | DC      |      | 20     | MHz   | HS, EC Osc mode                    |

|                  |               |                                                  | DC      |      | 200    | kHz   | LP Osc mode                        |

|                  |               | Oscillator Frequency <sup>(1)</sup>              | —       |      | 4      | MHz   | RC Osc mode, VDD = 5.0V            |

|                  |               |                                                  | 0.1     | _    | 4      | MHz   | XT Osc mode                        |

|                  |               |                                                  | 1       |      | 20     | MHz   | HS Osc mode                        |

|                  |               |                                                  |         |      | 200    | kHz   | LP Osc mode                        |

|                  |               |                                                  |         | 4    | —      | MHz   | INTOSC mode (fast)                 |

|                  |               |                                                  |         | 48   |        | kHz   | INTOSC mode (slow)                 |

| 1                | Tosc          | External CLKIN Period <sup>(1)</sup>             | 250     |      |        | ns    | XT and RC Osc mode                 |

|                  |               |                                                  | 50      | _    | _      | ns    | HS, EC Osc mode                    |

|                  |               |                                                  | 5       | —    | —      | μS    | LP Osc mode                        |

|                  |               | Oscillator Period <sup>(1)</sup>                 | 250     | —    | —      | ns    | RC Osc mode                        |

|                  |               |                                                  | 250     | _    | 10,000 | ns    | XT Osc mode                        |

|                  |               |                                                  | 50      |      | 1,000  | ns    | HS Osc mode                        |

|                  |               |                                                  | 5       | _    | —      | μS    | LP Osc mode                        |

|                  |               |                                                  | _       | 250  | —      | ns    | INTOSC mode (fast)                 |

|                  |               |                                                  | _       | 21   | _      | μS    | INTOSC mode (slow)                 |

| 2                | TCY           | Instruction Cycle Time                           | 200     | TCY  | DC     | ns    | Tcy = 4/Fosc                       |

| 3                | TosL,<br>TosH | External CLKIN (OSC1) High<br>External CLKIN Low | 100*    | —    | —      | ns    | XT oscillator, Tosc L/H duty cycle |

| 4                | RC            | External Biased RC<br>Frequency                  | 10 kHz* | _    | 4 MHz  | —     | VDD = 5.0V                         |

These parameters are characterized but not tested.

t Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time-based period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "Max" cycle time limit is "DC" (no clock) for all devices.

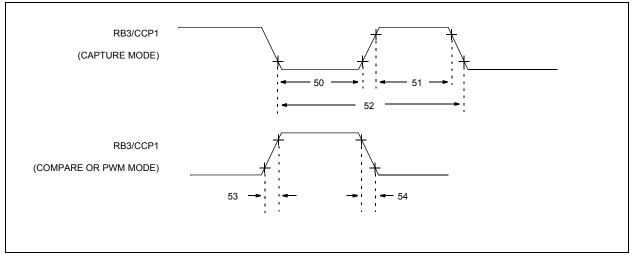

| Param<br>No. | Sym  |                        | Characteristic | ;           | Min                    | Тур† | Max | Units | Conditions                        |

|--------------|------|------------------------|----------------|-------------|------------------------|------|-----|-------|-----------------------------------|

| 50           | TCCL | CCP<br>input low time  | No Prescaler   |             | 0.5Tcy +<br>20*        | —    | —   | ns    |                                   |

|              |      |                        |                | PIC16F62XA  | 10*                    | _    | —   | ns    |                                   |

|              |      |                        | With Prescaler | PIC16LF62XA | 20*                    | —    | —   | ns    |                                   |

| 51           | ТссН | CCP<br>input high time | No Prescaler   |             | 0.5Tcy +<br>20*        | -    | —   | ns    |                                   |

|              |      |                        |                | PIC16F62XA  | 10*                    | —    | _   | ns    |                                   |

|              |      |                        | With Prescaler | PIC16LF62XA | 20*                    | —    | _   | ns    |                                   |

| 52           | TccP | CCP input period       |                |             | <u>3Tcy + 40*</u><br>N | _    | —   | ns    | N = prescale<br>value (1,4 or 16) |

| 53           | TccR | CCP output rise time   |                | PIC16F62XA  |                        | 10   | 25* | ns    |                                   |

|              |      |                        |                | PIC16LF62XA |                        | 25   | 45* | ns    |                                   |

| 54           | TccF | CCP output fall f      | time           | PIC16F62XA  |                        | 10   | 25* | ns    |                                   |

|              |      |                        |                | PIC16LF62XA |                        | 25   | 45* | ns    |                                   |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16F627A/628A/648A

### I

| I/O Ports                                   |     |

|---------------------------------------------|-----|

| Bidirectional                               | 46  |

| Block Diagrams                              |     |

| RB0/INT Pin                                 |     |

| RB1/RX/DT Pin                               |     |

| RB2/TX/CK Pin                               |     |

| RB3/CCP1 Pin                                |     |

| RB4/PGM Pin                                 |     |

| RB5 Pin                                     |     |

| RB6/T1OSO/T1CKI Pin                         |     |

| RB7/T1OSI Pin                               |     |

| PORTA                                       |     |

| PORTB                                       |     |

| Programming Considerations                  |     |

| Successive Operations<br>TRISA              |     |

| TRISA<br>TRISB                              |     |

| ID Locations                                |     |

| INCF Instruction                            |     |

| INCFSZ Instruction                          |     |

| In-Circuit Serial Programming™              |     |

| Indirect Addressing, INDF and FSR Registers |     |

| Instruction Flow/Pipelining                 |     |

| Instruction Set                             |     |

| ADDLW                                       | 119 |

| ADDWF                                       |     |

| ANDLW                                       |     |

| ANDWF                                       |     |

| BCF                                         |     |

| BSF                                         |     |

| BTFSC                                       |     |

| BTFSS                                       | 121 |

| CALL                                        | 121 |

| CLRF                                        | 121 |

| CLRW                                        | 122 |

| CLRWDT                                      | 122 |

| COMF                                        | 122 |

| DECF                                        | 122 |

| DECFSZ                                      | 123 |

| GOTO                                        | 123 |

| INCF                                        | 124 |

| INCFSZ                                      |     |

| IORLW                                       |     |

| IORWF                                       |     |

| MOVF                                        |     |

| MOVLW                                       |     |

| MOVWF                                       |     |

| NOP                                         |     |

| OPTION                                      |     |

| RETFIE                                      |     |

| RETLW                                       |     |

| RETURN                                      |     |

| RLF                                         |     |

| RRF                                         |     |

| SLEEP                                       |     |

| SUBLW                                       |     |

| SUBWF<br>SWAPF                              |     |

| TRIS                                        |     |

| XORLW                                       |     |

| XORWF                                       |     |

| Instruction Set Summary                     |     |

| INT Interrupt                               |     |

| INTCON Register                             |     |

|                                             |     |

| Internet Address         | 173 |

|--------------------------|-----|

| Interrupt Sources        |     |

| Capture Complete (CCP)   | 58  |

| Compare Complete (CCP)   | 59  |

| TMR2 to PR2 Match (PWM)  |     |

| Interrupts               | 109 |

| Interrupts, Enable Bits  |     |

| CCP1 Enable (CCP1IE Bit) | 58  |

| Interrupts, Flag Bits    |     |

| CCP1 Flag (CCP1IF Bit)   | 58  |

| IORLW Instruction        | 125 |

| IORWF Instruction        | 125 |

## Μ

| 1, 93, 95 |

|-----------|

| 173       |

| 172       |

| 125       |

| 125       |

| 126       |

| 132       |

| are 131   |

| 134       |

| 133       |

| 132       |

|           |

### Ν

| NOP | Instruction | 12 | 6 |

|-----|-------------|----|---|

|-----|-------------|----|---|

### 0

| OPTION Instruction              | 126 |

|---------------------------------|-----|

| OPTION Register                 |     |

| OPTION_REG Register             |     |

| Oscillator Configurations       |     |

| Oscillator Start-up Timer (OST) |     |

# Ρ

| Package Marking Information          | 163   |

|--------------------------------------|-------|

| Packaging Information                | 163   |

| PCL and PCLATH                       |       |

| Stack                                | 30    |

| PCON Register                        | 29    |

| PIE1 Register                        |       |

| Pin Functions                        |       |

| RC6/TX/CK                            | 73–89 |

| RC7/RX/DT                            | 73–89 |

| PIR1 Register                        |       |

| PORTA                                | 33    |

| PORTB                                | 38    |

| PORTB Interrupt                      |       |

| Power Control/Status Register (PCON) | 104   |

| Power-Down Mode (Sleep)              |       |

| Power-On Reset (POR)                 | 103   |

| Power-up Timer (PWRT)                | 103   |

| PR2 Register                         |       |

| Program Memory Organization          | 17    |

| PWM (CCP Module)                     | 60    |

| Block Diagram                        | 60    |

| Simplified PWM                       | 60    |

| CCPR1H:CCPR1L Registers              | 60    |

| Duty Cycle                           | 61    |

| Example Frequencies/Resolutions      | 61    |

| Period                               | 60    |

| Set-Up for PWM Operation             | 61    |

| TMR2 to PR2 Match                    | 60    |

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.              | x <u>/xx xxx</u>                                                                                                                                                                                                                                                                      | Examples:                                                                                                                                                                                                                                    |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                | Temperature<br>RangePackage<br>Pattern<br>RangePIC16F627A/628A/648A:Standard VDD range 3.0V to<br>5.5VPIC16F627A/628A/648AT:VDD range 3.0V to 5.5V<br>(Tape and Reel)PIC16LF627A/628A/648A:VDD range 2.0V to 5.5V<br>PIC16LF627A/628A/648AT:VDD range 2.0V to 5.5V<br>(Tape and Reel) | <ul> <li>a) PIC16F627A - E/P 301 = Extended<br/>Temp.,<br/>PDIP package, 20 MHz, normal VDD lim-<br/>its, QTP pattern #301.</li> <li>b) PIC16LF627A - I/SO = Industrial Temp.,<br/>SOIC package, 20 MHz, extended VDD<br/>limits.</li> </ul> |