Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 224 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f628t-04-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16F627A/628A/648A family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16F627A/628A/648A uses a Harvard architecture in which program and data are accessed from separate memories using separate busses. This improves bandwidth over traditional Von Neumann architecture where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single-word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single-cycle (200 ns @ 20 MHz) except for program branches.

Table 3-1 lists device memory sizes (Flash, Data and EEPROM).

TABLE 3-1: DEVICE MEMORY LIST

|             | Memory           |             |                |  |  |  |

|-------------|------------------|-------------|----------------|--|--|--|

| Device      | Flash<br>Program | RAM<br>Data | EEPROM<br>Data |  |  |  |

| PIC16F627A  | 1024 x 14        | 224 x 8     | 128 x 8        |  |  |  |

| PIC16F628A  | 2048 x 14        | 224 x 8     | 128 x 8        |  |  |  |

| PIC16F648A  | 4096 x 14        | 256 x 8     | 256 x 8        |  |  |  |

| PIC16LF627A | 1024 x 14        | 224 x 8     | 128 x 8        |  |  |  |

| PIC16LF628A | 2048 x 14        | 224 x 8     | 128 x 8        |  |  |  |

| PIC16LF648A | 4096 x 14        | 256 x 8     | 256 x 8        |  |  |  |

The PIC16F627A/628A/648A can directly or indirectly address its register files or data memory. All Special Function Registers (SFR), including the program counter, are mapped in the data memory. The PIC16F627A/628A/648A have an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation, on any register, using any addressing mode. This symmetrical nature and lack of 'special optimal situations' makes programming with the PIC16F627A/628A/648A simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16F627A/628A/648A devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the Status Register. The C and DC bits operate as Borrow and Digit Borrow out bits, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, and a description of the device pins in Table 3-2.

Two types of data memory are provided on the PIC16F627A/628A/648A devices. Nonvolatile EEPROM data memory is provided for long term storage of data, such as calibration values, look-up table data, and any other data which may require periodic updating in the field. These data types are not lost when power is removed. The other data memory provided is regular RAM data memory. Regular RAM data memory is provided for temporary storage of data during normal operation. Data is lost when power is removed.

| Name                                                  | Function | Input Type | Output Type                           | Description                                                                                                                                              |

|-------------------------------------------------------|----------|------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB4/PGM                                               | RB4      | TTL        | CMOS                                  | Bidirectional I/O port. Interrupt-on-pin change.<br>Can be software programmed for internal<br>weak pull-up.                                             |

|                                                       | PGM      | ST         | _                                     | Low-voltage programming input pin. When<br>low-voltage programming is enabled, the<br>interrupt-on-pin change and weak pull-up<br>resistor are disabled. |

| RB5                                                   | RB5      | TTL        | CMOS                                  | Bidirectional I/O port. Interrupt-on-pin change.<br>Can be software programmed for internal<br>weak pull-up.                                             |

| RB6/T1OSO/T1CKI/PGC                                   | RB6      | TTL        | CMOS                                  | Bidirectional I/O port. Interrupt-on-pin change.<br>Can be software programmed for internal<br>weak pull-up.                                             |

|                                                       | T10S0    | —          | XTAL                                  | Timer1 oscillator output                                                                                                                                 |

|                                                       | T1CKI    | ST         | —                                     | Timer1 clock input                                                                                                                                       |

|                                                       | PGC      | ST         | —                                     | ICSP™ programming clock                                                                                                                                  |

| RB7/T1OSI/PGD                                         | RB7      | TTL        | CMOS                                  | Bidirectional I/O port. Interrupt-on-pin change.<br>Can be software programmed for internal<br>weak pull-up.                                             |

|                                                       | T10SI    | XTAL       | _                                     | Timer1 oscillator input                                                                                                                                  |

|                                                       | PGD      | ST         | CMOS                                  | ICSP data I/O                                                                                                                                            |

| Vss                                                   | Vss      | Power      | —                                     | Ground reference for logic and I/O pins                                                                                                                  |

| Vdd                                                   | Vdd      | Power      | —                                     | Positive supply for logic and I/O pins                                                                                                                   |

| Legend: O = Output<br>— = Not used<br>TTL = TTL Input |          | l = Ir     | MOS Output<br>iput<br>ipen Drain Outj | P = Power<br>ST = Schmitt Trigger Input<br>AN = Analog                                                                                                   |

### TABLE 3-2: PIC16F627A/628A/648A PINOUT DESCRIPTION (CONTINUED)

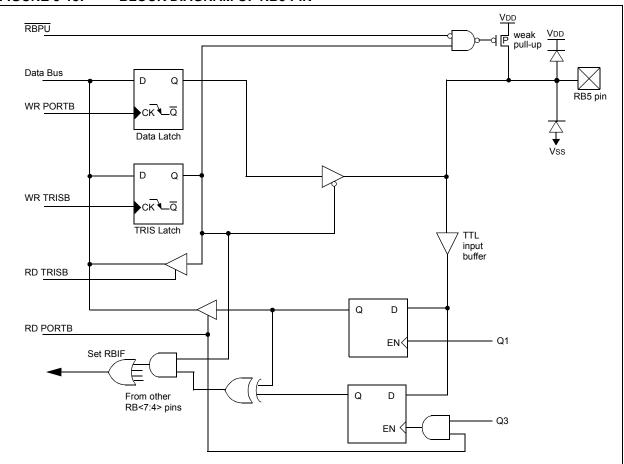

### FIGURE 5-13: BLOCK DIAGRAM OF RB5 PIN

## 6.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Read/write capabilities

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module. Additional information is available in the *"PIC<sup>®</sup> Mid-Range MCU Family Reference Manual"* (DS33023).

Timer mode is selected by clearing the TOCS bit (OPTION<5>). In Timer mode, the TMR0 register value will increment every instruction cycle (without prescaler). If the TMR0 register is written to, the increment is inhibited for the following two cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit. In this mode the TMR0 register value will increment either on every rising or falling edge of pin RA4/T0CKI/CMP2. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in **Section 6.2 "Using Timer0 with External Clock"**.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4,..., 1:256 are selectable. **Section 6.3 "Timer0 Prescaler**" details the operation of the prescaler.

### 6.1 Timer0 Interrupt

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before reenabling this interrupt. The Timer0 interrupt cannot wake the processor from Sleep since the timer is shut off during Sleep.

### 6.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-1). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device. See Table 17-8.

NOTES:

## **10.0 COMPARATOR MODULE**

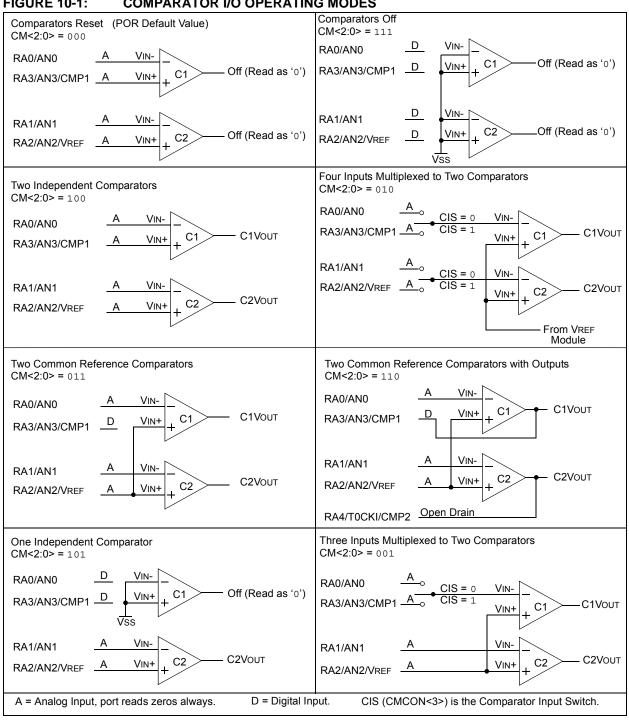

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the RA0 through RA3 pins. The on-chip Voltage Reference (Section 11.0 "Voltage Reference Module") can also be an input to the comparators.

The CMCON register, shown in Register 10-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 10-1.

### **REGISTER 10-1: CMCON – COMPARATOR CONFIGURATION REGISTER (ADDRESS: 01Fh)**

|         | R-0              | R-0                             | R/W-0      | R/W-0       | R/W-0           | R/W-0   | R/W-0 | ,<br>R/W-0 |

|---------|------------------|---------------------------------|------------|-------------|-----------------|---------|-------|------------|

|         | C2OUT            | C10UT                           | C2INV      | C1INV       | CIS             | CM2     | CM1   | CM0        |

|         | bit 7            | 0.001                           | 02         | •           | 0.0             | 0       | •     | bit 0      |

|         |                  |                                 |            |             |                 |         |       |            |

| bit 7   | C2OUT: C         | omparator 2                     | Output bit |             |                 |         |       |            |

|         | When C2I         | -                               | e alpar al |             |                 |         |       |            |

|         |                  | + > C2 VIN-                     |            |             |                 |         |       |            |

|         | 0 = C2 VIN       | ₁+ < C2 VIN-                    |            |             |                 |         |       |            |

|         | When C2I         | NV = 1                          |            |             |                 |         |       |            |

|         |                  | I+ < C2 VIN-                    |            |             |                 |         |       |            |

|         | 0 = C2 VIN       | + > C2 VIN-                     |            |             |                 |         |       |            |

| bit 6   | <b>C10UT</b> : C | omparator 1                     | Output bit |             |                 |         |       |            |

|         | When C1I         | NV = 0:                         |            |             |                 |         |       |            |

|         | -                | I+ > C1 VIN-                    |            |             |                 |         |       |            |

|         | 0 = C1 VIN       | ₁+ < C1 Vin-                    |            |             |                 |         |       |            |

|         | When C1I         | NV = 1:                         |            |             |                 |         |       |            |

|         | -                | ₁+ < C1 Vin-                    |            |             |                 |         |       |            |

|         |                  | ₁+ > C1 Vin-                    |            |             |                 |         |       |            |

| bit 5   |                  | omparator 2 (                   | -          | rsion bit   |                 |         |       |            |

|         |                  | Itput inverted                  |            |             |                 |         |       |            |

| bit 4   |                  | itput not inve                  |            | raion hit   |                 |         |       |            |

| DIL 4   |                  | itput inverted                  | -          | ISION DIL   |                 |         |       |            |

|         |                  | itput not inve                  |            |             |                 |         |       |            |

| bit 3   |                  | parator Input                   |            |             |                 |         |       |            |

|         |                  | <2:0>: = 001                    |            |             |                 |         |       |            |

|         | Then:            |                                 |            |             |                 |         |       |            |

|         |                  | I- connects to                  |            |             |                 |         |       |            |

|         | 0 = C1 VIN       | I- connects to                  | D RAU      |             |                 |         |       |            |

|         | When CM          | <2:0> = 010                     |            |             |                 |         |       |            |

|         | Then:            |                                 |            |             |                 |         |       |            |

|         | -                | I- connects to                  |            |             |                 |         |       |            |

|         |                  | N- connects t<br>I- connects to |            |             |                 |         |       |            |

|         |                  | N- connects t                   |            |             |                 |         |       |            |

| bit 2-0 |                  | Comparator                      |            |             |                 |         |       |            |

|         |                  | -                               |            | r modes and | d CM<2:0> bit s | ettings |       |            |

|         | -                |                                 | ·          |             |                 | -       |       |            |

|         | Legend:          |                                 |            |             |                 |         |       |            |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### **10.1** Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select the mode. Figure 10-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode.

If the Comparator mode is changed, the comparator output level may not be valid for the specified mode change delay shown in Table 17-2.

- Note 1: Comparator interrupts should be disabled during a Comparator mode change, otherwise a false interrupt may occur.

- 2: Comparators can have an inverted output. See Figure 10-1.

### FIGURE 10-1: COMPARATOR I/O OPERATING MODES

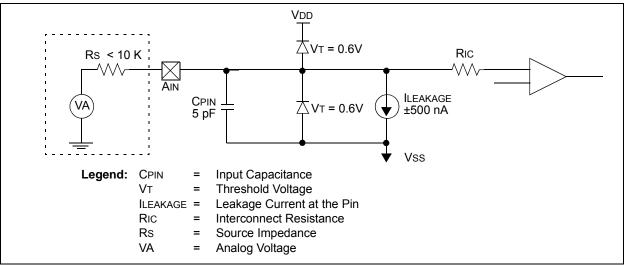

### FIGURE 10-4: ANALOG INPUT MODE

| Address                 | Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>Resets |

|-------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 1Fh                     | CMCON  | C2OUT  | C10UT  | C2INV  | C1NV   | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE    | PEIE   | T0IE   | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 0Ch                     | PIR1   | EEIF   | CMIF   | RCIF   | TXIF   | _      | CCP1IF | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                       |

| 8Ch                     | PIE1   | EEIE   | CMIE   | RCIE   | TXIE   | _      | CCP1IE | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                       |

| 85h                     | TRISA  | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

**Legend:** x = Unknown, u = Unchanged, - = Unimplemented, read as '0'

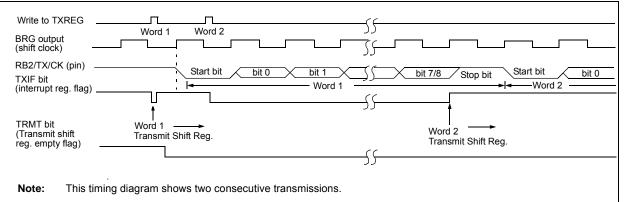

### FIGURE 12-3: ASYNCHRONOUS TRANSMISSION (BACK TO BACK)

### TABLE 12-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address | Name                                  | Bit 7     | Bit 6    | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>all other<br>Resets |

|---------|---------------------------------------|-----------|----------|------------|-------|-------|--------|--------|--------|-----------------|---------------------------------|

| 0Ch     | PIR1                                  | EEIF      | CMIF     | RCIF       | TXIF  |       | CCP1IF | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                       |

| 18h     | RCSTA                                 | SPEN      | RX9      | SREN       | CREN  | ADEN  | FERR   | OERR   | RX9D   | x000 0000       | 0000 000x                       |

| 19h     | TXREG                                 | USART Tra | nsmit Da | ta Registe | er    |       |        |        |        | 0000 0000       | 0000 0000                       |

| 8Ch     | PIE1                                  | EEIE      | CMIE     | RCIE       | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                       |

| 98h     | TXSTA                                 | CSRC      | TX9      | TXEN       | SYNC  |       | BRGH   | TRMT   | TX9D   | 0000 -010       | 0000 -010                       |

| 99h     | 9h SPBRG Baud Rate Generator Register |           |          |            |       |       |        |        |        | 0000 0000       | 0000 0000                       |

**Legend:** x = unknown, - = unimplemented locations read as '0'.

Shaded cells are not used for Asynchronous Transmission.

## 12.5 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RB2/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in Sleep mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

### 12.5.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from Sleep and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Follow these steps when setting up a Synchronous Slave Transmission:

- 1. TRISB<1> and TRISB<2> should both be set to '1' to configure the RB1/RX/DT and RB2/TX/CK pins as inputs. Output drive, when required, is controlled by the peripheral circuitry.

- Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 3. Clear bits CREN and SREN.

- 4. If interrupts are desired, then set enable bit TXIE.

- 5. If 9-bit transmission is desired, then set bit TX9.

- 6. Enable the transmission by setting enable bit TXEN.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 8. Start transmission by loading data to the TXREG register.

### 13.3 Reading the EEPROM Data Memory

To read a data memory location, the user must write the address to the EEADR register and then set control bit RD (EECON1<0>). The data is available, in the very next cycle, in the EEDATA register; therefore it can be read in the next instruction. EEDATA will hold this value until another read or until it is written to by the user (during a write operation).

EXAMPLE 13-1: DATA EEPROM READ

| BSF   | STATUS, RPO | ;Bank 1          |

|-------|-------------|------------------|

| MOVLW | CONFIG_ADDR | ;                |

| MOVWF | EEADR       | ;Address to read |

| BSF   | EECON1, RD  | ;EE Read         |

| MOVF  | EEDATA, W   | ;W = EEDATA      |

| BCF   | STATUS, RPO | ;Bank 0          |

|       |             |                  |

## 13.4 Writing to the EEPROM Data Memory

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDATA register. Then the user must follow a specific sequence to initiate the write for each byte.

EXAMPLE 13-2: DATA EEPROM WRITE

| quired               | BSF<br>BSF<br>BCF<br>BTFSC<br>GOTO<br>MOVLW<br>MOVLW<br>MOVLW | STATUS, RPO<br>EECON1, WREN<br>INTCON, GIE<br>INTCON, GIE<br>\$-2<br>55h<br>EECON2<br>AAh | <pre>;Bank 1 ;Enable write ;Disable INTs. ;See AN576 ; ;Write 55h ;</pre>     |

|----------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Required<br>Sequence | MOVLW<br>MOVWF<br>BSF                                         | EECON2<br>AAh<br>EECON2<br>EECON1,WR<br>CON, GIE                                          | ;Write 55n<br>;<br>;Write AAh<br>;Set WR bit<br>;begin write<br>;Enable INTs. |

The write will not initiate if the above sequence is not followed exactly (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. We strongly recommend that interrupts be disabled during this code segment. A cycle count is executed during the required sequence. Any number that is not equal to the required cycles to execute the required sequence will cause the data not to be written into the EEPROM.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. The EEIF bit in the PIR1 registers must be cleared by software.

## 13.5 Write Verify

Depending on the application, good programming practice may dictate that the value written to the Data EEPROM should be verified (Example 13-3) to the desired value to be written. This should be used in applications where an EEPROM bit will be stressed near the specification limit.

### EXAMPLE 13-3: WRITE VERIFY

|     | BSF      | STATUS, RPO | );Bank 1          |

|-----|----------|-------------|-------------------|

|     | MOVF     | EEDATA, W   |                   |

|     | BSF      | EECON1, RD  | ;Read the         |

|     |          |             | ;value written    |

| ;   |          |             |                   |

| ;Is | the val  | ue written  | (in W reg) and    |

| ;re | ad (in E | EEDATA) the | same?             |

| ;   |          |             |                   |

|     | SUBWF    | EEDATA, W   | ;                 |

|     | BTFSS    | STATUS, Z   | ;Is difference 0? |

|     | GOTO     | WRITE ERR   | ;NO, Write error  |

|     | :        |             | ;YES, Good write  |

|     | :        |             | ;Continue program |

|     |          |             |                   |

## 13.6 Protection Against Spurious Write

There are conditions when the device may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built-in. On power-up, WREN is cleared. Also when enabled, the Power-up Timer (72 ms duration) prevents EEPROM write.

The write initiate sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch or software malfunction.

### 14.2 Oscillator Configurations

### 14.2.1 OSCILLATOR TYPES

The PIC16F627A/628A/648A can be operated in eight different oscillator options. The user can program three configuration bits (FOSC2 through FOSC0) to select one of these eight modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC External Resistor/Capacitor (2 modes)

- INTOSC Internal Precision Oscillator (2 modes)

- EC External Clock In

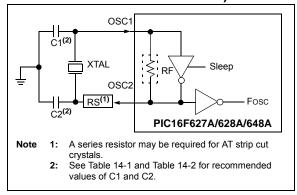

## 14.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (Figure 14-1). The PIC16F627A/628A/648A oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (Figure 14-4).

### FIGURE 14-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

## TABLE 14-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| Mode | Freq     | OSC1(C1)  | OSC2(C2)  |

|------|----------|-----------|-----------|

| XT   | 455 kHz  | 22-100 pF | 22-100 pF |

|      | 2.0 MHz  | 15-68 pF  | 15-68 pF  |

|      | 4.0 MHz  | 15-68 pF  | 15-68 pF  |

| HS   | 8.0 MHz  | 10-68 pF  | 10-68 pF  |

|      | 16.0 MHz | 10-22 pF  | 10-22 pF  |

|      |          |           |           |

**Note:** Higher capacitance increases the stability of the oscillator, but also increases the start-up time. These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

### TABLE 14-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Mode | Freq    | OSC1(C1)  | OSC2(C2)   |

|------|---------|-----------|------------|

| LP   | 32 kHz  | 15-30 pF  | 15-30 pF   |

|      | 200 kHz | 0-15 pF   | 0-15 pF    |

| XT   | 100 kHz | 68-150 pF | 150-200 pF |

|      | 2 MHz   | 15-30 pF  | 15-30 pF   |

|      | 4 MHz   | 15-30 pF  | 15-30 pF   |

| HS   | 8 MHz   | 15-30 pF  | 15-30 pF   |

|      | 10 MHz  | 15-30 pF  | 15-30 pF   |

|      | 20 MHz  | 15-30 pF  | 15-30 pF   |

**Note:** Higher capacitance increases the stability of the oscillator, but also increases the start-up time. These values are for design guidance only. A series resistor (RS) may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

NOTES:

### 16.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

### 16.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

### 16.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

### 16.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 16.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB IDE compatibility

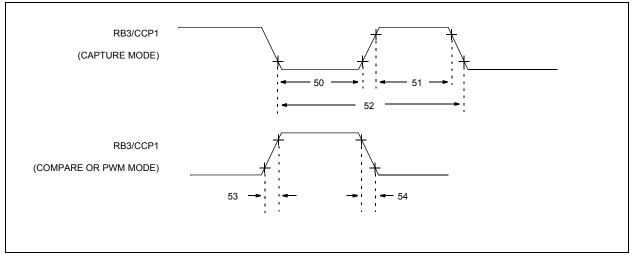

| Param<br>No. | Sym                            | Characteristic         |                | Min         | Тур†                   | Max | Units | Conditions |                                   |

|--------------|--------------------------------|------------------------|----------------|-------------|------------------------|-----|-------|------------|-----------------------------------|

| 50           | TCCL                           | CCP<br>input low time  | No Prescaler   |             | 0.5Tcy +<br>20*        | —   | —     | ns         |                                   |

|              |                                |                        |                | PIC16F62XA  | 10*                    | _   | —     | ns         |                                   |

|              |                                |                        | With Prescaler | PIC16LF62XA | 20*                    | —   | —     | ns         |                                   |

| 51           | 51 TCCH CCP<br>input high time |                        | No Prescaler   |             | 0.5Tcy +<br>20*        | -   | —     | ns         |                                   |

|              |                                |                        |                | PIC16F62XA  | 10*                    | —   | _     | ns         |                                   |

|              |                                |                        | With Prescaler | PIC16LF62XA | 20*                    | —   | _     | ns         |                                   |

| 52           | TCCP                           | CCP input perio        | d              |             | <u>3Tcy + 40*</u><br>N | -   | —     | ns         | N = prescale<br>value (1,4 or 16) |

| 53           | TccR                           | R CCP output rise time |                | PIC16F62XA  |                        | 10  | 25*   | ns         |                                   |

|              |                                |                        |                | PIC16LF62XA |                        | 25  | 45*   | ns         |                                   |

| 54           | TccF                           | CCP output fall time   |                | PIC16F62XA  |                        | 10  | 25*   | ns         |                                   |

|              |                                |                        |                | PIC16LF62XA |                        | 25  | 45*   | ns         |                                   |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

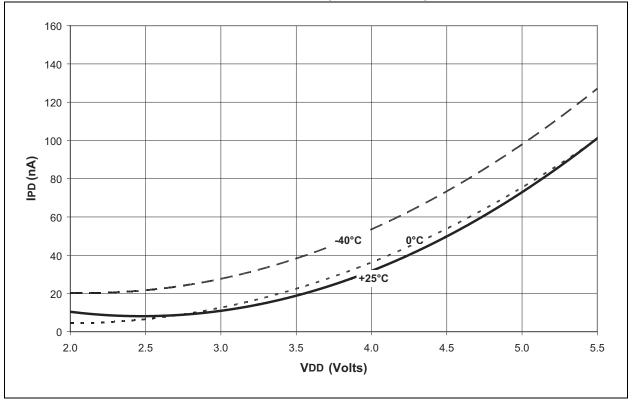

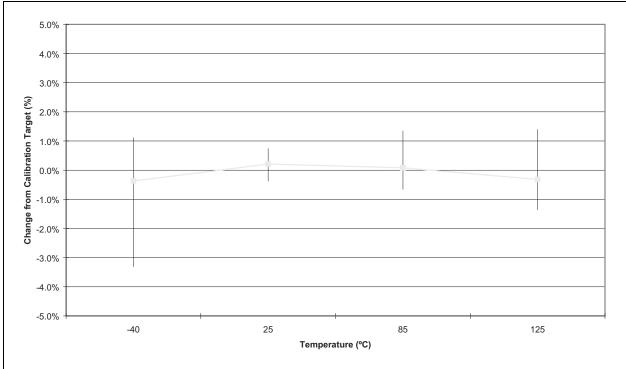

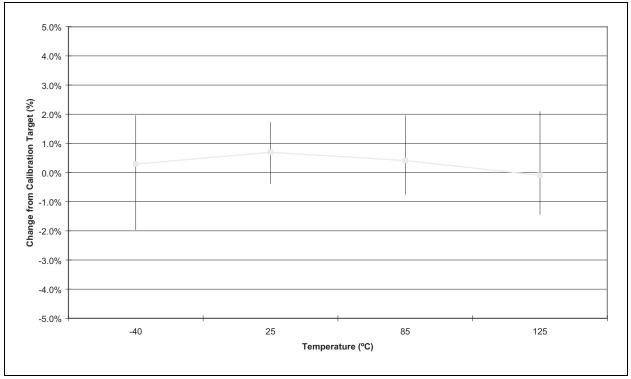

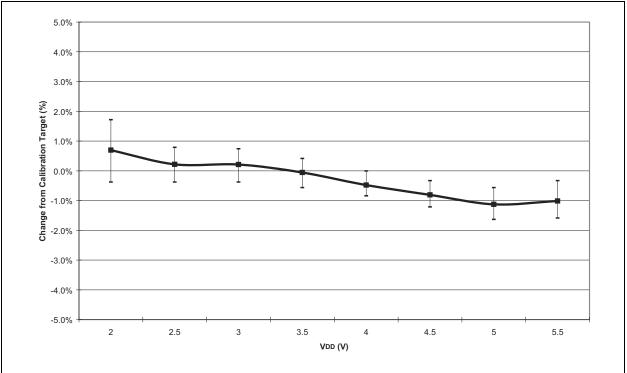

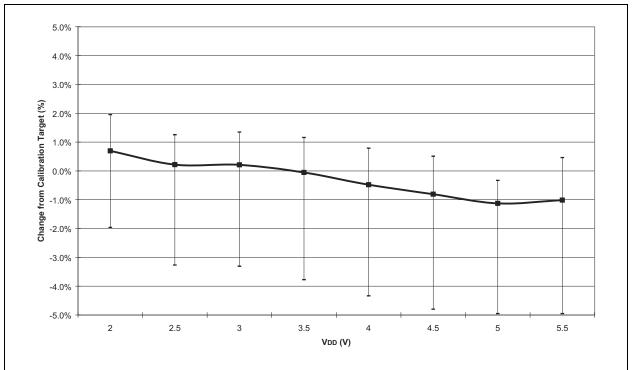

## 18.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for design guidance and are not tested.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

The data presented in this section is a **statistical summary** of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at 25°C. 'Max' or 'Min' represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation, over the whole temperature range.

FIGURE 18-1: TYPICAL BASELINE IPD vs. VDD (-40°C TO 25°C)

FIGURE 18-10: TYPICAL INTERNAL OSCILLATOR FREQUENCY vs. TEMPERATURE VDD = 3 VOLTS

FIGURE 18-11: TYPICAL INTERNAL OSCILLATOR FREQUENCY vs. TEMPERATURE VDD = 2 VOLTS

FIGURE 18-13: TYPICAL INTERNAL OSCILLATOR FREQUENCY vs. VDD TEMPERATURE = -40°C TO 85°C

## APPENDIX C: DEVICE MIGRATIONS

This section describes the functional and electrical specification differences when migrating between functionally similar devices. (such as from a PIC16F627 to a PIC16F627A).

### C.1 PIC16F627/628 to a PIC16F627A/ 628A

- 1. ER mode is now RC mode.

- Code protection for the program memory has changed from code-protect sections of memory to code-protect of the whole memory. The configuration bits CP0 and CP1 in the PIC16F627/628 do not exist in the PIC16F627A/ 628A. They have been replaced with one configuration bit<13> CP.

- "Brown-out Detect (BOD)" terminology has changed to "Brown-out Reset (BOR)" to better represent the function of the Brown-out circuitry.

- 4. Enabling Brown-out Reset (BOR) does not automatically enable the Power-up Timer (PWRT) the way it did in the PIC16F627/628.

- 5. INTRC is now called INTOSC.

- Timer1 Oscillator is now designed for 32.768 kHz operation. In the PIC16F627/628, the Timer1 oscillator was designed to run up to 200 kHz.

- The Dual-Speed Oscillator mode only works in the INTOSC oscillator mode. In the PIC16F627/ 628, the Dual-Speed Oscillator mode worked in both the INTRC and ER oscillator modes.

## APPENDIX D: MIGRATING FROM OTHER PIC<sup>®</sup> DEVICES

This discusses some of the issues in migrating from other PIC MCU devices to the PIC16F627A/628A/ 648A family of devices.

### D.1 PIC16C62X/CE62X to PIC16F627A/ 628A/648A Migration

See Microchip web site for availability (www.microchip.com).

### D.2 PIC16C622A to PIC16F627A/628A/ 648A Migration

See Microchip web site for availability (www.microchip.com).

**Note:** This device has been designed to perform to the parameters of its data sheet. It has been tested to an electrical specification designed to determine its conformance with these parameters. Due to process differences in the manufacture of this device, this device may have different performance characteristics than its earlier version. These differences may cause this device to perform differently in your application than the earlier version of this device.

### INDEX

| 1 |    |

|---|----|

| ^ | ۰. |

| A/D                         |     |

|-----------------------------|-----|

| Special Event Trigger (CCP) | 59  |

| Absolute Maximum Ratings    | 135 |

| ADDLW Instruction           | 119 |

| ADDWF Instruction           |     |

| ANDLW Instruction           |     |

| ANDWF Instruction           |     |

| Architectural Overview      | 11  |

| Assembler                   |     |

| MPASM Assembler             | 132 |

| В                           |     |

| Baud Rate Error             | 75  |

| Baud Rate Formula           | 75  |

| BCF Instruction             | 120 |

| Block Diagrams              |     |

| Comparator                  |     |

| I/O Operating Modes         |     |

| Modified Comparator Output  | 66  |

| I/O Ports                   |     |

| RB0/INT Pin                 |     |

| RB1/RX/DT Pin               |     |

| RB2/TX/CK Pin               |     |

| RB3/CCP1 Pin                |     |

| RB4/PGM Pin                 |     |

| RB5 Pin                     |     |

| RB6/T10S0/T1CKI Pin         |     |

| RB7/T10SI Pin               |     |

| RC Oscillator Mode          |     |

| USART Receive               |     |

| USART Transmit              |     |

| BRGH bit                    |     |

| Brown-Out Reset (BOR)       |     |

| BSF Instruction             |     |

| BTFSC Instruction           |     |

| BTFSS Instruction           | 121 |

## С

| C Compilers                         |     |

|-------------------------------------|-----|

| MPLAB C18                           | 132 |

| CALL Instruction                    | 121 |

| Capture (CCP Module)                | 58  |

| Block Diagram                       | 58  |

| CCP Pin Configuration               | 58  |

| CCPR1H:CCPR1L Registers             | 58  |

| Changing Between Capture Prescalers | 58  |

| Prescaler                           | 58  |

| Software Interrupt                  | 58  |

| Timer1 Mode Selection               | 58  |

| Capture/Compare/PWM (CCP)           | 57  |

| Capture Mode. See Capture           |     |

| CCP1                                | 57  |

| CCPR1H Register                     | 57  |

| CCPR1L Register                     | 57  |

| CCP2                                | 57  |

| Compare Mode. See Compare           |     |

| PWM Mode. See PWM                   |     |

| Timer Resources                     | 57  |

| CCP1CON Register                    | 57  |

| CCP1M Bits                          | 57  |

| CCP1X:CCP1Y Bits                    | 57  |

| CCP2CON Register                    |     |

| CCP2M<3:2> Bits                     | 57  |

| CCP2X:CCP2Y Bits                     | 57  |

|--------------------------------------|-----|

| Clocking Scheme/Instruction Cycle    |     |

| CLRF Instruction                     |     |

| CLRW Instruction                     |     |

| CLRWDT Instruction                   |     |

| CMCON Register                       |     |

| Code Examples                        |     |

| Data EEPROM Refresh Routine          |     |

| Code Protection                      | 113 |

| COMF Instruction                     | 122 |

| Comparator                           |     |

| Block Diagrams                       |     |

| I/O Operating Modes                  | 64  |

| Modified Comparator Output           | 66  |

| Comparator Module                    | 63  |

| Configuration                        | 64  |

| Interrupts                           | 67  |

| Operation                            | 65  |

| Reference                            | 65  |

| Compare (CCP Module)                 | 58  |

| Block Diagram                        | 58  |

| CCP Pin Configuration                | 59  |

| CCPR1H:CCPR1L Registers              | 58  |

| Software Interrupt                   | 59  |

| Special Event Trigger                | 59  |

| Timer1 Mode Selection                | 59  |

| CONFIG Register                      |     |

| Configuration Bits                   |     |

| Crystal Operation                    |     |

| Customer Change Notification Service | 173 |

| Customer Notification Service        |     |

| Customer Support                     | 173 |

### D

| Data EEPROM Memory               |     |

|----------------------------------|-----|

| EECON1 Register                  |     |

| EECON2 Register                  |     |

| Operation During Code Protection | 95  |

| Reading                          | 93  |

| Spurious Write Protection        | 93  |

| Using                            | 94  |

| Write Verify                     | 93  |

| Writing to                       | 93  |

| Data Memory Organization         | 17  |

| DECF Instruction                 | 122 |

| DECFSZ Instruction               | 123 |

| Development Support              | 131 |

| Device Differences               | 171 |

| Device Migrations                | 172 |

| Dual-speed Oscillator Modes      | 101 |

|                                  |     |

### Ε

| EECON1 Register                     |  |

|-------------------------------------|--|

| EECON1 register                     |  |

| EECON2 register                     |  |

| Errata                              |  |

| External Crystal Oscillator Circuit |  |

### F

Fuses. See Configuration Bits

### G

| General-Purpose Register File 17 | , |

|----------------------------------|---|

| GOTO Instruction                 | 3 |