Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 224 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f628t-04-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 GENERAL DESCRIPTION

The PIC16F627A/628A/648A are 18-pin Flash-based members of the versatile PIC16F627A/628A/648A family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers.

All PIC<sup>®</sup> microcontrollers employ an advanced RISC architecture. The PIC16F627A/628A/648A have enhanced core features, an eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single-cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available, complemented by a large register set.

PIC16F627A/628A/648A microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

PIC16F627A/628A/648A devices have integrated features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption.

The PIC16F627A/628A/648A has 8 oscillator configurations. The single-pin RC oscillator provides a low-cost solution. The LP oscillator minimizes power consumption, XT is a standard crystal, and INTOSC is a self-contained precision two-speed internal oscillator.

The HS mode is for High-Speed crystals. The EC mode is for an external clock source.

The Sleep (Power-down) mode offers power savings. Users can wake-up the chip from Sleep through several external interrupts, internal interrupts and Resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock-up.

Table 1-1 shows the features of the PIC16F627A/628A/ 648A mid-range microcontroller family.

A simplified block diagram of the PIC16F627A/628A/ 648A is shown in Figure 3-1.

The PIC16F627A/628A/648A series fits in applications ranging from battery chargers to low power remote sensors. The Flash technology makes customizing application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages makes this microcontroller series ideal for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16F627A/628A/648A very versatile.

## 1.1 Development Support

The PIC16F627A/628A/648A family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low cost in-circuit debugger, a low cost development programmer and a full-featured programmer. A Third Party "C" compiler support tool is also available.

|             |                                      | PIC16F627A                                         | PIC16F628A                                         | PIC16F648A                                         | PIC16LF627A                                        | PIC16LF628A                                        | PIC16LF648A                                        |

|-------------|--------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|

| Clock       | Maximum Frequency of Operation (MHz) | 20                                                 | 20                                                 | 20                                                 | 20                                                 | 20                                                 | 20                                                 |

|             | Flash Program<br>Memory (words)      | 1024                                               | 2048                                               | 4096                                               | 1024                                               | 2048                                               | 4096                                               |

| Memory      | RAM Data Memory<br>(bytes)           | 224                                                | 224                                                | 256                                                | 224                                                | 224                                                | 256                                                |

|             | EEPROM Data<br>Memory (bytes)        | 128                                                | 128                                                | 256                                                | 128                                                | 128                                                | 256                                                |

|             | Timer module(s)                      | TMR0, TMR1,<br>TMR2                                |

|             | Comparator(s)                        | 2                                                  | 2                                                  | 2                                                  | 2                                                  | 2                                                  | 2                                                  |

| Peripherals | Capture/Compare/<br>PWM modules      | 1                                                  | 1                                                  | 1                                                  | 1                                                  | 1                                                  | 1                                                  |

|             | Serial Communications                | USART                                              | USART                                              | USART                                              | USART                                              | USART                                              | USART                                              |

|             | Internal Voltage<br>Reference        | Yes                                                | Yes                                                | Yes                                                | Yes                                                | Yes                                                | Yes                                                |

|             | Interrupt Sources                    | 10                                                 | 10                                                 | 10                                                 | 10                                                 | 10                                                 | 10                                                 |

|             | I/O Pins                             | 16                                                 | 16                                                 | 16                                                 | 16                                                 | 16                                                 | 16                                                 |

| Features    | Voltage Range (Volts)                | 3.0-5.5                                            | 3.0-5.5                                            | 3.0-5.5                                            | 2.0-5.5                                            | 2.0-5.5                                            | 2.0-5.5                                            |

|             | Brown-out Reset                      | Yes                                                | Yes                                                | Yes                                                | Yes                                                | Yes                                                | Yes                                                |

|             | Packages                             | 18-pin DIP,<br>SOIC, 20-pin<br>SSOP,<br>28-pin QFN |

TABLE 1-1: PIC16F627A/628A/648A FAMILY OF DEVICES

All PIC<sup>®</sup> family devices have Power-on Reset, selectable Watchdog Timer, selectable code-protect and high I/O current capability. All PIC16F627A/628A/648A family devices use serial programming with clock pin RB6 and data pin RB7.

#### FIGURE 4-2: DATA MEMORY MAP OF THE PIC16F627A AND PIC16F628A

| direct addr.(1)     | 00h | Indirect addr. <sup>(1)</sup> | 80h | Indirect addr. <sup>(1)</sup> | 100h | Indirect addr. <sup>(1)</sup> |

|---------------------|-----|-------------------------------|-----|-------------------------------|------|-------------------------------|

| TMR0                | 01h | OPTION                        | 81h | TMR0                          | 101h | OPTION                        |

| PCL                 | 02h | PCL                           | 82h | PCL                           | 102h | PCL                           |

| STATUS              | 03h | STATUS                        | 83h | STATUS                        | 103h | STATUS                        |

| FSR                 | 04h | FSR                           | 84h | FSR                           | 104h | FSR                           |

| PORTA               | 05h | TRISA                         | 85h |                               | 105h |                               |

| PORTB               | 06h | TRISB                         | 86h | PORTB                         | 106h | TRISB                         |

|                     | 07h |                               | 87h |                               | 107h |                               |

|                     | 08h |                               | 88h |                               | 108h |                               |

|                     | 09h |                               | 89h |                               | 109h |                               |

| PCLATH              | 0Ah | PCLATH                        | 8Ah | PCLATH                        | 10Ah | PCLATH                        |

| INTCON              | 0Bh | INTCON                        | 8Bh | INTCON                        | 10Bh | INTCON                        |

| PIR1                | 0Ch | PIE1                          | 8Ch |                               | 10Ch |                               |

|                     | 0Dh |                               | 8Dh |                               | 10Dh |                               |

| TMR1L               | 0Eh | PCON                          | 8Eh |                               | 10Eh |                               |

| TMR1H               | 0Fh |                               | 8Fh |                               | 10Fh |                               |

| T1CON               | 10h |                               | 90h |                               |      |                               |

| TMR2                | 11h |                               | 91h |                               |      |                               |

| T2CON               | 12h | PR2                           | 92h |                               |      |                               |

|                     | 13h |                               | 93h |                               |      |                               |

|                     | 14h |                               | 94h |                               |      |                               |

| CCPR1L              | 15h |                               | 95h |                               |      |                               |

| CCPR1H              | 16h |                               | 96h |                               |      |                               |

| CCP1CON             | 17h |                               | 97h |                               |      |                               |

| RCSTA               | 18h | TXSTA                         | 98h |                               |      |                               |

| TXREG               | 19h | SPBRG                         | 99h |                               |      |                               |

| RCREG               | 1Ah | EEDATA                        | 9Ah |                               |      |                               |

|                     | 1Bh | EEADR                         | 9Bh |                               |      |                               |

|                     | 1Ch | EECON1                        | 9Ch |                               |      |                               |

|                     | 1Dh | EECON2 <sup>(1)</sup>         | 9Dh |                               |      |                               |

|                     | 1Eh |                               | 9Eh |                               |      |                               |

| CMCON               | 1Fh | VRCON                         | 9Fh |                               | 11Fh |                               |

|                     | 20h |                               | A0h | General<br>Purpose            | 120h |                               |

| General             |     | General                       |     | Register                      |      |                               |

| Purpose<br>Register |     | Purpose<br>Register           |     | 48 Bytes                      | 14Fh |                               |

| •                   |     | 80 Bytes                      |     |                               | 150h |                               |

| 80 Bytes            |     |                               |     |                               |      |                               |

|                     | 6Fh |                               | EFh |                               | 16Fh |                               |

| 16 Bytes            | 70h | accesses                      | F0h | accesses                      | 170h | accesses                      |

| IO Dyles            |     | 70h-7Fh                       |     | 70h-7Fh                       |      | 70h-7Fh                       |

|                     | 7Fh |                               | FFh |                               | 17Fh |                               |

| Bank 0              |     | Bank 1                        |     | Bank 2                        |      | Bank 3                        |

| <b>-</b>            | 4 4 | a memory locations, r         |     | ,                             |      |                               |

#### 4.2.2.1 Status Register

The Status register, shown in Register 4-1, contains the arithmetic status of the ALU; the Reset status and the bank select bits for data memory (SRAM).

The Status register can be the destination for any instruction, like any other register. If the Status register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are non-writable. Therefore, the result of an instruction with the Status register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the Status register as "000uu1uu" (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the Status register because these instructions do not affect any Status bit. For other instructions, not affecting any Status bits, see the "Instruction Set Summary".

| Note: | The C and DC bits operate as a Borrow      |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | and Digit Borrow out bit, respectively, in |  |  |  |  |  |  |  |  |

|       | subtraction. See the SUBLW and SUBWF       |  |  |  |  |  |  |  |  |

|       | instructions for examples.                 |  |  |  |  |  |  |  |  |

#### REGISTER 4-1: STATUS – STATUS REGISTER (ADDRESS: 03h, 83h, 103h, 183h)

|         | R/W-0                                                           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0        | R-1           | R-1                          | R/W-x     | R/W-x          | R/W-x       |  |  |  |  |

|---------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------|------------------------------|-----------|----------------|-------------|--|--|--|--|

|         | IRP                                                             | RP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RP0          | TO            | PD                           | Z         | DC             | С           |  |  |  |  |

|         | bit 7 bit 0                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |               |                              |           |                |             |  |  |  |  |

| bit 7   | 1 = Bank 2                                                      | IRP: Register Bank Select bit (used for indirect addressing)<br>1 = Bank 2, 3 (100h-1FFh)<br>0 = Bank 0, 1 (00h-FFh)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |               |                              |           |                |             |  |  |  |  |

| bit 6-5 | <b>RP&lt;1:0&gt;</b> : 1<br>00 = Bank<br>01 = Bank<br>10 = Bank | <b>RP&lt;1:0&gt;</b> : Register Bank Select bits (used for direct addressing)<br>00 = Bank 0 (00h-7Fh)<br>01 = Bank 1 (80h-FFh)<br>10 = Bank 2 (100h-17Fh)<br>11 = Bank 3 (180h-1FFh)                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |               |                              |           |                |             |  |  |  |  |

| bit 4   | 1 = After p                                                     | TO: Time Out bit<br>1 = After power-up, CLRWDT instruction or SLEEP instruction<br>0 = A WDT time out occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |               |                              |           |                |             |  |  |  |  |

| bit 3   | 1 = After p                                                     | <b>PD</b> : Power-down bit 1 = After power-up or by the CLRWDT instruction 0 = By execution of the SLEEP instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |               |                              |           |                |             |  |  |  |  |

| bit 2   |                                                                 | sult of an arit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |               | on is zero<br>on is not zero |           |                |             |  |  |  |  |

| bit 1   | is reversed<br>1 = A carry                                      | 1)<br>/-out from the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | e 4th low or | der bit of th |                              |           | for Borrow t   | he polarity |  |  |  |  |

| bit 0   | <b>C</b> : Carry/B<br>1 = A carry                               | <ul> <li>1 = A carry-out from the 4th low order bit of the result occurred</li> <li>0 = No carry-out from the 4th low order bit of the result</li> <li>C: Carry/Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)</li> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> <li>Note: For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.</li> </ul> |              |               |                              |           |                |             |  |  |  |  |

|         | Legend:                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |               |                              |           |                |             |  |  |  |  |

|         | R = Reada                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | VV = V       | Vritable bit  | U = Unimple                  | emented b | oit, read as ' | יכ          |  |  |  |  |

|         | -n = Value                                                      | at POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | '1' = E      | Bit is set    | '0' = Bit is c               | leared    | x = Bit is ur  | nknown      |  |  |  |  |

#### 4.2.2.6 PCON Register

The PCON register contains flag bits to differentiate between a Power-on Reset, an external MCLR Reset, WDT Reset or a Brown-out Reset.

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if BOR is cleared, indicating a brown-out has occurred. The BOR Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BOREN bit in the Configuration Word).

#### REGISTER 4-6:

#### PCON – POWER CONTROL REGISTER (ADDRESS: 8Eh)

| U-0   | U-0 | U-0 | U-0 | R/W-1 | U-0 | R/W-0 | R/W-x |

|-------|-----|-----|-----|-------|-----|-------|-------|

| _     | —   | _   | _   | OSCF  |     | POR   | BOR   |

| bit 7 |     |     |     |       |     |       | bit 0 |

- bit 7-4 Unimplemented: Read as '0'

- bit 3 OSCF: INTOSC Oscillator Frequency bit

- 1 = 4 MHz typical

- 0 = 48 kHz typical

- bit 2 Unimplemented: Read as '0'

- bit 1 **POR**: Power-on Reset Status bit

- 1 = No Power-on Reset occurred

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

- bit 0 BOR: Brown-out Reset Status bit

- 1 = No Brown-out Reset occurred

- 0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

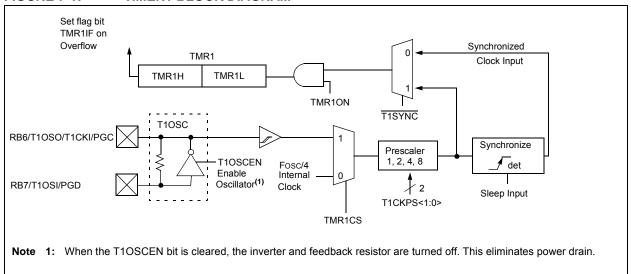

## 7.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L) which are readable and writable. The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The Timer1 Interrupt, if enabled, is generated on overflow of the TMR1 register pair which latches the interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing the Timer1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- As a timer

- As a counter

The Operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

-n = Value at POR

In Timer mode, the TMR1 register pair value increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "Reset input". This Reset can be generated by the CCP module (Section 9.0 "Capture/Compare/PWM (CCP) Module"). Register 7-1 shows the Timer1 control register.

For the PIC16F627A/628A/648A, when the Timer1 oscillator is enabled (T1OSCEN is set), the RB7/T1OSI/PGD and RB6/T1OSO/T1CKI/PGC pins become inputs. That is, the TRISB<7:6> value is ignored.

| TER 7-1: | T1CON – TIMER1 CONTROL REGISTER (ADDRESS: 10h)                                                 |                                                                                                          |                 |                |                 |            |                |            |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------|----------------|-----------------|------------|----------------|------------|--|--|--|--|

|          | U-0                                                                                            | U-0                                                                                                      | R/W-0           | R/W-0          | R/W-0           | R/W-0      | R/W-0          | R/W-0      |  |  |  |  |

|          | —                                                                                              |                                                                                                          | T1CKPS1         | T1CKPS0        | T1OSCEN         | T1SYNC     | TMR1CS         | TMR10N     |  |  |  |  |

|          | bit 7                                                                                          |                                                                                                          |                 |                |                 |            |                | bit 0      |  |  |  |  |

| bit 7-6  | Unimplement                                                                                    | ed: Read                                                                                                 | <b>d as</b> 'o' |                |                 |            |                |            |  |  |  |  |

| bit 5-4  | T1CKPS<1:0>                                                                                    | TICKPS<1:0>: Timer1 Input Clock Prescale Select bits                                                     |                 |                |                 |            |                |            |  |  |  |  |

|          | 10 = 1:4 Preso<br>01 = 1:2 Preso                                                               | 11 = 1:8 Prescale value<br>10 = 1:4 Prescale value<br>01 = 1:2 Prescale value<br>00 = 1:1 Prescale value |                 |                |                 |            |                |            |  |  |  |  |

| bit 3    | T1OSCEN: Tir                                                                                   | mer1 Oso                                                                                                 | cillator Enat   | ole Control bi | t               |            |                |            |  |  |  |  |

|          |                                                                                                | 1 = Oscillator is enabled<br>0 = Oscillator is shut off <sup>(1)</sup>                                   |                 |                |                 |            |                |            |  |  |  |  |

| bit 2    | T1SYNC: Time                                                                                   | er1 Exter                                                                                                | nal Clock Ir    | nput Synchro   | nization Contro | ol bit     |                |            |  |  |  |  |

|          | <u>TMR1CS = 1</u><br>1 = Do not syr<br>0 = Synchroniz<br><u>TMR1CS = 0</u><br>This bit is igno | ze exterr                                                                                                | al clock inp    | out            | ck when TMR1    | CS = 0.    |                |            |  |  |  |  |

| bit 1    | TMR1CS: Tim                                                                                    | er1 Cloc                                                                                                 | k Source Se     | elect bit      |                 |            |                |            |  |  |  |  |

|          | 1 = External cl<br>0 = Internal clo                                                            |                                                                                                          |                 | 10SO/T1CKI     | /PGC (on the r  | ising edge | )              |            |  |  |  |  |

| bit 0    | TMR1ON: Tim                                                                                    | er1 On b                                                                                                 | bit             |                |                 |            |                |            |  |  |  |  |

|          | 1 = Enables T<br>0 = Stops Time                                                                |                                                                                                          |                 |                |                 |            |                |            |  |  |  |  |

|          | Note 1: Th                                                                                     | <b>Note 1:</b> The oscillator inverter and feedback resistor are turned off to eliminate power drain.    |                 |                |                 |            |                |            |  |  |  |  |

|          | Legend:                                                                                        |                                                                                                          |                 |                |                 |            |                |            |  |  |  |  |

|          | R = Readable                                                                                   | bit                                                                                                      | VV = V          | Vritable bit   | U = Unimple     | emented bi | it, read as '( | <b>)</b> ' |  |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

REGISTER 7-1: T1CON – TIMER1 CONTROL REGISTER (ADDRESS: 10h)

x = Bit is unknown

## 7.1 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect since the internal clock is always in sync.

#### 7.2 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode, the TMR1 register pair value increments on every rising edge of clock input on pin RB7/T1OSI/PGD when bit T1OSCEN is set or pin RB6/T1OSO/T1CKI/ PGC when bit T1OSCEN is cleared.

If  $\overline{T1SYNC}$  is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple-counter.

In this configuration, during Sleep mode, the TMR1 register pair value will not increment even if the external clock is present, since the synchronization circuit is shut off. The prescaler however will continue to increment.

#### 7.2.1 EXTERNAL CLOCK INPUT TIMING FOR SYNCHRONIZED COUNTER MODE

When an external clock input is used for Timer1 in Synchronized Counter mode, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of the TMR1 register pair value after synchronization.

When the prescaler is 1:1, the external clock input is the same as the prescaler output. The synchronization of T1CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T1CKI to be high for at least 2 Tosc (and a small RC delay of 20 ns) and low for at least 2 Tosc (and a small RC delay of 20 ns). Refer to Table 17-8 in the Electrical Specifications Section, timing parameters 45, 46 and 47.

When a prescaler other than 1:1 is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. In order for the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for T1CKI to have a period of at least 4 TOSC (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T1CKI high and low time is that they do not violate the minimum pulse width requirements of 10 ns). Refer to the appropriate electrical specifications in Table 17-8, parameters 45, 46 and 47.

#### FIGURE 7-1: TIMER1 BLOCK DIAGRAM

## 7.3 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 7.3.2 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | In Asynchronous Counter mode, Timer1      |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|

|       | cannot be used as a time base for capture |  |  |  |  |  |  |

|       | or compare operations.                    |  |  |  |  |  |  |

#### 7.3.1 EXTERNAL CLOCK INPUT TIMING WITH UNSYNCHRONIZED CLOCK

If control bit  $\overline{\text{T1SYNC}}$  is set, the timer will increment completely asynchronously. The input clock must meet certain minimum high and low time requirements. Refer to Table 17-8 in the Electrical Specifications Section, timing parameters 45, 46 and 47.

#### 7.3.2 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading the TMR1H or TMR1L register, while the timer is running from an external asynchronous clock, will produce a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself poses certain problems since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Example 7-1 is an example routine to read the 16-bit timer value. This is useful if the timer cannot be stopped.

#### EXAMPLE 7-1: READING A 16-BIT FREE-RUNNING TIMER

|   | All inte | rrupts are d | lisabled                |

|---|----------|--------------|-------------------------|

| , | MOVF     | TMR1H, W     |                         |

|   | MOVWF    |              | , kedd high byte        |

|   |          |              |                         |

|   | MOVF     | ,            | ;Read low byte          |

|   | MOVWF    | TMPL         | ;                       |

|   | MOVF     | TMR1H, W     | ;Read high byte         |

|   | SUBWF    | TMPH, W      | ;Sub 1st read with      |

|   |          |              | ;2nd read               |

|   | BTFSC    | STATUS, Z    | ;Is result = 0          |

|   | GOTO     | CONTINUE     | ;Good 16-bit read       |

| ; |          |              |                         |

| ; | TMR1L ma | v have rolle | ed over between the     |

| ; |          | -            | l low bytes. Reading    |

| ' |          | 5            |                         |

| ; | 5        | and low byc  | es now will read a good |

| ; | value.   |              |                         |

| ; |          |              |                         |

|   | MOVF     | TMR1H, W     | ;Read high byte         |

|   | MOVWF    | TMPH         | ;                       |

|   | MOVF     | TMR1L, W     | ;Read low byte          |

|   | MOVWF    | TMPL         | i                       |

| ; | Re-enabl | e the Intern | rupts (if required)     |

|   | ONTINUE  |              | ;Continue with your     |

|   |          |              | ; code                  |

|   |          |              | , coue                  |

#### 9.2.1 CCP PIN CONFIGURATION

The user must configure the RB3/CCP1 pin as an output by clearing the TRISB<3> bit.

| Note: | Clearing the CCP1CON register will force    |

|-------|---------------------------------------------|

|       | the RB3/CCP1 compare output latch to        |

|       | the default low level. This is not the data |

|       | latch.                                      |

#### 9.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 9.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 9.2.4 SPECIAL EVENT TRIGGER

In this mode (CCP1M<3:0>=1011), an internal hardware trigger is generated, which may be used to initiate an action. See Register 9-1.

The special event trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and CCPR1H, CCPR1L register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the TMR1 clock. This allows the CCPR1 register pair to effectively be a 16-bit programmable period register for Timer1. The special event trigger output also starts an A/D conversion provided that the A/D module is enabled.

**Note:** Removing the match condition by changing the contents of the CCPR1H, CCPR1L register pair between the clock edge that generates the special event trigger and the clock edge that generates the TMR1 Reset will preclude the Reset from occuring.

| Address                 | Name    | Bit 7   | Bit 6   | Bit 5          | Bit 4        | Bit 3        | Bit 2        | Bit 1    | Bit 0  | Value on<br>POR |      | all of |      |

|-------------------------|---------|---------|---------|----------------|--------------|--------------|--------------|----------|--------|-----------------|------|--------|------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON  | GIE     | PEIE    | TOIE           | INTE         | RBIE         | TOIF         | INTF     | RBIF   | 0000            | 000x | 0000   | 000u |

| 0Ch                     | PIR1    | EEIF    | CMIF    | RCIF           | TXIF         | _            | CCP1IF       | TMR2IF   | TMR1IF | 0000            | -000 | 0000   | -000 |

| 8Ch                     | PIE1    | EEIE    | CMIE    | RCIE           | TXIE         | _            | CCP1IE       | TMR2IE   | TMR1IE | 0000            | -000 | 0000   | -000 |

| 86h, 186h               | TRISB   | PORTI   | B Data  | Direction R    | egister      |              |              |          |        | 1111            | 1111 | 1111   | 1111 |

| 0Eh                     | TMR1L   | Holding | g Regis | ster for the l | _east Signif | icant Byte o | f the 16-bit | TMR1 Re  | gister | xxxx            | xxxx | uuuu   | uuuu |

| 0Fh                     | TMR1H   | Holding | g Regis | ster for the I | Most Signifi | cant Byte of | the 16-bit   | TMR1 Reg | lister | xxxx            | xxxx | uuuu   | uuuu |

| 10h                     | T1CON   | _       | _       | T1CKPS1        | T1CKPS0      | T10SCEN      | T1SYNC       | TMR1CS   | TMR10N | 00              | 0000 | uu     | uuuu |

| 15h                     | CCPR1L  | Captur  | re/Com  | pare/PWM       | Register1 (I | _SB)         |              |          |        | xxxx            | xxxx | uuuu   | uuuu |

| 16h                     | CCPR1H  | Captur  | e/Com   | pare/PWM       | Register1 (I | MSB)         |              |          |        | xxxx            | xxxx | uuuu   | uuuu |

| 17h                     | CCP1CON | -       | _       | CCP1X          | CCP1Y        | CCP1M3       | CCP1M2       | CCP1M1   | CCP1M0 | 00              | 0000 | 00     | 0000 |

#### TABLE 9-2: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by Capture and Timer1.

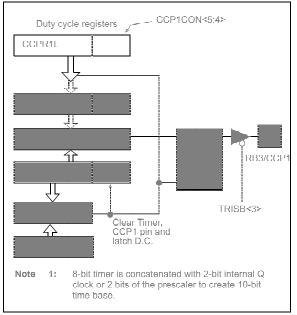

## 9.3 PWM Mode

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTB data latch, the TRISB<3> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force         |

|-------|--------------------------------------------------|

|       | the CCP1 PWM output latch to the default         |

|       | low level. This is not the PORTB I/O data latch. |

Figure 9-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step by step procedure on how to set up the CCP module for PWM operation, see **Section 9.3.3** "**Set-Up for PWM Operation**".

#### FIGURE 9-3: SIMPLIFIED PWM BLOCK DIAGRAM

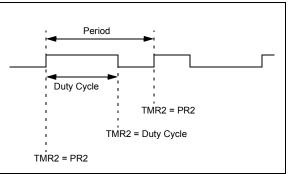

A PWM output (Figure 9-4) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (frequency = 1/period).

FIGURE 9-4: PWM OUTPUT

## 9.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

$$PWM \ period = [(PR2) + 1] \cdot 4 \cdot Tosc \cdot TMR2 \ prescale \\ value$$

PWM frequency is defined as 1/[PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

| BAUD     | Fosc = 20 N | lHz    | SPBRG              | 16 MHz  |        | SPBRG              | 10 MHz |        | SPBRG              |

|----------|-------------|--------|--------------------|---------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD       | ERROR  | value<br>(decimal) | KBAUD   | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 9600     | 9.615       | +0.16% | 129                | 9.615   | +0.16% | 103                | 9.615  | +0.16% | 64                 |

| 19200    | 19.230      | +0.16% | 64                 | 19.230  | +0.16% | 51                 | 18.939 | -1.36% | 32                 |

| 38400    | 37.878      | -1.36% | 32                 | 38.461  | +0.16% | 25                 | 39.062 | +1.7%  | 15                 |

| 57600    | 56.818      | -1.36% | 21                 | 58.823  | +2.12% | 16                 | 56.818 | -1.36% | 10                 |

| 115200   | 113.636     | -1.36% | 10                 | 111.111 | -3.55% | 8                  | 125    | +8.51% | 4                  |

| 250000   | 250         | 0      | 4                  | 250     | 0      | 3                  | NA     |        |                    |

| 625000   | 625         | 0      | 1                  | NA      | _      | _                  | 625    | 0      | 0                  |

| 1250000  | 1250        | 0      | 0                  | NA      | _      | _                  | NA     | _      |                    |

## TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD     | Fosc = 7.16 | MHz    | SPBRG              | 5.068 MHz |         | SPBRG              | 4 MHz    |         | SPBRG              |

|----------|-------------|--------|--------------------|-----------|---------|--------------------|----------|---------|--------------------|

| RATE (K) | KBAUD       | ERROR  | value<br>(decimal) | KBAUD     | ERROR   | value<br>(decimal) | KBAUD    | ERROR   | value<br>(decimal) |

| 9600     | 9.520       | -0.83% | 46                 | 9598.485  | 0.016%  | 32                 | 9615.385 | 0.160%  | 25                 |

| 19200    | 19.454      | +1.32% | 22                 | 18632.35  | -2.956% | 16                 | 19230.77 | 0.160%  | 12                 |

| 38400    | 37.286      | -2.90% | 11                 | 39593.75  | 3.109%  | 7                  | 35714.29 | -6.994% | 6                  |

| 57600    | 55.930      | -2.90% | 7                  | 52791.67  | -8.348% | 5                  | 62500    | 8.507%  | 3                  |

| 115200   | 111.860     | -2.90% | 3                  | 105583.3  | -8.348% | 2                  | 125000   | 8.507%  | 1                  |

| 250000   | NA          |        |                    | 316750    | 26.700% | 0                  | 250000   | 0.000%  | 0                  |

| 625000   | NA          | _      |                    | NA        | _       | _                  | NA       | _       | _                  |

| 1250000  | NA          | _      |                    | NA        | _       | _                  | NA       | _       | _                  |

| BAUD     | Fosc = 3.57 | 9 MHz    | SPBRG              | 1 MHz   |          | SPBRG              | 32.768 kHz |       | SPBRG              |

|----------|-------------|----------|--------------------|---------|----------|--------------------|------------|-------|--------------------|

| RATE (K) | KBAUD       | ERROR    | value<br>(decimal) | KBAUD   | ERROR    | value<br>(decimal) | KBAUD      | ERROR | value<br>(decimal) |

| 9600     | 9725.543    | 1.308%   | 22                 | 8.928   | -6.994%  | 6                  | NA         | NA    | NA                 |

| 19200    | 18640.63    | -2.913%  | 11                 | 20833.3 | 8.507%   | 2                  | NA         | NA    | NA                 |

| 38400    | 37281.25    | -2.913%  | 5                  | 31250   | -18.620% | 1                  | NA         | NA    | NA                 |

| 57600    | 55921.88    | -2.913%  | 3                  | 62500   | +8.507   | 0                  | NA         | NA    | NA                 |

| 115200   | 111243.8    | -2.913%  | 1                  | NA      | _        | _                  | NA         | NA    | NA                 |

| 250000   | 223687.5    | -10.525% | 0                  | NA      | _        | _                  | NA         | NA    | NA                 |

| 625000   | NA          | _        | _                  | NA      | _        | _                  | NA         | NA    | NA                 |

| 1250000  | NA          | _        | _                  | NA      | _        | _                  | NA         | NA    | NA                 |

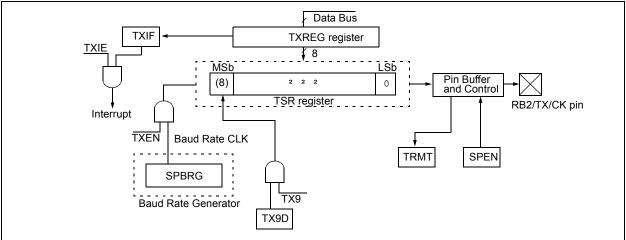

#### FIGURE 12-1: USART TRANSMIT BLOCK DIAGRAM

Follow these steps when setting up an Asynchronous Transmission:

- TRISB<1> and TRISB<2> should both be set to '1' to configure the RB1/RX/DT and RB2/TX/CK pins as inputs. Output drive, when required, is controlled by the peripheral circuitry.

- Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH. (Section 12.1 "USART Baud Rate Generator (BRG)").

- 3. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 4. If interrupts are desired, then set enable bit TXIE.

- 5. If 9-bit transmission is desired, then set transmit bit TX9.

- 6. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 8. Load data to the TXREG register (starts transmission).

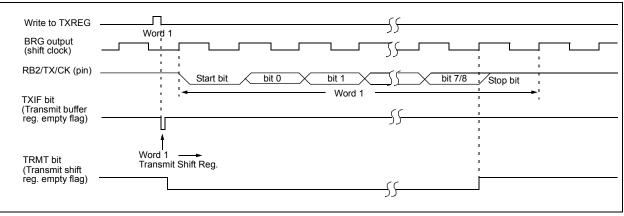

#### FIGURE 12-2: ASYNCHRONOUS TRANSMISSION

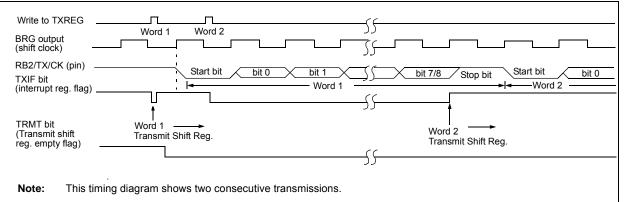

#### FIGURE 12-3: ASYNCHRONOUS TRANSMISSION (BACK TO BACK)

#### TABLE 12-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address | Name  | Bit 7                            | Bit 6    | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>all other<br>Resets |

|---------|-------|----------------------------------|----------|------------|-------|-------|--------|--------|--------|-----------------|---------------------------------|

| 0Ch     | PIR1  | EEIF                             | CMIF     | RCIF       | TXIF  |       | CCP1IF | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                       |

| 18h     | RCSTA | SPEN                             | RX9      | SREN       | CREN  | ADEN  | FERR   | OERR   | RX9D   | x000 0000       | 0000 000x                       |

| 19h     | TXREG | REG USART Transmit Data Register |          |            |       |       |        |        |        | 0000 0000       | 0000 0000                       |

| 8Ch     | PIE1  | EEIE                             | CMIE     | RCIE       | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                       |

| 98h     | TXSTA | CSRC                             | TX9      | TXEN       | SYNC  |       | BRGH   | TRMT   | TX9D   | 0000 -010       | 0000 -010                       |

| 99h     | SPBRG | Baud Rate                        | Generato | r Register | r     |       |        |        |        | 0000 0000       | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'.

Shaded cells are not used for Asynchronous Transmission.

#### 12.4.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>) or enable bit CREN (RCSTA<4>). Data is sampled on the RB1/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read-only bit which is reset by the hardware. In this case, it is reset when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a twodeep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full, then overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited, so it is essential to clear bit OERR if it is set. The 9th receive bit is buffered the same way as the receive data. Reading the RCREG register, will load bit RX9D with a new value, therefore it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old RX9D information.

Follow these steps when setting up a Synchronous Master Reception:

- 1. TRISB<1> and TRISB<2> should both be set to '1' to configure the RB1/RX/DT and RB2/TX/CK pins as inputs. Output drive, when required, is controlled by the peripheral circuitry.

- Initialize the SPBRG register for the appropriate baud rate. (Section 12.1 "USART Baud Rate Generator (BRG)").

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, then set enable bit RCIE.

- 6. If 9-bit reception is desired, then set bit RX9.

- 7. If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an OERR error occurred, clear the error by clearing bit CREN.

| Address | Name  | Bit 7   | Bit 6                        | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on:<br>POR | Value on all other Resets |

|---------|-------|---------|------------------------------|-------|-------|-------|--------|--------|-----------|------------------|---------------------------|

| 0Ch     | PIR1  | EEIF    | CMIF                         | RCIF  | TXIF  |       | CCP1IF | TMR2IF | TMR1IF    | 0000 -000        | 0000 -000                 |

| 18h     | RCSTA | SPEN    | RX9                          | SREN  | CREN  | ADEN  | FERR   | OERR   | RX9D      | 0000 000x        | 0000 000x                 |

| 1Ah     | RCREG | USART F | USART Receive Data Register  |       |       |       |        |        |           | 0000 0000        | 0000 0000                 |

| 8Ch     | PIE1  | EPIE    | CMIE                         | RCIE  | TXIE  | -     | CCP1IE | TMR2IE | TMR1IE    | -000 0000        | -000 -000                 |

| 98h     | TXSTA | CSRC    | TX9                          | TXEN  | SYNC  | _     | BRGH   | TRMT   | TX9D      | 0000 -010        | 0000 -010                 |

| 99h     | SPBRG | Baud Ra | Baud Rate Generator Register |       |       |       |        |        | 0000 0000 | 0000 0000        |                           |

#### TABLE 12-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous master reception.

## 13.8 Data EEPROM Operation During Code-Protect

When the device is code-protected, the CPU is able to read and write data to the data EEPROM.

#### TABLE 13-1: REGISTERS/BITS ASSOCIATED WITH DATA EEPROM

| Address | Name                  | Bit 7 | Bit 6                    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other<br>Resets |

|---------|-----------------------|-------|--------------------------|-------|-------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| 9Ah     | EEDATA                | EEPRO | EPROM Data Register      |       |       |       |       |       |       | xxxx xxxx                     | uuuu uuuu                       |

| 9Bh     | EEADR                 | EEPRO | EEPROM Address Register  |       |       |       |       |       |       | xxxx xxxx                     | uuuu uuuu                       |

| 9Ch     | EECON1                | _     | _                        | —     | —     | WRERR | WREN  | WR    | RD    | x000                          | q000                            |

| 9Dh     | EECON2 <sup>(1)</sup> | EEPRO | EPROM Control Register 2 |       |       |       |       |       |       |                               |                                 |

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by data EEPROM.

**Note 1:** EECON2 is not a physical register.

## 14.2 Oscillator Configurations

#### 14.2.1 OSCILLATOR TYPES

The PIC16F627A/628A/648A can be operated in eight different oscillator options. The user can program three configuration bits (FOSC2 through FOSC0) to select one of these eight modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC External Resistor/Capacitor (2 modes)

- INTOSC Internal Precision Oscillator (2 modes)

- EC External Clock In

## 14.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

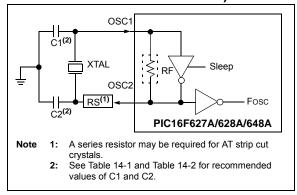

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (Figure 14-1). The PIC16F627A/628A/648A oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (Figure 14-4).

#### FIGURE 14-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

## TABLE 14-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| Mode | Freq     | OSC1(C1)  | OSC2(C2)  |

|------|----------|-----------|-----------|

| XT   | 455 kHz  | 22-100 pF | 22-100 pF |

|      | 2.0 MHz  | 15-68 pF  | 15-68 pF  |

|      | 4.0 MHz  | 15-68 pF  | 15-68 pF  |

| HS   | 8.0 MHz  | 10-68 pF  | 10-68 pF  |

|      | 16.0 MHz | 10-22 pF  | 10-22 pF  |

|      |          |           |           |

**Note:** Higher capacitance increases the stability of the oscillator, but also increases the start-up time. These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

#### TABLE 14-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Mode | Freq    | OSC1(C1)  | OSC2(C2)   |

|------|---------|-----------|------------|

| LP   | 32 kHz  | 15-30 pF  | 15-30 pF   |

|      | 200 kHz | 0-15 pF   | 0-15 pF    |

| XT   | 100 kHz | 68-150 pF | 150-200 pF |

|      | 2 MHz   | 15-30 pF  | 15-30 pF   |

|      | 4 MHz   | 15-30 pF  | 15-30 pF   |

| HS   | 8 MHz   | 15-30 pF  | 15-30 pF   |

|      | 10 MHz  | 15-30 pF  | 15-30 pF   |

|      | 20 MHz  | 15-30 pF  | 15-30 pF   |

**Note:** Higher capacitance increases the stability of the oscillator, but also increases the start-up time. These values are for design guidance only. A series resistor (RS) may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

#### 14.4.5 TIME OUT SEQUENCE

On power-up, the time out sequence is as follows: First PWRT time-out is invoked after POR has expired. Then OST is activated. The total time out will vary based on oscillator configuration and <u>PWRTE</u> bit Status. For example, in RC mode with <u>PWRTE</u> bit set (PWRT disabled), there will be no time out at all. Figure 14-8, Figure 14-11 and Figure 14-12 depict time out sequences.

Since the time outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 14-11). This is useful for testing purposes or to synchronize more than one PIC16F627A/628A/ 648A device operating in parallel.

Table 14-6 shows the Reset conditions for some special registers, while Table 14-7 shows the Reset conditions for all the registers.

#### 14.4.6 POWER CONTROL (PCON) STATUS REGISTER

The PCON/Status register, PCON (address 8Eh), has two bits.

Bit 0 is  $\overline{\text{BOR}}$  (Brown-out Reset).  $\overline{\text{BOR}}$  is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if  $\overline{\text{BOR}} = 0$ indicating that a brown-out has occurred. The  $\overline{\text{BOR}}$ Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (by setting BOREN bit = 0 in the Configuration Word).

Bit 1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent Reset if POR is '0', it will indicate that a Power-on Reset must have occurred (VDD may have gone too low).

| Oscillator Configuration | Power-u              | ıp Timer         | Brown-o              | Wake-up from     |           |

|--------------------------|----------------------|------------------|----------------------|------------------|-----------|

| Oscillator Configuration | <b>PWRTE</b> = 0     | <b>PWRTE</b> = 1 | <b>PWRTE</b> = 0     | <b>PWRTE</b> = 1 | Sleep     |

| XT, HS, LP               | 72 ms +<br>1024•Tosc | 1024•Tosc        | 72 ms +<br>1024•Tosc | 1024•Tosc        | 1024•Tosc |

| RC, EC                   | 72 ms                | —                | 72 ms                | _                | —         |

| INTOSC                   | 72 ms                | —                | 72 ms                | —                | 6 μs      |

| TABLE 14-3. THE OUT IN VARIOUS SITUATIONS | TABLE 14-3: | TIME OUT IN VARIOUS SITUATIONS |

|-------------------------------------------|-------------|--------------------------------|

|-------------------------------------------|-------------|--------------------------------|

## TABLE 14-4: STATUS/PCON BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD | Condition                          |

|-----|-----|----|----|------------------------------------|

| 0   | Х   | 1  | 1  | Power-on Reset                     |

| 0   | Х   | 0  | Х  | Illegal, TO is set on POR          |

| 0   | Х   | Х  | 0  | Illegal, PD is set on POR          |

| 1   | 0   | Х  | Х  | Brown-out Reset                    |

| 1   | 1   | 0  | u  | WDT Reset                          |

| 1   | 1   | 0  | 0  | WDT Wake-up                        |

| 1   | 1   | u  | u  | MCLR Reset during normal operation |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep            |

**Legend:** u = unchanged, x = unknown

| INCF                              | Increme                                                               | nt f                                  |                                           |                |           | INCFSZ                                                          | Increm                                                                                                                                                                                                                                                                                                                                     | ent f, Sk                 | tip if 0 |               |

|-----------------------------------|-----------------------------------------------------------------------|---------------------------------------|-------------------------------------------|----------------|-----------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------|---------------|

| Syntax:                           | [ <i>label</i> ] INCF f,d                                             |                                       |                                           | I              | Syntax:   | [label] INCFSZ f,d                                              |                                                                                                                                                                                                                                                                                                                                            |                           |          |               |

| Operands:                         | $0 \le f \le 127$<br>d $\in [0,1]$                                    |                                       |                                           |                | Operands: | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$ |                                                                                                                                                                                                                                                                                                                                            |                           |          |               |

| Operation:                        | (f) + 1 →                                                             | (dest)                                |                                           |                |           | Operation:                                                      | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                                           |                           |          |               |

| Status Affected:                  | Z                                                                     |                                       |                                           |                |           | Status Affected:                                                | None                                                                                                                                                                                                                                                                                                                                       |                           |          |               |

| Encoding:                         | 00                                                                    | 1010                                  | dfff                                      | ffff           |           | Encoding:                                                       | 00                                                                                                                                                                                                                                                                                                                                         | 1111                      | dfff     | ffff          |

| Description:<br>Words:<br>Cycles: | The cont<br>incremer<br>result is p<br>If 'd' is '1<br>back in r<br>1 | nted. If '<br>placed in<br>.', the re | d' is 'o', t<br>n the W re<br>sult is pla | he<br>egister. |           | Description:                                                    | The contents of register 'f' are<br>incremented. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is placed<br>back in register 'f'.<br>If the result is '0', the next<br>instruction, which is already<br>fetched, is discarded. A NOP is<br>executed instead making it a<br>two-cycle instruction. |                           |          |               |

| Example                           | INCF<br>Before Ir                                                     | REG1,                                 |                                           |                |           |                                                                 |                                                                                                                                                                                                                                                                                                                                            |                           |          |               |