Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f648a-e-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, PIC<sup>32</sup> logo, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2009, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.

# 18-pin Flash-Based, 8-Bit CMOS Microcontrollers with nanoWatt Technology

## **High-Performance RISC CPU:**

- Operating speeds from DC 20 MHz

- · Interrupt capability

- 8-level deep hardware stack

- Direct, Indirect and Relative Addressing modes

- 35 single-word instructions:

- All instructions single cycle except branches

### **Special Microcontroller Features:**

- · Internal and external oscillator options:

- Precision internal 4 MHz oscillator factory calibrated to  $\pm 1\%$

- Low-power internal 48 kHz oscillator

- External Oscillator support for crystals and resonators

- Power-saving Sleep mode

- · Programmable weak pull-ups on PORTB

- Multiplexed Master Clear/Input-pin

- Watchdog Timer with independent oscillator for reliable operation

- Low-voltage programming

- In-Circuit Serial Programming<sup>™</sup> (via two pins)

- Programmable code protection

- Brown-out Reset

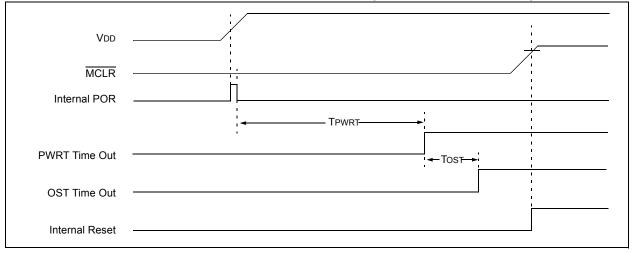

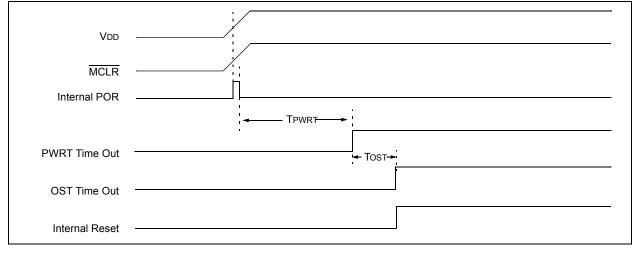

- Power-on Reset

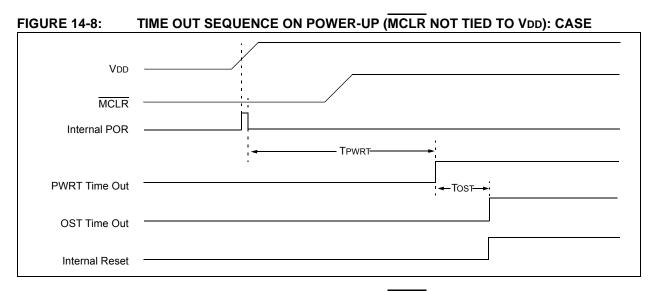

- · Power-up Timer and Oscillator Start-up Timer

- Wide operating voltage range (2.0-5.5V)

- Industrial and extended temperature range

- High-Endurance Flash/EEPROM cell:

- 100,000 write Flash endurance

- 1,000,000 write EEPROM endurance

- 40 year data retention

### Low-Power Features:

- · Standby Current:

- 100 nA @ 2.0V, typical

- · Operating Current:

- 12 μA @ 32 kHz, 2.0V, typical

- 120 μA @ 1 MHz, 2.0V, typical

- Watchdog Timer Current:

- 1 μA @ 2.0V, typical

- Timer1 Oscillator Current:

- 1.2 μA @ 32 kHz, 2.0V, typical

- Dual-speed Internal Oscillator:

- Run-time selectable between 4 MHz and 48 kHz

- 4 µs wake-up from Sleep, 3.0V, typical

# **Peripheral Features:**

- 16 I/O pins with individual direction control

- High current sink/source for direct LED drive

- · Analog comparator module with:

- Two analog comparators

- Programmable on-chip voltage reference (VREF) module

- Selectable internal or external reference

- Comparator outputs are externally accessible

- Timer0: 8-bit timer/counter with 8-bit programmable prescaler

- Timer1: 16-bit timer/counter with external crystal/ clock capability

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

- · Capture, Compare, PWM module:

- 16-bit Capture/Compare

- 10-bit PWM

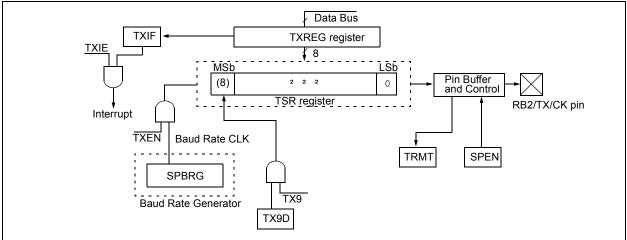

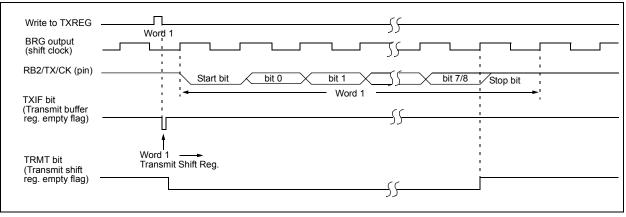

- Addressable Universal Synchronous/Asynchronous Receiver/Transmitter USART/SCI

| Device     | Program<br>Memory | Data N          | lemory            | CCP |       | USART | Compositoro | Timers   |

|------------|-------------------|-----------------|-------------------|-----|-------|-------|-------------|----------|

|            | Flash<br>(words)  | SRAM<br>(bytes) | EEPROM<br>(bytes) | I/O | (PWM) | USART | Comparators | 8/16-bit |

| PIC16F627A | 1024              | 224             | 128               | 16  | 1     | Y     | 2           | 2/1      |

| PIC16F628A | 2048              | 224             | 128               | 16  | 1     | Y     | 2           | 2/1      |

| PIC16F648A | 4096              | 256             | 256               | 16  | 1     | Y     | 2           | 2/1      |

| Name                                                  | Function | Input Type | Output Type | Description                                                                                                                                                          |

|-------------------------------------------------------|----------|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RA0/AN0                                               | RA0      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                               |

|                                                       | AN0      | AN         | —           | Analog comparator input                                                                                                                                              |

| RA1/AN1                                               | RA1      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                               |

|                                                       | AN1      | AN         | _           | Analog comparator input                                                                                                                                              |

| RA2/AN2/VREF                                          | RA2      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                               |

|                                                       | AN2      | AN         |             | Analog comparator input                                                                                                                                              |

|                                                       | VREF     | —          | AN          | VREF output                                                                                                                                                          |

| RA3/AN3/CMP1                                          | RA3      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                               |

|                                                       | AN3      | AN         |             | Analog comparator input                                                                                                                                              |

|                                                       | CMP1     | —          | CMOS        | Comparator 1 output                                                                                                                                                  |

| RA4/T0CKI/CMP2                                        | RA4      | ST         | OD          | Bidirectional I/O port                                                                                                                                               |

|                                                       | TOCKI    | ST         | _           | Timer0 clock input                                                                                                                                                   |

|                                                       | CMP2     | _          | OD          | Comparator 2 output                                                                                                                                                  |

| RA5/MCLR/VPP                                          | RA5      | ST         | _           | Input port                                                                                                                                                           |

|                                                       | MCLR     | ST         | _           | Master clear. When configured as MCLR, th<br>pin is an active low Reset to the device.<br>Voltage on MCLR/VPP must not exceed VDr<br>during normal device operation. |

|                                                       | VPP      | —          | —           | Programming voltage input                                                                                                                                            |

| RA6/OSC2/CLKOUT                                       | RA6      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                               |

|                                                       | OSC2     | —          | XTAL        | Oscillator crystal output. Connects to crystal<br>or resonator in Crystal Oscillator mode.                                                                           |

|                                                       | CLKOUT   |            | CMOS        | In RC/INTOSC mode, OSC2 pin can output<br>CLKOUT, which has 1/4 the frequency of<br>OSC1.                                                                            |

| RA7/OSC1/CLKIN                                        | RA7      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                               |

|                                                       | OSC1     | XTAL       | —           | Oscillator crystal input                                                                                                                                             |

|                                                       | CLKIN    | ST         | —           | External clock source input. RC biasing pin.                                                                                                                         |

| RB0/INT                                               | RB0      | TTL        | CMOS        | Bidirectional I/O port. Can be software<br>programmed for internal weak pull-up.                                                                                     |

|                                                       | INT      | ST         | —           | External interrupt                                                                                                                                                   |

| RB1/RX/DT                                             | RB1      | TTL        | CMOS        | Bidirectional I/O port. Can be software programmed for internal weak pull-up.                                                                                        |

|                                                       | RX       | ST         | —           | USART receive pin                                                                                                                                                    |

|                                                       | DT       | ST         | CMOS        | Synchronous data I/O                                                                                                                                                 |

| RB2/TX/CK                                             | RB2      | TTL        | CMOS        | Bidirectional I/O port. Can be software programmed for internal weak pull-up.                                                                                        |

|                                                       | ТХ       |            | CMOS        | USART transmit pin                                                                                                                                                   |

|                                                       | CK       | ST         | CMOS        | Synchronous clock I/O                                                                                                                                                |

| RB3/CCP1                                              | RB3      | TTL        | CMOS        | Bidirectional I/O port. Can be software programmed for internal weak pull-up.                                                                                        |

|                                                       | CCP1     | ST         | CMOS        | Capture/Compare/PWM I/O                                                                                                                                              |

| Legend: O = Output<br>— = Not used<br>TTL = TTL Input |          | I = Ir     | MOS Output  | P = Power<br>ST = Schmitt Trigger Input<br>AN = Analog                                                                                                               |

#### TABLE 3-2: PIC16F627A/628A/648A PINOUT DESCRIPTION

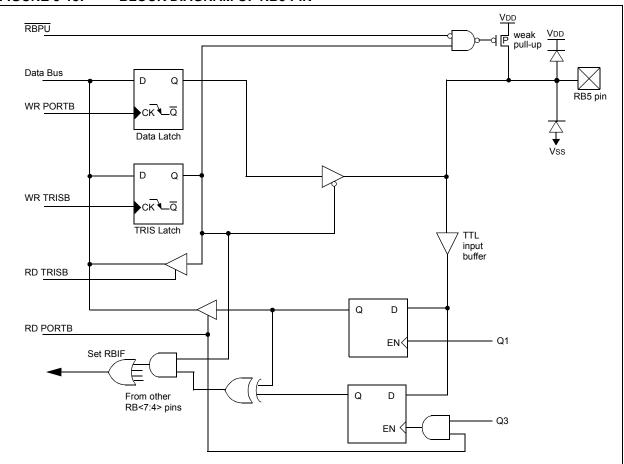

# 5.0 I/O PORTS

The PIC16F627A/628A/648A have two ports, PORTA and PORTB. Some pins for these I/O ports are multiplexed with alternate functions for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

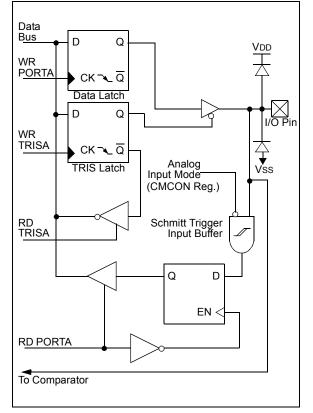

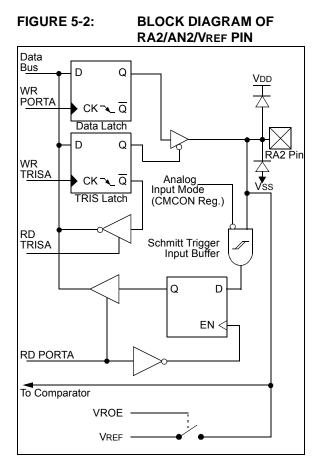

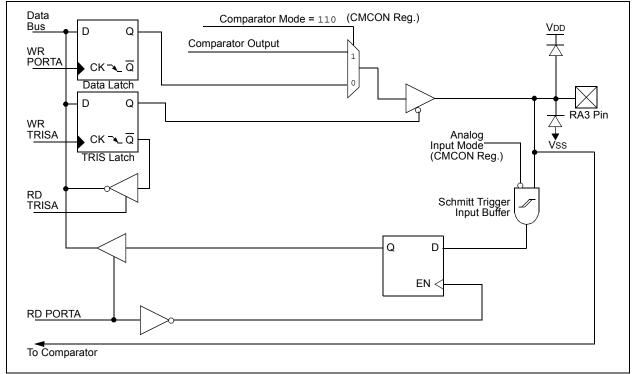

## 5.1 PORTA and TRISA Registers

PORTA is an 8-bit wide latch. RA4 is a Schmitt Trigger input and an open drain output. Port RA4 is multiplexed with the T0CKI clock input. RA5<sup>(1)</sup> is a Schmitt Trigger input only and has no output drivers. All other RA port pins have Schmitt Trigger input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as input or output.

A '1' in the TRISA register puts the corresponding output driver in a High-impedance mode. A '0' in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

The PORTA pins are multiplexed with comparator and voltage reference functions. The operation of these pins are selected by control bits in the CMCON (Comparator Control register) register and the VRCON (Voltage Reference Control register) register. When selected as a comparator input, these pins will read as '0's.

- Note 1: RA5 shares function with VPP. When VPP voltage levels are applied to RA5, the device will enter Programming mode.

- 2: On Reset, the TRISA register is set to all inputs. The digital inputs (RA<3:0>) are disabled and the comparator inputs are forced to ground to reduce current consumption.

- 3: TRISA<6:7> is overridden by oscillator configuration. When PORTA<6:7> is overridden, the data reads '0' and the TRISA<6:7> bits are ignored.

TRISA controls the direction of the RA pins, even when they are being used as comparator inputs. The user must make sure to keep the pins configured as inputs when using them as comparator inputs.

The RA2 pin will also function as the output for the voltage reference. When in this mode, the VREF pin is a very high-impedance output. The user must configure TRISA<2> bit as an input and use high-impedance loads.

In one of the comparator modes defined by the CMCON register, pins RA3 and RA4 become outputs of the comparators. The TRISA<4:3> bits must be cleared to enable outputs to use this function.

#### EXAMPLE 5-1: INITIALIZING PORTA

| CLRF  | PORTA   | ;Initialize PORTA by<br>;setting |

|-------|---------|----------------------------------|

|       |         | , 5                              |

|       |         | ;output data latches             |

| MOVLW | 0x07    | ;Turn comparators off and        |

| MOVWF | CMCON   | ;enable pins for I/O             |

|       |         | ;functions                       |

| BCF   | STATUS, | RP1                              |

| BSF   | STATUS, | RP0;Select Bank1                 |

| MOVLW | 0x1F    | ;Value used to initialize        |

|       |         | ;data direction                  |

| MOVWF | TRISA   | ;Set RA<4:0> as inputs           |

|       |         | ;TRISA<5> always                 |

|       |         | ;read as `1'.                    |

|       |         | ;TRISA<7:6>                      |

|       |         | ;depend on oscillator            |

|       |         | ;mode                            |

|       |         |                                  |

FIGURE 5-1:

#### BLOCK DIAGRAM OF RA0/AN0:RA1/AN1 PINS

#### FIGURE 5-3: BLOCK DIAGRAM OF THE RA3/AN3/CMP1 PIN

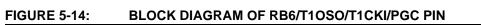

#### FIGURE 5-13: BLOCK DIAGRAM OF RB5 PIN

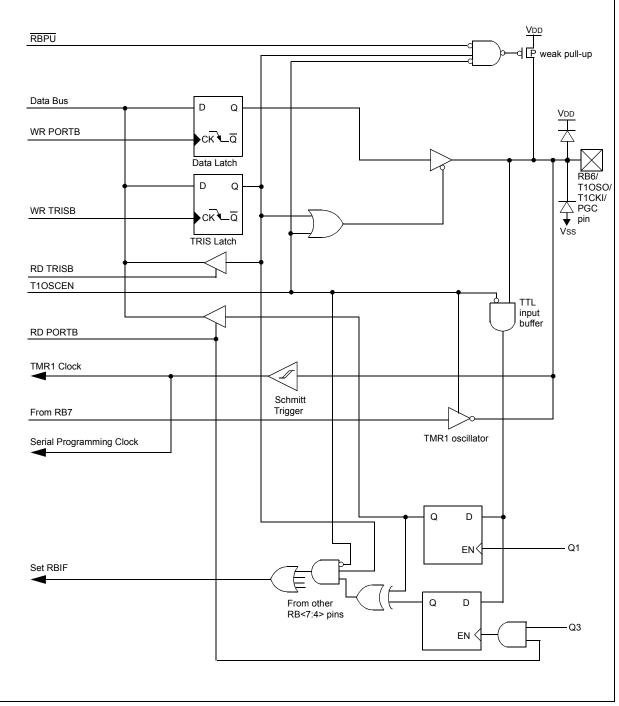

### 6.3 Timer0 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer. A prescaler assignment for the Timer0 module means that there is no postscaler for the Watchdog Timer, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x...etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

FIGURE 6-1: BLOCK DIAGRAM OF THE TIMER0/WDT

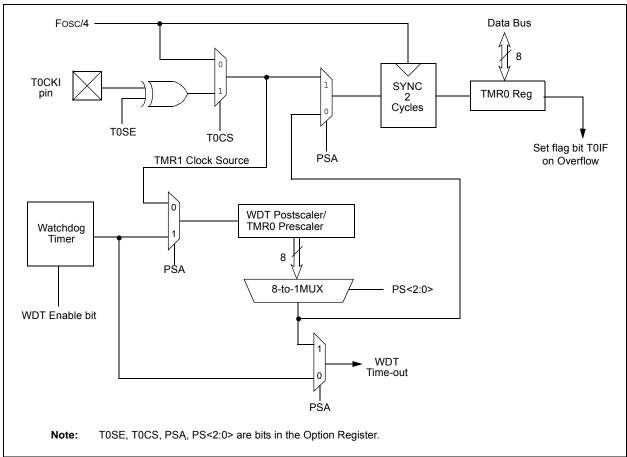

# 7.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L) which are readable and writable. The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The Timer1 Interrupt, if enabled, is generated on overflow of the TMR1 register pair which latches the interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing the Timer1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- As a timer

- As a counter

The Operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

-n = Value at POR

In Timer mode, the TMR1 register pair value increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "Reset input". This Reset can be generated by the CCP module (Section 9.0 "Capture/Compare/PWM (CCP) Module"). Register 7-1 shows the Timer1 control register.

For the PIC16F627A/628A/648A, when the Timer1 oscillator is enabled (T1OSCEN is set), the RB7/T1OSI/PGD and RB6/T1OSO/T1CKI/PGC pins become inputs. That is, the TRISB<7:6> value is ignored.

| TER 7-1: | T1CON – TIN                                                                                    | IER1 C                 | ONTROLI         | REGISTER       | (ADDRESS:       | 10h)        |                |             |

|----------|------------------------------------------------------------------------------------------------|------------------------|-----------------|----------------|-----------------|-------------|----------------|-------------|

|          | U-0                                                                                            | U-0                    | R/W-0           | R/W-0          | R/W-0           | R/W-0       | R/W-0          | R/W-0       |

|          | —                                                                                              |                        | T1CKPS1         | T1CKPS0        | T1OSCEN         | T1SYNC      | TMR1CS         | TMR10N      |

|          | bit 7                                                                                          |                        |                 |                |                 |             |                | bit 0       |

| bit 7-6  | Unimplement                                                                                    | ed: Read               | <b>d as</b> 'o' |                |                 |             |                |             |

| bit 5-4  | T1CKPS<1:0>                                                                                    | : Timer1               | Input Clock     | k Prescale Se  | elect bits      |             |                |             |

|          | 11 = 1:8 Preso<br>10 = 1:4 Preso<br>01 = 1:2 Preso<br>00 = 1:1 Preso                           | cale valu<br>cale valu | e               |                |                 |             |                |             |

| bit 3    | T1OSCEN: Tir                                                                                   | mer1 Oso               | cillator Enat   | ole Control bi | t               |             |                |             |

|          | 1 = Oscillator i<br>0 = Oscillator i                                                           |                        |                 |                |                 |             |                |             |

| bit 2    | T1SYNC: Time                                                                                   | er1 Exter              | nal Clock Ir    | nput Synchro   | nization Contro | ol bit      |                |             |

|          | <u>TMR1CS = 1</u><br>1 = Do not syr<br>0 = Synchroniz<br><u>TMR1CS = 0</u><br>This bit is igno | ze exterr              | al clock inp    | out            | ck when TMR1    | CS = 0.     |                |             |

| bit 1    | TMR1CS: Tim                                                                                    | er1 Cloc               | k Source Se     | elect bit      |                 |             |                |             |

|          | 1 = External cl<br>0 = Internal clo                                                            |                        |                 | 10SO/T1CKI     | /PGC (on the r  | ising edge  | )              |             |

| bit 0    | TMR1ON: Tim                                                                                    | er1 On b               | bit             |                |                 |             |                |             |

|          | 1 = Enables T<br>0 = Stops Time                                                                |                        |                 |                |                 |             |                |             |

|          | Note 1: Th                                                                                     | e oscillat             | tor inverter a  | and feedback   | resistor are tu | rned off to | eliminate po   | ower drain. |

|          | Legend:                                                                                        |                        |                 |                |                 |             |                |             |

|          | R = Readable                                                                                   | bit                    | VV = V          | Vritable bit   | U = Unimple     | emented bi  | it, read as '( | <b>)</b> '  |

'1' = Bit is set

'0' = Bit is cleared

REGISTER 7-1: T1CON – TIMER1 CONTROL REGISTER (ADDRESS: 10h)

x = Bit is unknown

# 7.1 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect since the internal clock is always in sync.

#### 7.2 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode, the TMR1 register pair value increments on every rising edge of clock input on pin RB7/T1OSI/PGD when bit T1OSCEN is set or pin RB6/T1OSO/T1CKI/ PGC when bit T1OSCEN is cleared.

If  $\overline{T1SYNC}$  is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple-counter.

In this configuration, during Sleep mode, the TMR1 register pair value will not increment even if the external clock is present, since the synchronization circuit is shut off. The prescaler however will continue to increment.

#### 7.2.1 EXTERNAL CLOCK INPUT TIMING FOR SYNCHRONIZED COUNTER MODE

When an external clock input is used for Timer1 in Synchronized Counter mode, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of the TMR1 register pair value after synchronization.

When the prescaler is 1:1, the external clock input is the same as the prescaler output. The synchronization of T1CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T1CKI to be high for at least 2 Tosc (and a small RC delay of 20 ns) and low for at least 2 Tosc (and a small RC delay of 20 ns). Refer to Table 17-8 in the Electrical Specifications Section, timing parameters 45, 46 and 47.

When a prescaler other than 1:1 is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. In order for the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for T1CKI to have a period of at least 4 TOSC (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T1CKI high and low time is that they do not violate the minimum pulse width requirements of 10 ns). Refer to the appropriate electrical specifications in Table 17-8, parameters 45, 46 and 47.

#### FIGURE 7-1: TIMER1 BLOCK DIAGRAM

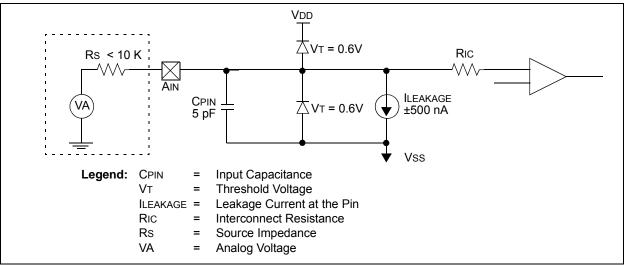

#### FIGURE 10-4: ANALOG INPUT MODE

| Address                 | Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>Resets |

|-------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 1Fh                     | CMCON  | C2OUT  | C10UT  | C2INV  | C1NV   | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE    | PEIE   | T0IE   | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 0Ch                     | PIR1   | EEIF   | CMIF   | RCIF   | TXIF   | _      | CCP1IF | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                       |

| 8Ch                     | PIE1   | EEIE   | CMIE   | RCIE   | TXIE   | _      | CCP1IE | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                       |

| 85h                     | TRISA  | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

**Legend:** x = Unknown, u = Unchanged, - = Unimplemented, read as '0'

| TER 12-2: | RCSTA – RECEIVE STATUS AND CONTROL REGISTER (ADDRESS: 18h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |            |              |           |            |                  |       |  |  |  |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|--------------|-----------|------------|------------------|-------|--|--|--|--|

|           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0        | R/W-0      | R/W-0        | R/W-0     | R-0        | R-0              | R-x   |  |  |  |  |

|           | SPEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RX9          | SREN       | CREN         | ADEN      | FERR       | OERR             | RX9D  |  |  |  |  |

|           | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |            |              |           |            |                  | bit 0 |  |  |  |  |

| bit 7     | SPEN: Serial Port Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |            |              |           |            |                  |       |  |  |  |  |

|           | (Configures RB1/RX/DT and RB2/TX/CK pins as serial port pins when bits TRISB<2:1> are set)<br>1 = Serial port enabled<br>0 = Serial port disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |            |              |           |            |                  |       |  |  |  |  |

| bit 6     | <b>RX9</b> : 9-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Receive En   | able bit   |              |           |            |                  |       |  |  |  |  |

|           | <ul> <li>1 = Selects 9-bit reception</li> <li>0 = Selects 8-bit reception</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |            |              |           |            |                  |       |  |  |  |  |

| bit 5     | SREN: Sin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | gle Receive  | Enable bit |              |           |            |                  |       |  |  |  |  |

|           | Asynchronous mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |            |              |           |            |                  |       |  |  |  |  |

|           | Don't care<br>Synchronous mode - master:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |            |              |           |            |                  |       |  |  |  |  |

|           | <u>Synchronous mode - master:</u><br>1 = Enables single receive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |            |              |           |            |                  |       |  |  |  |  |

|           | 0 = Disables single receive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |            |              |           |            |                  |       |  |  |  |  |

|           | This bit is cleared after reception is complete.<br>Synchronous mode - slave:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |            |              |           |            |                  |       |  |  |  |  |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | in this mode |            |              |           |            |                  |       |  |  |  |  |