Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f648a-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

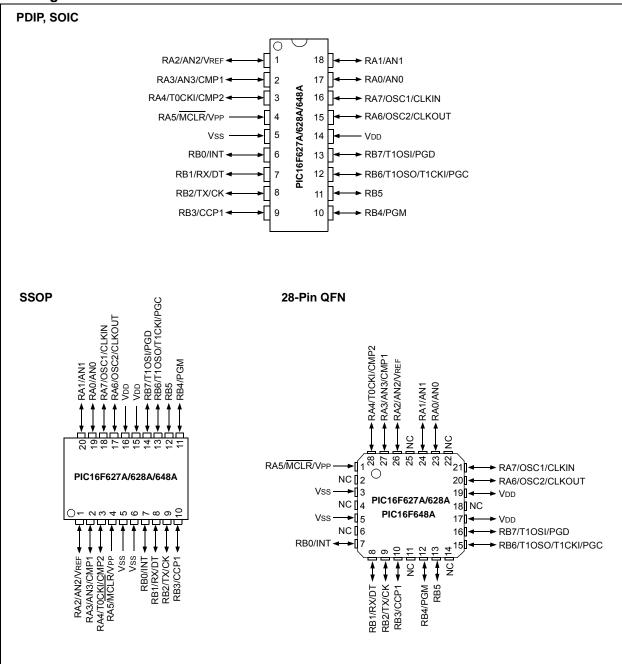

## **Pin Diagrams**

### **Table of Contents**

| 1.0 General Description                                                     | 7    |

|-----------------------------------------------------------------------------|------|

| 2.0 PIC16F627A/628A/648A Device Varieties                                   | 9    |

| 3.0 Architectural Overview                                                  | . 11 |

| 4.0 Memory Organization                                                     | 17   |

| 5.0 I/O Ports                                                               |      |

| 6.0 Timer0 Module                                                           | 47   |

| 7.0 Timer1 Module                                                           | 50   |

| 8.0 Timer2 Module                                                           | . 54 |

| 9.0 Capture/Compare/PWM (CCP) Module                                        | . 57 |

| 10.0 Comparator Module                                                      | . 63 |

| 11.0 Voltage Reference Module                                               | . 69 |

| 12.0 Universal Synchronous Asynchronous Receiver Transmitter (USART) Module |      |

| 13.0 Data EEPROM Memory                                                     | 91   |

| 14.0 Special Features of the CPU                                            |      |

| 15.0 Instruction Set Summary                                                | 117  |

| 16.0 Development Support                                                    | 131  |

| 17.0 Electrical Specifications                                              | 135  |

| 18.0 DC and AC Characteristics Graphs and Tables                            | 151  |

| 19.0 Packaging Information                                                  | 163  |

| Appendix A: Data Sheet Revision History                                     | 171  |

| Appendix B: Device Differences                                              | 171  |

| Appendix C: Device Migrations                                               | 172  |

| Appendix D: Migrating from other PIC <sup>®</sup> Devices                   | 172  |

| The Microchip Web Site                                                      | 173  |

| Customer Change Notification Service                                        | 173  |

| Customer Support                                                            | 173  |

| Reader Response                                                             |      |

| Product Identification System                                               | 179  |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

- To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

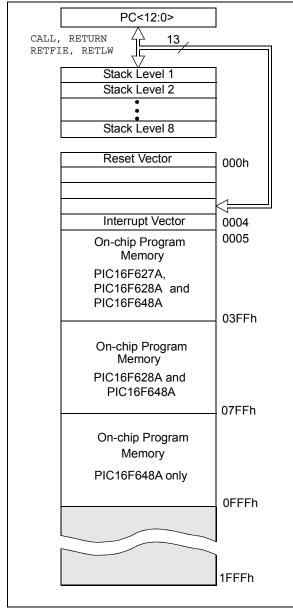

# 4.0 MEMORY ORGANIZATION

## 4.1 Program Memory Organization

The PIC16F627A/628A/648A has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 1K x 14 (0000h-03FFh) for the PIC16F627A, 2K x 14 (0000h-07FFh) for the PIC16F628A and 4K x 14 (0000h-0FFFh) for the PIC16F648A are physically implemented. Accessing a location above these boundaries will cause a wraparound within the first 1K x 14 space (PIC16F627A), 2K x 14 space (PIC16F628A) or 4K x 14 space (PIC16F648A). The Reset vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1).

## 4.2 Data Memory Organization

The data memory (Figure 4-2 and Figure 4-3) is partitioned into four banks, which contain the General Purpose Registers (GPRs) and the Special Function Registers (SFRs). The SFRs are located in the first 32 locations of each bank. There are General Purpose Registers implemented as static RAM in each bank. Table 4-1 lists the General Purpose Register available in each of the four banks.

| TABLE 4-1: | GENERAL PURPOSE STATIC |

|------------|------------------------|

|            | RAM REGISTERS          |

|       | PIC16F627A/628A      | PIC16F648A |

|-------|----------------------|------------|

| Bank0 | 20-7Fh               | 20-7Fh     |

| Bank1 | A0h-FF               | A0h-FF     |

| Bank2 | 120h-14Fh, 170h-17Fh | 120h-17Fh  |

| Bank3 | 1F0h-1FFh            | 1F0h-1FFh  |

Addresses F0h-FFh, 170h-17Fh and 1F0h-1FFh are implemented as common RAM and mapped back to addresses 70h-7Fh.

Table 4-2 lists how to access the four banks of registers via the Status register bits RP1 and RP0.

#### TABLE 4-2: ACCESS TO BANKS OF REGISTERS

| Bank | RP1 | RP0 |

|------|-----|-----|

| 0    | 0   | 0   |

| 1    | 0   | 1   |

| 2    | 1   | 0   |

| 3    | 1   | 1   |

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $224 \times 8$  in the PIC16F627A/628A and  $256 \times 8$  in the PIC16F648A. Each is accessed either directly or indirectly through the File Select Register (FSR), See **Section 4.4** "Indirect Addressing, INDF and FSR Registers".

### 4.2.2.3 INTCON Register

bit 7

bit 6

bit 5

bit 2

The INTCON register is a readable and writable register, which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 4.2.2.4 "PIE1 Register" and Section 4.2.2.5 "PIR1 Register" for a description of the comparator enable and flag bits.

**Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

## REGISTER 4-3: INTCON – INTERRUPT CONTROL REGISTER (ADDRESS: 0Bh, 8Bh, 10Bh, 18Bh)

|                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |       |       |       | L33. 0DI |       | ы, товп <u>ј</u> |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|----------|-------|------------------|--|

| R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-x            |  |

| GIE                                                                                                                                                                                                                                                                                                                                                                                                                                | PEIE  | T0IE  | INTE  | RBIE  | T0IF     | INTF  | RBIF             |  |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                              |       |       |       |       |          |       | bit 0            |  |

| <ul> <li>GIE: Global Interrupt Enable bit</li> <li>1 = Enables all un-masked interrupts</li> <li>0 = Disables all interrupts</li> <li>PEIE: Peripheral Interrupt Enable bit</li> <li>1 = Enables all un-masked peripheral interrupts</li> <li>0 = Disables all peripheral interrupts</li> <li>TOIE: TMR0 Overflow Interrupt Enable bit</li> <li>1 = Enables the TMR0 interrupt</li> <li>0 = Disables the TMR0 interrupt</li> </ul> |       |       |       |       |          |       |                  |  |

| bit 4 | INTE: RB0/INT External Interrupt Enable bit |

|-------|---------------------------------------------|

|       | 1 = Enables the RB0/INT external interrupt  |

|       | 0 = Disables the RB0/INT external interrupt |

| bit 3 | RBIE: RB Port Change Interrupt Enable bit   |

- 1 = Enables the RB port change interrupt

- 0 = Disables the RB port change interrupt

- **T0IF**: TMR0 Overflow Interrupt Flag bit 1 = TMR0 register has overflowed (must be cleared in software)

- 0 = TMR0 register did not overflow

- bit 1 INTF: RB0/INT External Interrupt Flag bit 1 = The RB0/INT external interrupt occurred (must be cleared in software) 0 = The RB0/INT external interrupt did not occur bit 0 RBIF: RB Port Change Interrupt Flag bit

- 1 = When at least one of the RB<7:4> pins changes state (must be cleared in software)

- 0 = None of the RB<7:4> pins have changed state

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented I  | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

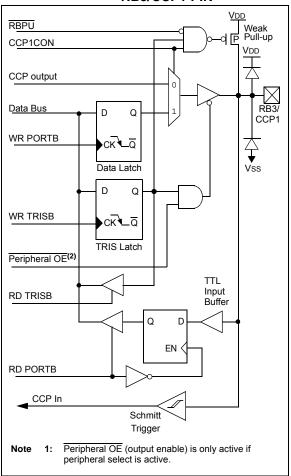

#### FIGURE 5-11: BLOCK DIAGRAM OF RB3/CCP1 PIN

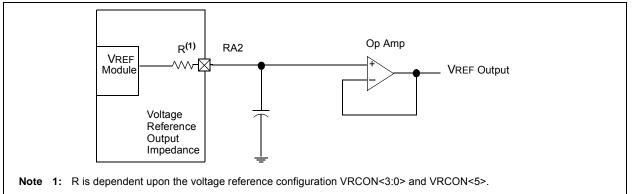

#### FIGURE 11-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 11-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR | Value On<br>All Other<br>Resets |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 9Fh     | VRCON | VREN   | VROE   | VRR    | —      | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 1Fh     | CMCON | C2OUT  | C10UT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 85h     | TRISA | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

**Legend:** - = Unimplemented, read as '0'.

## 12.2 USART Asynchronous Mode

In this mode, the USART uses standard non-return-tozero (NRZ) format (one Start bit, eight or nine data bits and one Stop bit). The most common data format is 8-bit. A dedicated 8-bit baud rate generator is used to derive baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The USART's transmitter and receiver are functionally independent, but use the same data format and baud rate. The baud rate generator produces a clock either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during Sleep.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- · Asynchronous Receiver

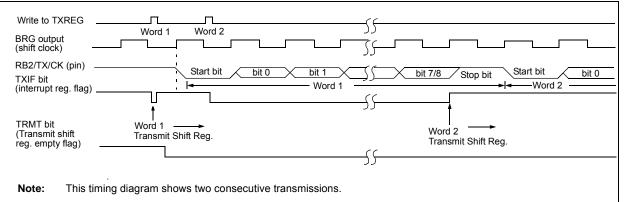

## 12.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 12-1. The heart of the transmitter is the Transmit (serial) Shift Register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the Stop bit has been transmitted from the previous load. As soon as the Stop bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG register is empty and flag bit TXIF (PIR1<4>) is set. This interrupt can be enabled/ disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicated the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read-only bit which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

- Note 1: The TSR register is not mapped in data memory so it is not available to the user.

- 2: Flag bit TXIF is set when enable bit TXEN is set.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the Baud Rate Generator (BRG) has produced a shift clock (Figure 12-1). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally when transmission is first started, the TSR register is empty, so a transfer to the TXREG register will result in an immediate transfer to TSR resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 12-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result the RB2/TX/CK pin will revert to high-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

#### FIGURE 12-3: ASYNCHRONOUS TRANSMISSION (BACK TO BACK)

#### TABLE 12-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address | Name                               | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>all other<br>Resets |

|---------|------------------------------------|-------|-------|-------|-------|-------|--------|--------|--------|-----------------|---------------------------------|

| 0Ch     | PIR1                               | EEIF  | CMIF  | RCIF  | TXIF  |       | CCP1IF | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                       |

| 18h     | RCSTA                              | SPEN  | RX9   | SREN  | CREN  | ADEN  | FERR   | OERR   | RX9D   | x000 0000       | 0000 000x                       |

| 19h     | TXREG USART Transmit Data Register |       |       |       |       |       |        |        |        | 0000 0000       | 0000 0000                       |

| 8Ch     | PIE1                               | EEIE  | CMIE  | RCIE  | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                       |

| 98h     | TXSTA                              | CSRC  | TX9   | TXEN  | SYNC  |       | BRGH   | TRMT   | TX9D   | 0000 -010       | 0000 -010                       |

| 99h     | SPBRG Baud Rate Generator Register |       |       |       |       |       |        |        |        | 0000 0000       | 0000 0000                       |

**Legend:** x = unknown, - = unimplemented locations read as '0'.

Shaded cells are not used for Asynchronous Transmission.

## 13.8 Data EEPROM Operation During Code-Protect

When the device is code-protected, the CPU is able to read and write data to the data EEPROM.

#### TABLE 13-1: REGISTERS/BITS ASSOCIATED WITH DATA EEPROM

| Address | Name                  | Bit 7                     | Bit 6                   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other<br>Resets |

|---------|-----------------------|---------------------------|-------------------------|-------|-------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| 9Ah     | EEDATA                | EEPRO                     | EEPROM Data Register    |       |       |       |       |       |       |                               | uuuu uuuu                       |

| 9Bh     | EEADR                 | EEPRO                     | EEPROM Address Register |       |       |       |       |       |       | xxxx xxxx                     | uuuu uuuu                       |

| 9Ch     | EECON1                | _                         | _                       | —     | —     | WRERR | WREN  | WR    | RD    | x000                          | q000                            |

| 9Dh     | EECON2 <sup>(1)</sup> | EEPROM Control Register 2 |                         |       |       |       |       |       |       |                               |                                 |

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by data EEPROM.

**Note 1:** EECON2 is not a physical register.

## 14.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real-time applications are what sets a microcontroller apart from other processors. The PIC16F627A/628A/648A family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. Reset

- 3. Power-on Reset (POR)

- 4. Power-up Timer (PWRT)

- 5. Oscillator Start-Up Timer (OST)

- 6. Brown-out Reset (BOR)

- 7. Interrupts

- 8. Watchdog Timer (WDT)

- 9. Sleep

- 10. Code protection

- 11. ID Locations

- 12. In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

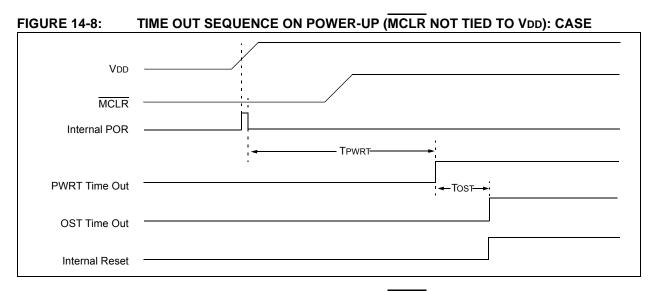

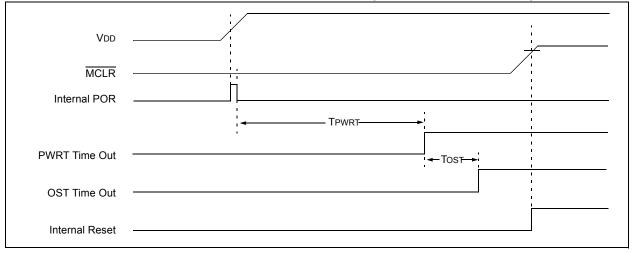

The PIC16F627A/628A/648A has a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in Reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs. With these three functions on-chip, most applications need no external Reset circuitry.

The Sleep mode is designed to offer a very low current Power-down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

## 14.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special configuration memory space (2000h-3FFFh), which can be accessed only during programming. See *"PIC16F627A/628A/648A EEPROM Memory*"

*Programming Specification*" (DS41196) for additional information.

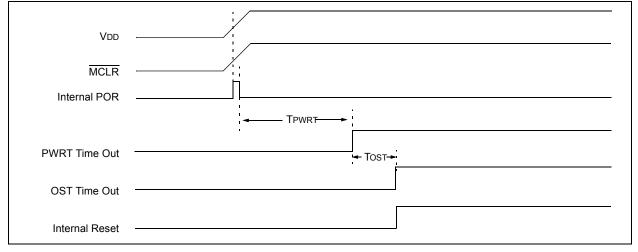

### FIGURE 14-10: TIME OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

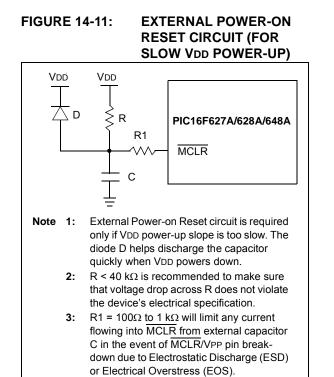

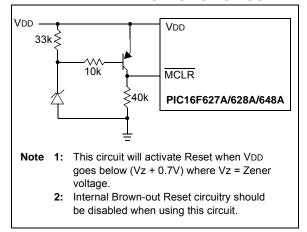

FIGURE 14-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

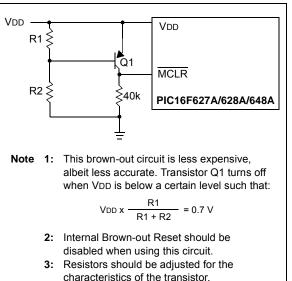

#### FIGURE 14-13: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

# 15.0 INSTRUCTION SET SUMMARY

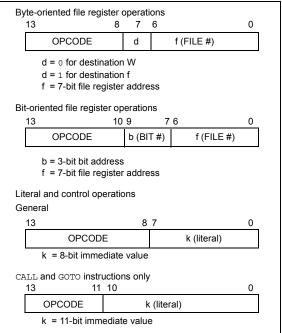

Each PIC16F627A/628A/648A instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16F627A/628A/648A instruction set summary in Table 15-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 15-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

## 15.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a "clrf PORTB" instruction will read PORTB, clear all the data bits, then write the result back to PORTB. This example would have the unintended result that the condition that sets the RBIF flag would be cleared for pins configured as inputs and using the PORTB interrupt-on-change feature.

#### TABLE 15-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                      |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                             |

| W     | Working register (accumulator)                                                                                                                                                   |

| b     | Bit address within an 8-bit file register                                                                                                                                        |

| k     | Literal field, constant data or label                                                                                                                                            |

| x     | Don't care location (= $0$ or 1)<br>The assembler will generate code with x = $0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                     |

| то    | Time-out bit                                                                                                                                                                     |

| PD    | Power-down bit                                                                                                                                                                   |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- · Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 15-2 lists the instructions recognized by the MPASM<sup>™</sup> assembler.

Figure 15-1 shows the three general formats that the instructions can have.

| Note 1: | Any unused opcode is reserved. Use of |

|---------|---------------------------------------|

|         | any reserved opcode may cause unex-   |

|         | pected operation.                     |

2: To maintain upward compatibility with future PIC MCU products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where 'h' signifies a hexadecimal digit.

### FIGURE 15-1: GENERAL FORMAT FOR INSTRUCTIONS

| CLRW             | Clear W                                                                  |  |  |  |  |

|------------------|--------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] CLRW                                                             |  |  |  |  |

| Operands:        | None                                                                     |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$    |  |  |  |  |

| Status Affected: | Z                                                                        |  |  |  |  |

| Encoding:        | 00 0001 0000 0011                                                        |  |  |  |  |

| Description:     | W register is cleared. Zero bit (Z) is set.                              |  |  |  |  |

| Words:           | 1                                                                        |  |  |  |  |

| Cycles:          | 1                                                                        |  |  |  |  |

| Example          | CLRW                                                                     |  |  |  |  |

|                  | Before Instruction<br>W = 0x5A<br>After Instruction<br>W = 0x00<br>Z = 1 |  |  |  |  |

| COMF             | Complement f                                                                                                                                                   |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] COMF f,d                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                    |

| Operation:       | $(\overline{f}) \rightarrow (dest)$                                                                                                                            |

| Status Affected: | Z                                                                                                                                                              |

| Encoding:        | 00 1001 dfff ffff                                                                                                                                              |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the<br>result is stored in W. If 'd' is '1',<br>the result is stored back in<br>register 'f'. |

| Words:           | 1                                                                                                                                                              |

| Cycles:          | 1                                                                                                                                                              |

| Example          | COMF REG1, 0                                                                                                                                                   |

|                  | Before Instruction<br>REG1 = 0x13<br>After Instruction<br>REG1 = 0x13<br>W = 0xEC                                                                              |

| CLRWDT           | Clear W                                                                                                                                                  | latchdo              | g Timer                                            |       |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------------------------------|-------|

| Syntax:          | [ label ]                                                                                                                                                | CLRW                 | DT                                                 |       |

| Operands:        | None                                                                                                                                                     |                      |                                                    |       |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \end{array}$ |                      |                                                    |       |

| Status Affected: | TO, PD                                                                                                                                                   |                      |                                                    |       |

| Encoding:        | 00                                                                                                                                                       | 0000                 | 0110                                               | 0100  |

| Description:     | Watchd<br>the pres                                                                                                                                       | og Timei             | ion resets<br>r. It also r<br>the WDT.<br>are set. | esets |

| Words:           | 1                                                                                                                                                        |                      |                                                    |       |

| Cycles:          | 1                                                                                                                                                        |                      |                                                    |       |

| Example          | CLRWDT                                                                                                                                                   |                      |                                                    |       |

|                  | After Ins                                                                                                                                                | struction<br>WDT cou | unter = ?                                          |       |

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECF f,d                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                 |

| Operation:       | (f) - 1 $\rightarrow$ (dest)                                                                                                                      |

| Status Affected: | Z                                                                                                                                                 |

| Encoding:        | 00 0011 dfff ffff                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is<br>'0'. the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

| Words:           | 1                                                                                                                                                 |

| Cycles:          | 1                                                                                                                                                 |

| Example          | DECF CNT, 1                                                                                                                                       |

|                  | Before Instruction<br>CNT = 0x01<br>Z = 0<br>After Instruction<br>CNT = 0x00<br>Z = 1                                                             |

# 17.5 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| Z. TPPS  |                                        |     |                |  |

|----------|----------------------------------------|-----|----------------|--|

| т        |                                        |     |                |  |

| F        | Frequency                              | Т   | Time           |  |

| Lowercas | se subscripts (pp) and their meanings: |     |                |  |

| рр       |                                        |     |                |  |

| ck       | CLKOUT                                 | OSC | OSC1           |  |

| io       | I/O port                               | tO  | TOCKI          |  |

| mc       | MCLR                                   |     |                |  |

| Uppercas | se letters and their meanings:         |     |                |  |

| S        |                                        |     |                |  |

| F        | Fall                                   | Р   | Period         |  |

| Н        | High                                   | R   | Rise           |  |

| I        | Invalid (High-impedance)               | V   | Valid          |  |

| L        | Low                                    | Z   | High-Impedance |  |

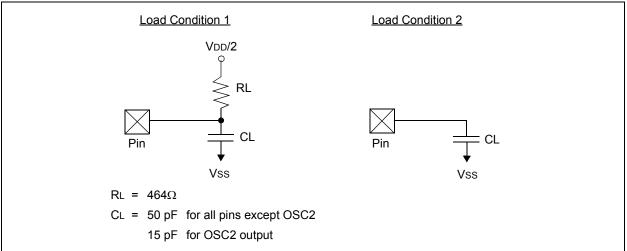

### FIGURE 17-3: LOAD CONDITIONS

| TABLE 17-8: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |           |                                                   |                                                   |                |                                            |                                            |       |       |                                        |                                       |

|-----------------------------------------------------------|-----------|---------------------------------------------------|---------------------------------------------------|----------------|--------------------------------------------|--------------------------------------------|-------|-------|----------------------------------------|---------------------------------------|

| Param<br>No.                                              | Sym       |                                                   | Characterist                                      | ic             | Min                                        | Тур†                                       | Мах   | Units | Conditions                             |                                       |

| 40                                                        | T⊤0H      | T0CKI High                                        | Pulse Width                                       | No Prescaler   | 0.5Tcy + 20*                               | _                                          | _     | ns    |                                        |                                       |

|                                                           |           |                                                   |                                                   | With Prescaler | 10*                                        | _                                          | —     | ns    |                                        |                                       |

| 41                                                        | TT0L      | T0CKI Low F                                       | Pulse Width                                       | No Prescaler   | 0.5Tcy + 20*                               | _                                          | _     | ns    |                                        |                                       |

|                                                           |           |                                                   |                                                   | With Prescaler | 10*                                        | —                                          | _     | ns    |                                        |                                       |

| 42                                                        | TT0P      | T0CKI Perio                                       | d                                                 |                | Greater of:<br>20 or <u>Tcy + 40*</u><br>N |                                            |       | ns    | N = prescale<br>value (2, 4,<br>, 256) |                                       |

| 45                                                        | T⊤1H      |                                                   | Synchronous,                                      | No Prescaler   | 0.5Tcy + 20*                               | —                                          | —     | ns    |                                        |                                       |

|                                                           |           | Time                                              | Synchronous,                                      | PIC16F62XA     | 15*                                        | —                                          | —     | ns    |                                        |                                       |

|                                                           |           |                                                   | with Prescaler                                    | PIC16LF62XA    | 25*                                        | —                                          | _     | ns    |                                        |                                       |

|                                                           |           |                                                   | Asynchronous                                      | PIC16F62XA     | 30*                                        | _                                          | —     | ns    |                                        |                                       |

|                                                           |           |                                                   |                                                   | PIC16LF62XA    | 50*                                        | —                                          | —     | ns    |                                        |                                       |

| 46                                                        | T⊤1L      | Time                                              | Synchronous,                                      | No Prescaler   | 0.5Tcy + 20*                               | —                                          | —     | ns    |                                        |                                       |

|                                                           |           |                                                   | Synchronous,<br>with Prescaler<br>Asynchronous    | PIC16F62XA     | 15*                                        |                                            | —     | ns    |                                        |                                       |

|                                                           |           |                                                   |                                                   | PIC16LF62XA    | 25*                                        | —                                          | —     | ns    |                                        |                                       |

|                                                           |           |                                                   |                                                   | PIC16F62XA     | 30*                                        |                                            | —     | ns    |                                        |                                       |

|                                                           |           |                                                   |                                                   | PIC16LF62XA    | 50*                                        |                                            | —     | ns    |                                        |                                       |

| 47                                                        | T⊤1P      | TT1P T1CKI inpu<br>period                         |                                                   | Synchronous    | PIC16F62XA                                 | Greater of:<br>20 or <u>Tcy + 40*</u><br>N | _     |       | ns                                     | N = prescale<br>value (1, 2,<br>4, 8) |

|                                                           |           |                                                   |                                                   | PIC16LF62XA    | Greater of:<br>20 or <u>Tcy + 40*</u><br>N | _                                          |       | —     |                                        |                                       |

|                                                           |           |                                                   | Asynchronous PIC1<br>PIC1                         | PIC16F62XA     | 60*                                        | _                                          |       | ns    |                                        |                                       |

|                                                           |           |                                                   |                                                   | PIC16LF62XA    | 100*                                       | _                                          | —     | ns    |                                        |                                       |

|                                                           | F⊤1       |                                                   | lator input frequency range nabled by setting bit |                | —                                          | 32.7 <sup>(1)</sup>                        | —     | kHz   |                                        |                                       |

| 48                                                        | TCKEZTMR1 | Delay from external clock edge to timer increment |                                                   |                | 2Tosc                                      |                                            | 7Tosc | _     |                                        |                                       |

## TABLE 17-8: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** This oscillator is intended to work only with 32.768 kHz watch crystals and their manufactured tolerances. Higher value crystal frequencies may not be compatible with this crystal driver.

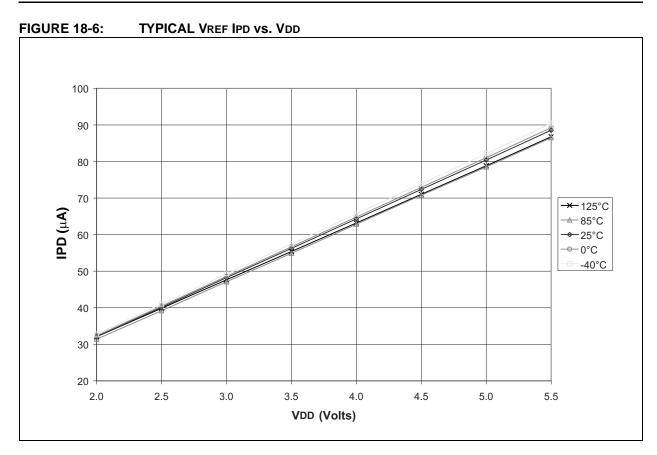

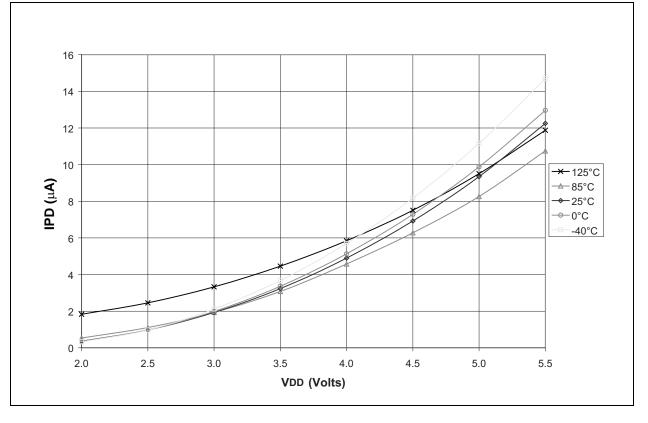

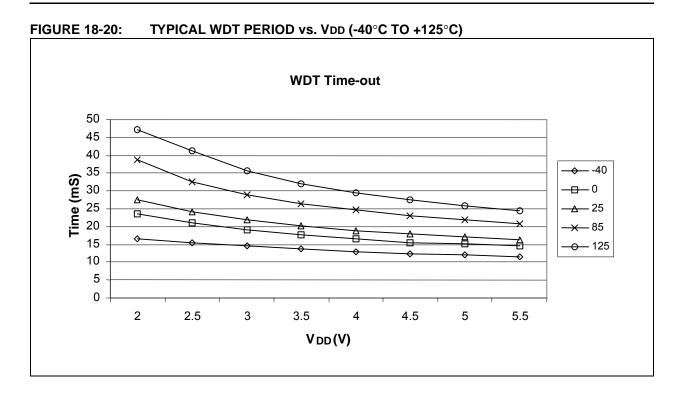

FIGURE 18-7: TYPICAL WDT IPD vs. VDD

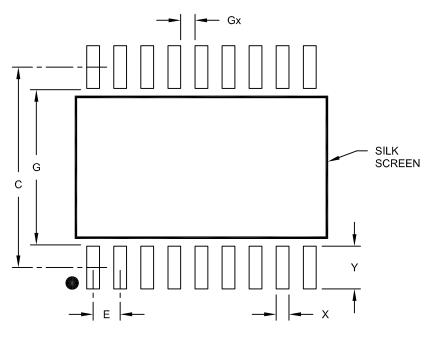

18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

## RECOMMENDED LAND PATTERN

|                       | N      | ILLIMETER | S        |      |

|-----------------------|--------|-----------|----------|------|

| Dimension             | Limits | MIN       | NOM      | MAX  |

| Contact Pitch         | Е      |           | 1.27 BSC |      |

| Contact Pad Spacing   | С      |           | 9.40     |      |

| Contact Pad Width     | Х      |           |          | 0.60 |

| Contact Pad Length    | Y      |           |          | 2.00 |

| Distance Between Pads | Gx     | 0.67      |          |      |

| Distance Between Pads | G      | 7.40      |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2051A

## **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:      | Technical Publications Manager         | Total Pages Sent                                       |

|----------|----------------------------------------|--------------------------------------------------------|

| RE:      | Reader Response                        |                                                        |

| From     | n: Name                                |                                                        |

|          | Company                                |                                                        |

|          | Address                                |                                                        |

|          | City / State / ZIP / Country           |                                                        |

|          | Telephone: ()                          | FAX: ()                                                |

| Appli    | ication (optional):                    |                                                        |

| Wou      | ld you like a reply?YN                 |                                                        |

| Devi     | ce: PIC16F627A/628A/648A               | Literature Number: DS40044G                            |

| Ques     | stions:                                |                                                        |

| 1. V     | What are the best features of this do  | cument?                                                |

|          |                                        |                                                        |

|          |                                        |                                                        |

| 2. H     | How does this document meet your l     | hardware and software development needs?               |

| _        |                                        |                                                        |

| _        |                                        |                                                        |

| 3. E     | Do you find the organization of this d | locument easy to follow? If not, why?                  |

| _        |                                        |                                                        |

| _        |                                        |                                                        |

| 4. V     | What additions to the document do y    | ou think would enhance the structure and subject?      |

| _        |                                        |                                                        |

| -        |                                        |                                                        |

| 5. V     | What deletions from the document c     | ould be made without affecting the overall usefulness? |

|          |                                        |                                                        |

| -        |                                        |                                                        |

| 6. I     | s there any incorrect or misleading i  | nformation (what and where)?                           |

| _        |                                        |                                                        |

| -<br>7 ' | low would you improve this desures     | ant?                                                   |

| 7. F     | low would you improve this docume      | ant (                                                  |

| _        |                                        |                                                        |

| -        |                                        |                                                        |