Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | UART/USART                                                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 18-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f648a-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address | Name   | Bit 7       | Bit 6           | Bit 5       | Bit 4        | Bit 3        | Bit 2         | Bit 1        | Bit 0         | Value on<br>POR<br>Reset <sup>(1)</sup> | Details<br>on Page |

|---------|--------|-------------|-----------------|-------------|--------------|--------------|---------------|--------------|---------------|-----------------------------------------|--------------------|

| Bank 2  |        |             |                 |             |              |              |               |              |               |                                         |                    |

| 100h    | INDF   | Addressing  | g this location | uses conter | nts of FSR t | o address d  | ata memory    | (not a physi | cal register) | xxxx xxxx                               | 30                 |

| 101h    | TMR0   | Timer0 Mo   | dule's Registe  | er          |              |              |               |              |               | xxxx xxxx                               | 47                 |

| 102h    | PCL    | Program C   | Counter's (PC)  | Least Sign  | ificant Byte |              |               |              |               | 0000 0000                               | 30                 |

| 103h    | STATUS | IRP         | RP1             | С           | 0001 1xxx    | 24           |               |              |               |                                         |                    |

| 104h    | FSR    | Indirect Da | ata Memory A    | ddress Poin | ter          |              |               |              |               | xxxx xxxx                               | 30                 |

| 105h    | _      | Unimpleme   | ented           |             |              |              |               |              |               | —                                       | -                  |

| 106h    | PORTB  | RB7         | RB6             | RB5         | RB4          | RB3          | RB2           | RB1          | RB0           | xxxx xxxx                               | 38                 |

| 107h    | _      | Unimpleme   | ented           | •           | •            | •            |               | •            |               | _                                       | _                  |

| 108h    | _      | Unimpleme   | ented           |             |              |              |               |              |               | _                                       | _                  |

| 109h    | _      | Unimpleme   | ented           |             |              |              |               |              |               | _                                       | —                  |

| 10Ah    | PCLATH | _           | _               | _           | Write        | Buffer for u | pper 5 bits o | f Program C  | Counter       | 0 0000                                  | 30                 |

| 10Bh    | INTCON | GIE         | PEIE            | T0IE        | INTE         | RBIE         | TOIF          | INTF         | RBIF          | 0000 000x                               | 26                 |

| 10Ch    | —      | Unimpleme   | implemented     |             |              |              |               |              |               |                                         |                    |

| 10Dh    | —      | Unimpleme   | ented           |             |              |              |               |              |               | —                                       | _                  |

| 10Eh    | _      | Unimpleme   | ented           |             |              |              |               |              |               | _                                       |                    |

| 10Fh    | _      | Unimpleme   | ented           |             |              |              |               |              |               | _                                       |                    |

| 110h    |        | Unimpleme   | ented           |             |              |              |               |              |               | _                                       |                    |

| 111h    |        | Unimpleme   | ented           |             |              |              |               |              |               | —                                       | —                  |

| 112h    |        | Unimpleme   | ented           |             |              |              |               |              |               | —                                       | —                  |

| 113h    |        | Unimpleme   | ented           |             |              |              |               |              |               | —                                       | —                  |

| 114h    | —      | Unimpleme   | ented           |             |              |              |               |              |               | —                                       | _                  |

| 115h    | —      | Unimpleme   | ented           |             |              |              |               |              |               | _                                       | _                  |

| 116h    | —      | Unimpleme   | ented           |             |              |              |               |              |               | _                                       | —                  |

| 117h    | _      | Unimpleme   | ented           |             |              |              |               |              |               | _                                       |                    |

| 118h    | _      | Unimpleme   | ented           |             |              |              |               |              |               | _                                       |                    |

| 119h    |        | Unimpleme   |                 |             |              |              |               |              |               | _                                       |                    |

| 11Ah    |        | Unimpleme   |                 |             |              |              |               |              |               | —                                       | —                  |

| 11Bh    | _      | Unimpleme   |                 |             |              |              |               |              |               | —                                       | —                  |

| 11Ch    | _      | Unimpleme   |                 |             |              |              |               |              |               | _                                       | —                  |

| 11Dh    | -      | Unimpleme   |                 |             |              |              |               |              |               | —                                       | —                  |

| 11Eh    | -      | Unimpleme   |                 |             |              |              |               |              |               | —                                       | —                  |

| 11Fh    | —      | Unimpleme   | ented           |             |              |              |               |              |               | —                                       | —                  |

### TABLE 4-5: SPECIAL FUNCTION REGISTERS SUMMARY BANK2

Legend:- = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented.Note1:For the initialization condition for registers tables, refer to Table 14-6 and Table 14-7.

### 4.2.2.1 Status Register

The Status register, shown in Register 4-1, contains the arithmetic status of the ALU; the Reset status and the bank select bits for data memory (SRAM).

The Status register can be the destination for any instruction, like any other register. If the Status register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are non-writable. Therefore, the result of an instruction with the Status register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the Status register as "000uu1uu" (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the Status register because these instructions do not affect any Status bit. For other instructions, not affecting any Status bits, see the "Instruction Set Summary".

| Note: | The C and DC bits operate as a Borrow      |

|-------|--------------------------------------------|

|       | and Digit Borrow out bit, respectively, in |

|       | subtraction. See the SUBLW and SUBWF       |

|       | instructions for examples.                 |

### REGISTER 4-1: STATUS – STATUS REGISTER (ADDRESS: 03h, 83h, 103h, 183h)

|         | R/W-0                                                                                                                                                                               | R/W-0                                                                                                                  | R/W-0                                                                   | R-1                                                                             | R-1                                                                                                                                                                                         | R/W-x                                      | R/W-x          | R/W-x       |  |  |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------|-------------|--|--|--|--|--|

|         | IRP                                                                                                                                                                                 | RP1                                                                                                                    | RP0                                                                     | TO                                                                              | PD                                                                                                                                                                                          | Z                                          | DC             | С           |  |  |  |  |  |

|         | bit 7                                                                                                                                                                               |                                                                                                                        |                                                                         |                                                                                 |                                                                                                                                                                                             |                                            |                | bit 0       |  |  |  |  |  |

| bit 7   | 1 = Bank 2                                                                                                                                                                          | 2, 3 (100h-1F                                                                                                          | Fh)                                                                     | d for indirec                                                                   | t addressing)                                                                                                                                                                               |                                            |                |             |  |  |  |  |  |

| bit 6-5 | <b>RP&lt;1:0&gt;</b> : 1<br>00 = Bank<br>01 = Bank<br>10 = Bank                                                                                                                     | <ul> <li>a = After power-up or by the CLRWDT instruction</li> <li>b = By execution of the SLEEP instruction</li> </ul> |                                                                         |                                                                                 |                                                                                                                                                                                             |                                            |                |             |  |  |  |  |  |

| bit 4   | 1 = After p                                                                                                                                                                         | <b>TO</b> : Time Out bit<br>1 = After power-up, CLRWDT instruction or SLEEP instruction<br>0 = A WDT time out occurred |                                                                         |                                                                                 |                                                                                                                                                                                             |                                            |                |             |  |  |  |  |  |

| bit 3   | <ul> <li>a WDT time out occurred</li> <li>PD: Power-down bit</li> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul> |                                                                                                                        |                                                                         |                                                                                 |                                                                                                                                                                                             |                                            |                |             |  |  |  |  |  |

| bit 2   |                                                                                                                                                                                     | sult of an arit                                                                                                        |                                                                         |                                                                                 |                                                                                                                                                                                             |                                            |                |             |  |  |  |  |  |

| bit 1   | is reversed<br>1 = A carry                                                                                                                                                          | d)                                                                                                                     | e 4th low or                                                            | der bit of th                                                                   | BLW, SUBWF insi<br>e result occurre                                                                                                                                                         |                                            | for Borrow t   | he polarity |  |  |  |  |  |

| bit 0   | <b>C</b> : Carry/B<br>1 = A carry                                                                                                                                                   | orrow bit (AD<br>-out from the<br>ry-out from the<br>For Borrow,<br>complement                                         | DWF, ADDL<br>e Most Sigr<br>he Most Sig<br>the polarity<br>t of the sec | W, SUBLW, S<br>nificant bit of<br>gnificant bit<br>/ is reversed<br>cond operar | The result<br>SUBWF instruction<br>of the result occur<br>of the result occur<br>of the result occur<br>of the result occur<br>d. A subtraction<br>and. For rotate (F<br>order bit of the s | irred<br>curred<br>is execute<br>RRF, RLF) | instructions   |             |  |  |  |  |  |

|         | Legend:                                                                                                                                                                             |                                                                                                                        |                                                                         |                                                                                 |                                                                                                                                                                                             |                                            |                |             |  |  |  |  |  |

|         | R = Reada                                                                                                                                                                           |                                                                                                                        | VV = V                                                                  | Vritable bit                                                                    | U = Unimple                                                                                                                                                                                 | emented b                                  | oit, read as ' | יכ          |  |  |  |  |  |

|         | -n = Value                                                                                                                                                                          | at POR                                                                                                                 | '1' = E                                                                 | Bit is set                                                                      | '0' = Bit is c                                                                                                                                                                              | leared                                     | x = Bit is ur  | nknown      |  |  |  |  |  |

## 4.2.2.4 PIE1 Register

This register contains interrupt enable bits.

| REGISTER 4-4: | PIE1 – PERIPHERAL INTERRUPT ENABLE REGISTER 1 (ADDRESS: 8Ch)                                                  |                                                                                                               |                 |                                 |                |           |                |        |  |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------|----------------|-----------|----------------|--------|--|--|--|--|--|

|               | R/W-0                                                                                                         | R/W-0                                                                                                         | R/W-0           | R/W-0                           | U-0            | R/W-0     | R/W-0          | R/W-0  |  |  |  |  |  |

|               | EEIE                                                                                                          | CMIE                                                                                                          | RCIE            | TXIE                            |                | CCP1IE    | TMR2IE         | TMR1IE |  |  |  |  |  |

|               | bit 7                                                                                                         | bit 7 bit 0                                                                                                   |                 |                                 |                |           |                |        |  |  |  |  |  |

| bit 7         | EEIE: EE Write Complete Interrupt Enable Bit                                                                  |                                                                                                               |                 |                                 |                |           |                |        |  |  |  |  |  |

|               |                                                                                                               | s the EE wr<br>es the EE wi                                                                                   |                 |                                 |                |           |                |        |  |  |  |  |  |

| bit 6         | CMIE: Com                                                                                                     | nparator Inte                                                                                                 | errupt Enabl    | e bit                           |                |           |                |        |  |  |  |  |  |

|               |                                                                                                               | <ul> <li>E = Enables the comparator interrupt</li> <li>D = Disables the comparator interrupt</li> </ul>       |                 |                                 |                |           |                |        |  |  |  |  |  |

| bit 5         | RCIE: USART Receive Interrupt Enable bit                                                                      |                                                                                                               |                 |                                 |                |           |                |        |  |  |  |  |  |

|               |                                                                                                               | <ul> <li>1 = Enables the USART receive interrupt</li> <li>0 = Disables the USART receive interrupt</li> </ul> |                 |                                 |                |           |                |        |  |  |  |  |  |

| bit 4         | TXIE: USART Transmit Interrupt Enable bit                                                                     |                                                                                                               |                 |                                 |                |           |                |        |  |  |  |  |  |

|               |                                                                                                               | s the USAR<br>as the USAF                                                                                     |                 |                                 |                |           |                |        |  |  |  |  |  |

| bit 3         | Unimplem                                                                                                      | ented: Rea                                                                                                    | <b>d as</b> '0' |                                 |                |           |                |        |  |  |  |  |  |

| bit 2         | CCP1IE: C                                                                                                     | CCP1IE: CCP1 Interrupt Enable bit                                                                             |                 |                                 |                |           |                |        |  |  |  |  |  |

|               |                                                                                                               | s the CCP1<br>es the CCP1                                                                                     |                 |                                 |                |           |                |        |  |  |  |  |  |

| bit 1         | TMR2IE: T                                                                                                     | MR2 to PR2                                                                                                    | 2 Match Inte    | errupt Enable                   | e bit          |           |                |        |  |  |  |  |  |

|               |                                                                                                               |                                                                                                               |                 | tch interrupt<br>atch interrupt |                |           |                |        |  |  |  |  |  |

| bit 0         | TMR1IE: T                                                                                                     | MR1 Overfle                                                                                                   | ow Interrupt    | Enable bit                      |                |           |                |        |  |  |  |  |  |

|               | <ul> <li>1 = Enables the TMR1 overflow interrupt</li> <li>0 = Disables the TMR1 overflow interrupt</li> </ul> |                                                                                                               |                 |                                 |                |           |                |        |  |  |  |  |  |

|               | Legend:                                                                                                       |                                                                                                               |                 |                                 |                |           |                |        |  |  |  |  |  |

|               | R = Reada                                                                                                     | ble bit                                                                                                       | VV = V          | Vritable bit                    | U = Unimpl     | emented b | it, read as '( | )'     |  |  |  |  |  |

|               | -n = Value                                                                                                    | at POR                                                                                                        | '1' = E         | Bit is set                      | '0' = Bit is c | leared    | x = Bit is ur  | nknown |  |  |  |  |  |

## REGISTER 4-4: PIE1 – PERIPHERAL INTERRUPT ENABLE REGISTER 1 (ADDRESS: 8Ch)

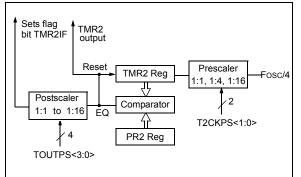

## 8.0 TIMER2 MODULE

Timer2 is an 8-bit timer with a prescaler and a postscaler. It can be used as the PWM time base for PWM mode of the CCP module. The TMR2 register is readable and writable, and is cleared on any device Reset.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS<1:0> (T2CON<1:0>).

The Timer2 module has an 8-bit period register PR2. The TMR2 register value increments from 00h until it matches the PR2 register value and then resets to 00h on the next increment cycle. The PR2 register is a readable and writable register. The PR2 register is initialized to FFh upon Reset.

The match output of Timer2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a Timer2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

Timer2 can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Register 8-1 shows the Timer2 control register.

### 8.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- · a write to the T2CON register

- any device Reset (Power-on Reset, MCLR Reset, Watchdog Timer Reset or Brown-out Reset)

The TMR2 register is not cleared when T2CON is written.

## 8.2 TMR2 Output

The TMR2 output (before the postscaler) is fed to the Synchronous Serial Port module which optionally uses it to generate shift clock.

#### FIGURE 8-1: TIMER2 BLOCK DIAGRAM

| REGISTER 8-1: | T2CO                     | N – TIMER2                                       | CONTRO      | L REGISTE      | R (ADDRES  | S: 12h)     |                |         |  |  |  |  |  |  |

|---------------|--------------------------|--------------------------------------------------|-------------|----------------|------------|-------------|----------------|---------|--|--|--|--|--|--|

|               | U-0                      | R/W-0                                            | R/W-0       | R/W-0          | R/W-0      | R/W-0       | R/W-0          | R/W-0   |  |  |  |  |  |  |

|               | —                        | TOUTPS3                                          | TOUTPS2     | TOUTPS1        | TOUTPS0    | TMR2ON      | T2CKPS1        | T2CKPS0 |  |  |  |  |  |  |

|               | bit 7                    |                                                  |             |                |            |             |                | bit 0   |  |  |  |  |  |  |

| bit 7         | Unimplem                 | ented: Read                                      | as '0'      |                |            |             |                |         |  |  |  |  |  |  |

| bit 6-3       | -                        | TOUTPS<3:0>: Timer2 Output Postscale Select bits |             |                |            |             |                |         |  |  |  |  |  |  |

|               |                          | 0000 = 1:1 Postscale Value                       |             |                |            |             |                |         |  |  |  |  |  |  |

|               | 0001 = 1:2               | 0001 = 1:2 Postscale Value                       |             |                |            |             |                |         |  |  |  |  |  |  |

|               | •                        |                                                  |             |                |            |             |                |         |  |  |  |  |  |  |

|               | •                        | •                                                |             |                |            |             |                |         |  |  |  |  |  |  |

|               | 1111 <b>= 1</b> :1       | 6 Postscale                                      |             |                |            |             |                |         |  |  |  |  |  |  |

| bit 2         | TMR2ON:                  | Timer2 On bi                                     | it          |                |            |             |                |         |  |  |  |  |  |  |

|               | 1 = Timer2<br>0 = Timer2 |                                                  |             |                |            |             |                |         |  |  |  |  |  |  |

| bit 1-0       |                          | 1:0>: Timer2                                     | Clock Presc | ale Select bit | s          |             |                |         |  |  |  |  |  |  |

|               |                          | rescaler Valu                                    |             |                | -          |             |                |         |  |  |  |  |  |  |

|               | 01 <b>= 1:4 P</b>        | rescaler Valu                                    | е           |                |            |             |                |         |  |  |  |  |  |  |

|               | 1x = 1:16                | Prescaler Val                                    | ue          |                |            |             |                |         |  |  |  |  |  |  |

|               | Legend:                  |                                                  |             |                |            |             |                |         |  |  |  |  |  |  |

|               | R = Reada                | able bit                                         | W = W       | /ritable bit   | U = Unimpl | emented bit | t, read as '0' |         |  |  |  |  |  |  |

### TABLE 8-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

-n = Value at POR

| Address                 | Name                          | Bit 7       | Bit 6       | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR | Value on<br>all other<br>Resets |

|-------------------------|-------------------------------|-------------|-------------|---------|---------|---------|--------|---------|---------|-----------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON                        | GIE         | PEIE        | TOIE    | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x       | 0000 000u                       |

| 0Ch                     | PIR1                          | EEIF        | CMIF        | RCIF    | TXIF    | 1       | CCP1IF | TMR2IF  | TMR1IF  | 0000 -000       | 0000 -000                       |

| 8Ch                     | PIE1                          | EEIE        | CMIE        | RCIE    | TXIE    | _       | CCP1IE | TMR2IE  | TMR1IE  | 0000 -000       | 0000 -000                       |

| 11h                     | TMR2 Timer2 Module's Register |             |             |         |         |         |        |         |         | 0000 0000       | 0000 0000                       |

| 12h                     | T2CON                         | _           | TOUTPS3     | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000       | -000 0000                       |

| 92h                     | PR2                           | Timer2 Peri | od Register |         |         |         |        |         |         | 1111 1111       | 1111 1111                       |

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

NOTES:

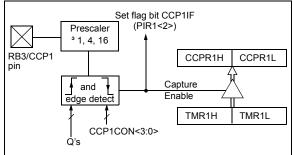

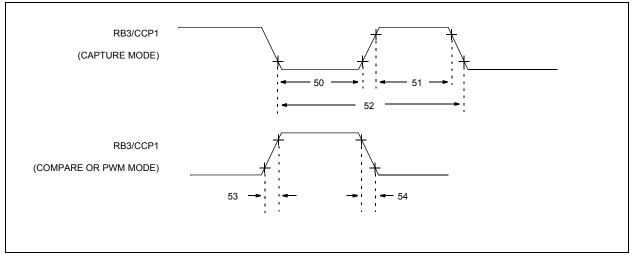

## 9.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RB3/CCP1. An event is defined as:

- · Every falling edge

- Every rising edge

- · Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M<3:0> (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

### 9.1.1 CCP PIN CONFIGURATION

In Capture mode, the RB3/CCP1 pin should be configured as an input by setting the TRISB<3> bit.

| Note: | If the RB3/CCP1 is configured as an     |

|-------|-----------------------------------------|

|       | output, a write to the port can cause a |

|       | capture condition.                      |

### FIGURE 9-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

### 9.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 9.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in Operating mode.

## 9.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M<3:0>. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 9-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 9-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ; the new prescaler     |

|       |             | ; mode value and CCP ON |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ; value                 |

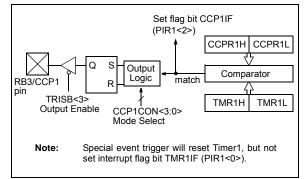

## 9.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RB3/CCP1 pin is:

- Driven high

- Driven low

- · Remains unchanged

The action on the pin is based on the value of control bits CCP1M<3:0> (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

FIGURE 9-2: C

#### COMPARE MODE OPERATION BLOCK DIAGRAM

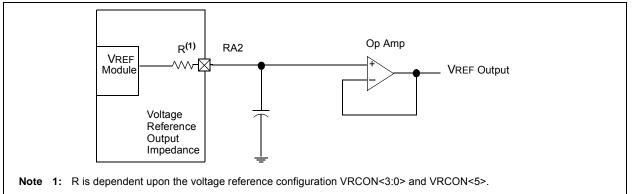

## 11.0 VOLTAGE REFERENCE MODULE

The Voltage Reference module consists of a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of VREF values and has a power-down function to conserve power when the reference is not being used. The VRCON register controls the operation of the reference as shown in Figure 11-1. The block diagram is given in Figure 11-1.

## 11.1 Voltage Reference Configuration

bit

bit

bit

bit bit

The Voltage Reference module can output 16 distinct voltage levels for each range.

-n = Value at POR

The equations used to calculate the output of the Voltage Reference module are as follows:

if VRR = 1:

$$VREF = \frac{VR < 3:0}{24} \times VDD$$

if VRR = 0:

$$VREF = \left(VDD \times \frac{I}{4}\right) + \frac{VR < 3:0}{32} \times VDD$$

The setting time of the Voltage Reference module must be considered when changing the VREF output (Table 17-3). Example 11-1 demonstrates how voltage reference is configured for an output voltage of 1.25V with VDD = 5.0V.

| REGISTER 11-1: | VRCON – VOLTAGE REFERENCE CONTROL REGISTER (ADDRESS: 9Fh) |  |

|----------------|-----------------------------------------------------------|--|

|                |                                                           |  |

| VICON -                                                                                                                                                                                                             | in - Voltage Reference Control Register (ADDRess. 9Fil)                                                |                 |              |            |           |                |       |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------|--------------|------------|-----------|----------------|-------|--|--|--|--|--|--|

| R/W-0                                                                                                                                                                                                               | R/W-0                                                                                                  | R/W-0           | U-0          | R/W-0      | R/W-0     | R/W-0          | R/W-0 |  |  |  |  |  |  |

| VREN                                                                                                                                                                                                                | VROE                                                                                                   | VRR             | _            | VR3        | VR2       | VR1            | VR0   |  |  |  |  |  |  |

| bit 7                                                                                                                                                                                                               | · · · · · · · · · · · · · · · · · · ·                                                                  |                 |              |            |           |                | bit 0 |  |  |  |  |  |  |

| VREN: VR                                                                                                                                                                                                            | EF Enable bit                                                                                          | t               |              |            |           |                |       |  |  |  |  |  |  |

| 1 = VREF circuit powered on<br>0 = VREF circuit powered down, no IDD drain<br>VROF: VREF Output Enable bit                                                                                                          |                                                                                                        |                 |              |            |           |                |       |  |  |  |  |  |  |

| 1 = Vref i                                                                                                                                                                                                          | VROE: VREF Output Enable bit<br>1 = VREF is output on RA2 pin<br>0 = VREF is disconnected from RA2 pin |                 |              |            |           |                |       |  |  |  |  |  |  |

| <ul> <li>0 = VREF is disconnected from RA2 pin</li> <li>VRR: VREF Range Selection bit</li> <li>1 = Low range</li> <li>0 = High range</li> </ul>                                                                     |                                                                                                        |                 |              |            |           |                |       |  |  |  |  |  |  |

| Unimplen                                                                                                                                                                                                            | nented: Read                                                                                           | <b>d as</b> '0' |              |            |           |                |       |  |  |  |  |  |  |

| <b>Unimplemented</b> : Read as '0'<br><b>VR&lt;3:0&gt;</b> : VREF Value Selection bits $0 \le VR < 3:0> \le 15$<br>When VRR = 1: VREF = (VR<3:0>/ 24) * VDD<br>When VRR = 0: VREF = 1/4 * VDD + (VR<3:0>/ 32) * VDD |                                                                                                        |                 |              |            |           |                |       |  |  |  |  |  |  |

| Legend:                                                                                                                                                                                                             |                                                                                                        |                 |              |            |           |                |       |  |  |  |  |  |  |

| R = Reada                                                                                                                                                                                                           | able bit                                                                                               | VV = V          | Vritable bit | U = Unimpl | emented b | it, read as '( | 0'    |  |  |  |  |  |  |

|                                                                                                                                                                                                                     |                                                                                                        |                 |              |            |           |                |       |  |  |  |  |  |  |

'0' = Bit is cleared

'1' = Bit is set

x = Bit is unknown

#### FIGURE 11-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 11-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR | Value On<br>All Other<br>Resets |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 9Fh     | VRCON | VREN   | VROE   | VRR    | —      | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 1Fh     | CMCON | C2OUT  | C10UT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 85h     | TRISA | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

**Legend:** - = Unimplemented, read as '0'.

| TER 12-2: | RCSTA – RECEIVE STATUS AND CONTROL REGISTER (ADDRESS: 18h)                                                                                 |                                                                                     |             |                |              |             |               |            |  |  |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------|----------------|--------------|-------------|---------------|------------|--|--|--|

|           | R/W-0                                                                                                                                      | R/W-0                                                                               | R/W-0       | R/W-0          | R/W-0        | R-0         | R-0           | R-x        |  |  |  |

|           | SPEN                                                                                                                                       | RX9                                                                                 | SREN        | CREN           | ADEN         | FERR        | OERR          | RX9D       |  |  |  |

|           | bit 7                                                                                                                                      | •                                                                                   |             | 1              |              | •           | •             | bit 0      |  |  |  |

| bit 7     | <b>SPEN</b> : Serial Port Enable bit<br>(Configures RB1/RX/DT and RB2/TX/CK pins as serial port pins when bits TRISB<2:1> are set)         |                                                                                     |             |                |              |             |               |            |  |  |  |

|           |                                                                                                                                            | port enabled<br>port disabled                                                       |             |                |              |             |               |            |  |  |  |

| bit 6     | RX9: 9-bit Receive Enable bit                                                                                                              |                                                                                     |             |                |              |             |               |            |  |  |  |

|           |                                                                                                                                            | s 9-bit recep<br>s 8-bit recep                                                      |             |                |              |             |               |            |  |  |  |

| bit 5     | SREN: Sin                                                                                                                                  | gle Receive                                                                         | Enable bit  |                |              |             |               |            |  |  |  |

|           | Asynchronous mode:                                                                                                                         |                                                                                     |             |                |              |             |               |            |  |  |  |

|           | Don't ca<br>Synchrono                                                                                                                      | ire<br>i <u>us mode - n</u>                                                         | naetor:     |                |              |             |               |            |  |  |  |

|           |                                                                                                                                            |                                                                                     |             |                |              |             |               |            |  |  |  |

|           | 0 = Disa                                                                                                                                   | <ol> <li>1 = Enables single receive</li> <li>0 = Disables single receive</li> </ol> |             |                |              |             |               |            |  |  |  |

|           | This bit is cleared after reception is complete.<br>Synchronous mode - slave:                                                              |                                                                                     |             |                |              |             |               |            |  |  |  |

|           |                                                                                                                                            | in this mode                                                                        |             |                |              |             |               |            |  |  |  |

| bit 4     | CREN: Continuous Receive Enable bit                                                                                                        |                                                                                     |             |                |              |             |               |            |  |  |  |

|           | Asynchronous mode:                                                                                                                         |                                                                                     |             |                |              |             |               |            |  |  |  |

|           | 1 = Enables continuous receive                                                                                                             |                                                                                     |             |                |              |             |               |            |  |  |  |

|           | 0 = Disables continuous receive                                                                                                            |                                                                                     |             |                |              |             |               |            |  |  |  |

|           | Synchronous mode:<br>1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)                                 |                                                                                     |             |                |              |             |               |            |  |  |  |

|           |                                                                                                                                            | ables continu                                                                       |             |                |              |             |               | 0 01 (211) |  |  |  |

| bit 3     | ADEN: Address Detect Enable bit                                                                                                            |                                                                                     |             |                |              |             |               |            |  |  |  |

|           | Asynchronous mode 9-bit (RX9 = 1):<br>1 = Enables address detection, enable interrupt and load of the receive buffer when RSR<8><br>is set |                                                                                     |             |                |              |             |               |            |  |  |  |

|           | 0 = Disables address detection, all bytes are received, and ninth bit can be used as parity bit                                            |                                                                                     |             |                |              |             |               |            |  |  |  |

|           | Asynchronous mode 8-bit (RX9 = 0):<br>Unused in this mode                                                                                  |                                                                                     |             |                |              |             |               |            |  |  |  |

|           |                                                                                                                                            | in this mode                                                                        |             |                |              |             |               |            |  |  |  |

| bit 2     | FERR: Framing Error bit                                                                                                                    |                                                                                     |             |                |              |             |               |            |  |  |  |

|           | 1 = Framin<br>0 = No frar                                                                                                                  |                                                                                     | n be update | d by reading   | RCREG regis  | ter and rec | eive next va  | ilid byte) |  |  |  |

| bit 1     | OERR: Overrun Error bit                                                                                                                    |                                                                                     |             |                |              |             |               |            |  |  |  |

|           | <ul> <li>1 = Overrun error (Can be cleared by clearing bit CREN)</li> <li>0 = No overrun error</li> </ul>                                  |                                                                                     |             |                |              |             |               |            |  |  |  |

| bit 0     | <b>RX9D</b> : 9th                                                                                                                          | bit of receiv                                                                       | ed data (Ca | an be parity l | oit)         |             |               |            |  |  |  |

|           | Legend:                                                                                                                                    |                                                                                     |             |                |              |             |               | ]          |  |  |  |

|           | R = Reada                                                                                                                                  | able bit                                                                            | VV = V      | Vritable bit   | U = Unimp    | lemented b  | it, read as ' | D'         |  |  |  |

|           | -n = Value                                                                                                                                 | at POR                                                                              | '1' = E     | Bit is set     | '0' = Bit is | cleared     | x = Bit is u  | ıknown     |  |  |  |

|           | ,                                                                                                                                          |                                                                                     |             |                |              |             |               |            |  |  |  |

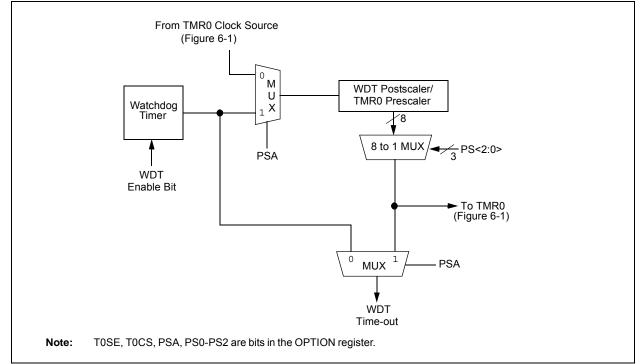

#### FIGURE 14-16: WATCHDOG TIMER BLOCK DIAGRAM

| <b>TABLE 14-9</b> : | SUMMARY OF WATCHDOG TIMER REGISTERS |

|---------------------|-------------------------------------|

|                     |                                     |

| Address   | Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR Reset | Value on<br>all other<br>Resets |

|-----------|--------|-------|--------|-------|-------|-------|-------|-------|-------|-----------------------|---------------------------------|

| 2007h     | CONFIG | LVP   | BOREN  | MCLRE | FOSC2 | PWRTE | WDTE  | FOSC1 | FOSC0 | uuuu uuuu             | uuuu uuuu                       |

| 81h, 181h | OPTION | RBPU  | INTEDG | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111             | 1111 1111                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. **Note:** Shaded cells are not used by the Watchdog Timer.

## 14.8 Power-Down Mode (Sleep)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit in the Status register is cleared, the TO bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before SLEEP was executed (driving high, low or high-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSs with no external circuitry drawing current from the I/O pin and the comparators, and VREF should be disabled. I/O pins that are high-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a Reset generated<br>by a WDT time-out does not drive MCLR |

|-------|------------------------------------------------------------------------------------|

|       | pin low.                                                                           |

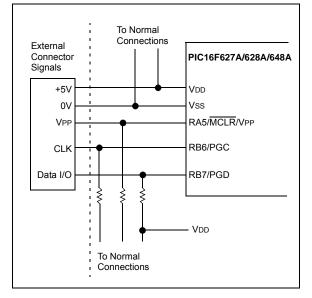

## 14.11 In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

The PIC16F627A/628A/648A microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the RB6 and RB7 pins low while raising the MCLR (VPP) pin from VIL to VIHH. See "*PIC16F627A/628A/648A EEPROM Memory Programming Specification*" (DS41196) for details. RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After Reset, to place the device into Programming/Verify mode, the Program Counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to "*PIC16F627A/628A/648A EEPROM Memory Programming Specification*" (DS41196).

A typical In-Circuit Serial Programming connection is shown in Figure 14-18.

#### FIGURE 14-18: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

## 14.12 Low-Voltage Programming

The LVP bit of the Configuration Word, enables the lowvoltage programming. This mode allows the microcontroller to be programmed via ICSP using only a 5V source. This mode removes the requirement of VIHH to be placed on the MCLR pin. The LVP bit is normally erased to '1' which enables the low-voltage programming. In this mode, the RB4/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin. The device will enter Programming mode when a '1' is placed on the RB4/ PGM pin. The High-Voltage Programming mode is still available by placing VIHH on the MCLR pin.

- Note 1: While in this mode, the RB4 pin can no longer be used as a general purpose I/O pin.

- 2: VDD must be 5.0V <u>+</u>10% during erase operations.

If Low-Voltage Programming mode is not used, the LVP bit should be programmed to a '0' so that RB4/ PGM becomes a digital I/O pin. To program the device, VIHH must be placed onto MCLR during programming. The LVP bit may only be programmed when programming is entered with VIHH on MCLR. The LVP bit cannot be programmed when programming is entered with RB4/PGM.

It should be noted, that once the LVP bit is programmed to '0', only High-Voltage Programming mode can be used to program the device.

NOTES:

AND Literal with W

ANDLW

| ADDLW            | Add Literal and W                                                                                                          |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |  |  |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                          |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |  |  |  |  |  |

| Encoding:        | 11 111x kkkk kkkk                                                                                                          |  |  |  |  |  |  |

| Description:     | The contents of the W register<br>are added to the eight bit literal<br>'k' and the result is placed in the<br>W register. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                          |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                          |  |  |  |  |  |  |

| Example          | ADDLW 0x15                                                                                                                 |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x10<br>After Instruction<br>W = 0x25                                                            |  |  |  |  |  |  |

| Curstand                                                |                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                                 | [ <i>label</i> ] ANDLW k                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Operands:                                               | $0 \leq k \leq 255$                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Operation:                                              | (W) .AND. (k) $\rightarrow$ (W)                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Status Affected:                                        | Z                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Encoding:                                               | 11 1001 kkkk kkkk                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Description:                                            | The contents of W register are<br>AND'ed with the eight bit literal<br>'k'. The result is placed in the W<br>register.                                                                                                                                                                                                                                    |  |  |  |  |  |

| Words:                                                  | 1                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Cycles:                                                 | 1                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Example                                                 | ANDLW 0x5F                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                                                         | Before Instruction<br>W = 0xA3<br>After Instruction                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                                                         | W = 0x03                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| ANDWF                                                   | AND W with f                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| Syntax:                                                 | [label] ANDWF f,d                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Operands:                                               | $0 \le f \le 127$                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|                                                         | $d \in [0,1]$                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Operation:                                              | d ∈ [0,1]<br>(W) .AND. (f) → (dest)                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Operation:<br>Status Affected:                          |                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| •                                                       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Status Affected:                                        | (W) .AND. (f) $\rightarrow$ (dest)<br>Z                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Status Affected:<br>Encoding:                           | (W) .AND. (f) $\rightarrow$ (dest)<br>Z<br>00 0101 dfff ffff<br>AND the W register with register<br>'f'. If 'd' is '0', the result is stored<br>in the W register. If 'd' is '1', the<br>result is stored back in register                                                                                                                                |  |  |  |  |  |