Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

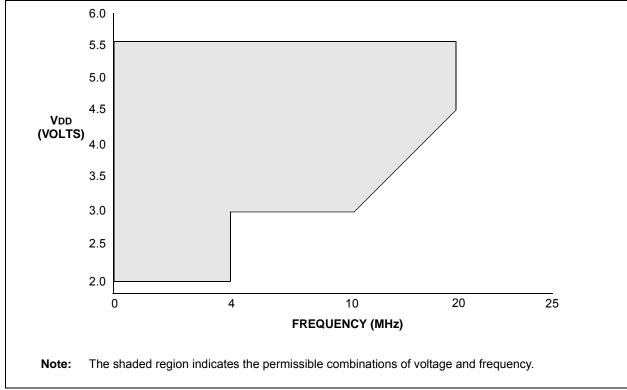

| Speed                      | 20MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

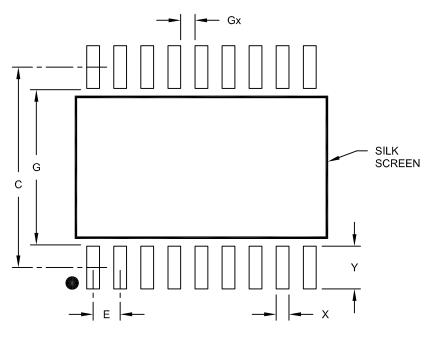

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f648at-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| Name                                                  | Function | Input Type | Output Type | Description                                                                                                                                                          |  |  |  |

|-------------------------------------------------------|----------|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RA0/AN0                                               | RA0      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                               |  |  |  |

|                                                       | AN0      | AN         | —           | Analog comparator input                                                                                                                                              |  |  |  |

| RA1/AN1                                               | RA1      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                               |  |  |  |

|                                                       | AN1      | AN         | _           | Analog comparator input                                                                                                                                              |  |  |  |

| RA2/AN2/VREF                                          | RA2      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                               |  |  |  |

|                                                       | AN2      | AN         |             | Analog comparator input                                                                                                                                              |  |  |  |

|                                                       | VREF     | —          | AN          | VREF output                                                                                                                                                          |  |  |  |

| RA3/AN3/CMP1                                          | RA3      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                               |  |  |  |

|                                                       | AN3      | AN         |             | Analog comparator input                                                                                                                                              |  |  |  |

|                                                       | CMP1     | —          | CMOS        | Comparator 1 output                                                                                                                                                  |  |  |  |

| RA4/T0CKI/CMP2                                        | RA4      | ST         | OD          | Bidirectional I/O port                                                                                                                                               |  |  |  |

|                                                       | TOCKI    | ST         | _           | Timer0 clock input                                                                                                                                                   |  |  |  |

|                                                       | CMP2     | _          | OD          | Comparator 2 output                                                                                                                                                  |  |  |  |

| RA5/MCLR/VPP                                          | RA5      | ST         | _           | Input port                                                                                                                                                           |  |  |  |

|                                                       | MCLR     | ST         | _           | Master clear. When configured as MCLR, th<br>pin is an active low Reset to the device.<br>Voltage on MCLR/VPP must not exceed VDr<br>during normal device operation. |  |  |  |

|                                                       | VPP      | —          | —           | Programming voltage input                                                                                                                                            |  |  |  |

| RA6/OSC2/CLKOUT                                       | RA6      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                               |  |  |  |

|                                                       | OSC2     | —          | XTAL        | Oscillator crystal output. Connects to crystal<br>or resonator in Crystal Oscillator mode.                                                                           |  |  |  |

|                                                       | CLKOUT   |            | CMOS        | In RC/INTOSC mode, OSC2 pin can output<br>CLKOUT, which has 1/4 the frequency of<br>OSC1.                                                                            |  |  |  |

| RA7/OSC1/CLKIN                                        | RA7      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                               |  |  |  |

|                                                       | OSC1     | XTAL       | —           | Oscillator crystal input                                                                                                                                             |  |  |  |

|                                                       | CLKIN    | ST         | —           | External clock source input. RC biasing pin.                                                                                                                         |  |  |  |

| RB0/INT                                               | RB0      | TTL        | CMOS        | Bidirectional I/O port. Can be software<br>programmed for internal weak pull-up.                                                                                     |  |  |  |

|                                                       | INT      | ST         | —           | External interrupt                                                                                                                                                   |  |  |  |

| RB1/RX/DT                                             | RB1      | TTL        | CMOS        | Bidirectional I/O port. Can be software programmed for internal weak pull-up.                                                                                        |  |  |  |

|                                                       | RX       | ST         | —           | USART receive pin                                                                                                                                                    |  |  |  |

|                                                       | DT       | ST         | CMOS        | Synchronous data I/O                                                                                                                                                 |  |  |  |

| RB2/TX/CK                                             | RB2      | TTL        | CMOS        | Bidirectional I/O port. Can be software programmed for internal weak pull-up.                                                                                        |  |  |  |

|                                                       | ТХ       |            | CMOS        | USART transmit pin                                                                                                                                                   |  |  |  |

|                                                       | CK       | ST         | CMOS        | Synchronous clock I/O                                                                                                                                                |  |  |  |

| RB3/CCP1                                              | RB3      | TTL        | CMOS        | Bidirectional I/O port. Can be software programmed for internal weak pull-up.                                                                                        |  |  |  |

|                                                       | CCP1     | ST         | CMOS        | Capture/Compare/PWM I/O                                                                                                                                              |  |  |  |

| Legend: O = Output<br>— = Not used<br>TTL = TTL Input |          | I = Ir     | MOS Output  | P = Power<br>ST = Schmitt Trigger Input<br>AN = Analog                                                                                                               |  |  |  |

#### TABLE 3-2: PIC16F627A/628A/648A PINOUT DESCRIPTION

# 4.0 MEMORY ORGANIZATION

### 4.1 Program Memory Organization

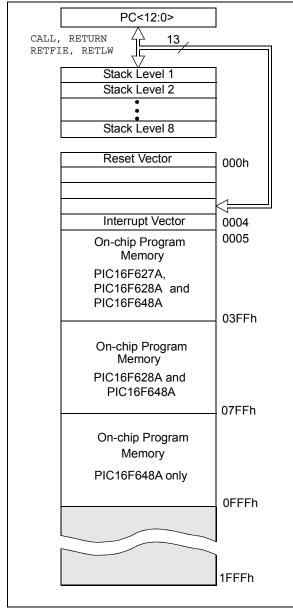

The PIC16F627A/628A/648A has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 1K x 14 (0000h-03FFh) for the PIC16F627A, 2K x 14 (0000h-07FFh) for the PIC16F628A and 4K x 14 (0000h-0FFFh) for the PIC16F648A are physically implemented. Accessing a location above these boundaries will cause a wraparound within the first 1K x 14 space (PIC16F627A), 2K x 14 space (PIC16F628A) or 4K x 14 space (PIC16F648A). The Reset vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1).

### 4.2 Data Memory Organization

The data memory (Figure 4-2 and Figure 4-3) is partitioned into four banks, which contain the General Purpose Registers (GPRs) and the Special Function Registers (SFRs). The SFRs are located in the first 32 locations of each bank. There are General Purpose Registers implemented as static RAM in each bank. Table 4-1 lists the General Purpose Register available in each of the four banks.

| TABLE 4-1: | GENERAL PURPOSE STATIC |

|------------|------------------------|

|            | RAM REGISTERS          |

|       | PIC16F627A/628A      | PIC16F648A |

|-------|----------------------|------------|

| Bank0 | 20-7Fh               | 20-7Fh     |

| Bank1 | A0h-FF               | A0h-FF     |

| Bank2 | 120h-14Fh, 170h-17Fh | 120h-17Fh  |

| Bank3 | 1F0h-1FFh            | 1F0h-1FFh  |

Addresses F0h-FFh, 170h-17Fh and 1F0h-1FFh are implemented as common RAM and mapped back to addresses 70h-7Fh.

Table 4-2 lists how to access the four banks of registers via the Status register bits RP1 and RP0.

# TABLE 4-2: ACCESS TO BANKS OF REGISTERS

| Bank | RP1 | RP0 |

|------|-----|-----|

| 0    | 0   | 0   |

| 1    | 0   | 1   |

| 2    | 1   | 0   |

| 3    | 1   | 1   |

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $224 \times 8$  in the PIC16F627A/628A and  $256 \times 8$  in the PIC16F648A. Each is accessed either directly or indirectly through the File Select Register (FSR), See **Section 4.4** "Indirect Addressing, INDF and FSR Registers".

# 5.3 I/O Programming Considerations

#### 5.3.1 BIDIRECTIONAL I/O PORTS

Any instruction that writes operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit 5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit 5 and PORTB is written to the output latches. If another bit of PORTB is used as a bidirectional I/O pin (e.g., bit 0) and is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit 0 is switched into Output mode later on, the content of the data latch may now be unknown.

Reading a port register reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-2 shows the effect of two sequential read-modify-write instructions (ex.,  ${\tt BCF}, {\tt BSF},$  etc.) on an I/O port

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-OR", "wired-AND"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-2: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

| ;Initial PORT settings:     | :PORTB<7:4> Inputs    |

|-----------------------------|-----------------------|

| ;                           | PORTB<3:0> Outputs    |

| ;PORTB<7:6> have extern     | nal pull-up and are   |

| ;not connected to other     | c circuitry           |

| ;                           |                       |

| ;                           | PORT latchPORT Pins   |

|                             |                       |

| BCF STATUS, RPO             | ;                     |

| BCF PORTB, 7                | ;01pp pppp 11pp pppp  |

| BSF STATUS, RPO             | ;                     |

|                             | ;10pp pppp 11pp pppp  |

| BCF TRISB, 6                | ;10pp pppp 10pp pppp  |

| ;                           | , the sets - set fore |

| ,<br>Note that the user may | v have expected the   |

| ; pin values to be 00pp     | -                     |

| ; caused RB7 to be latch    |                       |

| ; (High).                   | ica ab che più value  |

| , (111911).                 |                       |

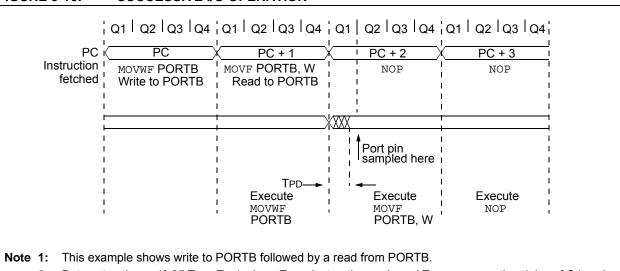

#### 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-16). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction, which causes that file to be read into the CPU, is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

2: Data setup time = (0.25 TCY - TPD) where TCY = instruction cycle and TPD = propagation delay of Q1 cycle to output valid. Therefore, at higher clock frequencies, a write followed by a read may be problematic.

### FIGURE 5-16: SUCCESSIVE I/O OPERATION

### 7.3 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 7.3.2 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | In Asynchronous Counter mode, Timer1      |

|-------|-------------------------------------------|

|       | cannot be used as a time base for capture |

|       | or compare operations.                    |

#### 7.3.1 EXTERNAL CLOCK INPUT TIMING WITH UNSYNCHRONIZED CLOCK

If control bit  $\overline{\text{T1SYNC}}$  is set, the timer will increment completely asynchronously. The input clock must meet certain minimum high and low time requirements. Refer to Table 17-8 in the Electrical Specifications Section, timing parameters 45, 46 and 47.

#### 7.3.2 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading the TMR1H or TMR1L register, while the timer is running from an external asynchronous clock, will produce a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself poses certain problems since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Example 7-1 is an example routine to read the 16-bit timer value. This is useful if the timer cannot be stopped.

#### EXAMPLE 7-1: READING A 16-BIT FREE-RUNNING TIMER

|   | All inte | rrupts are d | lisabled                |

|---|----------|--------------|-------------------------|

| , | MOVF     | TMR1H, W     |                         |

|   | MOVWF    |              | , kedd high byte        |

|   |          |              |                         |

|   | MOVF     | ,            | ;Read low byte          |

|   | MOVWF    | TMPL         | ;                       |

|   | MOVF     | TMR1H, W     | ;Read high byte         |

|   | SUBWF    | TMPH, W      | ;Sub 1st read with      |

|   |          |              | ;2nd read               |

|   | BTFSC    | STATUS, Z    | ;Is result = 0          |

|   | GOTO     | CONTINUE     | ;Good 16-bit read       |

| ; |          |              |                         |

| ; | TMR1L ma | v have rolle | ed over between the     |

| ; |          | -            | l low bytes. Reading    |

| ' |          | 5            |                         |

| ; | 5        | and low byc  | es now will read a good |

| ; | value.   |              |                         |

| ; |          |              |                         |

|   | MOVF     | TMR1H, W     | ;Read high byte         |

|   | MOVWF    | TMPH         | ;                       |

|   | MOVF     | TMR1L, W     | ;Read low byte          |

|   | MOVWF    | TMPL         | i                       |

| ; | Re-enabl | e the Intern | rupts (if required)     |

|   | ONTINUE  |              | ;Continue with your     |

|   |          |              | ; code                  |

|   |          |              | , coue                  |

### **10.6 Comparator Interrupts**

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be reset by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

| Note: | If a change in the CMCON register          |  |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | (C1OUT or C2OUT) should occur when a       |  |  |  |  |  |  |  |  |  |

|       | read operation is being executed (start of |  |  |  |  |  |  |  |  |  |

|       | the Q2 cycle), then the CMIF (PIR1<6>)     |  |  |  |  |  |  |  |  |  |

|       | interrupt flag may not get set.            |  |  |  |  |  |  |  |  |  |

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any write or read of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition and allow flag bit CMIF to be cleared.

#### 10.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from Sleep mode when enabled. While the comparator is powered-up, higher Sleep currents than shown in the power-down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators, CM<2:0> = 111, before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

# 10.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state. This forces the Comparator module to be in the comparator Reset mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at Reset time. The comparators will be powered-down during the Reset interval.

## 10.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 10-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

| TER 12-2: | RCSTA – RECEIVE STATUS AND CONTROL REGISTER (ADDRESS: 18h)                                                                                                                              |                                                            |              |              |                   |             |               |             |  |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------|--------------|-------------------|-------------|---------------|-------------|--|--|--|--|

|           | R/W-0                                                                                                                                                                                   | R/W-0                                                      | R/W-0        | R/W-0        | R/W-0             | R-0         | R-0           | R-x         |  |  |  |  |

|           | SPEN                                                                                                                                                                                    | RX9                                                        | SREN         | CREN         | ADEN              | FERR        | OERR          | RX9D        |  |  |  |  |

|           | bit 7                                                                                                                                                                                   | •                                                          |              | 1            |                   | •           | •             | bit 0       |  |  |  |  |

| bit 7     |                                                                                                                                                                                         | rial Port Ena<br>s RB1/RX/D                                |              | TX/CK pins a | as serial port pi | ns when bit | s TRISB<2:    | 1> are set) |  |  |  |  |

|           | <ul> <li>(Configures RB1/RX/DT and RB2/TX/CK pins as serial port pins when bits TRISB&lt;2:1&gt; are set)</li> <li>1 = Serial port enabled</li> <li>0 = Serial port disabled</li> </ul> |                                                            |              |              |                   |             |               |             |  |  |  |  |

| bit 6     | <b>RX9</b> : 9-bit                                                                                                                                                                      | Receive Ena                                                | able bit     |              |                   |             |               |             |  |  |  |  |

|           |                                                                                                                                                                                         | s 9-bit recep<br>s 8-bit recep                             |              |              |                   |             |               |             |  |  |  |  |

| bit 5     | SREN: Sin                                                                                                                                                                               | gle Receive                                                | Enable bit   |              |                   |             |               |             |  |  |  |  |

|           | Asynchron                                                                                                                                                                               |                                                            |              |              |                   |             |               |             |  |  |  |  |

|           | Don't ca<br>Synchrono                                                                                                                                                                   | ire<br>i <u>us mode - n</u>                                | naetor:      |              |                   |             |               |             |  |  |  |  |

|           |                                                                                                                                                                                         | bles single r                                              |              |              |                   |             |               |             |  |  |  |  |

|           | 0 = Disa                                                                                                                                                                                | ables single i                                             | receive      |              |                   |             |               |             |  |  |  |  |

|           |                                                                                                                                                                                         | is cleared af                                              |              | n is complet | e.                |             |               |             |  |  |  |  |

|           | <u>Synchronous mode - slave</u> :<br>Unused in this mode                                                                                                                                |                                                            |              |              |                   |             |               |             |  |  |  |  |

| bit 4     |                                                                                                                                                                                         |                                                            |              | le bit       |                   |             |               |             |  |  |  |  |

|           | CREN: Continuous Receive Enable bit<br>Asynchronous mode:                                                                                                                               |                                                            |              |              |                   |             |               |             |  |  |  |  |

|           | 1 = Enables continuous receive                                                                                                                                                          |                                                            |              |              |                   |             |               |             |  |  |  |  |

|           | 0 = Disables continuous receive                                                                                                                                                         |                                                            |              |              |                   |             |               |             |  |  |  |  |

|           | Synchronous mode:<br>1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)                                                                              |                                                            |              |              |                   |             |               |             |  |  |  |  |

|           |                                                                                                                                                                                         | ables continu                                              |              |              |                   |             |               | 0 01 (211)  |  |  |  |  |

| bit 3     | ADEN: Ad                                                                                                                                                                                | dress Detect                                               | t Enable bit |              |                   |             |               |             |  |  |  |  |

|           | Asynchronous mode 9-bit (RX9 = 1):<br>1 = Enables address detection, enable interrupt and load of the receive buffer when RSR<8><br>is set                                              |                                                            |              |              |                   |             |               |             |  |  |  |  |

|           | 0 = Disables address detection, all bytes are received, and ninth bit can be used as parity bit                                                                                         |                                                            |              |              |                   |             |               |             |  |  |  |  |

|           | Asynchronous mode 8-bit (RX9 = 0):<br>Unused in this mode                                                                                                                               |                                                            |              |              |                   |             |               |             |  |  |  |  |

|           | Synchronous mode<br>Unused in this mode                                                                                                                                                 |                                                            |              |              |                   |             |               |             |  |  |  |  |

| bit 2     | FERR: Fra                                                                                                                                                                               | iming Error b                                              | bit          |              |                   |             |               |             |  |  |  |  |

|           | 1 = Framin<br>0 = No frar                                                                                                                                                               |                                                            | n be update  | d by reading | RCREG regis       | ter and rec | eive next va  | ilid byte)  |  |  |  |  |

| bit 1     | OERR: Ov                                                                                                                                                                                | errun Error I                                              | oit          |              |                   |             |               |             |  |  |  |  |

|           | <ul> <li>1 = Overrun error (Can be cleared by clearing bit CREN)</li> <li>0 = No overrun error</li> </ul>                                                                               |                                                            |              |              |                   |             |               |             |  |  |  |  |

| bit 0     | <b>RX9D</b> : 9th                                                                                                                                                                       | <b>RX9D</b> : 9th bit of received data (Can be parity bit) |              |              |                   |             |               |             |  |  |  |  |

|           | Legend:                                                                                                                                                                                 |                                                            |              |              |                   |             |               | ]           |  |  |  |  |

|           | R = Reada                                                                                                                                                                               | able bit                                                   | VV = V       | Vritable bit | U = Unimp         | lemented b  | it, read as ' | D'          |  |  |  |  |

|           | -n = Value                                                                                                                                                                              | at POR                                                     | '1' = E      | Bit is set   | '0' = Bit is      | cleared     | x = Bit is u  | ıknown      |  |  |  |  |

|           | ,                                                                                                                                                                                       |                                                            |              |              |                   |             |               |             |  |  |  |  |

Follow these steps when setting up an Asynchronous Reception:

- 1. TRISB<1> and TRISB<2> should both be set to '1' to configure the RB1/RX/DT and RB2/TX/CK pins as inputs. Output drive, when required, is controlled by the peripheral circuitry.

- Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH. (Section 12.1 "USART Baud Rate Generator (BRG)").

- 3. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. Enable the reception by setting bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If an OERR error occurred, clear the error by clearing enable bit CREN.

| Address | Name  | Bit 7     | Bit 6                        | Bit 5     | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  |      | e on<br>DR |      | e on<br>ther<br>sets |

|---------|-------|-----------|------------------------------|-----------|-------|-------|--------|--------|--------|------|------------|------|----------------------|

| 0Ch     | PIR1  | EEIF      | CMIF                         | RCIF      | TXIF  | _     | CCP1IF | TMR2IF | TMR1IF | 0000 | -000       | 0000 | -000                 |

| 18h     | RCSTA | SPEN      | RX9                          | SREN      | CREN  | ADEN  | FERR   | OERR   | RX9D   | 0000 | 000x       | 0000 | 000x                 |

| 1Ah     | RCREG | USART R   | eceive D                     | Data Regi | ster  |       |        |        |        | 0000 | 0000       | 0000 | 0000                 |

| 8Ch     | PIE1  | EEIE      | CMIE                         | RCIE      | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE | 0000 | -000       | 0000 | -000                 |

| 98h     | TXSTA | CSRC      | TX9                          | TXEN      | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 | -010       | 0000 | -010                 |

| 99h     | SPBRG | Baud Rate | Baud Rate Generator Register |           |       |       |        |        |        |      |            | 0000 | 0000                 |

### TABLE 12-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

#### 12.5.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical except in the case of the Sleep mode. Also, bit SREN is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during Sleep. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Follow these steps when setting up a Synchronous Slave Reception:

- 1. TRISB<1> and TRISB<2> should both be set to '1' to configure the RB1/RX/DT and RB2/TX/CK pins as inputs. Output drive, when required, is controlled by the peripheral circuitry.

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. To enable reception, set enable bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If an OERR error occurred, clear the error by clearing bit CREN.

| IADLE I | ABLE 12-11. REGISTERS ASSOCIATED WITH STINCHRONOUS SLAVE TRANSMISSION |                                |          |         |         |       |        |        |        |                 |                           |  |

|---------|-----------------------------------------------------------------------|--------------------------------|----------|---------|---------|-------|--------|--------|--------|-----------------|---------------------------|--|

| Address | Name                                                                  | Bit 7                          | Bit 6    | Bit 5   | Bit 4   | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on all other Resets |  |

| 0Ch     | PIR1                                                                  | EEIF                           | CMIF     | RCIF    | TXIF    | _     | CCP1IF | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                 |  |

| 18h     | RCSTA                                                                 | SPEN                           | RX9      | SREN    | CREN    | ADEN  | FERR   | OERR   | RX9D   | 0000 000x       | 0000 000x                 |  |

| 19h     | TXREG                                                                 | USART                          | Transmit | Data Re | egister |       |        |        |        | 0000 0000       | 0000 0000                 |  |

| 8Ch     | PIE1                                                                  | EEIE                           | CMIE     | RCIE    | TXIE    | _     | CCP1IE | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                 |  |

| 98h     | TXSTA                                                                 | CSRC                           | TX9      | TXEN    | SYNC    | _     | BRGH   | TRMT   | TX9D   | 0000 -010       | 0000 -010                 |  |

| 99h     | SPBRG                                                                 | G Baud Rate Generator Register |          |         |         |       |        |        |        | 0000 0000       | 0000 0000                 |  |

|         |                                                                       |                                |          |         |         |       |        |        |        |                 |                           |  |

#### TABLE 12-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous slave transmission.

#### TABLE 12-12: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address | Name  | Bit 7                        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2     | Bit 1     | Bit 0  | Value on<br>POR | Value on all other Resets |

|---------|-------|------------------------------|-------|-------|-------|-------|-----------|-----------|--------|-----------------|---------------------------|

| 0Ch     | PIR1  | EEIF                         | CMIF  | RCIF  | TXIF  |       | CCP1IF    | TMR2IF    | TMR1IF | 0000 -000       | 0000 -000                 |

| 18h     | RCSTA | SPEN                         | RX9   | SREN  | CREN  | ADEN  | FERR      | OERR      | RX9D   | 0000 000x       | 0000 000x                 |

| 1Ah     | RCREG | USART Receive Data Register  |       |       |       |       | 0000 0000 | 0000 0000 |        |                 |                           |

| 8Ch     | PIE1  | EEIE                         | CMIE  | RCIE  | TXIE  | _     | CCP1IE    | TMR2IE    | TMR1IE | 0000 -000       | 0000 -000                 |

| 98h     | TXSTA | CSRC                         | TX9   | TXEN  | SYNC  |       | BRGH      | TRMT      | TX9D   | 0000 -010       | 0000 -010                 |

| 99h     | SPBRG | Baud Rate Generator Register |       |       |       |       | 0000 0000 | 0000 0000 |        |                 |                           |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous slave reception.

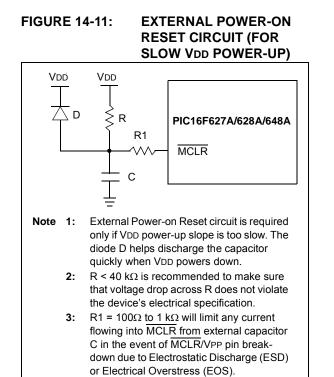

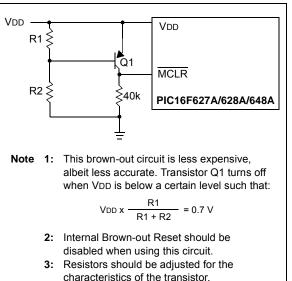

FIGURE 14-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

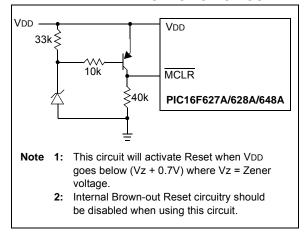

#### FIGURE 14-13: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

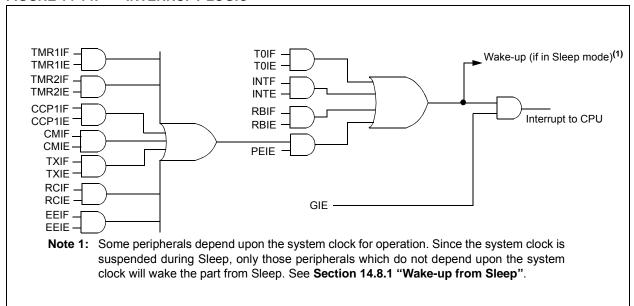

### 14.5 Interrupts

The PIC16F627A/628A/648A has 10 sources of interrupt:

- External Interrupt RB0/INT

- TMR0 Overflow Interrupt

- PORTB Change Interrupts (pins RB<7:4>)

- Comparator Interrupt

- USART Interrupt TX

- USART Interrupt RX

- CCP Interrupt

- TMR1 Overflow Interrupt

- TMR2 Match Interrupt

- Data EEPROM Interrupt

The Interrupt Control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A Global Interrupt Enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on Reset.

The "return-from-interrupt" instruction, RETFIE, exits interrupt routine as well as sets the GIE bit, which reenables RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag is contained in the special register PIR1. The corresponding interrupt enable bit is contained in special registers PIE1.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/ INT recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 14-15). The latency is the same for one or two-cycle instructions. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

#### FIGURE 14-14: INTERRUPT LOGIC

AND Literal with W

ANDLW

| ADDLW            | Add Literal and W                                                                                                          |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                          |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |  |  |  |

| Encoding:        | 11 111x kkkk kkkk                                                                                                          |  |  |  |  |

| Description:     | The contents of the W register<br>are added to the eight bit literal<br>'k' and the result is placed in the<br>W register. |  |  |  |  |

| Words:           | 1                                                                                                                          |  |  |  |  |

| Cycles:          | 1                                                                                                                          |  |  |  |  |

| Example          | ADDLW 0x15                                                                                                                 |  |  |  |  |

|                  | Before Instruction<br>W = 0x10<br>After Instruction<br>W = 0x25                                                            |  |  |  |  |

| Curstand                                                |                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                                 | [label] ANDLW k                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Operands:                                               | $0 \le k \le 255$                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Operation:                                              | (W) .AND. (k) $\rightarrow$ (W)                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Status Affected:                                        | Z                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Encoding:                                               | 11 1001 kkkk kkkk                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Description:                                            | The contents of W register are<br>AND'ed with the eight bit literal<br>'k'. The result is placed in the W<br>register.                                                                                                                                                                                                                                    |  |  |  |

| Words:                                                  | 1                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Cycles:                                                 | 1                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Example                                                 | ANDLW 0x5F                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                         | Before Instruction<br>W = 0xA3<br>After Instruction                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                                         | W = 0x03                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| ANDWF                                                   | AND W with f                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Syntax:                                                 | [label] ANDWF f,d                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Operands:                                               | $0 \le f \le 127$                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                                                         | $d \in [0,1]$                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Operation:                                              | d ∈ [0,1]<br>(W) .AND. (f) → (dest)                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Operation:<br>Status Affected:                          |                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| •                                                       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Status Affected:                                        | (W) .AND. (f) $\rightarrow$ (dest)<br>Z                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Status Affected:<br>Encoding:                           | (W) .AND. (f) $\rightarrow$ (dest)<br>Z<br>00 0101 dfff ffff<br>AND the W register with register<br>'f'. If 'd' is '0', the result is stored<br>in the W register. If 'd' is '1', the<br>result is stored back in register                                                                                                                                |  |  |  |

| Status Affected:<br>Encoding:<br>Description:           | $\begin{array}{c c} (W) \ . AND. \ (f) \rightarrow (dest) \\ \hline Z \\ \hline 00 & 0101 & dfff & ffff \\ \hline AND \ the \ W \ register \ with \ register \\ \ 'f'. \ If \ 'd' \ is \ '0', \ the \ result \ is \ stored \\ in \ the \ W \ register. \ If \ 'd' \ is \ '1', \ the \\ result \ is \ stored \ back \ in \ register \\ \ 'f'. \end{array}$ |  |  |  |

| Status Affected:<br>Encoding:<br>Description:<br>Words: | (W) .AND. (f) $\rightarrow$ (dest)<br>Z<br>00 0101 dfff ffff<br>AND the W register with register<br>'f'. If 'd' is '0', the result is stored<br>in the W register. If 'd' is '1', the<br>result is stored back in register<br>'f'.<br>1                                                                                                                   |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                                        |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] ADDWF f,d                                                                                                                                                                |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                 |  |  |  |

| Operation:       | $(W) + (f) \to (dest)$                                                                                                                                                             |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                           |  |  |  |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                                  |  |  |  |

| Description:     | Add the contents of the W<br>register with register 'f'. If 'd' is<br>'0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |

| Words:           | 1                                                                                                                                                                                  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                  |  |  |  |

| Example          | ADDWF REG1, 0                                                                                                                                                                      |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>REG1 = 0xC2<br>After Instruction<br>W = 0xD9<br>REG1 = 0xC2<br>Z = 0<br>C = 0<br>DC = 0                                                          |  |  |  |

| IORLW            | Inclusive OR Literal with W                                                                                              |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                 |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                        |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                             |  |  |  |  |

| Status Affected: | Z                                                                                                                        |  |  |  |  |

| Encoding:        | 11 1000 kkkk kkkk                                                                                                        |  |  |  |  |

| Description:     | The contents of the W register is<br>OR'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |  |  |  |  |

| Words:           | 1                                                                                                                        |  |  |  |  |

| Cycles:          | 1<br>IORLW 0x35                                                                                                          |  |  |  |  |

| Example          |                                                                                                                          |  |  |  |  |

|                  | Before Instruction<br>W = 0x9A<br>After Instruction<br>W = 0xBF<br>Z = 0                                                 |  |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                    |  |  |  |  |

| MOVLW            | Move Literal to W                                                                                   |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                            |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                 |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                                 |  |  |  |  |  |

| Status Affected: | d: None                                                                                             |  |  |  |  |  |

| Encoding:        | oding: 11 00xx kkkk kkkk                                                                            |  |  |  |  |  |

| Description:     | The eight bit literal 'k' is loaded<br>into W register. The "don't<br>cares" will assemble as '0's. |  |  |  |  |  |

| Words:           | 1                                                                                                   |  |  |  |  |  |

| Cycles:          | 1                                                                                                   |  |  |  |  |  |

| <u>Example</u>   | MOVLW 0x5A                                                                                          |  |  |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                                       |  |  |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                       |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in$ [0,1]                                                                                                                                          |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (dest)                                                                                                                                           |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |

| Encoding:        | 00 0100 dfff ffff                                                                                                                                                           |  |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result<br>is placed in the W register. If 'd'<br>is '1', the result is placed back in<br>register 'f'. |  |  |  |  |

| Words:           | 1                                                                                                                                                                           |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                           |  |  |  |  |

| Example          | IORWF REG1, 0                                                                                                                                                               |  |  |  |  |

|                  | Before Instruction<br>REG1 = 0x13<br>W = 0x91<br>After Instruction<br>REG1 = 0x13<br>W = 0x93<br>Z = 1                                                                      |  |  |  |  |

| MOVF             | Move f                                                                                                                                                                                                                                                                                   |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                                |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in[0,1] \end{array}$                                                                                                                                                                                                                               |  |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                                 |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Encoding:        | 00 1000 dfff ffff                                                                                                                                                                                                                                                                        |  |  |  |  |

| Description:     | The contents of register 'f' is<br>moved to a destination<br>dependent upon the status of<br>'d'. If $d = 0$ , destination is W<br>register. If $d = 1$ , the destination<br>is file register f itself. $d = 1$ is<br>useful to test a file register since<br>status flag Z is affected. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Example          | MOVF REG1, 0                                                                                                                                                                                                                                                                             |  |  |  |  |

|                  | After Instruction<br>W= value in REG1 register<br>Z = 1                                                                                                                                                                                                                                  |  |  |  |  |

| RETLW             | Return with Literal in W                                                                                                                                                               | RLF               | Rotate Left f through Carry                                                                                                                                                                                          |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:           | [ <i>label</i> ] RETLW k                                                                                                                                                               | Syntax:           | [ <i>label</i> ] RLF f,d                                                                                                                                                                                             |  |  |  |

| Operands:         | $0 \le k \le 255$                                                                                                                                                                      | Operands:         | $0 \leq f \leq 127$                                                                                                                                                                                                  |  |  |  |

| Operation:        | $k \rightarrow (W);$                                                                                                                                                                   |                   | d ∈ [0,1]                                                                                                                                                                                                            |  |  |  |

|                   | $TOS \rightarrow PC$                                                                                                                                                                   | Operation:        | See description below                                                                                                                                                                                                |  |  |  |

| Status Affected:  | None                                                                                                                                                                                   | Status Affected:  | С                                                                                                                                                                                                                    |  |  |  |

| Encoding:         | 11 01xx kkkk kkkk                                                                                                                                                                      | Encoding:         | 00 1101 dfff ffff                                                                                                                                                                                                    |  |  |  |