Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 201010                     |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 224 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf627a-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| Address | Name   | Bit 7       | Bit 6                                             | Bit 5         | Bit 4     | Bit 3        | Bit 2         | Bit 1       | Bit 0   | Value on<br>POR<br>Reset <sup>(1)</sup> | Details<br>on Page |  |

|---------|--------|-------------|---------------------------------------------------|---------------|-----------|--------------|---------------|-------------|---------|-----------------------------------------|--------------------|--|

| Bank 2  |        |             |                                                   |               |           |              |               |             |         |                                         |                    |  |

| 100h    | INDF   | Addressing  | g this location                                   | cal register) | xxxx xxxx | 30           |               |             |         |                                         |                    |  |

| 101h    | TMR0   | Timer0 Mo   | dule's Registe                                    | er            |           |              |               |             |         | xxxx xxxx                               | 47                 |  |

| 102h    | PCL    | Program C   | rogram Counter's (PC) Least Significant Byte      |               |           |              |               |             |         |                                         |                    |  |

| 103h    | STATUS | IRP         | RP1                                               | RP0           | TO        | PD           | Z             | DC          | С       | 0001 1xxx                               | 24                 |  |

| 104h    | FSR    | Indirect Da | ndirect Data Memory Address Pointer               |               |           |              |               |             |         |                                         |                    |  |

| 105h    | _      | Unimpleme   | direct Data Memory Address Pointer 2 nimplemented |               |           |              |               |             |         |                                         |                    |  |

| 106h    | PORTB  | RB7         | RB6                                               | RB5           | RB4       | RB3          | RB2           | RB1         | RB0     | xxxx xxxx                               | 38                 |  |

| 107h    | _      | Unimpleme   | ented                                             | •             | •         | •            |               | •           |         | _                                       | _                  |  |

| 108h    | _      | Unimpleme   | ented                                             |               |           |              |               |             |         | _                                       | _                  |  |

| 109h    | _      | Unimpleme   | ented                                             |               |           |              |               |             |         | _                                       | —                  |  |

| 10Ah    | PCLATH | _           | _                                                 | _             | Write     | Buffer for u | pper 5 bits o | f Program C | Counter | 0 0000                                  | 30                 |  |

| 10Bh    | INTCON | GIE         | PEIE                                              | T0IE          | INTE      | RBIE         | TOIF          | INTF        | RBIF    | 0000 000x                               | 26                 |  |

| 10Ch    | —      | Unimpleme   | ented                                             |               |           |              |               |             |         | —                                       |                    |  |

| 10Dh    | —      | Unimpleme   | ented                                             |               |           |              |               |             |         | —                                       | _                  |  |

| 10Eh    | _      | Unimpleme   | ented                                             |               |           |              |               |             |         | _                                       |                    |  |

| 10Fh    | _      | Unimpleme   | ented                                             |               |           |              |               |             |         | _                                       |                    |  |

| 110h    |        | Unimpleme   | ented                                             |               |           |              |               |             |         | _                                       |                    |  |

| 111h    |        | Unimpleme   | ented                                             |               |           |              |               |             |         | —                                       | —                  |  |

| 112h    |        | Unimpleme   | ented                                             |               |           |              |               |             |         | —                                       | —                  |  |

| 113h    |        | Unimpleme   | ented                                             |               |           |              |               |             |         | —                                       | —                  |  |

| 114h    | —      | Unimpleme   | ented                                             |               |           |              |               |             |         | —                                       | _                  |  |

| 115h    | —      | Unimpleme   | ented                                             |               |           |              |               |             |         | _                                       | _                  |  |

| 116h    | —      | Unimpleme   | ented                                             |               |           |              |               |             |         | _                                       | —                  |  |

| 117h    | _      | Unimpleme   | ented                                             |               |           |              |               |             |         | _                                       |                    |  |

| 118h    | _      | Unimpleme   | ented                                             |               |           |              |               |             |         | _                                       |                    |  |

| 119h    |        | Unimpleme   |                                                   |               |           |              |               |             |         | _                                       |                    |  |

| 11Ah    |        | Unimpleme   |                                                   |               |           |              |               |             |         | —                                       | —                  |  |

| 11Bh    | _      | Unimpleme   |                                                   |               |           |              |               |             |         | —                                       | —                  |  |

| 11Ch    | _      | Unimpleme   |                                                   |               |           |              |               |             |         | _                                       | —                  |  |

| 11Dh    | -      | Unimpleme   |                                                   |               |           |              |               |             |         | —                                       | —                  |  |

| 11Eh    | -      | Unimpleme   |                                                   |               |           |              |               |             |         | —                                       | —                  |  |

| 11Fh    | —      | Unimpleme   | ented                                             |               |           |              |               |             |         | —                                       | —                  |  |

#### TABLE 4-5: SPECIAL FUNCTION REGISTERS SUMMARY BANK2

Legend:- = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented.Note1:For the initialization condition for registers tables, refer to Table 14-6 and Table 14-7.

# 5.3 I/O Programming Considerations

#### 5.3.1 BIDIRECTIONAL I/O PORTS

Any instruction that writes operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit 5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit 5 and PORTB is written to the output latches. If another bit of PORTB is used as a bidirectional I/O pin (e.g., bit 0) and is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit 0 is switched into Output mode later on, the content of the data latch may now be unknown.

Reading a port register reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-2 shows the effect of two sequential read-modify-write instructions (ex.,  ${\tt BCF}, {\tt BSF},$  etc.) on an I/O port

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-OR", "wired-AND"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-2: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

| ;Initial PORT settings:     | :PORTB<7:4> Inputs    |

|-----------------------------|-----------------------|

| ;                           | PORTB<3:0> Outputs    |

| ;PORTB<7:6> have extern     | nal pull-up and are   |

| ;not connected to other     | c circuitry           |

| ;                           |                       |

| ;                           | PORT latchPORT Pins   |

|                             |                       |

| BCF STATUS, RPO             | ;                     |

| BCF PORTB, 7                | ;01pp pppp 11pp pppp  |

| BSF STATUS, RPO             | ;                     |

|                             | ;10pp pppp 11pp pppp  |

| BCF TRISB, 6                | ;10pp pppp 10pp pppp  |

| ;                           | , the sets - set fore |

| ,<br>Note that the user may | v have expected the   |

| ; pin values to be 00pp     | -                     |

| ; caused RB7 to be latch    |                       |

| ; (High).                   | ica ab che più value  |

| , (111911).                 |                       |

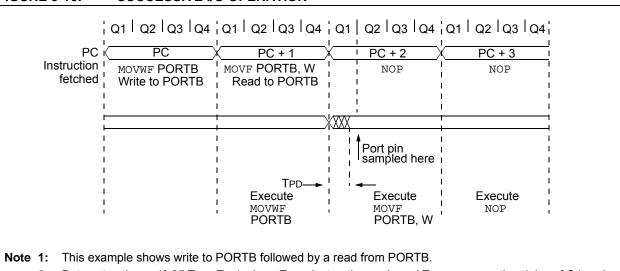

#### 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

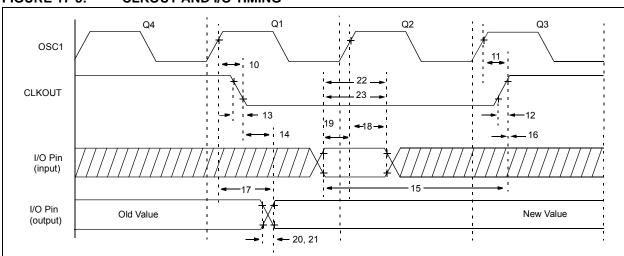

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-16). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction, which causes that file to be read into the CPU, is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

2: Data setup time = (0.25 TCY - TPD) where TCY = instruction cycle and TPD = propagation delay of Q1 cycle to output valid. Therefore, at higher clock frequencies, a write followed by a read may be problematic.

## FIGURE 5-16: SUCCESSIVE I/O OPERATION

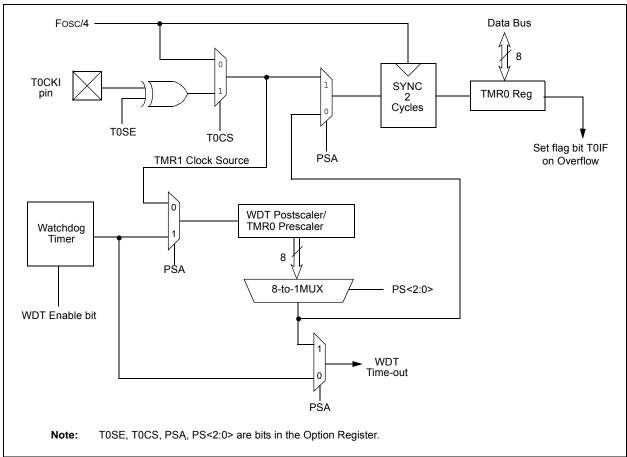

### 6.3 Timer0 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer. A prescaler assignment for the Timer0 module means that there is no postscaler for the Watchdog Timer, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x...etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

FIGURE 6-1: BLOCK DIAGRAM OF THE TIMER0/WDT

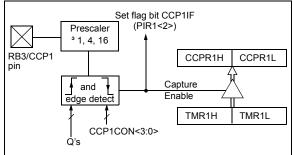

# 9.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The CCP (Capture/Compare/PWM) module contains a 16-bit register which can operate as a 16-bit Capture register, as a 16-bit Compare register or as a PWM master/slave Duty Cycle register. Table 9-1 shows the timer resources of the CCP module modes.

#### CCP1 Module

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

Additional information on the CCP module is available in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

#### TABLE 9-1: CCP MODE – TIMER RESOURCE

| CCP Mode | Timer Resource |  |  |  |

|----------|----------------|--|--|--|

| Capture  | Timer1         |  |  |  |

| Compare  | Timer1         |  |  |  |

| PWM      | Timer2         |  |  |  |

#### **REGISTER 9-1:** CCP1CON – CCP OPERATION REGISTER (ADDRESS: 17h)

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

| —     | —   | CCP1X | CCP1Y | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 |

| bit 7 |     |       |       |        |        |        | bit 0  |

- bit 7-6 Unimplemented: Read as '0'

- bit 5-4 CCP1X:CCP1Y: PWM Least Significant bits

- <u>Capture Mode</u> Unused <u>Compare Mode</u> Unused <u>PWM Mode</u>

These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.

#### bit 3-0 CCP1M<3:0>: CCPx Mode Select bits

- 0000 = Capture/Compare/PWM off (resets CCP1 module)

- 0100 = Capture mode, every falling edge

- 0101 = Capture mode, every rising edge

- 0110 = Capture mode, every 4th rising edge

- 0111 = Capture mode, every 16th rising edge

- 1000 = Compare mode, set output on match (CCP1IF bit is set)

- 1001 = Compare mode, clear output on match (CCP1IF bit is set)

- 1010 = Compare mode, generate software interrupt on match (CCP1IF bit is set, CCP1 pin is unaffected)

- 1011 = Compare mode, trigger special event (CCP1IF bit is set; CCP1 resets TMR1

- 11xx = PWM mode

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### 9.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RB3/CCP1. An event is defined as:

- · Every falling edge

- Every rising edge

- · Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M<3:0> (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 9.1.1 CCP PIN CONFIGURATION

In Capture mode, the RB3/CCP1 pin should be configured as an input by setting the TRISB<3> bit.

| Note: | If the RB3/CCP1 is configured as an     |

|-------|-----------------------------------------|

|       | output, a write to the port can cause a |

|       | capture condition.                      |

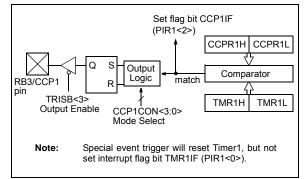

#### FIGURE 9-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 9.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 9.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in Operating mode.

### 9.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M<3:0>. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 9-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 9-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ; the new prescaler     |

|       |             | ; mode value and CCP ON |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ; value                 |

## 9.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RB3/CCP1 pin is:

- Driven high

- Driven low

- · Remains unchanged

The action on the pin is based on the value of control bits CCP1M<3:0> (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

FIGURE 9-2: C

#### COMPARE MODE OPERATION BLOCK DIAGRAM

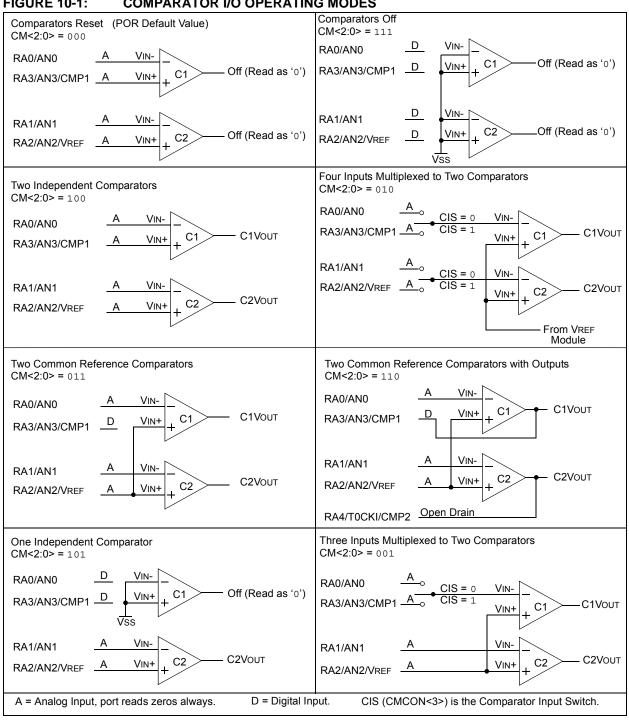

#### **10.1** Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select the mode. Figure 10-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode.

If the Comparator mode is changed, the comparator output level may not be valid for the specified mode change delay shown in Table 17-2.

- Note 1: Comparator interrupts should be disabled during a Comparator mode change, otherwise a false interrupt may occur.

- 2: Comparators can have an inverted output. See Figure 10-1.

#### FIGURE 10-1: COMPARATOR I/O OPERATING MODES

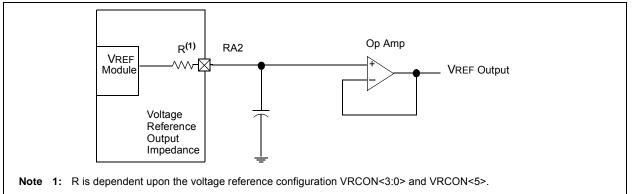

#### FIGURE 11-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 11-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR | Value On<br>All Other<br>Resets |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 9Fh     | VRCON | VREN   | VROE   | VRR    | —      | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 1Fh     | CMCON | C2OUT  | C10UT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 85h     | TRISA | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

**Legend:** - = Unimplemented, read as '0'.

| BAUD     | Fosc = 20 MHz |        | SPBRG              | 16 MHz |        | SPBRG              | 10 MHz | SPBRG  |                    |

|----------|---------------|--------|--------------------|--------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD         | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 0.3      | NA            |        | _                  | NA     |        | _                  | NA     | _      | _                  |

| 1.2      | 1.221         | +1.73% | 255                | 1.202  | +0.16% | 207                | 1.202  | +0.16% | 129                |

| 2.4      | 2.404         | +0.16% | 129                | 2.404  | +0.16% | 103                | 2.404  | +0.16% | 64                 |

| 9.6      | 9.469         | -1.36% | 32                 | 9.615  | +0.16% | 25                 | 9.766  | +1.73% | 15                 |

| 19.2     | 19.53         | +1.73% | 15                 | 19.23  | +0.16% | 12                 | 19.53  | +1.73V | 7                  |

| 76.8     | 78.13         | +1.73% | 3                  | 83.33  | +8.51% | 2                  | 78.13  | +1.73% | 1                  |

| 96       | 104.2         | +8.51% | 2                  | NA     | _      | _                  | NA     | _      | _                  |

| 300      | 312.5         | +4.17% | 0                  | NA     | _      | _                  | NA     | _      | _                  |

| 500      | NA            | _      | _                  | NA     | _      | _                  | NA     | _      | _                  |

| HIGH     | 312.5         | _      | 0                  | 250    | _      | 0                  | 156.3  | _      | 0                  |

| LOW      | 1.221         |        | 255                | 0.977  |        | 255                | 0.6104 | _      | 255                |

| <b>TABLE 12-4</b> : | BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0) |

|---------------------|---------------------------------------------|

|---------------------|---------------------------------------------|

| BAUD     | Fosc = 7.15909 MHz |        | SPBRG 5.0688 MHz   |        |        | SPBRG              | 4 MHz  | SPBRG  |                    |

|----------|--------------------|--------|--------------------|--------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD              | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 0.3      | NA                 | _      | _                  | 0.31   | +3.13% | 255                | 0.3005 | -0.17% | 207                |

| 1.2      | 1.203              | +0.23% | 92                 | 1.2    | 0      | 65                 | 1.202  | +1.67% | 51                 |

| 2.4      | 2.380              | -0.83% | 46                 | 2.4    | 0      | 32                 | 2.404  | +1.67% | 25                 |

| 9.6      | 9.322              | -2.90% | 11                 | 9.9    | +3.13% | 7                  | NA     | _      | _                  |

| 19.2     | 18.64              | -2.90% | 5                  | 19.8   | +3.13% | 3                  | NA     | _      | _                  |

| 76.8     | NA                 | _      | _                  | 79.2   | +3.13% | 0                  | NA     | _      | _                  |

| 96       | NA                 | _      | _                  | NA     | _      | _                  | NA     | _      | _                  |

| 300      | NA                 | _      | _                  | NA     |        | _                  | NA     | _      | _                  |

| 500      | NA                 | _      | _                  | NA     | _      | _                  | NA     | _      | _                  |

| HIGH     | 111.9              | _      | 0                  | 79.2   |        | 0                  | 62.500 | _      | 0                  |

| LOW      | 0.437              | _      | 255                | 0.3094 |        | 255                | 3.906  | _      | 255                |

| BAUD     | Fosc = 3.57 | 9545 MHz | SPBRG              | 1 MHz  |        | SPBRG              | 32.768 kHz |         | SPBRG<br>value |

|----------|-------------|----------|--------------------|--------|--------|--------------------|------------|---------|----------------|

| RATE (K) | KBAUD       | ERROR    | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) | KBAUD      | ERROR   | (decimal)      |

| 0.3      | 0.301       | +0.23%   | 185                | 0.300  | +0.16% | 51                 | 0.256      | -14.67% | 1              |

| 1.2      | 1.190       | -0.83%   | 46                 | 1.202  | +0.16% | 12                 | NA         | _       | _              |

| 2.4      | 2.432       | +1.32%   | 22                 | 2.232  | -6.99% | 6                  | NA         | _       | _              |

| 9.6      | 9.322       | -2.90%   | 5                  | NA     | _      | _                  | NA         | _       | _              |

| 19.2     | 18.64       | -2.90%   | 2                  | NA     | _      | _                  | NA         | _       | _              |

| 76.8     | NA          | _        | _                  | NA     | _      | _                  | NA         | _       | _              |

| 96       | NA          | _        | _                  | NA     |        | _                  | NA         | _       | _              |

| 300      | NA          | _        | _                  | NA     | _      | _                  | NA         | _       | _              |

| 500      | NA          | _        | _                  | NA     |        | _                  | NA         | _       | _              |

| HIGH     | 55.93       | _        | 0                  | 15.63  |        | 0                  | 0.512      | _       | 0              |

| LOW      | 0.2185      | _        | 255                | 0.0610 |        | 255                | 0.0020     | _       | 255            |

| Address | Name  | Bit 7    | Bit 6                        | Bit 5    | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on all other Resets |

|---------|-------|----------|------------------------------|----------|--------|-------|--------|--------|--------|-----------------|---------------------------|

| 0Ch     | PIR1  | EEIF     | CMIF                         | RCIF     | TXIF   | _     | CCP1IF | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                 |

| 18h     | RCSTA | SPEN     | RX9                          | SREN     | CREN   | ADEN  | FERR   | OERR   | RX9D   | 0000 000x       | 0000 000x                 |

| 19h     | TXREG | USART 1  | USART Transmit Data Register |          |        |       |        |        |        |                 | 0000 0000                 |

| 8Ch     | PIE1  | EEIE     | CMIE                         | RCIE     | TXIE   | _     | CCP1IE | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                 |

| 98h     | TXSTA | CSRC     | TX9                          | TXEN     | SYNC   | _     | BRGH   | TRMT   | TX9D   | 0000 -010       | 0000 -010                 |

| 99h     | SPBRG | Baud Rat | te Gener                     | ator Reg | gister |       |        |        |        | 0000 0000       | 0000 0000                 |

#### TABLE 12-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

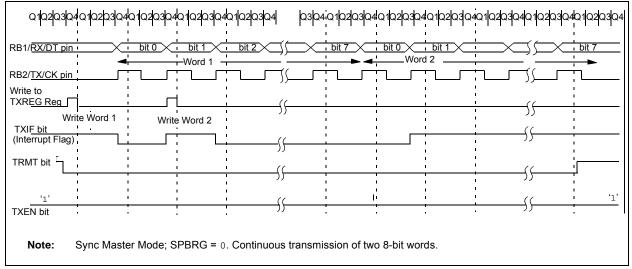

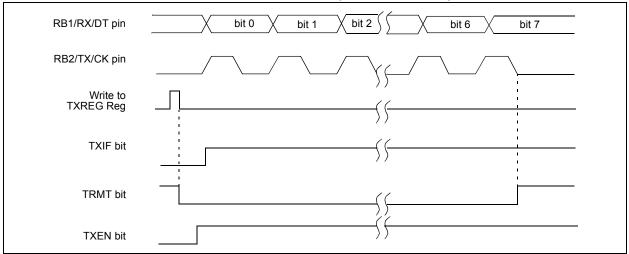

#### FIGURE 12-8: SYNCHRONOUS TRANSMISSION

#### FIGURE 12-9: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

#### 12.5.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical except in the case of the Sleep mode. Also, bit SREN is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during Sleep. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Follow these steps when setting up a Synchronous Slave Reception:

- 1. TRISB<1> and TRISB<2> should both be set to '1' to configure the RB1/RX/DT and RB2/TX/CK pins as inputs. Output drive, when required, is controlled by the peripheral circuitry.

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. To enable reception, set enable bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If an OERR error occurred, clear the error by clearing bit CREN.

| TABLE 12-11. REGISTERS ASSOCIATED WITH STNCHRONOUS SLAVE TRANSMISSION |       |         |                              |           |        |       |        |        |        |                 |                           |

|-----------------------------------------------------------------------|-------|---------|------------------------------|-----------|--------|-------|--------|--------|--------|-----------------|---------------------------|

| Address                                                               | Name  | Bit 7   | Bit 6                        | Bit 5     | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on all other Resets |

| 0Ch                                                                   | PIR1  | EEIF    | CMIF                         | RCIF      | TXIF   | _     | CCP1IF | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                 |

| 18h                                                                   | RCSTA | SPEN    | RX9                          | SREN      | CREN   | ADEN  | FERR   | OERR   | RX9D   | 0000 000x       | 0000 000x                 |

| 19h                                                                   | TXREG | USART   | USART Transmit Data Register |           |        |       |        |        |        |                 | 0000 0000                 |

| 8Ch                                                                   | PIE1  | EEIE    | CMIE                         | RCIE      | TXIE   | _     | CCP1IE | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                 |

| 98h                                                                   | TXSTA | CSRC    | TX9                          | TXEN      | SYNC   | _     | BRGH   | TRMT   | TX9D   | 0000 -010       | 0000 -010                 |

| 99h                                                                   | SPBRG | Baud Ra | te Gene                      | rator Reg | gister |       |        |        |        | 0000 0000       | 0000 0000                 |

|                                                                       |       |         |                              |           |        |       |        |        |        |                 |                           |

#### TABLE 12-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous slave transmission.

#### TABLE 12-12: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address | Name                                   | Bit 7   | Bit 6   | Bit 5 | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR | Value on all other Resets |

|---------|----------------------------------------|---------|---------|-------|-----------|-----------|--------|--------|-----------|-----------------|---------------------------|

| 0Ch     | PIR1                                   | EEIF    | CMIF    | RCIF  | TXIF      |           | CCP1IF | TMR2IF | TMR1IF    | 0000 -000       | 0000 -000                 |

| 18h     | RCSTA                                  | SPEN    | RX9     | SREN  | CREN      | ADEN      | FERR   | OERR   | RX9D      | 0000 000x       | 0000 000x                 |

| 1Ah     | RCREG                                  | USART F | Receive |       | 0000 0000 | 0000 0000 |        |        |           |                 |                           |

| 8Ch     | PIE1                                   | EEIE    | CMIE    | RCIE  | TXIE      | _         | CCP1IE | TMR2IE | TMR1IE    | 0000 -000       | 0000 -000                 |

| 98h     | TXSTA                                  | CSRC    | TX9     | TXEN  | SYNC      |           | BRGH   | TRMT   | TX9D      | 0000 -010       | 0000 -010                 |

| 99h     | 99h SPBRG Baud Rate Generator Register |         |         |       |           |           |        |        | 0000 0000 | 0000 0000       |                           |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous slave reception.

NOTES:

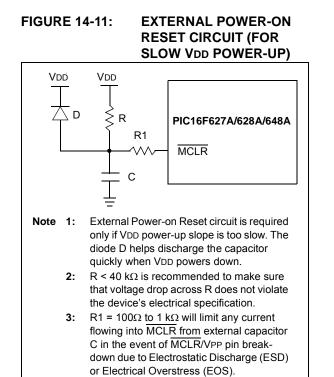

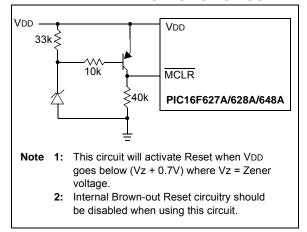

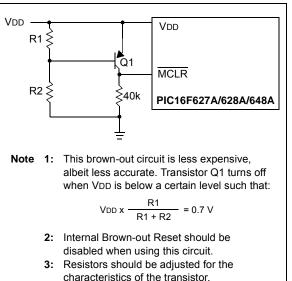

FIGURE 14-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

#### FIGURE 14-13: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

| INCF                              | Increme                                 | nt f                                                                                                                                                                            |           |      |                                                                                     | INCFSZ           | Increm                                                                                                                                                                                                                                        | ent f, Sk                          | tip if 0 |               |  |

|-----------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|-------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------|---------------|--|

| Syntax:                           | [ label ]                               | INCF                                                                                                                                                                            | f,d       |      | I                                                                                   | Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                            |                                    |          |               |  |

| Operands:                         |                                         | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                     |           |      |                                                                                     | Operands:        |                                                                                                                                                                                                                                               | $0 \le f \le 127$<br>d $\in [0,1]$ |          |               |  |

| Operation:                        | (f) + 1 →                               | (f) + 1 $\rightarrow$ (dest)                                                                                                                                                    |           |      |                                                                                     | Operation:       | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                              |                                    |          |               |  |

| Status Affected:                  | Z                                       |                                                                                                                                                                                 |           |      |                                                                                     | Status Affected: | None                                                                                                                                                                                                                                          |                                    |          |               |  |

| Encoding:                         | 00                                      | 1010                                                                                                                                                                            | dfff      | ffff |                                                                                     | Encoding:        | 00                                                                                                                                                                                                                                            | 1111                               | dfff     | ffff          |  |

| Description:<br>Words:<br>Cycles: | incremer<br>result is p<br>If 'd' is '1 | The contents of register 'f' are<br>incremented. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is placed<br>back in register 'f'.<br>1 |           |      |                                                                                     | Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is placed<br>back in register 'f'.<br>If the result is '0', the next<br>instruction, which is already |                                    |          |               |  |

| Example                           | INCF<br>Before Ir                       | REG1,                                                                                                                                                                           |           |      | fetched, is discarded. A NOP is executed instead making it a two-cycle instruction. |                  |                                                                                                                                                                                                                                               |                                    |          |               |  |

|                                   |                                         | EG1 =                                                                                                                                                                           |           |      |                                                                                     | Words:           | 1                                                                                                                                                                                                                                             |                                    |          |               |  |

|                                   | Z                                       |                                                                                                                                                                                 | 0         |      |                                                                                     | Cycles:          |                                                                                                                                                                                                                                               |                                    |          |               |  |

|                                   | After Insi<br>RE<br>Z                   | EG1 =                                                                                                                                                                           | 0x00<br>1 |      |                                                                                     | Example          | 1(2)<br>HERE<br>CONTIN                                                                                                                                                                                                                        | INCF<br>GOTO<br>UE •<br>•          |          | EG1, 1<br>DOP |  |

|                                   |                                         |                                                                                                                                                                                 |           |      |                                                                                     |                  | Before                                                                                                                                                                                                                                        | Instructio                         | on       |               |  |

PC = address HERE After Instruction REG1 = REG1 + 1 if CNT = 0, PC = address CONTINUE if REG1≠ 0, PC = address HERE +1

# 16.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit™ 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

### 16.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

## 16.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 16.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 16.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 16.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

### TABLE 17-2: COMPARATOR SPECIFICATIONS

|              | Operating Conditions: 2.0V < VDD <5.5V, -40°C < TA < +125°C, unless otherwise stated. |        |     |      |            |            |                                      |  |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------|--------|-----|------|------------|------------|--------------------------------------|--|--|--|--|--|

| Param<br>No. | Characteristics                                                                       | Sym    | Min | Тур  | Мах        | Units      | Comments                             |  |  |  |  |  |

| D300         | Input Offset Voltage                                                                  | VIOFF  |     | ±5.0 | ±10        | mV         |                                      |  |  |  |  |  |

| D301         | Input Common Mode Voltage                                                             | VICM   | 0   | _    | Vdd - 1.5* | V          |                                      |  |  |  |  |  |

| D302         | Common Mode Rejection Ratio                                                           | CMRR   | 55* | _    | —          | db         |                                      |  |  |  |  |  |

| D303         | Response Time <sup>(1)</sup>                                                          | TRESP  | _   | 300  | 400*       | ns         | VDD = 3.0V to 5.5V<br>-40° to +85°C  |  |  |  |  |  |

|              |                                                                                       |        | —   | 400  | 600*       | ns         | VDD = 3.0V to 5.5V<br>-85° to +125°C |  |  |  |  |  |

|              |                                                                                       |        | —   | 400  | 600*       | ns         | VDD = 2.0V to 3.0V<br>-40° to +85°C  |  |  |  |  |  |

| D304         | Comparator Mode Change to Output Valid                                                | Тмс2оv |     | 300  | 10*        | μ <b>S</b> |                                      |  |  |  |  |  |

\* These parameters are characterized but not tested.

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

#### TABLE 17-3: VOLTAGE REFERENCE SPECIFICATIONS

|             | Operating Conditions: 2.0V < VDD < 5.5V, -40°C < TA < +125°C, unless otherwise stated. |      |     |     |                                              |            |                                             |  |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------|------|-----|-----|----------------------------------------------|------------|---------------------------------------------|--|--|--|--|--|

| Spec<br>No. | Characteristics                                                                        | Sym  | Min | Тур | Max                                          | Units      | Comments                                    |  |  |  |  |  |

| D310        | Resolution                                                                             | VRES | —   | -   | VDD/24<br>VDD/32                             | LSb<br>LSb | Low Range (VRR = 1)<br>High Range (VRR = 0) |  |  |  |  |  |

| D311        | Absolute Accuracy                                                                      | VRAA | _   | _   | 1/4 <sup>(2)</sup> *<br>1/2 <sup>(2)</sup> * | LSb<br>LSb | Low Range (VRR = 1)<br>High Range (VRR = 0) |  |  |  |  |  |

| D312        | Unit Resistor Value (R)                                                                | Vrur | _   | 2k* | _                                            | Ω          |                                             |  |  |  |  |  |

| D313        | Settling Time <sup>(1)</sup>                                                           | TSET | _   | _   | 10*                                          | μS         |                                             |  |  |  |  |  |

\* These parameters are characterized but not tested.

Note 1: Settling time measured while VRR = 1 and VR<3:0> transitions from '0000' to '1111'.

2: When VDD is between 2.0V and 3.0V, the VREF output voltage levels on RA2 described by the equation:[VDD/2 ± (3 – VDD)/2] may cause the Absolute Accuracy (VRAA) of the VREF output signal on RA2 to be greater than the stated max.

| Parameter<br>No. | Sym     | Characteristic                | Min  | Тур | Max  | Units | Conditions                                                                                                                                                              |

|------------------|---------|-------------------------------|------|-----|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F10              | Fiosc   | Oscillator Center frequency   | _    | 4   | _    | MHz   |                                                                                                                                                                         |

| F13              | ∆losc   | Oscillator Accuracy           | 3.96 | 4   | 4.04 | MHz   | VDD = 3.5 V, 25°C                                                                                                                                                       |

|                  |         | 5                             | 3.92 | 4   | 4.08 | MHz   | $2.0V \le VDD \le 5.5V$<br>$0^{\circ}C \le TA \le +85^{\circ}C$                                                                                                         |

|                  |         |                               | 3.80 | 4   | 4.20 | MHz   | $\begin{array}{l} 2.0V \leq VDD \leq 5.5V \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ (IND)} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ (EXT)} \end{array}$ |

| F14 <sup>*</sup> | TIOSCST | Oscillator Wake-up from Sleep |      | 6   | 8    | μS    | VDD = 2.0V, -40°C to +85°C                                                                                                                                              |

|                  |         | start-up time                 |      | 4   | 6    | μS    | VDD = 3.0V, -40°C to +85°C                                                                                                                                              |

|                  |         |                               |      | 3   | 5    | μS    | VDD = 5.0V, -40°C to +85°C                                                                                                                                              |

TABLE 17-5: PRECISION INTERNAL OSCILLATOR PARAMETERS

Legend: TBD = To Be Determined.

\* Characterized but not tested.

#### FIGURE 17-5: CLKOUT AND I/O TIMING

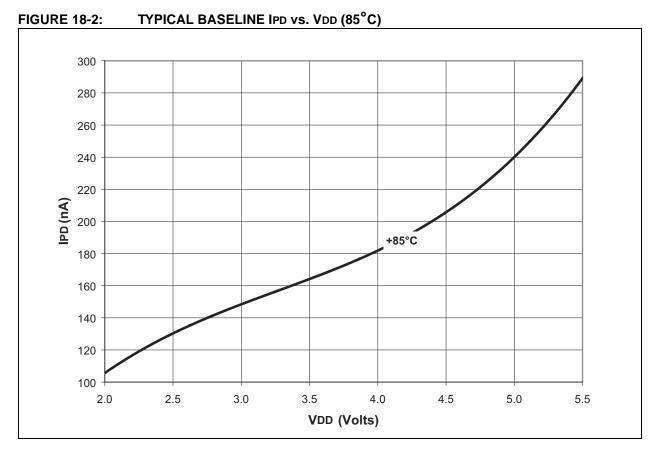

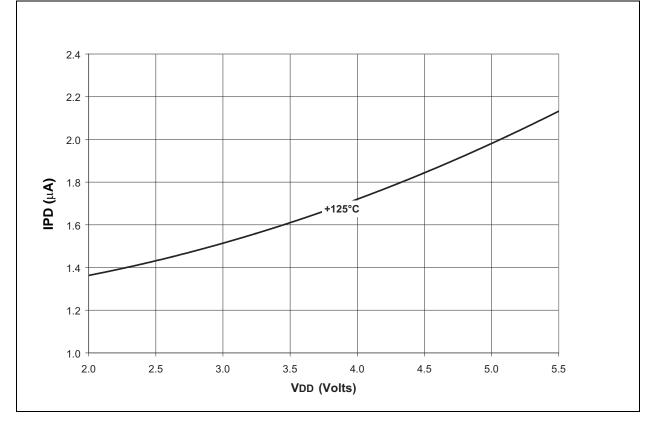

FIGURE 18-3: TYPICAL BASELINE CURRENT IPD vs. VDD (125°C)

#### INDEX

| 1 |    |

|---|----|

| ^ | ۰. |

| A/D                         |     |

|-----------------------------|-----|

| Special Event Trigger (CCP) | 59  |

| Absolute Maximum Ratings    | 135 |

| ADDLW Instruction           | 119 |

| ADDWF Instruction           |     |

| ANDLW Instruction           |     |

| ANDWF Instruction           |     |

| Architectural Overview      | 11  |

| Assembler                   |     |

| MPASM Assembler             | 132 |

| В                           |     |

| Baud Rate Error             | 75  |

| Baud Rate Formula           | 75  |

| BCF Instruction             | 120 |

| Block Diagrams              |     |

| Comparator                  |     |

| I/O Operating Modes         |     |

| Modified Comparator Output  | 66  |

| I/O Ports                   |     |

| RB0/INT Pin                 |     |

| RB1/RX/DT Pin               |     |

| RB2/TX/CK Pin               |     |

| RB3/CCP1 Pin                |     |

| RB4/PGM Pin                 |     |

| RB5 Pin                     |     |

| RB6/T1OSO/T1CKI Pin         |     |

| RB7/T10SI Pin               |     |

| RC Oscillator Mode          |     |

| USART Receive               |     |

| USART Transmit              |     |

| BRGH bit                    |     |

| Brown-Out Reset (BOR)       |     |

| BSF Instruction             |     |

| BTFSC Instruction           |     |

| BTFSS Instruction           | 121 |

# С

| C Compilers                         |     |

|-------------------------------------|-----|

| MPLAB C18                           | 132 |

| CALL Instruction                    | 121 |

| Capture (CCP Module)                | 58  |

| Block Diagram                       | 58  |

| CCP Pin Configuration               | 58  |

| CCPR1H:CCPR1L Registers             | 58  |

| Changing Between Capture Prescalers | 58  |

| Prescaler                           | 58  |

| Software Interrupt                  | 58  |

| Timer1 Mode Selection               | 58  |

| Capture/Compare/PWM (CCP)           | 57  |

| Capture Mode. See Capture           |     |

| CCP1                                | 57  |

| CCPR1H Register                     | 57  |

| CCPR1L Register                     | 57  |

| CCP2                                | 57  |

| Compare Mode. See Compare           |     |

| PWM Mode. See PWM                   |     |

| Timer Resources                     | 57  |

| CCP1CON Register                    | 57  |

| CCP1M Bits                          | 57  |

| CCP1X:CCP1Y Bits                    | 57  |

| CCP2CON Register                    |     |

| CCP2M<3:2> Bits                     | 57  |

| CCP2X:CCP2Y Bits                     | 57  |

|--------------------------------------|-----|

| Clocking Scheme/Instruction Cycle    |     |

| CLRF Instruction                     |     |

| CLRW Instruction                     |     |

| CLRWDT Instruction                   | 122 |

| CMCON Register                       |     |

| Code Examples                        |     |

| Data EEPROM Refresh Routine          | 94  |

| Code Protection                      | 113 |

| COMF Instruction                     | 122 |

| Comparator                           |     |

| Block Diagrams                       |     |

| I/O Operating Modes                  | 64  |

| Modified Comparator Output           | 66  |

| Comparator Module                    | 63  |

| Configuration                        | 64  |

| Interrupts                           | 67  |

| Operation                            | 65  |

| Reference                            | 65  |

| Compare (CCP Module)                 | 58  |

| Block Diagram                        |     |

| CCP Pin Configuration                | 59  |

| CCPR1H:CCPR1L Registers              | 58  |

| Software Interrupt                   | 59  |

| Special Event Trigger                | 59  |

| Timer1 Mode Selection                | 59  |

| CONFIG Register                      | 98  |

| Configuration Bits                   | 97  |

| Crystal Operation                    | 99  |

| Customer Change Notification Service | 173 |

| Customer Notification Service        |     |

| Customer Support                     | 173 |

#### D

| Data EEPROM Memory               |     |

|----------------------------------|-----|

| EECON1 Register                  |     |

| EECON2 Register                  |     |

| Operation During Code Protection | 95  |

| Reading                          | 93  |

| Spurious Write Protection        | 93  |

| Using                            |     |

| Write Verify                     | 93  |

| Writing to                       | 93  |

| Data Memory Organization         | 17  |

| DECF Instruction                 | 122 |

| DECFSZ Instruction               | 123 |

| Development Support              | 131 |

| Device Differences               | 171 |

| Device Migrations                | 172 |

| Dual-speed Oscillator Modes      | 101 |

|                                  |     |

### Ε

| EECON1 Register                     |  |

|-------------------------------------|--|

| EECON1 register                     |  |

| EECON2 register                     |  |

| Errata                              |  |

| External Crystal Oscillator Circuit |  |

### F

Fuses. See Configuration Bits

#### G

| General-Purpose Register File 17 | , |

|----------------------------------|---|

| GOTO Instruction                 | 3 |