Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf648a-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

NOTES:

#### FIGURE 4-2: DATA MEMORY MAP OF THE PIC16F627A AND PIC16F628A

| direct addr. <sup>(1)</sup> | 00h | Indirect addr. <sup>(1)</sup> | 80h | Indirect addr. <sup>(1)</sup> | 100h | Indirect addr. <sup>(1)</sup> |

|-----------------------------|-----|-------------------------------|-----|-------------------------------|------|-------------------------------|

| TMR0                        | 01h | OPTION                        | 81h | TMR0                          | 101h | OPTION                        |

| PCL                         | 02h | PCL                           | 82h | PCL                           | 102h | PCL                           |

| STATUS                      | 03h | STATUS                        | 83h | STATUS                        | 103h | STATUS                        |

| FSR                         | 04h | FSR                           | 84h | FSR                           | 104h | FSR                           |

| PORTA                       | 05h | TRISA                         | 85h |                               | 105h |                               |

| PORTB                       | 06h | TRISB                         | 86h | PORTB                         | 106h | TRISB                         |

|                             | 07h |                               | 87h |                               | 107h |                               |

|                             | 08h |                               | 88h |                               | 108h |                               |

|                             | 09h |                               | 89h |                               | 109h |                               |

| PCLATH                      | 0Ah | PCLATH                        | 8Ah | PCLATH                        | 10Ah | PCLATH                        |

| INTCON                      | 0Bh | INTCON                        | 8Bh | INTCON                        | 10Bh | INTCON                        |

| PIR1                        | 0Ch | PIE1                          | 8Ch |                               | 10Ch |                               |

|                             | 0Dh |                               | 8Dh |                               | 10Dh |                               |

| TMR1L                       | 0Eh | PCON                          | 8Eh |                               | 10Eh |                               |

| TMR1H                       | 0Fh |                               | 8Fh |                               | 10Fh |                               |

| T1CON                       | 10h |                               | 90h |                               |      |                               |

| TMR2                        | 11h |                               | 91h |                               |      |                               |

| T2CON                       | 12h | PR2                           | 92h |                               |      |                               |

|                             | 13h |                               | 93h |                               |      |                               |

|                             | 14h |                               | 94h |                               |      |                               |

| CCPR1L                      | 15h |                               | 95h |                               |      |                               |

| CCPR1H                      | 16h |                               | 96h |                               |      |                               |

| CCP1CON                     | 17h |                               | 97h |                               |      |                               |

| RCSTA                       | 18h | TXSTA                         | 98h |                               |      |                               |

| TXREG                       | 19h | SPBRG                         | 99h |                               |      |                               |

| RCREG                       | 1Ah | EEDATA                        | 9Ah |                               |      |                               |

|                             | 1Bh | EEADR                         | 9Bh |                               |      |                               |

|                             | 1Ch | EECON1                        | 9Ch |                               |      |                               |

|                             | 1Dh | EECON2 <sup>(1)</sup>         | 9Dh |                               |      |                               |

|                             | 1Eh |                               | 9Eh |                               |      |                               |

| CMCON                       | 1Fh | VRCON                         | 9Fh |                               | 11Fh |                               |

|                             | 20h |                               | A0h | General<br>Purpose            | 120h |                               |

| General                     |     | General                       |     | Register                      |      |                               |

| Purpose<br>Register         |     | Purpose<br>Register           |     | 48 Bytes                      | 14Fh |                               |

| •                           |     | 80 Bytes                      |     |                               | 150h |                               |

| 80 Bytes                    |     |                               |     |                               |      |                               |

|                             | 6Fh |                               | EFh |                               | 16Fh |                               |

| 16 Bytes                    | 70h | accesses                      | F0h | accesses                      | 170h | accesses                      |

| IO Dyles                    |     | 70h-7Fh                       |     | 70h-7Fh                       |      | 70h-7Fh                       |

|                             | 7Fh |                               | FFh |                               | 17Fh |                               |

| Bank 0                      |     | Bank 1                        |     | Bank 2                        |      | Bank 3                        |

| <b>-</b>                    | 4 4 | a memory locations, r         |     | ,                             |      |                               |

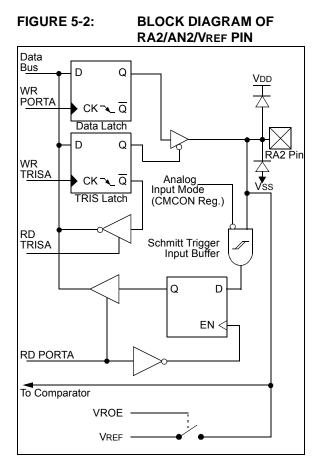

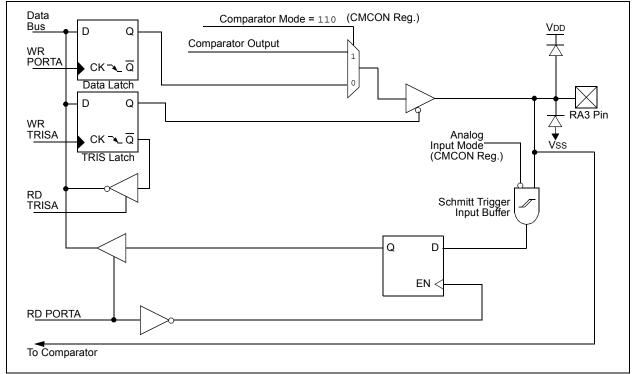

#### FIGURE 5-3: BLOCK DIAGRAM OF THE RA3/AN3/CMP1 PIN

### 5.3 I/O Programming Considerations

#### 5.3.1 BIDIRECTIONAL I/O PORTS

Any instruction that writes operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit 5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit 5 and PORTB is written to the output latches. If another bit of PORTB is used as a bidirectional I/O pin (e.g., bit 0) and is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit 0 is switched into Output mode later on, the content of the data latch may now be unknown.

Reading a port register reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-2 shows the effect of two sequential read-modify-write instructions (ex.,  ${\tt BCF}, {\tt BSF},$  etc.) on an I/O port

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-OR", "wired-AND"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-2: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

| ;Initial PORT settings:     | :PORTB<7:4> Inputs    |

|-----------------------------|-----------------------|

| ;                           | PORTB<3:0> Outputs    |

| ;PORTB<7:6> have extern     | nal pull-up and are   |

| ;not connected to other     | c circuitry           |

| ;                           |                       |

| ;                           | PORT latchPORT Pins   |

|                             |                       |

| BCF STATUS, RPO             | ;                     |

| BCF PORTB, 7                | ;01pp pppp 11pp pppp  |

| BSF STATUS, RPO             | ;                     |

|                             | ;10pp pppp 11pp pppp  |

| BCF TRISB, 6                | ;10pp pppp 10pp pppp  |

| ;                           | , the sets - set fore |

| ,<br>Note that the user may | v have expected the   |

| ; pin values to be 00pp     | -                     |

| ; caused RB7 to be latch    |                       |

| ; (High).                   | ica ab che più value  |

| , (111911).                 |                       |

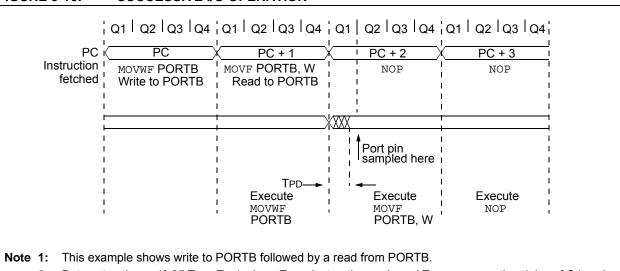

#### 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-16). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction, which causes that file to be read into the CPU, is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

2: Data setup time = (0.25 TCY - TPD) where TCY = instruction cycle and TPD = propagation delay of Q1 cycle to output valid. Therefore, at higher clock frequencies, a write followed by a read may be problematic.

### FIGURE 5-16: SUCCESSIVE I/O OPERATION

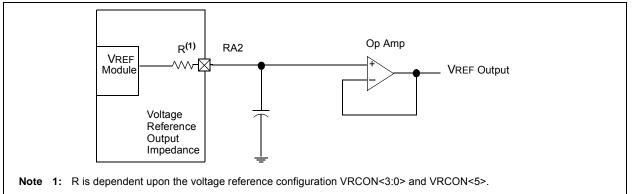

#### FIGURE 11-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 11-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR | Value On<br>All Other<br>Resets |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 9Fh     | VRCON | VREN   | VROE   | VRR    | —      | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 1Fh     | CMCON | C2OUT  | C10UT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 85h     | TRISA | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

**Legend:** - = Unimplemented, read as '0'.

NOTES:

| BAUD     | Fosc = 20 M | /IHz   | SPBRG              | 16 MHz |        | SPBRG              | 10 MHz |        | SPBRG              |

|----------|-------------|--------|--------------------|--------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD       | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 0.3      | NA          |        | _                  | NA     |        | _                  | NA     | _      | _                  |

| 1.2      | 1.221       | +1.73% | 255                | 1.202  | +0.16% | 207                | 1.202  | +0.16% | 129                |

| 2.4      | 2.404       | +0.16% | 129                | 2.404  | +0.16% | 103                | 2.404  | +0.16% | 64                 |

| 9.6      | 9.469       | -1.36% | 32                 | 9.615  | +0.16% | 25                 | 9.766  | +1.73% | 15                 |

| 19.2     | 19.53       | +1.73% | 15                 | 19.23  | +0.16% | 12                 | 19.53  | +1.73V | 7                  |

| 76.8     | 78.13       | +1.73% | 3                  | 83.33  | +8.51% | 2                  | 78.13  | +1.73% | 1                  |

| 96       | 104.2       | +8.51% | 2                  | NA     | _      | _                  | NA     | _      | _                  |

| 300      | 312.5       | +4.17% | 0                  | NA     | _      | _                  | NA     | _      | _                  |

| 500      | NA          | _      | _                  | NA     | _      | _                  | NA     | _      | _                  |

| HIGH     | 312.5       | _      | 0                  | 250    | _      | 0                  | 156.3  | _      | 0                  |

| LOW      | 1.221       |        | 255                | 0.977  |        | 255                | 0.6104 | _      | 255                |

| <b>TABLE 12-4</b> : | BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0) |

|---------------------|---------------------------------------------|

|---------------------|---------------------------------------------|

| BAUD     | Fosc = 7.15 | 909 MHz | SPBRG              | 5.0688 MHz |        | SPBRG              | 4 MHz  |        | SPBRG              |

|----------|-------------|---------|--------------------|------------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD       | ERROR   | value<br>(decimal) | KBAUD      | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 0.3      | NA          | _       | _                  | 0.31       | +3.13% | 255                | 0.3005 | -0.17% | 207                |

| 1.2      | 1.203       | +0.23%  | 92                 | 1.2        | 0      | 65                 | 1.202  | +1.67% | 51                 |

| 2.4      | 2.380       | -0.83%  | 46                 | 2.4        | 0      | 32                 | 2.404  | +1.67% | 25                 |

| 9.6      | 9.322       | -2.90%  | 11                 | 9.9        | +3.13% | 7                  | NA     | _      | _                  |

| 19.2     | 18.64       | -2.90%  | 5                  | 19.8       | +3.13% | 3                  | NA     | _      | _                  |

| 76.8     | NA          | _       | _                  | 79.2       | +3.13% | 0                  | NA     | _      | _                  |

| 96       | NA          | _       | _                  | NA         | _      | _                  | NA     | _      | _                  |

| 300      | NA          | _       | _                  | NA         |        | _                  | NA     | _      | _                  |

| 500      | NA          | _       | _                  | NA         | _      | _                  | NA     | _      | _                  |

| HIGH     | 111.9       | _       | 0                  | 79.2       |        | 0                  | 62.500 | _      | 0                  |

| LOW      | 0.437       | _       | 255                | 0.3094     |        | 255                | 3.906  | _      | 255                |

| BAUD     | Fosc = 3.57 | 9545 MHz | SPBRG              | 1 MHz  |        | SPBRG              | 32.768 kHz |         | SPBRG<br>value |

|----------|-------------|----------|--------------------|--------|--------|--------------------|------------|---------|----------------|

| RATE (K) | KBAUD       | ERROR    | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) | KBAUD      | ERROR   | (decimal)      |

| 0.3      | 0.301       | +0.23%   | 185                | 0.300  | +0.16% | 51                 | 0.256      | -14.67% | 1              |

| 1.2      | 1.190       | -0.83%   | 46                 | 1.202  | +0.16% | 12                 | NA         | _       | _              |

| 2.4      | 2.432       | +1.32%   | 22                 | 2.232  | -6.99% | 6                  | NA         | _       | _              |

| 9.6      | 9.322       | -2.90%   | 5                  | NA     | _      | _                  | NA         | _       | _              |

| 19.2     | 18.64       | -2.90%   | 2                  | NA     | _      | _                  | NA         | _       | _              |

| 76.8     | NA          | _        | _                  | NA     | _      | _                  | NA         | _       | _              |

| 96       | NA          | _        | _                  | NA     |        | _                  | NA         | _       | _              |

| 300      | NA          | _        | _                  | NA     | _      | _                  | NA         | _       | _              |

| 500      | NA          | _        | _                  | NA     |        | _                  | NA         | _       | _              |

| HIGH     | 55.93       | _        | 0                  | 15.63  |        | 0                  | 0.512      | _       | 0              |

| LOW      | 0.2185      | _        | 255                | 0.0610 |        | 255                | 0.0020     | _       | 255            |

#### 12.4.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>) or enable bit CREN (RCSTA<4>). Data is sampled on the RB1/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read-only bit which is reset by the hardware. In this case, it is reset when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a twodeep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full, then overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited, so it is essential to clear bit OERR if it is set. The 9th receive bit is buffered the same way as the receive data. Reading the RCREG register, will load bit RX9D with a new value, therefore it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old RX9D information.

Follow these steps when setting up a Synchronous Master Reception:

- 1. TRISB<1> and TRISB<2> should both be set to '1' to configure the RB1/RX/DT and RB2/TX/CK pins as inputs. Output drive, when required, is controlled by the peripheral circuitry.

- Initialize the SPBRG register for the appropriate baud rate. (Section 12.1 "USART Baud Rate Generator (BRG)").

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, then set enable bit RCIE.

- 6. If 9-bit reception is desired, then set bit RX9.

- 7. If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 9. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an OERR error occurred, clear the error by clearing bit CREN.

| Address | Name  | Bit 7   | Bit 6                       | Bit 5    | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR | Value on all other Resets |

|---------|-------|---------|-----------------------------|----------|--------|-------|--------|--------|--------|------------------|---------------------------|

| 0Ch     | PIR1  | EEIF    | CMIF                        | RCIF     | TXIF   |       | CCP1IF | TMR2IF | TMR1IF | 0000 -000        | 0000 -000                 |

| 18h     | RCSTA | SPEN    | RX9                         | SREN     | CREN   | ADEN  | FERR   | OERR   | RX9D   | 0000 000x        | 0000 000x                 |

| 1Ah     | RCREG | USART F | USART Receive Data Register |          |        |       |        |        |        | 0000 0000        | 0000 0000                 |

| 8Ch     | PIE1  | EPIE    | CMIE                        | RCIE     | TXIE   | -     | CCP1IE | TMR2IE | TMR1IE | -000 0000        | -000 -000                 |

| 98h     | TXSTA | CSRC    | TX9                         | TXEN     | SYNC   | _     | BRGH   | TRMT   | TX9D   | 0000 -010        | 0000 -010                 |

| 99h     | SPBRG | Baud Ra | te Gene                     | rator Re | gister |       |        |        |        | 0000 0000        | 0000 0000                 |

#### TABLE 12-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous master reception.

#### **REGISTER 14-1: CONFIG – CONFIGURATION WORD REGISTER**

| CP          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                                                                                                                          |                                                                             | CPD                                                              | LVP                                                                    | BOREN                                                                   | MCLRE                                                              | FOSC2                                                                             | PWRTE                                                             | WDTE                                | F0SC1                   | F0SC0 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------|-------------------------|-------|

| bit 13      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                            |                                                                             |                                                                  |                                                                        |                                                                         |                                                                    |                                                                                   |                                                                   |                                     |                         | bit 0 |

| bit 13:     | (PIC16F648A<br>1 = Coc<br>0 = 000<br>(PIC16F628A<br>1 = Coc<br>0 = 000<br>(PIC16F627A<br>1 = Coc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | de protection c<br>10h to 0FFFh c<br><u>0</u><br>de protection c<br>10h to 07FFh c                                         | ff<br>ode-protec<br>ff<br>ode-protec<br>ff                                  | sted                                                             | 2)                                                                     |                                                                         |                                                                    |                                                                                   |                                                                   |                                     |                         |       |

| bit 12-9:   | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ted: Read as                                                                                                               | ʻ0'                                                                         |                                                                  |                                                                        |                                                                         |                                                                    |                                                                                   |                                                                   |                                     |                         |       |

| bit 8:      | <b>CPD:</b> Data Code Protection bit <sup>(3)</sup><br>1 = Data memory code protection off<br>0 = Data memory code-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                            |                                                                             |                                                                  |                                                                        |                                                                         |                                                                    |                                                                                   |                                                                   |                                     |                         |       |

| bit 7:      | 1 = RB4/PGM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ltage Program<br>/l pin has PGN<br>/l is digital I/O,                                                                      | function, I                                                                 | <u>ow</u> -voltage                                               |                                                                        |                                                                         |                                                                    |                                                                                   |                                                                   |                                     |                         |       |

| bit 6:      | <b>BOREN</b> : Brow<br>1 = BOR Res<br>0 = BOR Res                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                            | Enable bit (                                                                | 1)                                                               |                                                                        |                                                                         |                                                                    |                                                                                   |                                                                   |                                     |                         |       |

| bit 5:      | 1 = RA5/MCL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5/MCLR/VPP P<br><u>_R/</u> VPP pin fun<br>_R/VPP pin fun                                                                   | ction is MC                                                                 | LR                                                               | ICLR inter                                                             | nally tied to                                                           | Vdd                                                                |                                                                                   |                                                                   |                                     |                         |       |

| bit 3:      | <b>PWRTE</b> : Pow<br>1 = PWRT dis<br>0 = PWRT en                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                            | nable bit <sup>(1</sup>                                                     | )                                                                |                                                                        |                                                                         |                                                                    |                                                                                   |                                                                   |                                     |                         |       |

| bit 2:      | WDTE: Watch<br>1 = WDT ena<br>0 = WDT disa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                            | able bit                                                                    |                                                                  |                                                                        |                                                                         |                                                                    |                                                                                   |                                                                   |                                     |                         |       |

| bit 4, 1-0: | FOSC<2:0>: Oscillator Selection bits <sup>(4)</sup><br>111 = RC oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, Resistor and Capacitor on RA7/OSC1/CLKIN<br>100 = RC oscillator: I/O function on RA6/OSC2/CLKOUT pin, Resistor and Capacitor on RA7/OSC1/CLKIN<br>101 = INTOSC oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN<br>100 = INTOSC oscillator: I/O function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN<br>101 = EC: I/O function on RA6/OSC2/CLKOUT pin, CLKIN on RA7/OSC1/CLKIN<br>100 = HS oscillator: High-speed crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN<br>101 = XT oscillator: Crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN<br>100 = LP oscillator: Low-power crystal on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN |                                                                                                                            |                                                                             |                                                                  |                                                                        |                                                                         |                                                                    |                                                                                   |                                                                   |                                     |                         |       |

|             | Note 1:<br>2:<br>3:<br>4:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Enabling Brov<br>PIC16F627/6<br>The code pro<br>entire Flash p<br>"PIC16F627/<br>The entire da<br>628A/648A E<br>When MCLR | 28 devices<br>tection sch<br>rogram me<br>/628A/648<br>ta EEPROI<br>EPROM M | eme has cl<br>mory need<br>A EEPROM<br>M needs to<br>lemory Prog | hanged fro<br>Is to be bu<br><i>M Memory</i><br>be bulk er<br>gramming | m the code<br>lk erased to<br>Programmin<br>ased to set<br>Specificatio | protection<br>set the CF<br>ng Specific<br>the CPD b<br>n" (DS4119 | scheme us<br>bit, turning<br><i>ation</i> " (DS4<br>it, turning t<br>96) for deta | ed on the F<br>g the code j<br>1196) for d<br>ne code pro<br>ils. | PIC16F627<br>protection<br>letails. | 7/628 devic<br>off. See |       |

|             | Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                            |                                                                             |                                                                  |                                                                        |                                                                         |                                                                    |                                                                                   |                                                                   |                                     |                         |       |

|             | R = Readable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | e bit                                                                                                                      | W = Wri                                                                     | table bit                                                        |                                                                        | U = Ur                                                                  | nimplement                                                         | ted bit, read                                                                     | d as '0'                                                          |                                     |                         |       |

|             | -n = Value at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | POR                                                                                                                        | '1' = bit                                                                   | is set                                                           |                                                                        | '0' = bi                                                                | it is cleared                                                      | l                                                                                 | x =                                                               | bit is unkn                         | own                     |       |

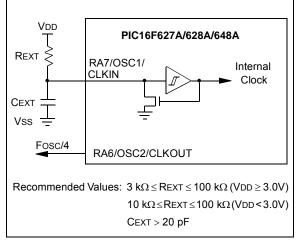

#### 14.2.6 RC OSCILLATOR

For applications where precise timing is not a requirement, the RC oscillator option is available. The operation and functionality of the RC oscillator is dependent upon a number of variables. The RC oscillator frequency is a function of:

- Supply voltage

- Resistor (REXT) and capacitor (CEXT) values

- Operating temperature

The oscillator frequency will vary from unit-to-unit due to normal process parameter variation. The difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to account for the tolerance of the external R and C components. Figure 14-5 shows how the R/C combination is connected.

#### FIGURE 14-5: RC OSCILLATOR MODE

The RC Oscillator mode has two options that control the unused OSC2 pin. The first allows it to be used as a general purpose I/O port. The other configures the pin as an output providing the Fosc signal (internal clock divided by 4) for test or external synchronization purposes.

#### 14.2.7 CLKOUT

The PIC16F627A/628A/648A can be configured to provide a clock out signal by programming the Configuration Word. The oscillator frequency, divided by 4 can be used for test purposes or to synchronize other logic.

### 14.2.8 SPECIAL FEATURE: DUAL-SPEED OSCILLATOR MODES

A software programmable dual-speed oscillator mode is provided when the PIC16F627A/628A/648A is configured in the INTOSC oscillator mode. This feature allows users to dynamically toggle the oscillator speed between 4 MHz and 48 kHz nominal in the INTOSC mode. Applications that require low-current power savings, but cannot tolerate putting the part into Sleep, may use this mode.

There is a time delay associated with the transition between fast and slow oscillator speeds. This oscillator speed transition delay consists of two existing clock pulses and eight new speed clock pulses. During this clock speed transition delay, the System Clock is halted causing the processor to be frozen in time. During this delay, the program counter and the CLKOUT stop.

The OSCF bit in the PCON register is used to control Dual Speed mode. See **Section 4.2.2.6** "**PCON Register**", Register 4-6.

### 14.3 Reset

The PIC16F627A/628A/648A differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during Sleep

- d) WDT Reset (normal operation)

- e) WDT wake-up (Sleep)

- f) Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on Power-on Reset, Brown-out Reset, MCLR Reset, WDT Reset and MCLR Reset during Sleep. They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different Reset situations as indicated in Table 14-4. These bits are used in software to determine the nature of the Reset. See Table 14-7 for a full description of Reset states of all registers.

A simplified block diagram of the on-chip Reset circuit is shown in Figure 14-6.

The  $\overline{\text{MCLR}}$  Reset path has a noise filter to detect and ignore small pulses. See Table 17-7 for pulse width specification.

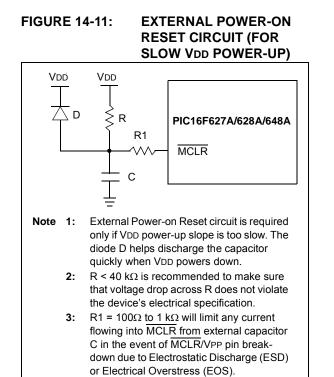

#### 14.4.5 TIME OUT SEQUENCE

On power-up, the time out sequence is as follows: First PWRT time-out is invoked after POR has expired. Then OST is activated. The total time out will vary based on oscillator configuration and <u>PWRTE</u> bit Status. For example, in RC mode with <u>PWRTE</u> bit set (PWRT disabled), there will be no time out at all. Figure 14-8, Figure 14-11 and Figure 14-12 depict time out sequences.

Since the time outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 14-11). This is useful for testing purposes or to synchronize more than one PIC16F627A/628A/ 648A device operating in parallel.

Table 14-6 shows the Reset conditions for some special registers, while Table 14-7 shows the Reset conditions for all the registers.

#### 14.4.6 POWER CONTROL (PCON) STATUS REGISTER

The PCON/Status register, PCON (address 8Eh), has two bits.

Bit 0 is  $\overline{\text{BOR}}$  (Brown-out Reset).  $\overline{\text{BOR}}$  is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if  $\overline{\text{BOR}} = 0$ indicating that a brown-out has occurred. The  $\overline{\text{BOR}}$ Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (by setting BOREN bit = 0 in the Configuration Word).

Bit 1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent Reset if POR is '0', it will indicate that a Power-on Reset must have occurred (VDD may have gone too low).

| Oscillator Configuration | Power-u              | ıp Timer         | Brown-o              | ut Reset         | Wake-up from |

|--------------------------|----------------------|------------------|----------------------|------------------|--------------|

| Oscillator Configuration | <b>PWRTE</b> = 0     | <b>PWRTE</b> = 1 | <b>PWRTE</b> = 0     | <b>PWRTE</b> = 1 | Sleep        |

| XT, HS, LP               | 72 ms +<br>1024•Tosc | 1024•Tosc        | 72 ms +<br>1024•Tosc | 1024•Tosc        | 1024•Tosc    |

| RC, EC                   | 72 ms                | —                | 72 ms                | _                | —            |

| INTOSC                   | 72 ms                | —                | 72 ms                | —                | 6 μs         |

| TABLE 14-3. THE OUT IN VARIOUS SITUATIONS | TABLE 14-3: | TIME OUT IN VARIOUS SITUATIONS |

|-------------------------------------------|-------------|--------------------------------|

|-------------------------------------------|-------------|--------------------------------|

### TABLE 14-4: STATUS/PCON BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD | Condition                          |  |  |  |

|-----|-----|----|----|------------------------------------|--|--|--|

| 0   | Х   | 1  | 1  | Power-on Reset                     |  |  |  |

| 0   | Х   | 0  | Х  | Illegal, TO is set on POR          |  |  |  |

| 0   | Х   | Х  | 0  | Illegal, PD is set on POR          |  |  |  |

| 1   | 0   | Х  | Х  | Brown-out Reset                    |  |  |  |

| 1   | 1   | 0  | u  | WDT Reset                          |  |  |  |

| 1   | 1   | 0  | 0  | WDT Wake-up                        |  |  |  |

| 1   | 1   | u  | u  | MCLR Reset during normal operation |  |  |  |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep            |  |  |  |

**Legend:** u = unchanged, x = unknown

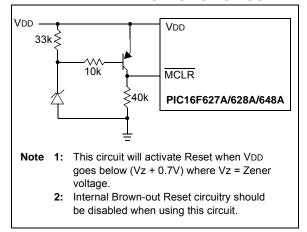

FIGURE 14-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

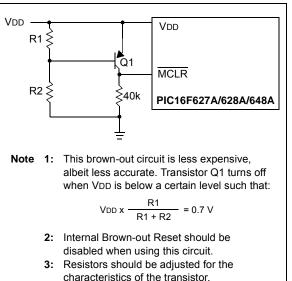

#### FIGURE 14-13: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

| SUBWF               | Subtract W from f                                                                                                                                                                           |  |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:             | [label] SUBWF f,d                                                                                                                                                                           |  |  |  |  |  |

| Operands:           | $0 \leq f \leq 127$                                                                                                                                                                         |  |  |  |  |  |

| <b>0</b> <i>1</i>   | d ∈ [0,1]                                                                                                                                                                                   |  |  |  |  |  |

| Operation:          | $(f) - (W) \rightarrow (dest)$                                                                                                                                                              |  |  |  |  |  |

| Status<br>Affected: | C, DC, Z                                                                                                                                                                                    |  |  |  |  |  |

| Encoding:           | 00 0010 dfff ffff                                                                                                                                                                           |  |  |  |  |  |

| Description:        | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is<br>'0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |  |

| Words:              | 1                                                                                                                                                                                           |  |  |  |  |  |

| Cycles:             | 1                                                                                                                                                                                           |  |  |  |  |  |

| Example 1:          | SUBWF REG1, 1                                                                                                                                                                               |  |  |  |  |  |

|                     | Before Instruction                                                                                                                                                                          |  |  |  |  |  |

|                     | REG1 = 3<br>W = 2<br>C = ?                                                                                                                                                                  |  |  |  |  |  |

|                     | After Instruction                                                                                                                                                                           |  |  |  |  |  |

|                     | REG1 = 1<br>W = 2<br>C = 1; result is positive<br>DC = 1<br>Z = 0                                                                                                                           |  |  |  |  |  |

| Example 2:          | Before Instruction                                                                                                                                                                          |  |  |  |  |  |

|                     | REG1 = 2<br>W = 2                                                                                                                                                                           |  |  |  |  |  |

|                     | C = ?                                                                                                                                                                                       |  |  |  |  |  |

|                     | After Instruction<br>REG1 = 0<br>W = 2<br>C = 1; result is zero<br>Z = DC = 1                                                                                                               |  |  |  |  |  |

| Example 3:          | Before Instruction                                                                                                                                                                          |  |  |  |  |  |

|                     | REG1 = 1<br>W = 2<br>C = ?                                                                                                                                                                  |  |  |  |  |  |

|                     | After Instruction                                                                                                                                                                           |  |  |  |  |  |

|                     | REG1 = 0xFF $W = 2$ $C = 0; result is negative$ $Z = DC = 0$                                                                                                                                |  |  |  |  |  |

| Swap Nibbles in f                                                                                                                                                                  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| [label] SWAPF f,d                                                                                                                                                                  |  |  |  |  |  |  |

| $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                 |  |  |  |  |  |  |

| (f<3:0>) → (dest<7:4>),<br>(f<7:4>) → (dest<3:0>)                                                                                                                                  |  |  |  |  |  |  |

| None                                                                                                                                                                               |  |  |  |  |  |  |

| 00 1110 dfff ffff                                                                                                                                                                  |  |  |  |  |  |  |

| The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is<br>'0', the result is placed in W<br>register. If 'd' is '1', the result is<br>placed in register 'f'.     |  |  |  |  |  |  |

| 1                                                                                                                                                                                  |  |  |  |  |  |  |

| 1                                                                                                                                                                                  |  |  |  |  |  |  |

| SWAPF REG1, 0                                                                                                                                                                      |  |  |  |  |  |  |

| Before Instruction                                                                                                                                                                 |  |  |  |  |  |  |

| REG1 = 0xA5                                                                                                                                                                        |  |  |  |  |  |  |

| After Instruction                                                                                                                                                                  |  |  |  |  |  |  |

| REG1 = 0xA5<br>W = 0x5A                                                                                                                                                            |  |  |  |  |  |  |

| Load TRIS Register                                                                                                                                                                 |  |  |  |  |  |  |

| [ <i>label</i> ] TRIS f                                                                                                                                                            |  |  |  |  |  |  |

| $5 \le f \le 7$                                                                                                                                                                    |  |  |  |  |  |  |

| $(W) \rightarrow TRIS$ register f;                                                                                                                                                 |  |  |  |  |  |  |

| None                                                                                                                                                                               |  |  |  |  |  |  |

| 00 0000 0110 0fff                                                                                                                                                                  |  |  |  |  |  |  |

| The instruction is supported for<br>code compatibility with the<br>PIC16C5X products. Since TRIS<br>registers are readable and<br>writable, the user can directly<br>address them. |  |  |  |  |  |  |

| 1                                                                                                                                                                                  |  |  |  |  |  |  |

| 1                                                                                                                                                                                  |  |  |  |  |  |  |

|                                                                                                                                                                                    |  |  |  |  |  |  |

| To maintain upward compatibil-<br>ity with future PIC <sup>®</sup> MCU<br>products, do not use this<br>instruction.                                                                |  |  |  |  |  |  |

|                                                                                                                                                                                    |  |  |  |  |  |  |

| XORLW                       | Exclusive OR Literal with W                                                                                                |     |           |         | XORWF                               |  |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------|-----|-----------|---------|-------------------------------------|--|

| Syntax:                     | [ <i>label</i> ] XORLW k                                                                                                   |     |           | Syntax: |                                     |  |

| Operands:                   | $0 \le k \le 255$                                                                                                          | 5   | Operands: |         |                                     |  |

| Operation:                  | (W) .XOR. $k \rightarrow$ (W)<br>Z                                                                                         |     |           |         |                                     |  |

| Status Affected:            |                                                                                                                            |     |           |         | Operation:                          |  |

| Encoding:                   | 11 1                                                                                                                       | 010 | kkkk      | kkkk    | Status Affected:                    |  |

| Description:                | The contents of the W register<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed in<br>the W register. |     |           |         | Encoding:<br>Description:           |  |

| Words:                      | 1                                                                                                                          |     |           |         |                                     |  |

| Cycles:<br><u>Example</u> : | 1<br>XORLW $0 \times AF$<br>Before Instruction<br>$W = 0 \times B5$<br>After Instruction<br>$W = 0 \times 1A$              |     |           |         | Words:<br>Cycles:<br><u>Example</u> |  |

| ORWF                                                                                                                                                                                                    | Exclusive OR W with f              |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|--|--|--|

| vntax:                                                                                                                                                                                                  | [ label ] XORWF f,d                |  |  |  |  |  |  |

| ,                                                                                                                                                                                                       |                                    |  |  |  |  |  |  |

| perands:                                                                                                                                                                                                | 0 ≤ f ≤ 127<br>d ∈ [0,1]           |  |  |  |  |  |  |

| peration:                                                                                                                                                                                               | (W) .XOR. (f) $\rightarrow$ (dest) |  |  |  |  |  |  |

| atus Affected:                                                                                                                                                                                          | Z                                  |  |  |  |  |  |  |

| ncoding:                                                                                                                                                                                                | 00 0110 dfff ffff                  |  |  |  |  |  |  |

| escription: Exclusive OR the contents of the<br>W register with register 'f'. If 'd' is<br>'0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |                                    |  |  |  |  |  |  |

| /ords:                                                                                                                                                                                                  | 1                                  |  |  |  |  |  |  |

| ycles:                                                                                                                                                                                                  | 1                                  |  |  |  |  |  |  |

| <u>xample</u>                                                                                                                                                                                           | XORWF REG1, 1                      |  |  |  |  |  |  |

|                                                                                                                                                                                                         | Before Instruction                 |  |  |  |  |  |  |

|                                                                                                                                                                                                         | REG1 = 0xAF<br>W = 0xB5            |  |  |  |  |  |  |

|                                                                                                                                                                                                         | After Instruction                  |  |  |  |  |  |  |

|                                                                                                                                                                                                         | REG1 = 0x1A $W = 0xB5$             |  |  |  |  |  |  |

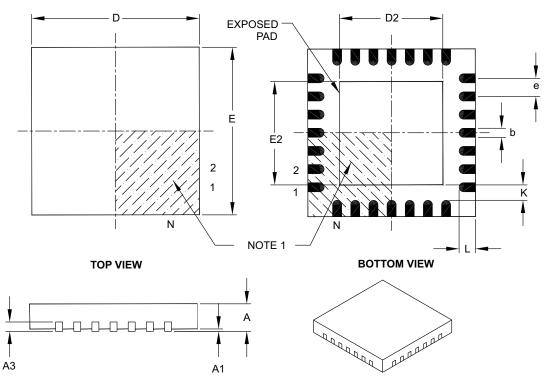

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS      |          |      |      |

|------------------------|------------------|----------|------|------|

| Dimensio               | Dimension Limits |          | NOM  | MAX  |

| Number of Pins         | Ν                | 28       |      |      |

| Pitch                  | е                | 0.65 BSC |      |      |

| Overall Height         | А                | 0.80     | 0.90 | 1.00 |

| Standoff               | A1               | 0.00     | 0.02 | 0.05 |

| Contact Thickness      | A3               | 0.20 REF |      |      |

| Overall Width          | E                | 6.00 BSC |      |      |

| Exposed Pad Width      | E2               | 3.65     | 3.70 | 4.20 |

| Overall Length         | D                | 6.00 BSC |      |      |

| Exposed Pad Length     | D2               | 3.65     | 3.70 | 4.20 |

| Contact Width          | b                | 0.23     | 0.30 | 0.35 |

| Contact Length         |                  | 0.50     | 0.55 | 0.70 |

| Contact-to-Exposed Pad | К                | 0.20     | _    | _    |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B