Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf648a-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                  | Function | Input Type | Output Type | Description                                                                                                                                                          |

|-------------------------------------------------------|----------|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RA0/AN0                                               | RA0      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                               |

|                                                       | AN0      | AN         | —           | Analog comparator input                                                                                                                                              |

| RA1/AN1                                               | RA1      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                               |

|                                                       | AN1      | AN         | _           | Analog comparator input                                                                                                                                              |

| RA2/AN2/VREF                                          | RA2      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                               |

|                                                       | AN2      | AN         |             | Analog comparator input                                                                                                                                              |

|                                                       | VREF     | —          | AN          | VREF output                                                                                                                                                          |

| RA3/AN3/CMP1                                          | RA3      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                               |

|                                                       | AN3      | AN         |             | Analog comparator input                                                                                                                                              |

|                                                       | CMP1     | —          | CMOS        | Comparator 1 output                                                                                                                                                  |

| RA4/T0CKI/CMP2                                        | RA4      | ST         | OD          | Bidirectional I/O port                                                                                                                                               |

|                                                       | TOCKI    | ST         | _           | Timer0 clock input                                                                                                                                                   |

|                                                       | CMP2     | _          | OD          | Comparator 2 output                                                                                                                                                  |

| RA5/MCLR/VPP                                          | RA5      | ST         | _           | Input port                                                                                                                                                           |

|                                                       | MCLR     | ST         | _           | Master clear. When configured as MCLR, th<br>pin is an active low Reset to the device.<br>Voltage on MCLR/VPP must not exceed VDr<br>during normal device operation. |

|                                                       | VPP      | —          | —           | Programming voltage input                                                                                                                                            |

| RA6/OSC2/CLKOUT                                       | RA6      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                               |

|                                                       | OSC2     | —          | XTAL        | Oscillator crystal output. Connects to crystal<br>or resonator in Crystal Oscillator mode.                                                                           |

|                                                       | CLKOUT   |            | CMOS        | In RC/INTOSC mode, OSC2 pin can output<br>CLKOUT, which has 1/4 the frequency of<br>OSC1.                                                                            |

| RA7/OSC1/CLKIN                                        | RA7      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                               |

|                                                       | OSC1     | XTAL       | —           | Oscillator crystal input                                                                                                                                             |

|                                                       | CLKIN    | ST         | —           | External clock source input. RC biasing pin.                                                                                                                         |

| RB0/INT                                               | RB0      | TTL        | CMOS        | Bidirectional I/O port. Can be software<br>programmed for internal weak pull-up.                                                                                     |

|                                                       | INT      | ST         | —           | External interrupt                                                                                                                                                   |

| RB1/RX/DT                                             | RB1      | TTL        | CMOS        | Bidirectional I/O port. Can be software programmed for internal weak pull-up.                                                                                        |

|                                                       | RX       | ST         | —           | USART receive pin                                                                                                                                                    |

|                                                       | DT       | ST         | CMOS        | Synchronous data I/O                                                                                                                                                 |

| RB2/TX/CK                                             | RB2      | TTL        | CMOS        | Bidirectional I/O port. Can be software programmed for internal weak pull-up.                                                                                        |

|                                                       | ТХ       |            | CMOS        | USART transmit pin                                                                                                                                                   |

|                                                       | CK       | ST         | CMOS        | Synchronous clock I/O                                                                                                                                                |

| RB3/CCP1                                              | RB3      | TTL        | CMOS        | Bidirectional I/O port. Can be software programmed for internal weak pull-up.                                                                                        |

|                                                       | CCP1     | ST         | CMOS        | Capture/Compare/PWM I/O                                                                                                                                              |

| Legend: O = Output<br>— = Not used<br>TTL = TTL Input |          | I = Ir     | MOS Output  | P = Power<br>ST = Schmitt Trigger Input<br>AN = Analog                                                                                                               |

#### TABLE 3-2: PIC16F627A/628A/648A PINOUT DESCRIPTION

NOTES:

#### FIGURE 4-2: DATA MEMORY MAP OF THE PIC16F627A AND PIC16F628A

| direct addr.(1)     | 00h | Indirect addr. <sup>(1)</sup> | 80h | Indirect addr. <sup>(1)</sup> | 100h | Indirect addr. <sup>(1)</sup> |

|---------------------|-----|-------------------------------|-----|-------------------------------|------|-------------------------------|

| TMR0                | 01h | OPTION                        | 81h | TMR0                          | 101h | OPTION                        |

| PCL                 | 02h | PCL                           | 82h | PCL                           | 102h | PCL                           |

| STATUS              | 03h | STATUS                        | 83h | STATUS                        | 103h | STATUS                        |

| FSR                 | 04h | FSR                           | 84h | FSR                           | 104h | FSR                           |

| PORTA               | 05h | TRISA                         | 85h |                               | 105h |                               |

| PORTB               | 06h | TRISB                         | 86h | PORTB                         | 106h | TRISB                         |

|                     | 07h |                               | 87h |                               | 107h |                               |

|                     | 08h |                               | 88h |                               | 108h |                               |

|                     | 09h |                               | 89h |                               | 109h |                               |

| PCLATH              | 0Ah | PCLATH                        | 8Ah | PCLATH                        | 10Ah | PCLATH                        |

| INTCON              | 0Bh | INTCON                        | 8Bh | INTCON                        | 10Bh | INTCON                        |

| PIR1                | 0Ch | PIE1                          | 8Ch |                               | 10Ch |                               |

|                     | 0Dh |                               | 8Dh |                               | 10Dh |                               |

| TMR1L               | 0Eh | PCON                          | 8Eh |                               | 10Eh |                               |

| TMR1H               | 0Fh |                               | 8Fh |                               | 10Fh |                               |

| T1CON               | 10h |                               | 90h |                               |      |                               |

| TMR2                | 11h |                               | 91h |                               |      |                               |

| T2CON               | 12h | PR2                           | 92h |                               |      |                               |

|                     | 13h |                               | 93h |                               |      |                               |

|                     | 14h |                               | 94h |                               |      |                               |

| CCPR1L              | 15h |                               | 95h |                               |      |                               |

| CCPR1H              | 16h |                               | 96h |                               |      |                               |

| CCP1CON             | 17h |                               | 97h |                               |      |                               |

| RCSTA               | 18h | TXSTA                         | 98h |                               |      |                               |

| TXREG               | 19h | SPBRG                         | 99h |                               |      |                               |

| RCREG               | 1Ah | EEDATA                        | 9Ah |                               |      |                               |

|                     | 1Bh | EEADR                         | 9Bh |                               |      |                               |

|                     | 1Ch | EECON1                        | 9Ch |                               |      |                               |

|                     | 1Dh | EECON2 <sup>(1)</sup>         | 9Dh |                               |      |                               |

|                     | 1Eh |                               | 9Eh |                               |      |                               |

| CMCON               | 1Fh | VRCON                         | 9Fh |                               | 11Fh |                               |

|                     | 20h |                               | A0h | General<br>Purpose            | 120h |                               |

| General             |     | General                       |     | Register                      |      |                               |

| Purpose<br>Register |     | Purpose<br>Register           |     | 48 Bytes                      | 14Fh |                               |

| •                   |     | 80 Bytes                      |     |                               | 150h |                               |

| 80 Bytes            |     |                               |     |                               |      |                               |

|                     | 6Fh |                               | EFh |                               | 16Fh |                               |

| 16 Bytes            | 70h | accesses                      | F0h | accesses                      | 170h | accesses                      |

| IO Dyles            |     | 70h-7Fh                       |     | 70h-7Fh                       |      | 70h-7Fh                       |

|                     | 7Fh |                               | FFh |                               | 17Fh |                               |

| Bank 0              |     | Bank 1                        |     | Bank 2                        |      | Bank 3                        |

| <b>-</b>            | 4 4 | a memory locations, r         |     | ,                             |      |                               |

| Address | Name   | Bit 7       | Bit 6           | Bit 5       | Bit 4        | Bit 3        | Bit 2         | Bit 1        | Bit 0         | Value on<br>POR<br>Reset <sup>(1)</sup> | Details<br>on Page |

|---------|--------|-------------|-----------------|-------------|--------------|--------------|---------------|--------------|---------------|-----------------------------------------|--------------------|

| Bank 2  |        |             |                 |             |              |              |               |              |               |                                         |                    |

| 100h    | INDF   | Addressing  | g this location | uses conter | nts of FSR t | o address d  | ata memory    | (not a physi | cal register) | xxxx xxxx                               | 30                 |

| 101h    | TMR0   | Timer0 Mo   | dule's Registe  | er          |              |              |               |              |               | xxxx xxxx                               | 47                 |

| 102h    | PCL    | Program C   | Counter's (PC)  | Least Sign  | ificant Byte |              |               |              |               | 0000 0000                               | 30                 |

| 103h    | STATUS | IRP         | RP1             | RP0         | TO           | PD           | Z             | DC           | С             | 0001 1xxx                               | 24                 |

| 104h    | FSR    | Indirect Da | ata Memory A    | ddress Poin | ter          |              |               |              |               | xxxx xxxx                               | 30                 |

| 105h    | _      | Unimpleme   | ented           |             |              |              |               |              |               | —                                       | -                  |

| 106h    | PORTB  | RB7         | RB6             | RB5         | RB4          | RB3          | RB2           | RB1          | RB0           | xxxx xxxx                               | 38                 |

| 107h    | _      | Unimpleme   | ented           | •           | •            | •            |               | •            |               | _                                       | _                  |

| 108h    | _      | Unimpleme   | ented           |             |              |              |               |              |               | _                                       | _                  |

| 109h    | _      | Unimpleme   | ented           |             |              |              |               |              |               | _                                       | —                  |

| 10Ah    | PCLATH | _           | _               | _           | Write        | Buffer for u | pper 5 bits o | f Program C  | Counter       | 0 0000                                  | 30                 |

| 10Bh    | INTCON | GIE         | PEIE            | T0IE        | INTE         | RBIE         | TOIF          | INTF         | RBIF          | 0000 000x                               | 26                 |

| 10Ch    | —      | Unimpleme   | ented           |             |              |              |               |              |               | —                                       |                    |

| 10Dh    | —      | Unimpleme   | ented           |             |              |              |               |              |               | —                                       | _                  |

| 10Eh    | _      | Unimpleme   | ented           |             |              |              |               |              |               | _                                       |                    |

| 10Fh    | _      | Unimpleme   | ented           |             |              |              |               |              |               | _                                       |                    |

| 110h    |        | Unimpleme   | ented           |             |              |              |               |              |               | _                                       |                    |

| 111h    |        | Unimpleme   | ented           |             |              |              |               |              |               | —                                       | —                  |

| 112h    |        | Unimpleme   | ented           |             |              |              |               |              |               | —                                       | —                  |

| 113h    |        | Unimpleme   | ented           |             |              |              |               |              |               | —                                       | —                  |

| 114h    | —      | Unimpleme   | ented           |             |              |              |               |              |               | —                                       | _                  |

| 115h    | —      | Unimpleme   | ented           |             |              |              |               |              |               | _                                       | _                  |

| 116h    | —      | Unimpleme   | ented           |             |              |              |               |              |               | _                                       | —                  |

| 117h    | _      | Unimpleme   | ented           |             |              |              |               |              |               | _                                       |                    |

| 118h    | _      | Unimpleme   | ented           |             |              |              |               |              |               | _                                       |                    |

| 119h    |        | Unimpleme   |                 |             |              |              |               |              |               | _                                       |                    |

| 11Ah    |        | Unimpleme   |                 |             |              |              |               |              |               | —                                       | —                  |

| 11Bh    | _      | Unimpleme   |                 |             |              |              |               |              |               | —                                       | —                  |

| 11Ch    | -      | Unimpleme   |                 |             |              |              |               |              |               | —                                       | —                  |

| 11Dh    | -      | Unimpleme   |                 |             |              |              |               |              |               | —                                       | —                  |

| 11Eh    | _      | Unimpleme   |                 |             |              |              |               |              |               | —                                       | —                  |

| 11Fh    | —      | Unimpleme   | ented           |             |              |              |               |              |               | —                                       | —                  |

#### TABLE 4-5: SPECIAL FUNCTION REGISTERS SUMMARY BANK2

Legend:- = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented.Note1:For the initialization condition for registers tables, refer to Table 14-6 and Table 14-7.

#### 4.2.2.2 OPTION Register

The Option register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT (PSA = 1). See Section 6.3.1 "Switching Prescaler Assignment".

#### **REGISTER 4-2:** OPTION\_REG – OPTION REGISTER (ADDRESS: 81h, 181h)

|         |                        |                                  |               |                  |                              | , , , , , , , , , , , , , , , , , , , , |       |       |  |  |  |

|---------|------------------------|----------------------------------|---------------|------------------|------------------------------|-----------------------------------------|-------|-------|--|--|--|

|         | R/W-1                  | R/W-1                            | R/W-1         | R/W-1            | R/W-1                        | R/W-1                                   | R/W-1 | R/W-1 |  |  |  |

|         | RBPU                   | INTEDG                           | TOCS          | T0SE             | PSA                          | PS2                                     | PS1   | PS0   |  |  |  |

|         | bit 7                  |                                  |               |                  |                              |                                         |       | bit 0 |  |  |  |

| bit 7   | <b>RBPU</b> : PC       | )RTB Pull-up                     | Enable bit    |                  |                              |                                         |       |       |  |  |  |

|         |                        | B pull-ups ar<br>B pull-ups ar   |               | by individual    | port latch valu              | es                                      |       |       |  |  |  |

| bit 6   | INTEDG:                | Interrupt Edg                    | e Select bit  | t                |                              |                                         |       |       |  |  |  |

|         |                        | pt on rising e<br>pt on falling  | 0             |                  |                              |                                         |       |       |  |  |  |

| bit 5   | <b>T0CS</b> : TM       | R0 Clock So                      | urce Selec    | t bit            |                              |                                         |       |       |  |  |  |

|         |                        | tion on RA4/<br>al instruction   |               | •                |                              |                                         |       |       |  |  |  |

| bit 4   | TOSE: TM               | R0 Source E                      | dge Select    | bit              |                              |                                         |       |       |  |  |  |

|         |                        | •                                |               |                  | 4/T0CKI/CMP2<br>4/T0CKI/CMP2 | •                                       |       |       |  |  |  |

| bit 3   | PSA: Pres              | PSA: Prescaler Assignment bit    |               |                  |                              |                                         |       |       |  |  |  |

|         |                        | aler is assign<br>aler is assign |               |                  | le                           |                                         |       |       |  |  |  |

| bit 2-0 | <b>PS&lt;2:0&gt;</b> : | Prescaler Ra                     | ate Select b  | its              |                              |                                         |       |       |  |  |  |

|         |                        | Bit Value T                      | MR0 Rate      | WDT Rate         |                              |                                         |       |       |  |  |  |

|         | -                      | 000                              | 1:2           | 1:1              |                              |                                         |       |       |  |  |  |

|         |                        | 001<br>010                       | 1:4<br>1:8    | 1:2<br>1:4       |                              |                                         |       |       |  |  |  |

|         |                        | 010                              | 1:16          | 1:8              |                              |                                         |       |       |  |  |  |

|         |                        | 100                              | 1:32          | 1:16             |                              |                                         |       |       |  |  |  |

|         |                        | 101                              | 1:64<br>1:128 | 1 : 32<br>1 : 64 |                              |                                         |       |       |  |  |  |

|         |                        | 110                              | 1.120         | 1 04             |                              |                                         |       |       |  |  |  |

110

1:128

1:64

111

1:256

1:128

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 4.2.2.6 PCON Register

The PCON register contains flag bits to differentiate between a Power-on Reset, an external MCLR Reset, WDT Reset or a Brown-out Reset.

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if BOR is cleared, indicating a brown-out has occurred. The BOR Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BOREN bit in the Configuration Word).

#### REGISTER 4-6:

#### PCON – POWER CONTROL REGISTER (ADDRESS: 8Eh)

| U-0   | U-0 | U-0 | U-0 | R/W-1 | U-0 | R/W-0 | R/W-x |

|-------|-----|-----|-----|-------|-----|-------|-------|

| _     | —   | _   | _   | OSCF  |     | POR   | BOR   |

| bit 7 |     |     |     |       |     |       | bit 0 |

- bit 7-4 Unimplemented: Read as '0'

- bit 3 OSCF: INTOSC Oscillator Frequency bit

- 1 = 4 MHz typical

- 0 = 48 kHz typical

- bit 2 Unimplemented: Read as '0'

- bit 1 **POR**: Power-on Reset Status bit

- 1 = No Power-on Reset occurred

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

- bit 0 BOR: Brown-out Reset Status bit

- 1 = No Brown-out Reset occurred

- 0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

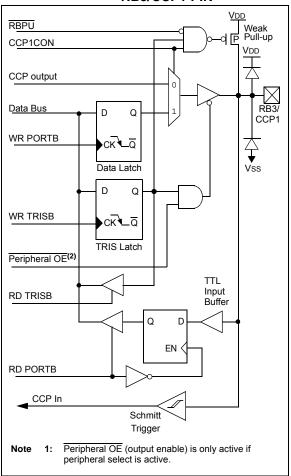

#### FIGURE 5-11: BLOCK DIAGRAM OF RB3/CCP1 PIN

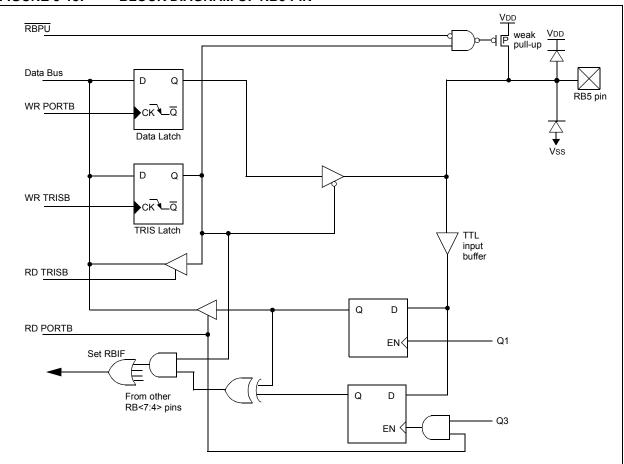

#### FIGURE 5-13: BLOCK DIAGRAM OF RB5 PIN

| REGISTER 8-1: | T2CO                     | N – TIMER2                                       | CONTRO      | L REGISTE      | R (ADDRES  | S: 12h)     |                |         |  |  |  |  |

|---------------|--------------------------|--------------------------------------------------|-------------|----------------|------------|-------------|----------------|---------|--|--|--|--|

|               | U-0                      | R/W-0                                            | R/W-0       | R/W-0          | R/W-0      | R/W-0       | R/W-0          | R/W-0   |  |  |  |  |

|               | —                        | TOUTPS3                                          | TOUTPS2     | TOUTPS1        | TOUTPS0    | TMR2ON      | T2CKPS1        | T2CKPS0 |  |  |  |  |

|               | bit 7                    |                                                  |             |                |            |             |                | bit 0   |  |  |  |  |

| bit 7         | Unimplem                 | ented: Read                                      | as '0'      |                |            |             |                |         |  |  |  |  |

| bit 6-3       | -                        | routps<3:0>: Timer2 Output Postscale Select bits |             |                |            |             |                |         |  |  |  |  |

|               |                          | Postscale V                                      |             |                |            |             |                |         |  |  |  |  |

|               | 0001 = 1:2               | 0001 = 1:2 Postscale Value                       |             |                |            |             |                |         |  |  |  |  |

|               | •                        |                                                  |             |                |            |             |                |         |  |  |  |  |

|               | •                        |                                                  |             |                |            |             |                |         |  |  |  |  |

|               | 1111 <b>= 1</b> :1       | 6 Postscale                                      |             |                |            |             |                |         |  |  |  |  |

| bit 2         | TMR2ON:                  | Timer2 On bi                                     | it          |                |            |             |                |         |  |  |  |  |

|               | 1 = Timer2<br>0 = Timer2 |                                                  |             |                |            |             |                |         |  |  |  |  |

| bit 1-0       |                          | 1:0>: Timer2                                     | Clock Presc | ale Select bit | s          |             |                |         |  |  |  |  |

|               |                          | rescaler Valu                                    |             |                | -          |             |                |         |  |  |  |  |

|               | 01 <b>= 1:4 P</b>        | rescaler Valu                                    | е           |                |            |             |                |         |  |  |  |  |

|               | 1x = 1:16                | Prescaler Val                                    | ue          |                |            |             |                |         |  |  |  |  |

|               | Legend:                  |                                                  |             |                |            |             |                |         |  |  |  |  |

|               | R = Reada                | able bit                                         | W = W       | /ritable bit   | U = Unimpl | emented bit | t, read as '0' |         |  |  |  |  |

#### TABLE 8-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

-n = Value at POR

| Address                 | Name   | Bit 7       | Bit 6                | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR | Value on<br>all other<br>Resets |

|-------------------------|--------|-------------|----------------------|---------|---------|---------|--------|---------|---------|-----------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE         | PEIE                 | TOIE    | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x       | 0000 000u                       |

| 0Ch                     | PIR1   | EEIF        | CMIF                 | RCIF    | TXIF    | 1       | CCP1IF | TMR2IF  | TMR1IF  | 0000 -000       | 0000 -000                       |

| 8Ch                     | PIE1   | EEIE        | CMIE                 | RCIE    | TXIE    | _       | CCP1IE | TMR2IE  | TMR1IE  | 0000 -000       | 0000 -000                       |

| 11h                     | TMR2   | Timer2 Mod  | lule's Registe       | er      |         |         |        |         |         | 0000 0000       | 0000 0000                       |

| 12h                     | T2CON  | _           | TOUTPS3              | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000       | -000 0000                       |

| 92h                     | PR2    | Timer2 Peri | mer2 Period Register |         |         |         |        |         |         | 1111 1111       | 1111 1111                       |

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

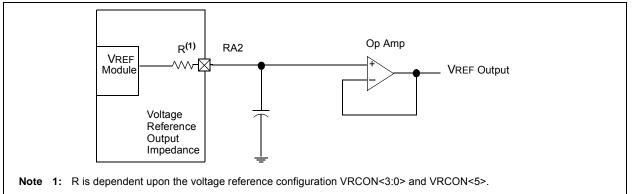

### 11.0 VOLTAGE REFERENCE MODULE

The Voltage Reference module consists of a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of VREF values and has a power-down function to conserve power when the reference is not being used. The VRCON register controls the operation of the reference as shown in Figure 11-1. The block diagram is given in Figure 11-1.

#### 11.1 Voltage Reference Configuration

bit

bit

bit

bit bit

The Voltage Reference module can output 16 distinct voltage levels for each range.

-n = Value at POR

The equations used to calculate the output of the Voltage Reference module are as follows:

if VRR = 1:

$$VREF = \frac{VR < 3:0}{24} \times VDD$$

if VRR = 0:

$$VREF = \left(VDD \times \frac{I}{4}\right) + \frac{VR < 3:0}{32} \times VDD$$

The setting time of the Voltage Reference module must be considered when changing the VREF output (Table 17-3). Example 11-1 demonstrates how voltage reference is configured for an output voltage of 1.25V with VDD = 5.0V.

| REGISTER 11-1: | VRCON – VOLTAGE REFERENCE CONTROL REGISTER (ADDRESS: 9Fh) |  |

|----------------|-----------------------------------------------------------|--|

|                |                                                           |  |

| VICON -                              | VULIAGE                                        | NEFERE          |              | INUL NEGIS | IER (ADI  | JKE33. 9       | гну   |

|--------------------------------------|------------------------------------------------|-----------------|--------------|------------|-----------|----------------|-------|

| R/W-0                                | R/W-0                                          | R/W-0           | U-0          | R/W-0      | R/W-0     | R/W-0          | R/W-0 |

| VREN                                 | VROE                                           | VRR             | _            | VR3        | VR2       | VR1            | VR0   |

| bit 7                                | · · · · · · · · · · · · · · · · · · ·          |                 |              |            |           |                | bit 0 |

| VREN: VR                             | EF Enable bit                                  | t               |              |            |           |                |       |

|                                      | circuit powere<br>circuit powere               |                 | d IDD drain  |            |           |                |       |

| 1 = Vref i                           | EF Output Er<br>s output on R<br>s disconnecte | RA2 pin         | 2 pin        |            |           |                |       |

| VRR: VRE<br>1 = Low ra<br>0 = High r | 0                                              | ection bit      |              |            |           |                |       |

| Unimplen                             | nented: Read                                   | <b>d as</b> '0' |              |            |           |                |       |

| When VRI                             | VREF Value S<br>R = 1: VREF =<br>R = 0: VREF = | = (VR<3:0>      | / 24) * VDD  |            |           |                |       |

| Legend:                              |                                                |                 |              |            |           |                |       |

| R = Reada                            | able bit                                       | VV = V          | Vritable bit | U = Unimpl | emented b | it, read as '( | 0'    |

|                                      |                                                |                 |              |            |           |                |       |

'0' = Bit is cleared

'1' = Bit is set

x = Bit is unknown

#### FIGURE 11-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 11-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR | Value On<br>All Other<br>Resets |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 9Fh     | VRCON | VREN   | VROE   | VRR    | —      | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 1Fh     | CMCON | C2OUT  | C10UT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 85h     | TRISA | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

**Legend:** - = Unimplemented, read as '0'.

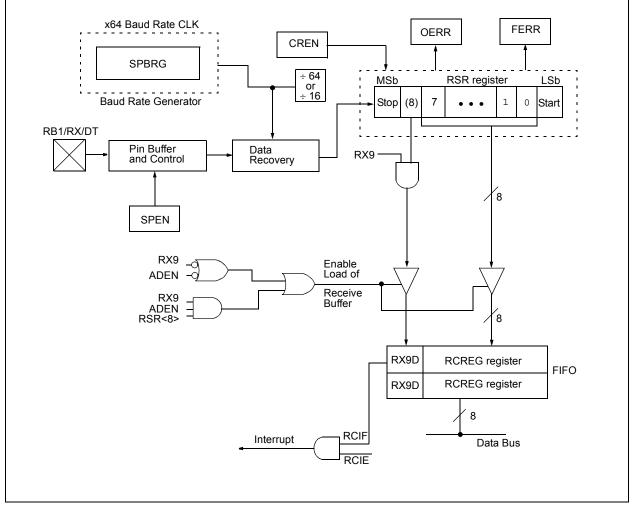

#### 12.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 12-4. The data is received on the RB1/RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc.

When Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the Receive (serial) Shift Register (RSR). After sampling the Stop bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read-only bit, which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a two-deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte begin shifting to the RSR register. On the detection of the Stop bit of the third byte, if the RCREG register is still full, then overrun error bit OERR (RCSTA<1>) will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited, so it is essential to clear error bit OERR if it is set. Framing error bit FERR (RCSTA<2>) is set if a Stop bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG, will load bits RX9D and FERR with new values, therefore it is essential for the user to read the RCSTA register before reading RCREG register in order not to lose the old FERR and RX9D information.

#### 12.3 USART Address Detect Function

#### 12.3.1 USART 9-BIT RECEIVER WITH ADDRESS DETECT

When the RX9 bit is set in the RCSTA register, 9 bits are received and the ninth bit is placed in the RX9D bit of the RCSTA register. The USART module has a special provision for multiprocessor communication. Multiprocessor communication is enabled by setting the ADEN bit (RCSTA<3>) along with the RX9 bit. The port is now programmed such that when the last bit is received, the contents of the Receive Shift Register (RSR) are transferred to the receive buffer, the ninth bit of the RSR (RSR<8>) is transferred to RX9D, and the receive interrupt is set if and only if RSR<8> = 1. This feature can be used in a multiprocessor system as follows:

A master processor intends to transmit a block of data to one of many slaves. It must first send out an address byte that identifies the target slave. An address byte is identified by setting the ninth bit (RSR<8>) to a '1' (instead of a '0' for a data byte). If the ADEN and RX9 bits are set in the slave's RCSTA register, enabling multiprocessor communication, all data bytes will be ignored. However, if the ninth received bit is equal to a '1', indicating that the received byte is an address, the slave will be interrupted and the contents of the RSR register will be transferred into the receive buffer. This allows the slave to be interrupted only by addresses, so that the slave can examine the received byte to see if it is being addressed. The addressed slave will then clear its ADEN bit and prepare to receive data bytes from the master.

When ADEN is enabled (= 1), all data bytes are ignored. Following the Stop bit, the data will not be loaded into the receive buffer, and no interrupt will occur. If another byte is shifted into the RSR register, the previous data byte will be lost. The ADEN bit will only take effect when the receiver is configured in 9-bit mode (RX9 = 1). When ADEN is disabled (= 0), all data bytes are received and the 9th bit can be used as the parity bit.

The receive block diagram is shown in Figure 12-4.

Reception is enabled by setting bit CREN (RCSTA<4>).

#### 12.3.1.1 Setting up 9-bit mode with Address Detect

Follow these steps when setting up Asynchronous Reception with Address Detect Enabled:

- 1. TRISB<1> and TRISB<2> should both be set to '1' to configure the RB1/RX/DT and RB2/TX/CK pins as inputs. Output drive, when required, is controlled by the peripheral circuitry.

- 2. Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH.

- 3. Enable asynchronous communication by setting or clearing bit SYNC and setting bit SPEN.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. Set bit RX9 to enable 9-bit reception.

- 6. Set ADEN to enable address detect.

- 7. Enable the reception by setting enable bit CREN or SREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 9. Read the 8-bit received data by reading the RCREG register to determine if the device is being addressed.

- 10. If an OERR error occurred, clear the error by clearing enable bit CREN if it was already set.

- 11. If the device has been addressed (RSR<8> = 1 with address match enabled), clear the ADEN and RCIF bits to allow data bytes and address bytes to be read into the receive buffer and interrupt the CPU.

| Address | Name                                   | Bit 7 | Bit 6   | Bit 5    | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>all other<br>Resets |

|---------|----------------------------------------|-------|---------|----------|--------|-------|--------|--------|--------|-----------------|---------------------------------|

| 0Ch     | PIR1                                   | EEIF  | CMIF    | RCIF     | TXIF   | _     | CCP1IF | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                       |

| 18h     | RCSTA                                  | SPEN  | RX9     | SREN     | CREN   | ADEN  | FERR   | OERR   | RX9D   | 0000 000x       | 0000 000x                       |

| 1Ah     | RCREG                                  | USART | Receive | Data Reg | gister |       |        |        |        | 0000 0000       | 0000 0000                       |

| 8Ch     | PIE1                                   | EEIE  | CMIE    | RCIE     | TXIE   | _     | CCP1IE | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                       |

| 98h     | TXSTA                                  | CSRC  | TX9     | TXEN     | SYNC   | _     | BRGH   | TRMT   | TX9D   | 0000 -010       | 0000 -010                       |

| 99h     | 99h SPBRG Baud Rate Generator Register |       |         |          |        |       |        |        |        | 0000 0000       | 0000 0000                       |

#### TABLE 12-8: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

**Legend:** x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

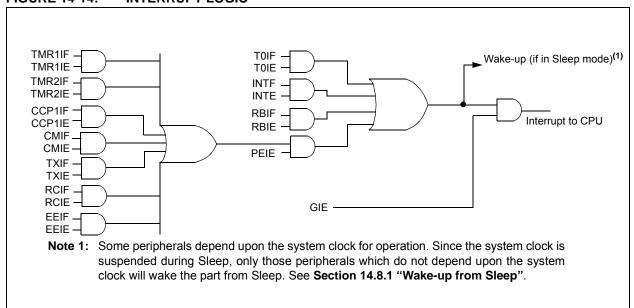

#### 14.5 Interrupts

The PIC16F627A/628A/648A has 10 sources of interrupt:

- External Interrupt RB0/INT

- TMR0 Overflow Interrupt

- PORTB Change Interrupts (pins RB<7:4>)

- Comparator Interrupt

- USART Interrupt TX

- USART Interrupt RX

- CCP Interrupt

- TMR1 Overflow Interrupt

- TMR2 Match Interrupt

- Data EEPROM Interrupt

The Interrupt Control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A Global Interrupt Enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on Reset.

The "return-from-interrupt" instruction, RETFIE, exits interrupt routine as well as sets the GIE bit, which reenables RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag is contained in the special register PIR1. The corresponding interrupt enable bit is contained in special registers PIE1.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/ INT recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 14-15). The latency is the same for one or two-cycle instructions. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

#### FIGURE 14-14: INTERRUPT LOGIC

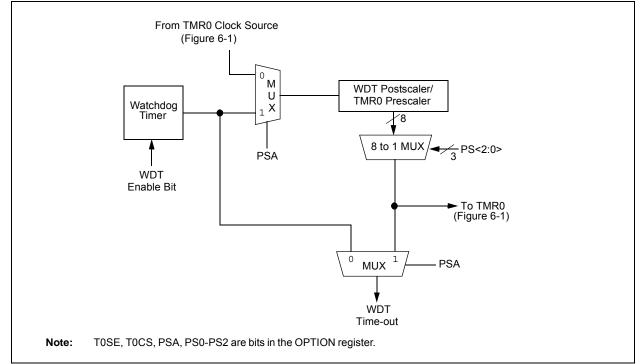

#### FIGURE 14-16: WATCHDOG TIMER BLOCK DIAGRAM

| <b>TABLE 14-9</b> : | SUMMARY OF WATCHDOG TIMER REGISTERS |

|---------------------|-------------------------------------|

|                     |                                     |

| Address   | Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR Reset | Value on<br>all other<br>Resets |  |

|-----------|--------|-------|--------|-------|-------|-------|-------|-------|-------|-----------------------|---------------------------------|--|

| 2007h     | CONFIG | LVP   | BOREN  | MCLRE | FOSC2 | PWRTE | WDTE  | FOSC1 | FOSC0 | uuuu uuuu             | uuuu uuuu                       |  |

| 81h, 181h | OPTION | RBPU  | INTEDG | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111             | 1111 1111                       |  |

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. **Note:** Shaded cells are not used by the Watchdog Timer.

### 14.8 Power-Down Mode (Sleep)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit in the Status register is cleared, the TO bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before SLEEP was executed (driving high, low or high-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSs with no external circuitry drawing current from the I/O pin and the comparators, and VREF should be disabled. I/O pins that are high-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a Reset generated<br>by a WDT time-out does not drive MCLR |

|-------|------------------------------------------------------------------------------------|

|       | pin low.                                                                           |

REG1, 7

REG1 = 0x0A

REG1 = 0x8A

Before Instruction

After Instruction

BSF

| BCF              | Bit Clear f                                                                          |            |              | BTFSC     | Bit Tes         | Bit Test f, Skip if Clear                                           |                                                                                           |                |        |  |  |

|------------------|--------------------------------------------------------------------------------------|------------|--------------|-----------|-----------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------|--------|--|--|

| Syntax:          | [ <i>label</i> ] BCF f,b                                                             |            |              |           | Syntax:         | [ label]                                                            | label]BTFSC f,b                                                                           |                |        |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                  |            |              | Operands: |                 | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |                                                                                           |                |        |  |  |

| Operation:       | $0 \rightarrow (f \leq$                                                              | b>)        |              |           | Operation:      | skip if (                                                           | ( <b>f<b>) =</b> 0</b>                                                                    |                |        |  |  |

| Status Affected: | None                                                                                 |            |              |           | Status Affected | I: None                                                             |                                                                                           |                |        |  |  |

| Encoding:        | 01                                                                                   | 00bb       | bfff         | ffff      | Encoding:       | 01                                                                  | 10bb                                                                                      | bfff           | ffff   |  |  |

| Description:     | Bit 'b' ir                                                                           | n register | f' is clea   | ared.     | Description:    |                                                                     | in register                                                                               |                |        |  |  |

| Words:           | 1                                                                                    |            |              |           |                 |                                                                     | struction is<br>' is '0', the                                                             |                |        |  |  |

| Cycles:          | 1                                                                                    |            |              |           |                 |                                                                     | tion fetche                                                                               |                |        |  |  |

| Example          | BCF REG1, 7<br>Before Instruction<br>REG1 = 0xC7<br>After Instruction<br>REG1 = 0x47 |            |              |           |                 |                                                                     | instructio                                                                                |                |        |  |  |

|                  |                                                                                      |            |              |           |                 |                                                                     | discarded, and a NOP is executed<br>instead, making this a two-cycle<br>instruction.<br>1 |                |        |  |  |

|                  |                                                                                      |            |              |           |                 |                                                                     |                                                                                           |                |        |  |  |

|                  |                                                                                      |            |              |           | Words:          | 1                                                                   |                                                                                           |                |        |  |  |

|                  |                                                                                      |            |              |           | Cycles:         | 1(2)                                                                |                                                                                           |                |        |  |  |

| BSF              | Bit Set                                                                              | f          |              |           | Example         | HERE<br>FALSE                                                       | BTFSC<br>GOTO                                                                             | REG1<br>PROCES | S_CODE |  |  |

| Syntax:          | [ label ]                                                                            | BSF f,     | b            |           |                 | TRUE                                                                | •                                                                                         |                |        |  |  |

| Operands:        | $0 \le f \le f$                                                                      |            |              |           |                 |                                                                     | •                                                                                         |                |        |  |  |

|                  | 0 ≤ b ≤                                                                              |            |              |           |                 |                                                                     | Instruction                                                                               | -              |        |  |  |

| Operation:       | $1 \rightarrow (f <$                                                                 | b>)        |              |           |                 |                                                                     | PC = add<br>struction                                                                     | dress HE       | RE     |  |  |

| Status Affected: | None                                                                                 |            |              |           |                 |                                                                     | f REG<1>                                                                                  | = 0.           |        |  |  |

| Encoding:        | 01                                                                                   | 01bb       | bfff         | ffff      |                 |                                                                     | PC = ad                                                                                   | - )            | UE     |  |  |

| Description:     | Bit 'b' ir                                                                           | n register | ʻʻf' is set. |           |                 |                                                                     | f REG<1>                                                                                  |                |        |  |  |

| Words:           | 1                                                                                    |            |              |           |                 | ł                                                                   | PC = ade                                                                                  | uress FA       | LSE    |  |  |

| Cycles:          | 1                                                                                    |            |              |           |                 |                                                                     |                                                                                           |                |        |  |  |

Example

#### 16.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

#### 16.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

#### 16.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

#### 16.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 16.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB IDE compatibility

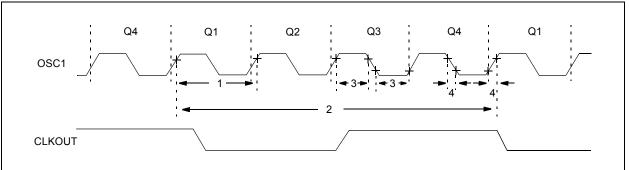

#### 17.6 **Timing Diagrams and Specifications**

#### **FIGURE 17-4: EXTERNAL CLOCK TIMING**

| TABLE 17-4: | EXTERNAL CLOCK TIMING REQUIREMENTS |

|-------------|------------------------------------|

|             |                                    |

| Parameter<br>No. | Sym           | Characteristic                                   | Min     | Тур† | Max    | Units | Conditions                         |

|------------------|---------------|--------------------------------------------------|---------|------|--------|-------|------------------------------------|

|                  | Fosc          | External CLKIN Frequency <sup>(1)</sup>          | DC      | —    | 4      | MHz   | XT and RC Osc mode,<br>VDD = 5.0 V |

|                  |               |                                                  | DC      |      | 20     | MHz   | HS, EC Osc mode                    |

|                  |               |                                                  | DC      |      | 200    | kHz   | LP Osc mode                        |

|                  |               | Oscillator Frequency <sup>(1)</sup>              | —       |      | 4      | MHz   | RC Osc mode, VDD = 5.0V            |

|                  |               |                                                  | 0.1     | _    | 4      | MHz   | XT Osc mode                        |

|                  |               |                                                  | 1       |      | 20     | MHz   | HS Osc mode                        |

|                  |               |                                                  | —       |      | 200    | kHz   | LP Osc mode                        |

|                  |               |                                                  | —       | 4    | —      | MHz   | INTOSC mode (fast)                 |

|                  |               |                                                  | —       | 48   |        | kHz   | INTOSC mode (slow)                 |

| 1                | Tosc          | External CLKIN Period <sup>(1)</sup>             | 250     | —    | —      | ns    | XT and RC Osc mode                 |

|                  |               |                                                  | 50      |      | —      | ns    | HS, EC Osc mode                    |

|                  |               |                                                  | 5       | —    | —      | μS    | LP Osc mode                        |

|                  |               | Oscillator Period <sup>(1)</sup>                 | 250     | —    | —      | ns    | RC Osc mode                        |

|                  |               |                                                  | 250     | _    | 10,000 | ns    | XT Osc mode                        |

|                  |               |                                                  | 50      |      | 1,000  | ns    | HS Osc mode                        |

|                  |               |                                                  | 5       | _    | —      | μS    | LP Osc mode                        |

|                  |               |                                                  | _       | 250  | —      | ns    | INTOSC mode (fast)                 |

|                  |               |                                                  | _       | 21   | _      | μS    | INTOSC mode (slow)                 |

| 2                | TCY           | Instruction Cycle Time                           | 200     | TCY  | DC     | ns    | Tcy = 4/Fosc                       |

| 3                | TosL,<br>TosH | External CLKIN (OSC1) High<br>External CLKIN Low | 100*    | _    | —      | ns    | XT oscillator, Tosc L/H duty cycle |

| 4                | RC            | External Biased RC<br>Frequency                  | 10 kHz* | _    | 4 MHz  | —     | VDD = 5.0V                         |

These parameters are characterized but not tested.

t Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time-based period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "Max" cycle time limit is "DC" (no clock) for all devices.

| Parameter<br>No. | Sym      | Characteristic                                          |             | Min          | Тур† | Max  | Units |

|------------------|----------|---------------------------------------------------------|-------------|--------------|------|------|-------|

| 10               | TosH2ckL | OSC1↑ to CLKOUT↓                                        | PIC16F62XA  | _            | 75   | 200* | ns    |

| 10A              |          |                                                         | PIC16LF62XA | —            |      | 400* | ns    |

| 11               | TosH2ckH | OSC1↑ to CLKOUT↑                                        | PIC16F62XA  | —            | 75   | 200* | ns    |

| 11A              |          |                                                         | PIC16LF62XA | —            | _    | 400* | ns    |

| 12               | ТскR     | CLKOUT rise time                                        | PIC16F62XA  | —            | 35   | 100* | ns    |

| 12A              |          |                                                         | PIC16LF62XA | —            | —    | 200* | ns    |

| 13               | ТскF     | CLKOUT fall time                                        | PIC16F62XA  | —            | 35   | 100* | ns    |

| 13A              |          |                                                         | PIC16LF62XA | —            | _    | 200* | ns    |

| 14               | TcĸL2IoV | CLKOUT $\downarrow$ to Port out valid                   |             | —            | _    | 20*  | ns    |

| 15               | TIOV2CKH | Port in valid before CLKOUT $\uparrow$                  | PIC16F62XA  | Tosc+200 ns* | —    | _    | ns    |

|                  |          |                                                         | PIC16LF62XA | Tosc+400 ns* | _    | _    | ns    |

| 16               | ΤςκΗ2ιοΙ | Port in hold after CLKOUT $\uparrow$                    |             | 0            | —    | _    | ns    |

| 17               | TosH2IoV | OSC1↑ (Q1 cycle) to                                     | PIC16F62XA  | —            | 50   | 150* | ns    |

|                  |          | Port out valid                                          | PIC16LF62XA |              |      | 300* | ns    |

| 18               | TosH2ıol | OSC1↑ (Q2 cycle) to Port input in<br>(I/O in hold time) | valid       | 100*<br>200* |      | _    | ns    |

#### TABLE 17-6: CLKOUT AND I/O TIMING REQUIREMENTS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

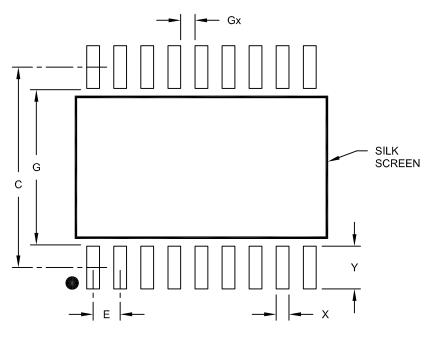

18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

### RECOMMENDED LAND PATTERN

|                       | Units  | MILLIMETERS |      |      |  |

|-----------------------|--------|-------------|------|------|--|

| Dimension             | Limits | MIN         | NOM  | MAX  |  |

| Contact Pitch         | Е      | 1.27 BSC    |      |      |  |

| Contact Pad Spacing   | С      |             | 9.40 |      |  |

| Contact Pad Width     | Х      |             |      | 0.60 |  |

| Contact Pad Length    | Y      |             |      | 2.00 |  |

| Distance Between Pads | Gx     | 0.67        |      |      |  |

| Distance Between Pads | G      | 7.40        |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2051A