Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | UART/USART                                                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf648at-i-so |

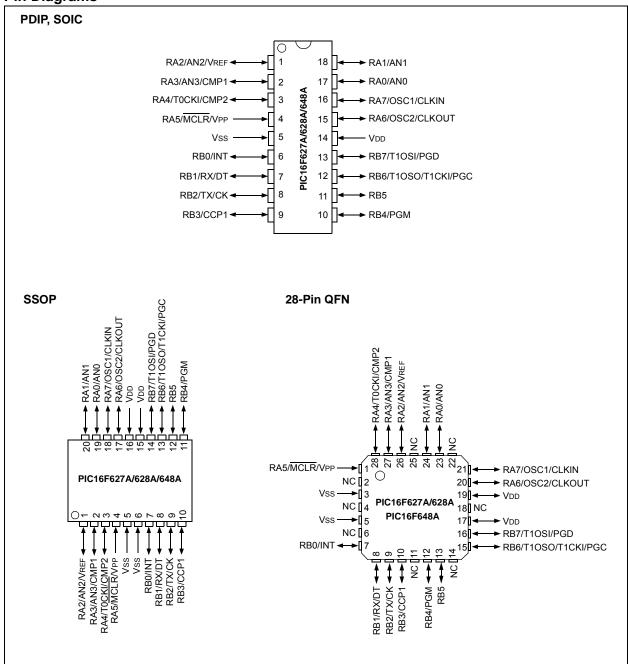

### **Pin Diagrams**

#### **Table of Contents**

| 1.0 General Description                                                     | 7    |

|-----------------------------------------------------------------------------|------|

| 2.0 PIC16F627A/628A/648A Device Varieties                                   | 9    |

| 3.0 Architectural Overview                                                  | . 11 |

| 4.0 Memory Organization                                                     | 17   |

| 5.0 I/O Ports                                                               | . 33 |

| 6.0 Timer0 Module                                                           | 47   |

| 7.0 Timer1 Module                                                           | 50   |

| 8.0 Timer2 Module                                                           | . 54 |

| 9.0 Capture/Compare/PWM (CCP) Module                                        | . 57 |

| 10.0 Comparator Module                                                      |      |

| 11.0 Voltage Reference Module                                               | . 69 |

| 12.0 Universal Synchronous Asynchronous Receiver Transmitter (USART) Module | . 73 |

| 13.0 Data EEPROM Memory                                                     |      |

| 14.0 Special Features of the CPU                                            |      |

| 15.0 Instruction Set Summary                                                | 117  |

| 16.0 Development Support                                                    | 131  |

| 17.0 Electrical Specifications                                              | 135  |

| 18.0 DC and AC Characteristics Graphs and Tables                            | 151  |

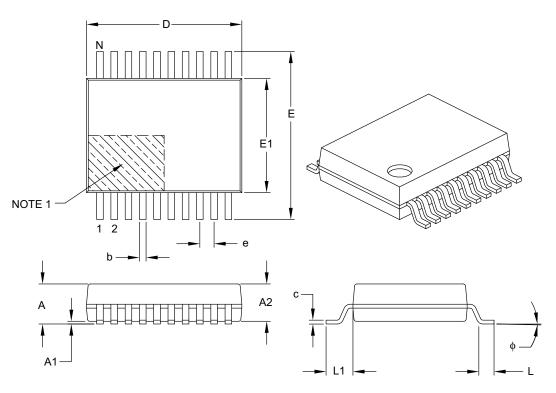

| 19.0 Packaging Information                                                  | 163  |

| Appendix A: Data Sheet Revision History                                     |      |

| Appendix B: Device Differences                                              | 171  |

| Appendix C: Device Migrations                                               |      |

| Appendix D: Migrating from other PIC <sup>®</sup> Devices                   | 172  |

| The Microchip Web Site                                                      | 173  |

| Customer Change Notification Service                                        |      |

| Customer Support                                                            | 173  |

| Reader Response                                                             | 174  |

| Product Identification System                                               | 179  |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

NOTES:

FIGURE 4-3: **DATA MEMORY MAP OF THE PIC16F648A** File Address Indirect addr. (1) Indirect addr.(1) Indirect addr. (1) Indirect addr. (1) 100h 00h 80h 180h 101h OPTION TMR0 01h **OPTION** TMR0 81h 181h PCL 102h PCL 02h PCL 82h **PCL** 182h **STATUS** 103h **STATUS** 03h **STATUS STATUS** 83h 183h **FSR** 04h **FSR** 104h FSR 184h **FSR** 84h 105h **PORTA** 05h 185h **TRISA** 85h TRISB **PORTB PORTB** 06h 106h **TRISB** 86h 186h 07h 107h 87h 187h 08h 108h 88h 188h 09h 109h 189h 89h **PCLATH** 10Ah **PCLATH** 0Ah **PCLATH** 8Ah **PCLATH** 18Ah INTCON 0Bh INTCON 10Bh INTCON INTCON 8Bh 18Bh PIR1 0Ch 10Ch 18Ch PIE1 8Ch 10Dh 0Dh 18Dh 8Dh 10Eh TMR1L 0Eh **PCON** 8Eh 18Eh TMR1H 0Fh 10Fh 18Fh 8Fh T1CON 10h 90h TMR2 11h 91h T2CON 12h PR2 92h 13h 93h 14h 94h CCPR1L 15h 95h CCPR1H 16h 96h CCP1CON 17h 97h 18h **RCSTA TXSTA** 98h 19h 99h **TXREG** SPBRG EEDATA 1Ah **RCREG** 9Ah 1Bh **EEADR** 9Bh EECON1 1Ch 9Ch EECON2<sup>(1)</sup> 1Dh 9Dh 1Eh 9Eh 1Fh **CMCON VRCON** 9Fh 11Fh 20h 120h A0h General General General Purpose Purpose Purpose Register 80 Bytes Register Register 80 Bytes 80 Bytes 1EFh 6Fh **EFh** 16Fh 1F0h 70h F0h 170h accesses accesses accesses 16 Bytes 70h-7Fh 70h-7Fh 70h-7Fh 1FFh 7Fh FFh 17Fh Bank 1 Bank 2 Bank 3 Bank 0 Unimplemented data memory locations, read as '0'. Note 1: Not a physical register.

### 4.2.2.2 OPTION Register

The Option register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT (PSA = 1). See **Section 6.3.1** "**Switching Prescaler Assignment**".

### REGISTER 4-2: OPTION\_REG - OPTION REGISTER (ADDRESS: 81h, 181h)

|       |        |       |       |       |       |       | 1 '' 0 |

|-------|--------|-------|-------|-------|-------|-------|--------|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0    |

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1  |

Note:

bit 7 bit 0

bit 7 RBPU: PORTB Pull-up Enable bit

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

bit 6 **INTEDG**: Interrupt Edge Select bit

1 = Interrupt on rising edge of RB0/INT pin

0 = Interrupt on falling edge of RB0/INT pin

bit 5 TOCS: TMR0 Clock Source Select bit

1 = Transition on RA4/T0CKI/CMP2 pin

0 = Internal instruction cycle clock (CLKOUT)

bit 4 **T0SE**: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on RA4/T0CKI/CMP2 pin

0 = Increment on low-to-high transition on RA4/T0CKI/CMP2 pin

bit 3 **PSA**: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 **PS<2:0>**: Prescaler Rate Select bits

| Bit Value | TMR0 Rate | WDT Rate |

|-----------|-----------|----------|

| 000       | 1:2       | 1:1      |

| 001       | 1:4       | 1:2      |

| 010       | 1:8       | 1:4      |

| 011       | 1:16      | 1:8      |

| 100       | 1:32      | 1:16     |

| 101       | 1:64      | 1:32     |

| 110       | 1:128     | 1:64     |

| 111       | 1:256     | 1 : 128  |

| e | ~ | Δ | n | ~ | • |

|---|---|---|---|---|---|

|   |   |   |   |   |   |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

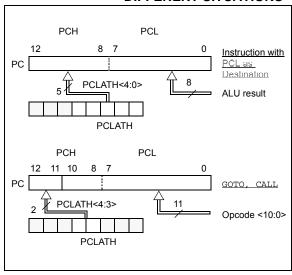

#### 4.3 PCL and PCLATH

The Program Counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 4-4 shows the two situations for loading the PC. The upper example in Figure 4-4 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 4-4 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 4-4: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the Application Note AN556 "Implementing a Table Read" (DS00556).

#### 4.3.2 STACK

The PIC16F627A/628A/648A family has an 8-level deep x 13-bit wide hardware stack (Figure 4-1). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth PUSH overwrites the value that was stored from the first PUSH. The tenth PUSH overwrites the second PUSH (and so on).

- **Note 1:** There are no Status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

## 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-5.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 4-1.

**EXAMPLE 4-1: INDIRECT ADDRESSING**

|      | MOVLW | 0x20  | ;initialize pointer  |

|------|-------|-------|----------------------|

|      | MOVWF | FSR   | ;to RAM              |

| NEXT | CLRF  | INDF  | clear INDF register; |

|      | INCF  | FSR   | ;inc pointer         |

|      | BTFSS | FSR,4 | ;all done?           |

|      | GOTO  | NEXT  | ;no clear next       |

|      |       |       | ;yes continue        |

|      |       |       |                      |

FIGURE 4-5: DIRECT/INDIRECT ADDRESSING PIC16F627A/628A/648A Status Register Status Register **Direct Addressing** Indirect Addressing RP1 RP0 from opcode 0 IRP FSR Register bank select location select bank select location select **▶** 00 01 10 11 00h 180h RAM File Registers 7Fh 1FFh Bank 0 Bank 1 Bank 2 Bank 3 For memory map detail see Figure 4-3, Figure 4-2 and Figure 4-1. Note:

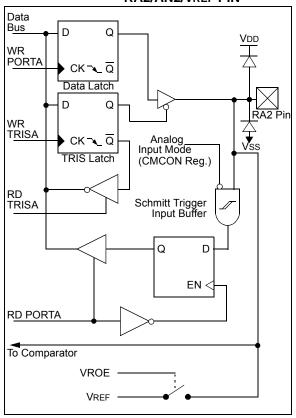

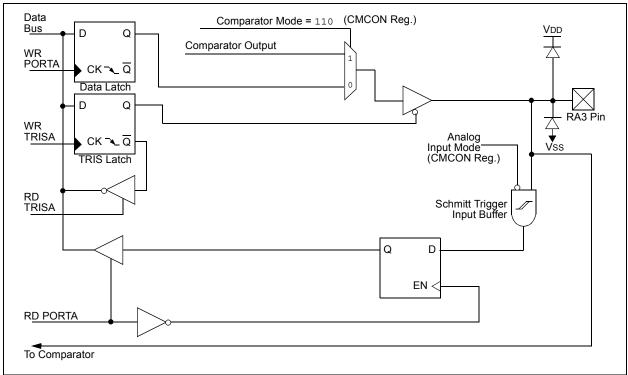

FIGURE 5-2: BLOCK DIAGRAM OF RA2/AN2/VREF PIN

### FIGURE 5-3: BLOCK DIAGRAM OF THE RA3/AN3/CMP1 PIN

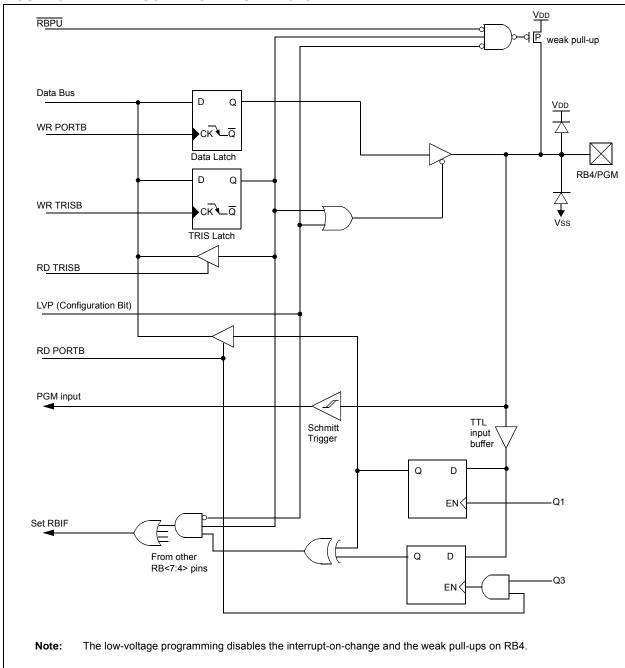

FIGURE 5-12: BLOCK DIAGRAM OF RB4/PGM PIN

### 10.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be reset by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

Note: If a change in the CMCON register (C1OUT or C2OUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CMIF (PIR1<6>) interrupt flag may not get set.

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- Any write or read of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition and allow flag bit CMIF to be cleared.

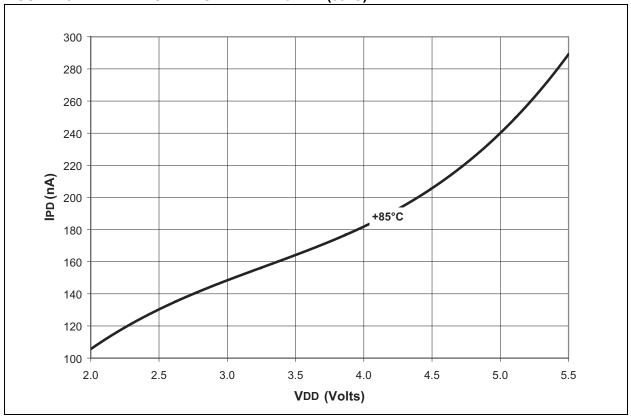

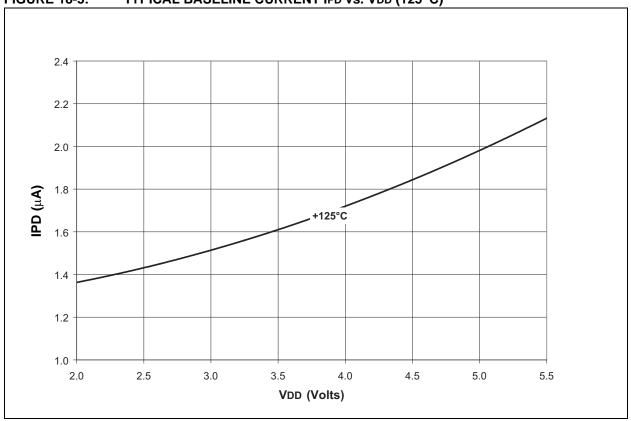

### 10.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from Sleep mode when enabled. While the comparator is powered-up, higher Sleep currents than shown in the power-down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators, CM<2:0> = 111, before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

#### 10.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state. This forces the Comparator module to be in the comparator Reset mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at Reset time. The comparators will be powered-down during the Reset interval.

### 10.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 10-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur. A maximum source impedance of 10  $k\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

### REGISTER 14-1: CONFIG – CONFIGURATION WORD REGISTER

| CP          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                  | _                                | CPD        | LVP        | BOREN                      | MCLRE         | FOSC2         | PWRTE    | WDTE        | F0SC1 | F0SC0 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------|------------|------------|----------------------------|---------------|---------------|----------|-------------|-------|-------|

| bit 13      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |                                  |            |            | -                          |               |               |          |             |       | bit 0 |

| bit 13:     | (PIC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CP: Flash Program Memory Code Protection bit <sup>(2)</sup> (PIC16F648A)  1 = Code protection off 0 = 0000h to 0FFFh code-protected (PIC16F628A)  1 = Code protection off 0 = 0000h to 07FFh code-protected (PIC16F627A)  1 = Code protection off 0 = 0000h to 03FFh code-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |                                  |            |            |                            |               |               |          |             |       |       |

| bit 12-9:   | Unim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | plemented                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>i</b> : Read as | '0'                              |            |            |                            |               |               |          |             |       |       |

| bit 8:      | 1 = D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Data Code<br>ata memor<br>ata memor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | y code pro         | tection off                      |            |            |                            |               |               |          |             |       |       |

| bit 7:      | 1 = R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | B4/PGM pi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | in has PGN         |                                  | ow-voltage |            | ning enableo<br>programmir |               |               |          |             |       |       |

| bit 6:      | 1 = B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | EN: Brown-<br>OR Reset of OR Reset of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | enabled            | Enable bit <sup>(</sup>          | (1)        |            |                            |               |               |          |             |       |       |

| bit 5:      | 1 = R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | A5/MCLR/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VPP pin fur        | Pin Function is MC action is dig | LR _       | ICLR inter | nally tied to              | VDD           |               |          |             |       |       |

| bit 3:      | 1 = P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TE: Power-<br>WRT disab<br>WRT enabl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | led                | Enable bit <sup>(1</sup>         | )          |            |                            |               |               |          |             |       |       |

| bit 2:      | 1 = W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | E: Watchdo<br>/DT enable<br>/DT disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | d                  | nable bit                        |            |            |                            |               |               |          |             |       |       |

| bit 4, 1-0: | 111 = 110 = 101 = 100 = 011 = 010 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 00000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 00000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 00000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 00000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 00000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 00000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 00000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 00000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 00000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 00000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 0000 = 00000 = 0000 = 0000 = 0000 = 0000 = 0000 = 00000 = 00000 = 0000 = 00000 = 00000 = 0000 = 0000 = 0000 = 00000 = 00000 = 00000 = 00000 | FOSC<2:0>: Oscillator Selection bits <sup>(4)</sup> 111 = RC oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, Resistor and Capacitor on RA7/OSC1/CLKIN 110 = RC oscillator: I/O function on RA6/OSC2/CLKOUT pin, Resistor and Capacitor on RA7/OSC1/CLKIN 101 = INTOSC oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN 100 = INTOSC oscillator: I/O function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN 011 = EC: I/O function on RA6/OSC2/CLKOUT pin, CLKIN on RA7/OSC1/CLKIN 010 = HS oscillator: High-speed crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN 001 = XT oscillator: Crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN 000 = LP oscillator: Low-power crystal on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN |                    |                                  |            |            |                            |               |               |          |             |       |       |

|             | <ol> <li>Enabling Brown-out Reset does not automatically enable the Power-up Timer (PWRT) the way it does on the PIC16F627/628 devices.</li> <li>The code protection scheme has changed from the code protection scheme used on the PIC16F627/628 devices. The entire Flash program memory needs to be bulk erased to set the CP bit, turning the code protection off. See "PIC16F627A/628A/648A EEPROM Memory Programming Specification" (DS41196) for details.</li> <li>The entire data EEPROM Memory Programming Specification" (DS41196) for details.</li> <li>When MCLR is asserted in INTOSC mode, the internal clock oscillator is disabled.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |                                  |            |            |                            |               |               |          |             |       |       |

|             | Lege                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | nd:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |                                  |            |            |                            |               |               |          |             |       |       |

|             | R = F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Readable bi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | t                  | W = Wri                          | itable bit |            | U = Ur                     | nimplemen     | ted bit, read | d as '0' |             |       |       |

|             | -n = \                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | /alue at PO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R                  | '1' = bit                        | is set     |            | '0' = bi                   | it is cleared | I             | x =      | bit is unkn | own   |       |

| CLRW             | Clear W                                                            |  |  |  |  |  |

|------------------|--------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] CLRW                                                       |  |  |  |  |  |

| Operands:        | None                                                               |  |  |  |  |  |

| Operation:       | $00h \rightarrow (W)$ $1 \rightarrow Z$                            |  |  |  |  |  |

| Status Affected: | Z                                                                  |  |  |  |  |  |

| Encoding:        | 00 0001 0000 0011                                                  |  |  |  |  |  |

| Description:     | W register is cleared. Zero bit (Z) is set.                        |  |  |  |  |  |

| Words:           | 1                                                                  |  |  |  |  |  |

| Cycles:          | 1                                                                  |  |  |  |  |  |

| Example          | CLRW                                                               |  |  |  |  |  |

|                  | Before Instruction $W = 0x5A$ After Instruction $W = 0x00$ $Z = 1$ |  |  |  |  |  |

| COMF             | Complement f                                                                                                                                       |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] COMF f,d                                                                                                                                 |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                 |

| Operation:       | $(\bar{f}) \rightarrow (\text{dest})$                                                                                                              |

| Status Affected: | Z                                                                                                                                                  |

| Encoding:        | 00 1001 dfff ffff                                                                                                                                  |

| Description:     | The contents of register 'f' are complemented. If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back in register 'f'. |

| Words:           | 1                                                                                                                                                  |

| Cycles:          | 1                                                                                                                                                  |

| Example Page 1   | COMF REG1, 0                                                                                                                                       |

|                  | Before Instruction REG1 = 0x13  After Instruction REG1 = 0x13 W = 0xEC                                                                             |

| CLRWDT           | Clear Watchdog Timer                                                                                                |                     |           |                |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------|---------------------|-----------|----------------|--|--|

| Syntax:          | [label] CLRWDT                                                                                                      |                     |           |                |  |  |

| Operands:        | None                                                                                                                |                     |           |                |  |  |

| Operation:       | 00h → WDT<br>0 → WDT prescaler,<br>1 → $\overline{TO}$<br>1 → $\overline{PD}$                                       |                     |           |                |  |  |

| Status Affected: | TO, PD                                                                                                              |                     |           |                |  |  |

| Encoding:        | 00                                                                                                                  | 0000                | 0110      | 0100           |  |  |

| Description:     | CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Stat bits TO and PD are set. |                     |           |                |  |  |

| Words:           | 1                                                                                                                   |                     |           |                |  |  |

| Cycles:          | 1                                                                                                                   |                     |           |                |  |  |

| <u>Example</u>   | CLRWDT                                                                                                              |                     |           |                |  |  |

|                  | After Ins                                                                                                           | struction<br>WDT co | unter = 1 | 0x00<br>0<br>1 |  |  |

| DECF             | Decrement f                                                                                                                              |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] DECF f,d                                                                                                                         |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                       |  |  |  |  |  |

| Operation:       | $(f) - 1 \rightarrow (dest)$                                                                                                             |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                        |  |  |  |  |  |

| Encoding:        | 00 0011 dfff ffff                                                                                                                        |  |  |  |  |  |

| Description:     | Decrement register 'f'. If 'd' is '0'. the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                        |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                        |  |  |  |  |  |

| <u>Example</u>   | DECF CNT, 1                                                                                                                              |  |  |  |  |  |

|                  | Before Instruction $CNT = 0x01$ $Z = 0$ After Instruction $CNT = 0x00$ $Z = 1$                                                           |  |  |  |  |  |

| RRF               | Rotate Right f through Carry                                                                                                       | SUBLW        | Subtract W from Literal                                                                                                             |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | [label] RRF f,d                                                                                                                    | Syntax:      | [ label ] SUBLW k                                                                                                                   |

| Operands:         | $0 \leq f \leq 127$                                                                                                                | Operands:    | $0 \leq k \leq 255$                                                                                                                 |

|                   | $d \in [0,1]$                                                                                                                      | Operation:   | $k - (W) \rightarrow (W)$                                                                                                           |

| Operation:        | See description below                                                                                                              | Status       | C, DC, Z                                                                                                                            |

| Status Affected:  | С                                                                                                                                  | Affected:    |                                                                                                                                     |

| Encoding:         | 00 1100 dfff ffff                                                                                                                  | Encoding:    | 11 110x kkkk kkkk                                                                                                                   |

| Description:      | The contents of register 'f' are rotated one bit to the right through the Carry Flag. If 'd' is '0', the result is placed in the W | Description: | The W register is subtracted (2's complement method) from the eight-<br>bit literal 'k'. The result is placed in<br>the W register. |

|                   | register. If 'd' is '1', the result is                                                                                             | Words:       | 1                                                                                                                                   |

|                   | placed back in register 'f'.                                                                                                       | Cycles:      | 1                                                                                                                                   |

|                   | C REGISTER F                                                                                                                       | Example 1:   | SUBLW 0x02                                                                                                                          |

| Words:            | 1                                                                                                                                  | •            | Before Instruction                                                                                                                  |

| Cycles:           | 1                                                                                                                                  |              | W = 1                                                                                                                               |

| <u>Example</u>    | RRF REG1, 0                                                                                                                        |              | C = ?                                                                                                                               |

| <del></del> -     | Before Instruction                                                                                                                 |              | After Instruction                                                                                                                   |

|                   | REG1 = 1110 0110                                                                                                                   |              | W = 1                                                                                                                               |