# E·XFL

#### NXP USA Inc. - MCF51EM256CLLR Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | Coldfire V1                                                            |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 50MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                             |

| Peripherals                | LCD, LVD, PWM, WDT                                                     |

| Number of I/O              | 63                                                                     |

| Program Memory Size        | 256KB (256K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 16K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |

| Data Converters            | A/D 16x12b                                                             |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 100-LQFP                                                               |

| Supplier Device Package    | 100-LQFP (14x14)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcf51em256cllr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Feature            | MCF51EM256 MCF51EM128 |    |  |  |

|--------------------|-----------------------|----|--|--|

| MTIM1 (8-bit)      | Ye                    | es |  |  |

| MTIM2 (8-bit)      | Yes                   |    |  |  |

| MTIM3 (16-it)      | Yes                   |    |  |  |

| TPM channels       | 2                     |    |  |  |

| PDB                | Yes                   |    |  |  |

| XOSC1 <sup>4</sup> | Yes                   |    |  |  |

| XOSC2 <sup>5</sup> | Yes                   |    |  |  |

#### Table 1. MCF51EM256 Series Features by MCU and Package (continued)

<sup>1</sup> Each differential channel is comprised of 2 pin inputs

<sup>2</sup> RGPIO is muxed with standard Port I/O

<sup>3</sup> Port I/O count does not include the ouput only PTC2/BKGD/MS.

<sup>4</sup> IRTC crystal input and possible crystal input to the ICS module

<sup>5</sup> Main external crystal input for the ICS module

### 1.2 Block Diagram

Figure 1 shows the connections between the MCF51EM256 series pins and modules.

### 1.3 Features

Table 2 describes the functional units of the MCF51EM256 series.

| Table 2. MCF51EM256 | <b>Series Functional Units</b> |

|---------------------|--------------------------------|

|---------------------|--------------------------------|

| Unit                                       | Function                                                                                                                                                                            |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC (analog-to-digital converter)          | Measures analog voltages at up to 16 bits of resolution. Each ADC has<br>up to four differential and 24 single-ended inputs.                                                        |

| BDM (background debug module)              | Provides single pin debugging interface (part of the V1 ColdFire core)                                                                                                              |

| CF1 CORE (V1 ColdFire core) with MAC unit  | Executes programs, handles interrupts and containes multiply-accumulate hardware (MAC).                                                                                             |

| PRACMP1, PRACMP2 (comparators)             | Analog comparators for comparing external analog signals against each other, or a variety of reference levels.                                                                      |

| COP (computer operating poperly)           | Software watchdog                                                                                                                                                                   |

| IRQ (interrupt request)                    | Single pin high priority interrupt (part of the V1 ColdFire core)                                                                                                                   |

| CRC (cyclic Redundancy Check)              | High-speed CRC calculation                                                                                                                                                          |

| DBG (debug)                                | Provides debugging and emulation capabilities (part of the V1 ColdFire core)                                                                                                        |

| FLASH (flash memory)                       | Provides storage for program code, constants and variables                                                                                                                          |

| IIC (inter-integrated circuits)            | Supports standard IIC communications protocol and SMBus                                                                                                                             |

| INTC (interrupt controller)                | Controls and prioritizes all device interrupts                                                                                                                                      |

| KBI1 & KBI2                                | Keyboard Interfaces 1 and 2                                                                                                                                                         |

| LCD                                        | Liquid crystal display driver                                                                                                                                                       |

| LVD (low voltage detect)                   | Provides an interrupt to the CF1CORE in the event that the supply voltage drops below a critical value. The LVD can also be programmed to reset the device upon a low voltage event |

| ICS (internal clock source)                | Provides clocking options for the device, including a three<br>frequency-locked loops (FLLs) for multiplying slower reference clock<br>sources                                      |

| IRTC (independent real-time clock)         | The independent real time clock provides an independent time-base with optional interrupt, battery backup and tamper protection                                                     |

| VREF (voltage reference)                   | The voltage reference output is available for both on and off-chip use                                                                                                              |

| MTIM1, MTIM2 (modulo timers)               | 8-bit modulo timers with configurable clock inputs and interrupt generation on overflow                                                                                             |

| MTIM3 (modulo timer)                       | 16-bit modulo timer with configurable clock inputs and interrupt generation on overflow                                                                                             |

| PDB (programmable delay block)             | This timer is optimized for scheduling ADC conversions                                                                                                                              |

| RAM (random-access memory)                 | Provides stack and variable storage                                                                                                                                                 |

| RGPIO (rapid general-purpose input/output) | Allows for I/O port access at CPU clock speeds and is used to implement GPIO functionality for PTA and PTB.                                                                         |

#### MCF51EM256 Series ColdFire Microcontroller Data Sheet, Rev.3

- 6 µs typical wakeup time from stop3 mode

- Clock source options

- Two independent oscillators (XOSC1 and XOSC2) loop-control Pierce oscillator;

32.768 kHz crystal or ceramic resonator. XOSC1 nominally supports the independent real time clock, and can be powered by a separate battery backup. XOSC2 is the primary external clock source for the ICS

- Internal clock source (ICS) internal clock source module containing a frequency-locked-loop (FLL) controlled by internal or external reference (XOSC1 or XOSC2); precision trimming of internal reference allowing 0.2% resolution and typical 0.5% to –1% deviation over temperature and voltage; supporting CPU frequencies from 4 kHz to 50 MHz

- System protection

- Watchdog computer operating properly (COP) reset with option to run from dedicated 1 kHz internal clock source or bus clock

- Low voltage detection with reset or interrupt; selectable trip points; seperate low voltage warning with optional interrupt; selectable trip points

- Illegal opcode and illegal address detection with reset

- Flash block protection for each array to prevent accidental write/erasure

- Hardware CRC module to support fast cyclic redundancy checks

- Development support

- Integrated ColdFire DEBUG\_Rev\_B+ interface with single wire BDM connection supports same electrical interface used by the S08 family debug modules

- Real-time debug support with six hardware breakpoints (4 PC, 1 address and 1 data)

- On-chip trace buffer provides programmable start/stop recording conditions

- Peripherals

- ADC16 4 analog-to-digital converters; the 100 pin version of the device has 1 dedicated differential channel and 1 dedicated single-ended channel per ADC, along with 3 muxed single-ended channels per ADC. The ADCs have 16-bit resolution, range compare function, 1.7 mV/°C temperature sensor, internal bandgap reference channel, operate in stop3 and are fully functional from 3.6 V to 1.8 V

- PDB Programmable delay block with 16-bit counter and modulus and 3-bit prescaler; 8 trigger outputs for ADC16 modules (2 per ADC); provides periodic coordination of ADC sampling sequence with programmable sequence completion interrupt

- IRTC Ultra-low power independent real time clock with calendar features (IRTC); runs in all MCU modes; external clock source with trim capabilities (XOSC1); independent voltage source runs IRTC when MCU is powered-down; tamper detection and indicator; battery monitor output to ADC; unaffected by MCU resets

- **PRACMPx** Two analog comparators with selectable interrupt on rising, falling, or either edge of comparator output; compare option to programmable internal reference voltage; operation in stop3

- LCD up to 288 segments  $(8 \times 36)$ ; 160 segments  $(4 \times 40)$ ; internal charge pump and option to provide internal reference voltage that can be trimmed for contrast control; flexible

| Freescale Part Number | Flash / SRAM (KB) | Package      | Temperature   |

|-----------------------|-------------------|--------------|---------------|

| MCF51EM256CLL         | 256/16            | 100-Pin LQFP | –40°C to 85°C |

| MCF51EM256CLK         | 256/16            | 80-Pin LQFP  | –40°C to 85°C |

| MCF51EM128CLL         | 128/16            | 100-Pin LQFP | –40°C to 85°C |

| MCF51EM128CLK         | 128/16            | 80-Pin LQFP  | –40°C to 85°C |

#### Table 3. Orderable Part Number Summary

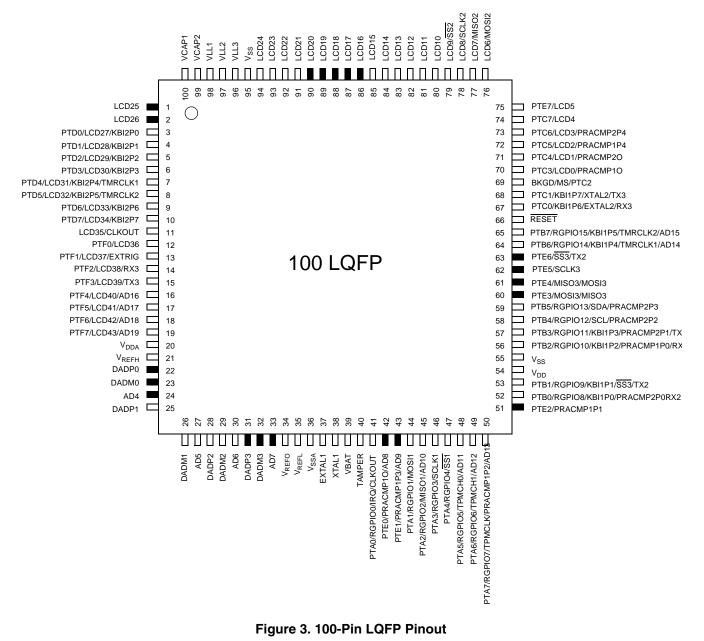

## 1.5.2 Pinout: 100-Pin LQFP

Figure 3 shows the pinout configuration for the 100-pin LQFP. Pins which are blacked out do not have an equivalent pin on the 80-pin LQFP package.

Table 4 shows the package pin assignments.

| 100<br>LQFP | 80<br>LQFP | Default Function  | ALT1   | ALT2   | ALT3    | Comment |

|-------------|------------|-------------------|--------|--------|---------|---------|

| 1           | _          | LCD25             |        |        |         |         |

| 2           | —          | LCD26             |        |        |         |         |

| 3           | 1          | PTD0              | LCD27  | KBI2P0 |         |         |

| 4           | 2          | PTD1              | LCD28  | KBI2P1 |         |         |

| 5           | 3          | PTD2              | LCD29  | KBI2P2 |         |         |

| 6           | 4          | PTD3              | LCD30  | KBI2P3 |         |         |

| 7           | 5          | PTD4              | LCD31  | KBI2P4 | TMRCLK1 |         |

| 8           | 6          | PTD5              | LCD32  | KBI2P5 | TMRCLK2 |         |

| 9           | 7          | PTD6              | LCD33  | KBI2P6 |         |         |

| 10          | 8          | PTD7              | LCD34  | KBI2P7 |         |         |

| 11          | 9          | LCD35             | CLKOUT |        |         |         |

| 12          | 10         | PTF0              | LCD36  |        |         |         |

| 13          | 11         | PTF1              | LCD37  |        | EXTRIG  |         |

| 14          | 12         | PTF2              | LCD38  |        | RX3     |         |

| 15          | 13         | PTF3              | LCD39  |        | TX3     |         |

| 16          | 14         | PTF4              | LCD40  |        | AD16    |         |

| 17          | 15         | PTF5              | LCD41  |        | AD17    |         |

| 18          | 16         | PTF6              | LCD42  |        | AD18    |         |

| 19          | 17         | PTF7              | LCD43  |        | AD19    |         |

| 20          | 18         | V <sub>DDA</sub>  |        |        |         |         |

| 21          | 19         | V <sub>REFH</sub> |        |        |         |         |

| 22          |            | DADP0             |        |        |         |         |

| 23          |            | DADM0             |        |        |         |         |

| 24          |            | AD4               |        |        |         |         |

| 25          | 20         | DADP1             |        |        |         |         |

| 26          | 21         | DADM1             |        |        |         |         |

| 27          | 22         | AD5               |        |        |         |         |

| 28          | 23         | DADP2             |        |        |         |         |

| 29          | 24         | DADM2             |        |        |         |         |

| 30          | 25         | AD6               |        |        |         |         |

| 31          | _          | DADP3             |        |        |         |         |

| 32          | _          | DADM3             |        |        |         |         |

#### Table 4. MCF51EM256 Series Package Pin Assignments

#### MCF51EM256 Series ColdFire Microcontroller Data Sheet, Rev.3

\_\_\_\_\_

#### MCF51EM256 Series Configurations

| 100<br>LQFP     | 80<br>LQFP      | Default Function | ALT1   | ALT2      | ALT3      | Comment                                                                                                         |

|-----------------|-----------------|------------------|--------|-----------|-----------|-----------------------------------------------------------------------------------------------------------------|

| 58              | 47              | PTB4/RGPIO12     | SCL    | PRACMP2P2 |           | RGPIO_ENB is used to select                                                                                     |

| 59              | 48              | PTB5/RGPIO13     | SDA    | PRACMP2P3 |           | between standard GPIO and RGPIO                                                                                 |

| 60              | —               | PTE3             | MOSI3  | MISO3     |           |                                                                                                                 |

| 61              | —               | PTE4             | MISO3  | MOSI3     |           | Open Drain                                                                                                      |

| 62              | —               | PTE5             | SCLK3  |           |           | Open Drain                                                                                                      |

| 63              | —               | PTE6             | SS3    | TX2       |           | Open Drain                                                                                                      |

| 64              | 49              | PTB6/RGPIO14     | KBI1P4 | TMRCLK1   | AD14      | RGPIO_ENB is used to select                                                                                     |

| 65              | 50              | PTB7/RGPIO15     | KBI1P5 | TMRCLK2   | AD15      | between standard GPIO and RGPIO                                                                                 |

| 66              | 51              | RESET            |        |           |           | This pin is an open drain device<br>and has an internal pullup. There is<br>no clamp diode to V <sub>DD</sub> . |

| 67              | 52              | PTC0             | KBI1P6 | EXTAL2    | RX3       |                                                                                                                 |

| 68              | 53              | PTC1             | KBI1P7 | XTAL2     | ТХ3       |                                                                                                                 |

| 69              | 54              | BKGD/MS          | PTC2   |           |           | This pin has an internal pullup.<br>PTC2 can only be programmed as an output.                                   |

| 70 <sup>1</sup> | 55 <sup>1</sup> | PTC3             | LCD0   | PRACMP10  |           |                                                                                                                 |

| 71 <sup>1</sup> | 56 <sup>1</sup> | PTC4             | LCD1   | PRACMP2O  |           |                                                                                                                 |

| 72 <sup>1</sup> | 57 <sup>1</sup> | PTC5             | LCD2   |           | PRACMP1P4 |                                                                                                                 |

| 73 <sup>1</sup> | 58 <sup>1</sup> | PTC6             | LCD3   |           | PRACMP2P4 |                                                                                                                 |

| 74 <sup>1</sup> | 59 <sup>1</sup> | PTC7             | LCD4   |           |           |                                                                                                                 |

| 75 <sup>1</sup> | 60 <sup>1</sup> | PTE7             | LCD5   |           |           |                                                                                                                 |

| 76 <sup>1</sup> | 61 <sup>1</sup> | LCD6             | MOSI2  |           |           |                                                                                                                 |

| 77 <sup>1</sup> | 62 <sup>1</sup> | LCD7             | MISO2  |           |           |                                                                                                                 |

| 78 <sup>1</sup> | 63 <sup>1</sup> | LCD8             | SCLK2  |           |           |                                                                                                                 |

| 79 <sup>1</sup> | 64 <sup>1</sup> | LCD9             | SS2    |           |           |                                                                                                                 |

| 80              | 65              | LCD10            |        |           |           |                                                                                                                 |

| 81              | 66              | LCD11            |        |           |           |                                                                                                                 |

| 82              | 67              | LCD12            |        |           |           |                                                                                                                 |

| 83              | 68              | LCD13            |        |           |           |                                                                                                                 |

| 84              | 69              | LCD14            |        |           |           |                                                                                                                 |

| 85              | 70              | LCD15            |        |           |           |                                                                                                                 |

| 86              | —               | LCD16            |        |           |           |                                                                                                                 |

| 80<br>LQFP | Default Function                | ALT1                                                                                                                                                                                                                                                                                                                                                                                  | ALT2                                                                 | ALT3                                                                     | Comment                                    |

|------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------|

| _          | LCD17                           |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                                                                          |                                            |

|            | LCD18                           |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                                                                          |                                            |

|            | LCD19                           |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                                                                          |                                            |

|            | LCD20                           |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                                                                          |                                            |

| 71         | LCD21                           |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                                                                          |                                            |

| 72         | LCD22                           |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                                                                          |                                            |

| 73         | LCD23                           |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                                                                          |                                            |

| 74         | LCD24                           |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                                                                          |                                            |

| 75         | V <sub>SS</sub>                 |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                                                                          |                                            |

| 76         | VLL3                            |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                                                                          |                                            |

| 77         | VLL2                            |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                                                                          |                                            |

| 78         | VLL1                            |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                                                                          |                                            |

| 79         | VCAP2                           |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                                                                          |                                            |

| 80         | VCAP1                           |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                                                                          |                                            |

|            | LQFP 71 72 73 74 75 76 77 78 79 | LQFP         Default Function           —         LCD17           —         LCD18           —         LCD19           —         LCD20           71         LCD21           72         LCD22           73         LCD23           74         LCD24           75         V <sub>SS</sub> 76         VLL3           77         VLL2           78         VLL1           79         VCAP2 | LQFP         Default Punction         ALT1           —         LCD17 | LQFP         Derault Function         ALT1         ALT2            LCD17 | LQFPDefault FunctionALTALT2ALT3-LCD17 </td |

Table 4. MCF51EM256 Series Package Pin Assignments (continued)

<sup>1</sup> These pins that are shared with the LCD are open-drain by default if not used as LCD pins. To configure this pins as full complementary drive outputs, you must have the LCD modules bits configured as follow: FCDEN =1, VSUPPLY = 11 and RVEN = 0. The Input levels and internal pullup resistors are referenced to VLL3. Referer to the LCD chapter for further information.

## 2 Electrical Characteristics

This section contains electrical specification tables and reference timing diagrams for the MCF51EM256/128 series microcontrollers, including detailed information on power considerations, DC/AC electrical characteristics, and AC timing specifications.

The electrical specifications are preliminary and are from previous designs or design simulations. These specifications may not be fully tested or guaranteed at this early stage of the product life cycle. These specifications will, however, be met for production silicon. Finalized specifications will be published after complete characterization and device qualifications have been completed.

#### NOTE

The parameters specified in this data sheet supersede any values found in the module specifications.

## 2.1 Parameter Classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding the following classification is used and the parameters are tagged accordingly in the tables where appropriate:

#### Table 5. Parameter Classifications

| Р | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| с | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| т | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

#### NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

## 2.2 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table 6 may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this section.

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for instance, either  $V_{SS}$  or  $V_{DD}$ ).

| Rating                                                                                                                                          | Symbol           | Value                         | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------|------|

| Supply voltage                                                                                                                                  | V <sub>DD</sub>  | -0.3 to 4.0                   | V    |

| Input voltage                                                                                                                                   | V <sub>In</sub>  | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Instantaneous maximum current<br>Single pin limit (applies to all port pins except PTB1<br>and PTB3) <sup>1</sup> , <sup>2</sup> , <sup>3</sup> | I <sub>D</sub>   | ±25                           | mA   |

| Instantaneous maximum current<br>Single pin limit (applies to PTB1 and PTB3) <sup>4</sup> , <sup>5</sup> , <sup>6</sup>                         | ۱ <sub>D</sub>   | ±50                           | mA   |

| Maximum current into V <sub>DD</sub>                                                                                                            | I <sub>DD</sub>  | 120                           | mA   |

| Storage temperature                                                                                                                             | ⊤ <sub>stg</sub> | -55 to 150                    | °C   |

Table 6. Absolute Maximum Ratings

<sup>1</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive (V<sub>DD</sub>) and negative (V<sub>SS</sub>) clamp voltages, then use the larger of the two resistance values.

$^2\,$  All functional non-supply pins are internally clamped to V\_{SS} and V\_{DD}

- <sup>3</sup> Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if the clock rate is very low which would reduce overall power consumption.

- <sup>4</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive (V<sub>DD</sub>) and negative (V<sub>SS</sub>) clamp voltages, then use the larger of the two resistance values.

- $^{5}$  All functional non-supply pins are internally clamped to V<sub>SS</sub> and V<sub>DD</sub>.

- <sup>6</sup> Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if the clock rate is very low which would reduce overall power consumption.

### 2.3 Thermal Characteristics

This section provides information about operating temperature range, power dissipation, and package thermal resistance. Power dissipation on I/O pins is usually small compared to the power dissipation in on-chip logic and it is user-determined rather than being controlled by the MCU design. In order to take  $P_{I/O}$  into account in power calculations, determine the difference between actual pin voltage and  $V_{SS}$  or  $V_{DD}$  and multiply by the pin current for each I/O pin. Except in cases of unusually high pin current (heavy loads), the difference between pin voltage and  $V_{SS}$  or  $V_{DD}$  will be very small.

| Rating                                                                             | Symbol          | Value                | Unit |

|------------------------------------------------------------------------------------|-----------------|----------------------|------|

| Operating temperature range (packaged)                                             | T <sub>A</sub>  | -40 to 85            | °C   |

| Maximum junction temperature                                                       | T <sub>JM</sub> | 95                   | °C   |

| Thermal resistance <sup>1,2,3,4</sup><br>100-pin LQFP<br>80-pin LQFP<br>1s<br>2s2p | θ <sub>JA</sub> | 54<br>42<br>55<br>42 | °C/W |

| Table 7. | Thermal | Characteristics |

|----------|---------|-----------------|

|----------|---------|-----------------|

Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- <sup>2</sup> Junction to Ambient Natural Convection

- <sup>3</sup> 1s Single layer board, one signal layer

<sup>4</sup> 2s2p — Four layers board, two signal and two power layers

The average chip-junction temperature  $(T_J)$  in °C can be obtained from:

| Num | Rating                                     | Symbol           | Min   | Max | Unit |

|-----|--------------------------------------------|------------------|-------|-----|------|

| 1   | Human Body Model (HBM)                     | V <sub>HBM</sub> | ±2000 | _   | V    |

| 2   | Machine Model (MM)                         | V <sub>MM</sub>  | ±200  | _   | V    |

| 3   | Charge Device Model (CDM)                  | V <sub>CDM</sub> | ±500  | _   | V    |

| 4   | Latch-up Current at T <sub>A</sub> = 85 °C | I <sub>LAT</sub> | ±100  | _   | mA   |

Table 9. ESD and Latch-Up Protection Characteristics

## 2.5 DC Characteristics

This section includes information about power supply requirements, I/O pin characteristics, and power supply current in various operating modes.

| Num | С   |                        | Parameter                                                                                                                                                                                                                                                 |                  | Min                   | Typical <sup>1</sup> | Max  | Unit |

|-----|-----|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|----------------------|------|------|

|     |     | Operating              | Digital supply — 50 MHz operation                                                                                                                                                                                                                         | V <sub>DD</sub>  | 2.5                   | —                    | 3.6  |      |

| 1   | Ρ   | voltage                | Digital supply <sup>2</sup> — 20 MHz maximum operation                                                                                                                                                                                                    | V <sub>DD</sub>  | 1.8                   | _                    | 3.6  | V    |

| 2   | Ρ   | Analog supply          |                                                                                                                                                                                                                                                           | V <sub>DDA</sub> | 1.8                   |                      | 3.6  | V    |

| 3   | D   | Battery supply         |                                                                                                                                                                                                                                                           | V <sub>BAT</sub> | 2.2                   | 3                    | 3.3  | V    |

| 4   | Ρ   | Bandgap volta          | ge reference <sup>3</sup>                                                                                                                                                                                                                                 | V <sub>BG</sub>  | 1.15                  | 1.17                 | 1.18 | V    |

|     | С   | Output high            | $\label{eq:ptau} \begin{split} & PTA[7{:}0],  PTB[7{:}0],  PTC[2{:}0],  PTE[6{:}0], \\ & low-drive strength. \\ & V_{DD} \geq 1.8   V,  I_{Load} = -0.6   mA \\ & PTA[7{:}0],  PTB[7{:}0],  PTC[2{:}0],  PTE[6{:}0], \end{split}$                         |                  |                       |                      |      |      |

| 5   | Ρ   | voltage                | high-drive strength. $V_{DD} \ge 2.7 \text{ V}, \text{ I}_{Load} = -10 \text{ mA}$                                                                                                                                                                        | V <sub>OH</sub>  | V <sub>DD</sub> – 0.5 | _                    | _    | V    |

|     | с   |                        | $\label{eq:ptau} \begin{array}{l} \mbox{PTA[7:0], PTB[7:0], PTC[2:0], PTE[6:0],} \\ \mbox{high-drive strength.} \\ \mbox{V}_{DD} \geq 1.8 \mbox{ V, } I_{Load} = -3 \mbox{ mA} \end{array}$                                                               |                  |                       |                      |      |      |

|     | С   |                        | $\label{eq:ptc:response} \begin{array}{l} \mbox{PTC[7:3], PTD[7:0], PTE7, PTF[7:0],} \\ \mbox{LCD35/CLKOUT, MOSI2, MISO2,} \\ \mbox{SCK2, SS2, low drive strength.} \\ \mbox{VDD} \geq 1.8 \ \mbox{V, } \ \mbox{I}_{Load} = -0.5 \ \mbox{mA} \end{array}$ |                  |                       |                      |      |      |

| 6   | 6 P | Output high<br>voltage | $\label{eq:ptc} \begin{array}{l} \mbox{PTC[7:3], PTD[7:0], PTE7, PTF[7:0],} \\ \mbox{LCD35/CLKOUT, MOSI2, MISO2,} \\ \mbox{SCK2, SS2, high-drive strength.} \\ \mbox{V}_{DD} \geq 2.7 \mbox{ V, } \mbox{I}_{Load} = -3 \mbox{ mA} \end{array}$            | V <sub>OH</sub>  | V <sub>DD</sub> – 0.5 | _                    | _    | v    |

| С   | С   |                        | $\label{eq:ptc:response} \begin{array}{l} \mbox{PTC[7:3], PTD[7:0], PTE7, PTF[7:0],} \\ \mbox{LCD35/CLKOUT, MOSI2, MISO2,} \\ \mbox{SCK2, SS2, high-drive strength.} \\ \mbox{V}_{DD} \geq 1.8 \mbox{ V, } I_{Load} = -1 \mbox{ mA} \end{array}$          |                  |                       |                      |      |      |

| 7   | D   | Output high<br>current | Max total I <sub>OH</sub> for all ports                                                                                                                                                                                                                   | I <sub>OHT</sub> | —                     | _                    | 100  | mA   |

#### Table 10. DC Characteristics

| Num | с | Parame                                                                                                                                             | ter                         | Symbol               | V <sub>DD</sub> (V) | Typical <sup>1</sup> | Мах | Unit | Temp<br>(°C)   |

|-----|---|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------|---------------------|----------------------|-----|------|----------------|

|     | Р |                                                                                                                                                    | 25.165 MHz                  |                      |                     | 66.2                 | 100 |      |                |

| 4   | Т | Run supply current                                                                                                                                 | 20 MHz                      |                      | 0                   | 55.3                 | —   |      | -40 to         |

| 1   | Т | FEI mode, all modules on                                                                                                                           | 8 MHz                       | RI <sub>DD</sub>     | 3                   | 23.9                 | _   | mA   | 85°C           |

|     | Т |                                                                                                                                                    | 1 MHz                       |                      |                     | 4.56                 | _   |      |                |

|     | С |                                                                                                                                                    | 25.165 MHz                  |                      |                     | 55.1                 | 56  |      |                |

| 2   | Т | Run supply current<br>FEI mode, all                                                                                                                | 20 MHz                      | ы                    | 3                   | 46.6                 | —   | mA   | -40 to         |

| 2   | Т | modules off                                                                                                                                        | 8 MHz                       | RI <sub>DD</sub>     | 5                   | 19.9                 | —   |      | 85°C           |

|     | Т |                                                                                                                                                    | 1 MHz                       |                      |                     | 3.92                 | _   |      |                |

|     | Т | Run supply current                                                                                                                                 | 16 kHz FBILP                |                      |                     | 239                  | —   |      |                |

| 3   | т | LPS=0, all modules off                                                                                                                             | 16 kHz<br>FBELP             | RI <sub>DD</sub>     | 3                   | 249                  | _   | μΑ   | _              |

| 4   | т | Run supply current<br>LPS = 1, all<br>modules off,<br>running from flash                                                                           | 16 kHz<br>FBELP             | RI <sub>DD</sub>     | 3                   | 50                   | _   | μΑ   | _              |

|     | С | Wait mode supply                                                                                                                                   | 25.165 MHz                  |                      |                     | 51.1                 | 69  |      |                |

| F   | Т | current                                                                                                                                            | 20 MHz                      | 14/1                 | 3                   | 42.6                 | _   |      | -40 to         |

| 5   | Т | FEI mode, all                                                                                                                                      | 8 MHz                       | WI <sub>DD</sub>     | 5                   | 18.8                 | _   | mA   | 85°C           |

|     | Т | modules off                                                                                                                                        | 1                           |                      |                     | 3.69                 | —   |      |                |

| 6   | т | Wait mode supply current<br>LPRS = 1, all mods off                                                                                                 |                             | WI <sub>DD</sub>     | 3                   | 1                    | _   | μA   | _              |

| 7   | Р | Stop2 mode supply c                                                                                                                                | urropt                      | S2I <sub>DD</sub>    | 3                   | 0.576                | 30  | μA   | -40 to         |

| 1   | С |                                                                                                                                                    | unent                       | 00                   | 2                   | 0.570                | 16  |      | 85°C           |

| 8   | Р | Stop3 mode supply c                                                                                                                                | urropt                      | 621                  | 3                   | 1.05                 | 45  |      | –40 to<br>85°C |

|     | С |                                                                                                                                                    | unent                       | S3I <sub>DD</sub>    | 2                   | 1.05                 | 27  | μΑ   |                |

| 9   | т | LVD adder to stop3, s<br>LVDSE = 1)                                                                                                                | stop2 (LVDE =               | S3I <sub>DDLVD</sub> | 3                   | 120                  | _   | μA   | _              |

|     |   | Voltago reference                                                                                                                                  | Low power<br>mode           |                      |                     | 90                   |     |      |                |

| 10  | Т | Voltage reference<br>adder to stop3                                                                                                                | Tight<br>regulation<br>mode | S3I <sub>DDLVD</sub> | 3                   | 270                  | _   | μA   | -              |

| 11  | т | PRACMP adder to                                                                                                                                    | PRG disabled                | 601                  | 3                   | 13                   |     |      |                |

| 11  |   | stop3                                                                                                                                              | PRG enabled                 | S3I <sub>DDLVD</sub> | 3                   | 29                   |     | μA   |                |

| 12  | т | LCD adder to stop3, stop2, VIREG<br>enabled, 1/4 duty cycle, 4x39<br>configuration for 156 segments,<br>32Hz frame rate, no LCD glass<br>connected |                             | S3I <sub>DDLVD</sub> | 3                   | 1.3                  | _   | μΑ   | _              |

| 13  | с | Adder to stop3 for ose<br>(ERCLKEN =1 and E                                                                                                        |                             | S3I <sub>DDOSC</sub> | 3                   | 5                    |     | μA   | _              |

#### Table 11. Supply Current Characteristics

| Num | С | Parameter                            | Symbol              | V <sub>DD</sub> (V) | Typical <sup>1</sup> | Мах | Unit | <b>Тетр</b><br>(°С) |

|-----|---|--------------------------------------|---------------------|---------------------|----------------------|-----|------|---------------------|

| 14  | Ρ | IRTC supply current <sup>3,4,5</sup> | I <sub>DD-BAT</sub> |                     | 1.5                  | 5   | μA   | –40 to<br>85°C      |

<sup>1</sup> Typicals are measured at 25 °C.

<sup>2</sup> Values given under the following conditions: low range operation (RANGE = 0), low power mode (HGO = 0).

$^3\,$  This is the current consumed when the IRTC is being powered by the V\_{BAT}

<sup>4</sup> The IRTC power source depends on the MCU configuration and V<sub>DD</sub> voltage level. Refer to reference manual for further information.

<sup>5</sup> The IRTC current consumption includes the IRTC XOSC1.

| Num | Charact<br>eristic          | Conditions                                                                                                 | Symb              | Min               | Typ <sup>1</sup> | Max               | Unit | Comment                    |

|-----|-----------------------------|------------------------------------------------------------------------------------------------------------|-------------------|-------------------|------------------|-------------------|------|----------------------------|

| 5   | Ref<br>Voltage<br>Low       |                                                                                                            | V <sub>REFL</sub> | V <sub>SSA</sub>  | V <sub>SSA</sub> | V <sub>SSA</sub>  | V    |                            |

| 6   | Input<br>Voltage            |                                                                                                            | V <sub>ADIN</sub> | V <sub>REFL</sub> | _                | V <sub>REFH</sub> | V    |                            |

| 7   | Input<br>Capacit<br>ance    | 16-bit modes<br>8/10/12-bit modes                                                                          | C <sub>ADIN</sub> | _                 | 8<br>4           | 10<br>5           | pF   |                            |

| 8   | Input<br>Resista<br>nce     |                                                                                                            | R <sub>ADIN</sub> | _                 | 2                | 5                 | kΩ   |                            |

| 9   |                             | 16 bit modes<br>f <sub>ADCK</sub> > 8MHz<br>4MHz < f <sub>ADCK</sub> < 8MHz<br>f <sub>ADCK</sub> < 4MHz    |                   |                   | —                | 0.5<br>1<br>2     |      |                            |

| 10  | Analog<br>Source<br>Resista | 13/12 bit modes<br>f <sub>ADCK</sub> > 8MHz<br>4MHz < f <sub>ADCK</sub> < 8MHz<br>f <sub>ADCK</sub> < 4MHz | R <sub>AS</sub>   |                   |                  | 1<br>2<br>5       | kΩ   | External to MCU<br>Assumes |

| 11  | nce                         | 11/10 bit modes<br>f <sub>ADCK</sub> > 8MHz<br>4MHz < f <sub>ADCK</sub> < 8MHz<br>f <sub>ADCK</sub> < 4MHz |                   |                   |                  | 2<br>5<br>10      |      | ADLSMP=0                   |

| 12  |                             | 9/8 bit modes<br>f <sub>ADCK</sub> > 8MHz<br>f <sub>ADCK</sub> < 8MHz                                      |                   | _                 | _                | 5<br>10           |      |                            |

| 13  | ADC                         | ADLPC = 0, ADHSC = 1                                                                                       |                   | 1.0               | _                | 8                 |      |                            |

| 14  | Convers<br>ion<br>Clock     | ADLPC = 0, ADHSC = 0                                                                                       | fadck             | 1.0               | _                | 5                 | MHz  |                            |

| 15  | Freq.                       | ADLPC = 1, ADHSC = 0                                                                                       |                   | 1.0               | _                | 2.5               |      |                            |

#### Table 13. 16-bit ADC Operating Conditions

<sup>1</sup> Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>2</sup> DC potential difference.

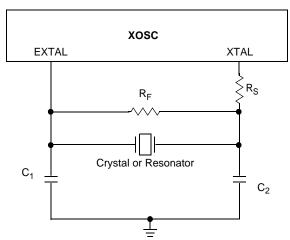

## 2.9 External Oscillator (XOSC) Characteristics

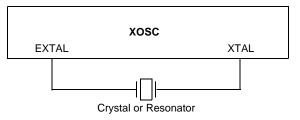

Reference Figure 11 and Figure 12 for crystal or resonator circuits. XOSC1 operates only in low power low range mode. XOSC2 operates in all the power and range modes.

| Num | С | Characteristic                                                                                                                                                                                                                                                 | Symbol                         | Min          | Typ <sup>1</sup>       | Max                   | Unit              |

|-----|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------|------------------------|-----------------------|-------------------|

| 1   | С | Oscillator crystal or resonator (EREFS = 1, ERCLKEN = 1)<br>Low range (RANGE = 0)<br>High range (RANGE = 1), high gain (HGO = 1)<br>High range (RANGE = 1), low power (HGO = 0)                                                                                |                                | 32<br>1<br>1 |                        | 38.4<br>16<br>8       | kHz<br>MHz<br>MHz |

| 2   | D | Load capacitors<br>Low range (RANGE=0), low power (HGO = 0)<br>Other oscillator settings                                                                                                                                                                       | C <sub>1,</sub> C <sub>2</sub> |              | See N<br>See N         |                       |                   |

| 3   | D | Feedback resistor<br>Low range, low power (RANGE = 0, HGO = 0) <sup>2</sup><br>Low range, high gain (RANGE = 0, HGO = 1)<br>High range (RANGE = 1, HGO = X)                                                                                                    | ĸ <sub>F</sub>                 |              | <br>10<br>1            |                       | MΩ                |

| 4   | D | Series resistor —<br>Low range, low power (RANGE = 0, HGO = 0) <sup>2</sup><br>Low range, high gain (RANGE = 0, HGO = 1)<br>High range, low power (RANGE = 1, HGO = 0)<br>High range, high gain (RANGE = 1, HGO = 1)<br>$\geq 8 \text{ MHz}$<br>4 MHz<br>1 MHz | R <sub>S</sub>                 |              | <br>100<br>0<br>0<br>0 | <br><br>0<br>10<br>20 | kΩ                |

| 5   | т | Crystal start-up time <sup>4</sup><br>Low range, low powe<br>Low range, high powe<br>High range, low powe<br>High range, high powe                                                                                                                             |                                | <br>         | 600<br>400<br>5<br>15  | <br>                  | ms                |

| 6   | D | Square wave input clock frequency (EREFS = 0, ERCLKEN = 1)<br>FEE mode<br>FBE or FBELP mode                                                                                                                                                                    | exiai                          | 0.03125<br>0 |                        | 50.33<br>50.33        | MHz<br>MHz        |

Table 16. XOSC Specifications (Temperature Range = -40 to 85 °C Ambient)

<sup>1</sup> Data in Typical column was characterized at 3.0 V, 25 °C or is typical recommended value.

<sup>2</sup> Load capacitors ( $C_1$ , $C_2$ ), feedback resistor ( $R_F$ ) and series resistor ( $R_S$ ) are incorporated internally when RANGE = HGO = 0.

<sup>3</sup> See crystal or resonator manufacturer's recommendation.

<sup>4</sup> Proper PC board layout procedures must be followed to achieve specifications.

Figure 12. Typical Crystal or Resonator Circuit: Low Range/Low Gain

### 2.10 Internal Clock Source (ICS) Characteristics

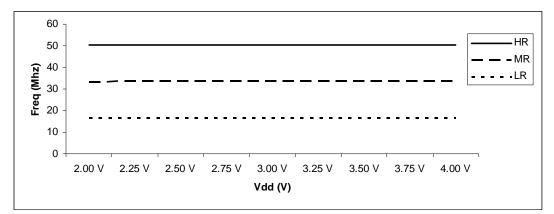

Table 17. ICS Frequency Specifications (Temperature Range = -40 to 85 °C Ambient)

| Num | С | Charac                                                                                                | teristic              | Symbol                   | Min   | Typical <sup>1</sup> | Max   | Unit              |

|-----|---|-------------------------------------------------------------------------------------------------------|-----------------------|--------------------------|-------|----------------------|-------|-------------------|

| 1   | Ρ | Average internal reference frequency — factory trimmed<br>at $V_{DD} = 3.6$ V and temperature = 25 °C |                       | f <sub>int_ft</sub>      | _     | 32.768               | _     | kHz               |

| 2   | Ρ | Internal reference frequency —                                                                        | user trimmed          | f <sub>int_ut</sub>      | 31.25 | —                    | 39.06 | kHz               |

| 3   | Т | Internal reference start-up time                                                                      |                       | t <sub>IRST</sub>        | _     | 60                   | 100   | μS                |

|     | Ρ |                                                                                                       | Low range (DRS = 00)  |                          | 16    | —                    | 20    |                   |

| 4   | С | DCO output frequency range<br>— trimmed <sup>2</sup>                                                  | Mid range (DRS = 01)  | f <sub>dco_u</sub>       | 32    | —                    | 40    | MHz               |

|     | Ρ |                                                                                                       | High range (DRS = 10) |                          | 48    |                      | 60    |                   |

|     | Ρ | DCO output frequency <sup>2</sup>                                                                     | Low range (DRS = 00)  |                          | _     | 19.92                | _     |                   |

| 5   | Ρ | Reference = 32768 Hz                                                                                  | Mid range (DRS = 01)  | f <sub>dco_DMX32</sub>   | _     | 39.85                | _     | MHz               |

|     | Ρ | and DMX32 = 1                                                                                         | High range (DRS = 10) |                          | _     | 59.77                |       |                   |

| 6   | С | Resolution of trimmed DCO output frequency at fixed voltage and temperature (using FTRIM)             |                       | $\Delta f_{dco\_res\_t}$ | _     | ±0.1                 | ±0.2  | %f <sub>dco</sub> |

| 7   | С | Resolution of trimmed DCO outp<br>and temperature (not using FTR                                      |                       | $\Delta f_{dco\_res\_t}$ | _     | ±0.2                 | ±0.4  | %f <sub>dco</sub> |

#### MCF51EM256 Series ColdFire Microcontroller Data Sheet, Rev.3

## 2.11 LCD Specifications

| Ν  | С   | Characteristic                               | Symbo                  | ol Min           | Typical        | Max               | Unit                   |  |

|----|-----|----------------------------------------------|------------------------|------------------|----------------|-------------------|------------------------|--|

| 1  | D   | LCD frame frequency                          | f <sub>Frame</sub>     | 28               | 30             | 58                | Hz                     |  |

| 2  | D   | LCD charge pump capacitance                  | C <sub>LCD</sub>       |                  | 100            | 100               | nF                     |  |

| 3  | D   | LCD bypass capacitance                       | C <sub>BYLC</sub>      | D                | 100            | 100               | nF                     |  |

| 4  | D   | LCD glass capacitance                        | C <sub>glass</sub>     | ;                | 2000           | 8000              | pF                     |  |

| 5  | D   | HRefSel                                      | = 0                    | .89              | 1.00           | 1.15              | v                      |  |

| 6  | D   | V <sub>IREG</sub> HRefSel                    | = 1 V <sub>IREG</sub>  | 1.49             | 1.67           | 1.85 <sup>1</sup> | v                      |  |

| 7  | D   | V <sub>IREG</sub> trim resolution            | $\Delta_{RTRIN}$       | <sub>Л</sub> 1.5 |                |                   | %<br>V <sub>IREG</sub> |  |

| 8  | D   | HRefSel                                      | = 0                    |                  |                | 0.1               | v                      |  |

| 0  | 8 U | V <sub>IREG</sub> ripple HRefSel             | = 1                    |                  |                | 0.15              |                        |  |

| 9  | D   | V <sub>IREG</sub> current adder RVEN         | = 1 I <sub>VIREG</sub> | i —              | 1 <sup>2</sup> |                   | μA                     |  |

| 10 | D   | V <sub>LCD</sub> buffered adder <sup>3</sup> | I <sub>Buff</sub>      | _                | 1              |                   | μΑ                     |  |

Table 18. LCD Electricals, 3 V Glass

<sup>1</sup>  $V_{IREG}$  Max can not exceed  $V_{DD} - 0.15$  V

<sup>2</sup> 2000 pF Load LCD, frame frequency = 32 Hz

<sup>3</sup> VSUPPLY = 10, BYPASS = 0

### 2.12 AC Characteristics

This section describes AC timing characteristics for each peripheral system.

## 2.13 VREF Characteristics

| Num | С      | Characteristic                                           | Symbol            | Min                                | Typical   | Мах           | Unit   |

|-----|--------|----------------------------------------------------------|-------------------|------------------------------------|-----------|---------------|--------|

| 1   |        | Supply voltage                                           | V <sub>DDAD</sub> | 1.80                               | _         | 3.60          | V      |

| 2   | _      | Operating temperature range                              | T <sub>op</sub>   | -40                                | _         | 105           | °C     |

| 3   | D      | Load capability                                          | I <sub>load</sub> | _                                  | _         | 10            | mA     |

| 4   | C<br>P | Voltage reference output<br>untrimmed<br>factory trimmed | nLi U             | 1.070<br>1.04                      | <br>1.150 | 1.202<br>1.17 | V<br>V |

| 5   | D      | Load regulation<br>mode = 10, I <sub>load</sub> = 1 mA   |                   | 20                                 | _         | 100           | μV/mA  |

| 6   | т      | Line regulation (power supply<br>rejection)<br>DC<br>AC  |                   | ±0.1 from room temp voltage<br>—60 |           | mV<br>dB      |        |

| 7   | Т      | Bandgap only (mode = 00)                                 | I <sub>BG</sub>   | _                                  | 72        | _             | μΑ     |

| 8   | С      | Low power mode (mode = 01)                               | I <sub>LP</sub>   | _                                  | 90        | 125           | μΑ     |

| 9   | Т      | Tight regulation mode (mode =10)                         | I <sub>TR</sub>   | _                                  | 0.27      | _             | mA     |

|  | Table 21. | VREF | Electrical | Specifications |

|--|-----------|------|------------|----------------|

|--|-----------|------|------------|----------------|

## 2.14 SPI Characteristics

Table 22 and Figure 19 through Figure 22 describe the timing requirements for the SPI system.

**Mechanical Outline Drawings**

## 3.2 100-pin LQFP Package

## 4 Revision History

#### Table 24. Revision History

| Revision | Date       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | 10/15/2009 | Initial public release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2        | 4/29/2010  | Updated teh descriptions of SPI in the Table 2.<br>Changed the FSPIx to SPI16 to keep the term in accordance.<br>Updated Figure 4 to Figure 8.<br>Updated WI <sub>DD</sub> , S2I <sub>DD</sub> , S3I <sub>DD</sub> in the Table 11.<br>Updated the ADC characteristics in the Table 13 to Table 15.<br>Updated description of XOSC in the Section 2.9, "External Oscillator (XOSC)<br>Characteristics."<br>Updated t <sub>CSTL</sub> in the Table 16.<br>Updated the classification of IBG and ITR to T and added Voltage reference output<br>(factory trimmed) in the Table 21.<br>Update SPI data in the Table 22. |

| 3        | 8/9/2010   | Updated the V <sub>DD</sub> at 20 MHz maximum operation to 3.6 V.<br>Updated the RI <sub>DD</sub> (at Run supply current FEI mode, all module on), S2I <sub>DD</sub> and S3I <sub>DD</sub> at 3 V, S3I <sub>DDLVD</sub> in the Table 11.<br>Updated ENOB at 16 bit single-ended mode in the Table 14.                                                                                                                                                                                                                                                                                                                |