# E·XFL

#### AMD Xilinx - XC2V80-4FGG256I Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 128                                                         |

| Number of Logic Elements/Cells |                                                             |

| Total RAM Bits                 | 147456                                                      |

| Number of I/O                  | 120                                                         |

| Number of Gates                | 80000                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                          |

| Package / Case                 | 256-BGA                                                     |

| Supplier Device Package        | 256-FBGA (17x17)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2v80-4fgg256i |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Device   |                 | CLB<br>(1 CLB = 4 slices = Max 128 bits) |        |                                     | SelectF              | AM Blocks         |                    |      |                                |

|----------|-----------------|------------------------------------------|--------|-------------------------------------|----------------------|-------------------|--------------------|------|--------------------------------|

|          | System<br>Gates | Array<br>Row x Col.                      | Slices | Maximum<br>Distributed<br>RAM Kbits | Multiplier<br>Blocks | 18 Kbit<br>Blocks | Max RAM<br>(Kbits) | DCMs | Max I/O<br>Pads <sup>(1)</sup> |

| XC2V40   | 40K             | 8 x 8                                    | 256    | 8                                   | 4                    | 4                 | 72                 | 4    | 88                             |

| XC2V80   | 80K             | 16 x 8                                   | 512    | 16                                  | 8                    | 8                 | 144                | 4    | 120                            |

| XC2V250  | 250K            | 24 x 16                                  | 1,536  | 48                                  | 24                   | 24                | 432                | 8    | 200                            |

| XC2V500  | 500K            | 32 x 24                                  | 3,072  | 96                                  | 32                   | 32                | 576                | 8    | 264                            |

| XC2V1000 | 1M              | 40 x 32                                  | 5,120  | 160                                 | 40                   | 40                | 720                | 8    | 432                            |

| XC2V1500 | 1.5M            | 48 x 40                                  | 7,680  | 240                                 | 48                   | 48                | 864                | 8    | 528                            |

| XC2V2000 | 2M              | 56 x 48                                  | 10,752 | 336                                 | 56                   | 56                | 1,008              | 8    | 624                            |

| XC2V3000 | ЗM              | 64 x 56                                  | 14,336 | 448                                 | 96                   | 96                | 1,728              | 12   | 720                            |

| XC2V4000 | 4M              | 80 x 72                                  | 23,040 | 720                                 | 120                  | 120               | 2,160              | 12   | 912                            |

| XC2V6000 | 6M              | 96 x 88                                  | 33,792 | 1,056                               | 144                  | 144               | 2,592              | 12   | 1,104                          |

| XC2V8000 | 8M              | 112 x 104                                | 46,592 | 1,456                               | 168                  | 168               | 3,024              | 12   | 1,108                          |

#### Table 1: Virtex-II Field-Programmable Gate Array Family Members

Notes:

1. See details in Table 2, "Maximum Number of User I/O Pads".

## **General Description**

The Virtex-II family is a platform FPGA developed for high performance from low-density to high-density designs that are based on IP cores and customized modules. The family delivers complete solutions for telecommunication, wireless, networking, video, and DSP applications, including PCI, LVDS, and DDR interfaces.

The leading-edge 0.15  $\mu$ m / 0.12  $\mu$ m CMOS 8-layer metal process and the Virtex-II architecture are optimized for high speed with low power consumption. Combining a wide variety of flexible features and a large range of densities up to 10 million system gates, the Virtex-II family enhances programmable logic design capabilities and is a powerful alternative to mask-programmed gates arrays. As shown in Table 1, the Virtex-II family comprises 11 members, ranging from 40K to 8M system gates.

### Packaging

Offerings include ball grid array (BGA) packages with 0.80 mm, 1.00 mm, and 1.27 mm pitches. In addition to traditional wire-bond interconnects, flip-chip interconnect is used in some of the BGA offerings. The use of flip-chip interconnect offers more I/Os than is possible in wire-bond versions of the similar packages. Flip-chip construction offers the combination of high pin count with high thermal capacity. Wire-bond packages CS, FG, and BG are optionally availabe in Pb-free versions CSG, FGG, and BGG. See Virtex-II Ordering Examples, page 6.

Table 2 shows the maximum number of user I/Os available. The Virtex-II device/package combination table (Table 6 at the end of this section) details the maximum number of I/Os for each device and package using wire-bond or flip-chip technology.

#### Table 2: Maximum Number of User I/O Pads

| Device   | Wire-Bond | Flip-Chip |

|----------|-----------|-----------|

| XC2V40   | 88        | -         |

| XC2V80   | 120       | -         |

| XC2V250  | 200       | -         |

| XC2V500  | 264       | -         |

| XC2V1000 | 328       | 432       |

| XC2V1500 | 392       | 528       |

| XC2V2000 | -         | 624       |

| XC2V3000 | 516       | 720       |

| XC2V4000 | -         | 912       |

| XC2V6000 | -         | 1,104     |

| XC2V8000 | -         | 1,108     |

|                          |            | Available I/Os |             |             |              |              |              |              |              |              |              |

|--------------------------|------------|----------------|-------------|-------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Package <sup>(1,2)</sup> | XC2V<br>40 | XC2V<br>80     | XC2V<br>250 | XC2V<br>500 | XC2V<br>1000 | XC2V<br>1500 | XC2V<br>2000 | XC2V<br>3000 | XC2V<br>4000 | XC2V<br>6000 | XC2V<br>8000 |

| CS144/CSG144             | 88         | 92             | 92          | -           | -            | -            | -            | -            | -            | -            | -            |

| FG256/FGG256             | 88         | 120            | 172         | 172         | 172          | -            | -            | -            | -            | -            | -            |

| FG456/FGG456             | -          | -              | 200         | 264         | 324          | -            | -            | -            | -            | -            | -            |

| FG676/FGG676             | -          | -              | -           | -           | -            | 392          | 456          | 484          | -            | -            | -            |

| FF896                    | -          | -              | -           | -           | 432          | 528          | 624          | -            | -            | -            | -            |

| FF1152                   | -          | -              | -           | -           | -            | -            | -            | 720          | 824          | 824          | 824          |

| FF1517                   | -          | -              | -           | -           | -            | -            | -            | -            | 912          | 1,104        | 1,108        |

| BG575/BGG575             | -          | -              | -           | -           | 328          | 392          | 408          | -            | -            | -            | -            |

| BG728/BGG728             | -          | -              | -           | -           | -            | -            | -            | 516          | -            | -            | -            |

| BF957                    | -          | -              | -           | -           | -            | -            | 624          | 684          | 684          | 684          | -            |

#### Table 6: Virtex-II Device/Package Combinations and Maximum Number of Available I/Os (Advance Information)

#### Notes:

1. All devices in a particular package are pinout (footprint) compatible. In addition, the FG456/FGG456 and FG676/FGG676 packages are compatible, as are the FF896 and FF1152 packages.

Wire-bond packages CS144, FG256, FG456, FG676, BG575, and BG728 are also available in Pb-free versions CSG144, FGG256, FGG456, FGG676, BGG575, and BGG728. See Virtex-II Ordering Examples for details on how to order.

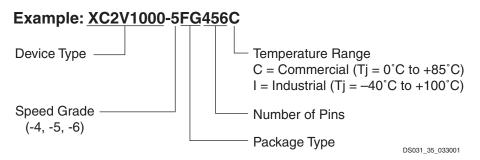

## **Virtex-II Ordering Examples**

## Example: XC2V3000-6BGG728C Device Type - Temperature Range $C = Commercial (Tj = 0^{\circ}C to +85^{\circ}C)$ $I = Industrial (Tj = -40^{\circ}C to +100^{\circ}C)$ Number of Pins Pb-Free Package Package Type

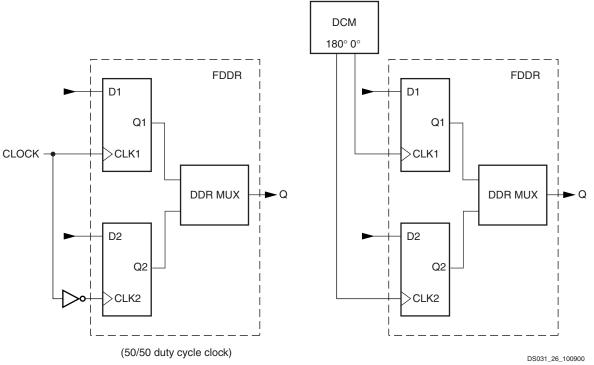

Figure 3: Double Data Rate Registers

The DDR mechanism shown in Figure 3 can be used to mirror a copy of the clock on the output. This is useful for propagating a clock along the data that has an identical delay. It is also useful for multiple clock generation, where there is a unique clock driver for every clock load. Virtex-II devices can produce many copies of a clock with very little skew.

Each group of two registers has a clock enable signal (ICE for the input registers, OCE for the output registers, and TCE for the 3-state registers). The clock enable signals are active High by default. If left unconnected, the clock enable for that storage element defaults to the active state.

Each IOB block has common synchronous or asynchronous set and reset (SR and REV signals).

SR forces the storage element into the state specified by the SRHIGH or SRLOW attribute. SRHIGH forces a logic "1". SRLOW forces a logic "0". When SR is used, a second input (REV) forces the storage element into the opposite state. The reset condition predominates over the set condition. The initial state after configuration or global initialization state is defined by a separate INITO and INIT1 attribute. By default, the SRLOW attribute forces INIT0, and the SRHIGH attribute forces INIT1. For each storage element, the SRHIGH, SRLOW, INITO, and INIT1 attributes are independent. Synchronous or asynchronous set / reset is consistent in an IOB block.

All the control signals have independent polarity. Any inverter placed on a control input is automatically absorbed.

Each register or latch (independent of all other registers or latches) (see Figure 4) can be configured as follows:

- No set or reset

- Synchronous set

- Synchronous reset

- Synchronous set and reset

- Asynchronous set (preset)

- Asynchronous reset (clear)

- Asynchronous set and reset (preset and clear)

The synchronous reset overrides a set, and an asynchronous clear overrides a preset.

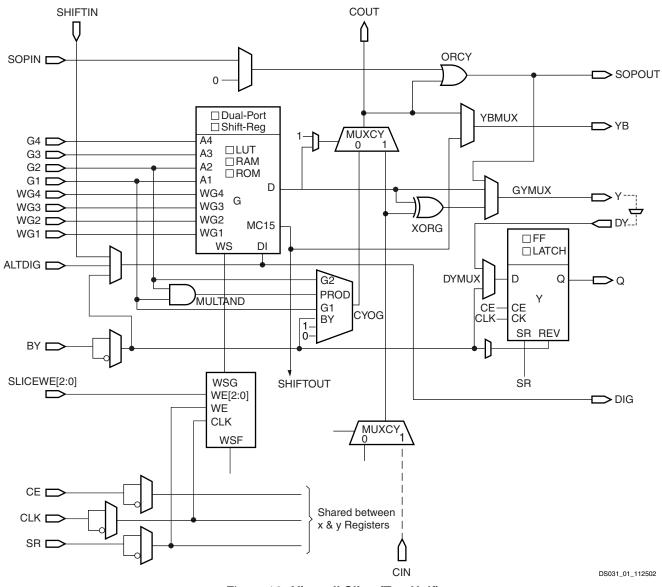

Figure 16: Virtex-II Slice (Top Half)

## 3-State Buffers

#### Introduction

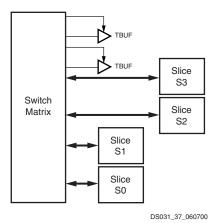

Each Virtex-II CLB contains two 3-state drivers (TBUFs) that can drive on-chip busses. Each 3-state buffer has its own 3-state control pin and its own input pin.

Each of the four slices have access to the two 3-state buffers through the switch matrix, as shown in Figure 27. TBUFs in neighboring CLBs can access slice outputs by direct connects. The outputs of the 3-state buffers drive horizontal routing resources used to implement 3-state busses.

Figure 27: Virtex-II 3-State Buffers

The 3-state buffer logic is implemented using AND-OR logic rather than 3-state drivers, so that timing is more predictable and less load dependant especially with larger devices.

#### Locations / Organization

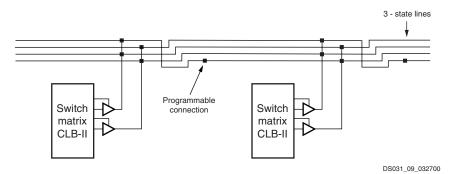

Four horizontal routing resources per CLB are provided for on-chip 3-state busses. Each 3-state buffer has access alternately to two horizontal lines, which can be partitioned as shown in Figure 28. The switch matrices corresponding to SelectRAM memory and multiplier or I/O blocks are skipped.

#### Number of 3-State Buffers

Table 11 shows the number of 3-state buffers available ineach Virtex-II device. The number of 3-state buffers is twicethe number of CLB elements.

| Table | 11: | Virtex-II 3-State Buffers |

|-------|-----|---------------------------|

|-------|-----|---------------------------|

| Device   | 3-State Buffers<br>per Row | Total Number<br>of 3-State Buffers |

|----------|----------------------------|------------------------------------|

| XC2V40   | 16                         | 128                                |

| XC2V80   | 16                         | 256                                |

| XC2V250  | 32                         | 768                                |

| XC2V500  | 48                         | 1,536                              |

| XC2V1000 | 64                         | 2,560                              |

| XC2V1500 | 80                         | 3,840                              |

| XC2V2000 | 96                         | 5,376                              |

| XC2V3000 | 112                        | 7,168                              |

| XC2V4000 | 144                        | 11,520                             |

| XC2V6000 | 176                        | 16,896                             |

| XC2V8000 | 208                        | 23,296                             |

*Figure 28:* **3-State Buffer Connection to Horizontal Lines**

### **CLB/Slice Configurations**

Table 12 summarizes the logic resources in one CLB. All of the CLBs are identical and each CLB or slice can be implemented in one of the configurations listed. Table 13 shows the available resources in all CLBs.

Table 12: Logic Resources in One CLB

| SI | lices | LUTs | Flip-Flops | MULT_ANDs | Arithmetic &<br>Carry-Chains | SOP<br>Chains | Distributed<br>SelectRAM | Shift<br>Registers | TBUF |

|----|-------|------|------------|-----------|------------------------------|---------------|--------------------------|--------------------|------|

|    | 4     | 8    | 8          | 8         | 2                            | 2             | 128 bits                 | 128 bits           | 2    |

DS031\_10\_071602

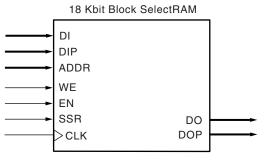

Figure 29: 18 Kbit Block SelectRAM Memory in Single-Port Mode

#### **Dual-Port Configuration**

As a dual-port RAM, each port of block SelectRAM has access to a common 18 Kbit memory resource. These are fully synchronous ports with independent control signals for each port. The data widths of the two ports can be configured independently, providing built-in bus-width conversion.

Table 15 illustrates the different configurations available onports A and B.

If both ports are configured in either 2K x 9-bit, 1K x 18-bit, or 512 x 36-bit configurations, the 18 Kbit block is accessible from port A or B. If both ports are configured in either 16K x 1-bit, 8K x 2-bit. or 4K x 4-bit configurations, the 16 K-bit block is accessible from Port A or Port B. All other configurations result in one port having access to an 18 Kbit memory block and the other port having access to a 16 K-bit subset of the memory block equal to 16 Kbits.

| Port A | 16K x 1  |

|--------|----------|----------|----------|----------|----------|----------|

| Port B | 16K x 1  | 8K x 2   | 4K x 4   | 2K x 9   | 1K x 18  | 512 x 36 |

| Port A | 8K x 2   |          |

| Port B | 8K x 2   | 4K x 4   | 2K x 9   | 1K x 18  | 512 x 36 | ]        |

| Port A | 4K x 4   | 4K x 4   | 4K x 4   | 4K x 4   |          | <u>,</u> |

| Port B | 4K x 4   | 2K x 9   | 1K x 18  | 512 x 36 |          |          |

| Port A | 2K x 9   | 2K x 9   | 2K x 9   |          | 2        |          |

| Port B | 2K x 9   | 1K x 18  | 512 x 36 | ]        |          |          |

| Port A | 1K x 18  | 1K x 18  |          | 2        |          |          |

| Port B | 1K x 18  | 512 x 36 |          |          |          |          |

| Port A | 512 x 36 |          |          |          |          |          |

| Port B | 512 x 36 |          |          |          |          |          |

| Table | 15: | Dual-Port | Mode | Configurations |

|-------|-----|-----------|------|----------------|

|-------|-----|-----------|------|----------------|

## XILINX<sup>®</sup>

## **Creating a Design**

Creating Virtex-II designs is easy with Xilinx Integrated Synthesis Environment (ISE) development systems, which support advanced design capabilities, including ProActive Timing Closure, integrated logic analysis, and the fastest place and route runtimes in the industry. ISE solutions enable designers to get the performance they need, quickly and easily.

As a result of the ongoing cooperative development efforts between Xilinx and EDA Alliance partners, designers can take advantage of the benefits provided by EDA technologies in the programmable logic design process. Xilinx development systems are available in a number of easy to use configurations, collectively known as the ISE Series.

## **ISE Alliance**

The ISE Alliance solution is designed to plug and play within an existing design environment. Built using industry standard data formats and netlists, these stable, flexible products enable Alliance EDA partners to deliver their best design automation capabilities to Xilinx customers, along with the time to market benefits of ProActive Timing Closure.

## **ISE Foundation**

The ISE Foundation solution delivers the benefits of true HDL-based design in a seamlessly integrated design environment. An intuitive project navigator, as well as powerful HDL design and two HDL synthesis tools, ensure that high-quality results are achieved quickly and easily. The ISE Foundation product includes:

- State Diagram entry using Xilinx StateCAD

- Automatic HDL Testbench generation using Xilinx

HDLBencher

- HDL Simulation using ModelSim XE

## **Design Flow**

Virtex-II design flow proceeds as follows:

- Design Entry

- Synthesis

- Implementation

- Verification

Most programmable logic designers iterate through these steps several times in the process of completing a design.

## Design Entry

All Xilinx ISE development systems support the mainstream EDA design entry capabilities, ranging from schematic design to advanced HDL design methodologies. Given the high densities of the Virtex-II family, designs are created most efficiently using HDLs. To further improve their time to market, many Xilinx customers employ incremental, modular, and Intellectual Property (IP) design techniques. When properly used, these techniques further accelerate the logic design process. To enable designers to leverage existing investments in EDA tools, and to ensure high performance design flows, Xilinx jointly develops tools with leading EDA vendors, including:

- Aldec<sup>®</sup>

- Cadence<sup>®</sup>

- Exemplar<sup>®</sup>

- Mentor Graphics<sup>®</sup>

- Model Technology<sup>®</sup>

- Synopsys<sup>®</sup>

- Synplicity<sup>®</sup>

Complete information on Alliance Series partners and their associated design flows is available at <u>www.xilinx.com</u> on the Xilinx Alliance Series web page.

The ISE Foundation product offers schematic entry and HDL design capabilities as part of an integrated design solution - enabling one-stop shopping. These capabilities are powerful, easy to use, and they support the full portfolio of Xilinx programmable logic devices. HDL design capabilities include a color-coded HDL editor with integrated language templates, state diagram entry, and Core generation capabilities.

#### Synthesis

The ISE Alliance product is engineered to support advanced design flows with the industry's best synthesis tools. Advanced design methodologies include:

- Physical Synthesis

- Incremental synthesis

- RTL floorplanning

- Direct physical mapping

The ISE Foundation product seamlessly integrates synthesis capabilities purchased directly from Exemplar, Synopsys, and Synplicity. In addition, it includes the capabilities of Xilinx Synthesis Technology.

A benefit of having two seamlessly integrated synthesis engines within an ISE design flow is the ability to apply alternative sets of optimization techniques on designs, helping to ensure that designers can meet even the toughest timing requirements.

### **Design Implementation**

The ISE Series development systems include Xilinx timing-driven implementation tools, frequently called "place and route" or "fitting" software. This robust suite of tools enables the creation of an intuitive, flexible, tightly integrated design flow that efficiently bridges "logical" and "physical" design domains. This simplifies the task of defining a design, including its behavior, timing requirements, and optional layout (or floorplanning), as well as simplifying the task of analyzing reports generated during the implementation process. ments to begin changing state in response to the logic and the user clock.

The relative timing of these events can be changed via configuration options in software. In addition, the GTS and GWE events can be made dependent on the DONE pins of multiple devices all going High, forcing the devices to start synchronously. The sequence can also be paused at any stage, until lock has been achieved on any or all DCMs, as well as the DCI.

#### Readback

In this mode, configuration data from the Virtex-II FPGA device can be read back. Readback is supported only in the SelectMAP (master and slave) and Boundary-Scan mode.

Along with the configuration data, it is possible to read back the contents of all registers, distributed SelectRAM, and block RAM resources. This capability is used for real-time debugging. For more detailed configuration information, see the Virtex-II *Platform FPGA User Guide*.

#### **Bitstream Encryption**

Virtex-II devices have an on-chip decryptor using one or two sets of three keys for triple-key Data Encryption Standard (DES) operation. Xilinx software tools offer an optional encryption of the configuration data (bitstream) with a triple-key DES determined by the designer. The keys are stored in the FPGA by JTAG instruction and retained by a battery connected to the  $V_{BATT}$  pin, when the device is not powered. Virtex-II devices can be configured with the corresponding encrypted bitstream, using any of the configuration modes described previously.

A detailed description of how to use bitstream encryption is provided in the *Virtex-II Platform FPGA User Guide*. For devices that support this feature, please contact your sales representative for specific ordering part number.

### **Partial Reconfiguration**

Partial reconfiguration of Virtex-II devices can be accomplished in either Slave SelectMAP mode or Boundary-Scan mode. Instead of resetting the chip and doing a full configuration, new data is loaded into a specified area of the chip, while the rest of the chip remains in operation. Data is loaded on a column basis, with the smallest load unit being a configuration "frame" of the bitstream (device size dependent).

Partial reconfiguration is useful for applications that require different designs to be loaded into the same area of a chip, or that require the ability to change portions of a design without having to reset or reconfigure the entire chip.

## **Revision History**

This section records the change history for this module of the data sheet.

| Date     | Version | Revision                                                                                                                                                                                                                                                        |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11/07/00 | 1.0     | Early access draft.                                                                                                                                                                                                                                             |

| 12/06/00 | 1.1     | Initial release.                                                                                                                                                                                                                                                |

| 01/15/01 | 1.2     | Added values to the tables in the Virtex-II Performance Characteristics and Virtex-II Switching Characteristics sections.                                                                                                                                       |

| 01/25/01 | 1.3     | The data sheet was divided into four modules (per the current style standard). A note was added to Table 1.                                                                                                                                                     |

| 04/02/01 | 1.5     | <ul> <li>Under Input/Output Individual Options, the range of values for optional pull-up and pull-down resistors was changed to 10 - 60 KΩ from 50 - 100 KΩ.</li> <li>Skipped v1.4 to sync up modules. Reverted to traditional double-column format.</li> </ul> |

| 07/30/01 | 1.6     | <ul> <li>Added Table 6.</li> <li>Changed definition of multiply and divide integer ranges under Digital Clock Manager (DCM).</li> <li>Made numerous minor edits throughout this module.</li> </ul>                                                              |

| 10/02/01 | 1.7     | Updated descriptions under Digitally Controlled Impedance (DCI), Global Clock Multiplexer Buffers, Digital Clock Manager (DCM), and Creating a Design.                                                                                                          |

| 10/12/01 | 1.8     | Made clarifying edits under Digital Clock Manager (DCM).                                                                                                                                                                                                        |

| 11/29/01 | 1.9     | Changed bitstream lengths for each device in Table 26.                                                                                                                                                                                                          |

## Virtex-II Platform FPGAs: DC and Switching Characteristics

DS031-3 (v3.5) November 5, 2007

#### **Product Specification**

## Virtex-II Electrical Characteristics

Virtex-II<sup>™</sup> devices are provided in -6, -5, and -4 speed grades, with -6 having the highest performance.

Virtex-II DC and AC characteristics are specified for both commercial and industrial grades. Except the operating temperature range or unless otherwise noted, all the DC and AC electrical parameters are the same for a particular speed grade (that is, the timing characteristics of a -4 speed grade industrial device are the same as for a -4 speed grade

commercial device). However, only selected speed grades and/or devices might be available in the industrial range.

All supply voltage and junction temperature specifications are representative of worst-case conditions. The parameters included are common to popular designs and typical applications. Contact Xilinx for design considerations requiring more detailed information.

All specifications are subject to change without notice.

#### **Virtex-II DC Characteristics**

#### Table 1: Absolute Maximum Ratings

| Symbol                         | Desc                                         |                                                               | Units       |    |  |  |

|--------------------------------|----------------------------------------------|---------------------------------------------------------------|-------------|----|--|--|

| V <sub>CCINT</sub>             | Internal supply voltage relative to GNE      | Internal supply voltage relative to GND                       |             |    |  |  |

| V <sub>CCAUX</sub>             | Auxiliary supply voltage relative to GN      | D                                                             | -0.5 to 4.0 | V  |  |  |

| V <sub>CCO</sub>               | Output drivers supply voltage relative       | to GND                                                        | -0.5 to 4.0 | V  |  |  |

| V <sub>BATT</sub>              | Key memory battery backup supply             | -0.5 to 4.0                                                   | V           |    |  |  |

| V <sub>REF</sub>               | Input reference voltage                      | -0.5 to V <sub>CCO</sub> + 0.5                                | V           |    |  |  |

| V <sub>IN</sub> <sup>(3)</sup> | Input voltage relative to GND (user an       | -0.5 to V <sub>CCO</sub> + 0.5                                | V           |    |  |  |

| V <sub>TS</sub>                | Voltage applied to 3-state output (user      | -0.5 to 4.0                                                   | V           |    |  |  |

| T <sub>STG</sub>               | Storage temperature (ambient)                |                                                               | -65 to +150 | °C |  |  |

|                                |                                              | All regular FF/BF flip-chip and FG/BG/CS wire-bond packages   | +220        | °C |  |  |

| T <sub>SOL</sub>               | Maximum soldering temperature <sup>(2)</sup> | Pb-free FGG456, FGG676, BGG575, and BGG728 wire-bond packages | +250        | °C |  |  |

|                                |                                              | Pb-free FGG256 and CSG144 wire-bond packages                  | +260        | °C |  |  |

| TJ                             | Maximum junction temperature <sup>(2)</sup>  | +125                                                          | °C          |    |  |  |

Notes:

. Stresses beyond those listed under Absolute Maximum Ratings might cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time might affect device reliability.

2. For soldering guidelines and thermal considerations, see the <u>Device Packaging and Thermal Characteristics Guide</u> information on the Xilinx website.

3. Inputs configured as PCI are fully PCI compliant. This statement takes precedence over any specification that would imply that the device is not PCI compliant.

© 2000–2007 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

## Virtex-II Pin-to-Pin Output Parameter Guidelines

All devices are 100% functionally tested. Listed below are representative values for typical pin locations and normal clock loading. Values are expressed in nanoseconds unless otherwise noted.

## Global Clock Input to Output Delay for LVTTL, 12 mA, Fast Slew Rate, With DCM

#### Table 34: Global Clock Input to Output Delay for LVTTL, 12 mA, Fast Slew Rate, With DCM

| Description                                                                                                                                                              | Symbol                | Device   | -6   | -5   | -4   | Units |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------|------|------|------|-------|

| LVTTL Global Clock Input to Output delay using<br>Output flip-flop, 12 mA, Fast Slew Rate, <i>with</i><br>DCM.                                                           |                       |          |      |      |      |       |

| For data <i>output</i> with different standards, adjust<br>the delays with the values shown in IOB Output<br>Switching Characteristics Standard<br>Adjustments, page 14. |                       |          |      |      |      |       |

| Global Clock and OFF with DCM                                                                                                                                            | T <sub>ICKOFDCM</sub> | XC2V40   | 1.10 | 1.28 | 1.48 | ns    |

|                                                                                                                                                                          |                       | XC2V80   | 1.10 | 1.28 | 1.48 | ns    |

|                                                                                                                                                                          |                       | XC2V250  | 1.10 | 1.28 | 1.48 | ns    |

|                                                                                                                                                                          |                       | XC2V500  | 1.10 | 1.28 | 1.48 | ns    |

|                                                                                                                                                                          |                       | XC2V1000 | 1.10 | 1.28 | 1.48 | ns    |

|                                                                                                                                                                          |                       | XC2V1500 | 1.10 | 1.28 | 1.48 | ns    |

|                                                                                                                                                                          |                       | XC2V2000 | 1.10 | 1.28 | 1.48 | ns    |

|                                                                                                                                                                          |                       | XC2V3000 | 1.19 | 1.38 | 1.59 | ns    |

|                                                                                                                                                                          |                       | XC2V4000 | 1.19 | 1.38 | 1.59 | ns    |

|                                                                                                                                                                          |                       | XC2V6000 | 1.64 | 1.88 | 2.17 | ns    |

|                                                                                                                                                                          |                       | XC2V8000 |      | 1.88 | 2.17 | ns    |

Notes:

1. Listed above are representative values where one global clock input drives one vertical clock line in each accessible column, and where all accessible IOB and CLB flip-flops are clocked by the global clock net.

2. Output timing is measured at 50% V<sub>CC</sub> threshold with test setup shown in Figure 1. For other I/O standards, see Table 19.

#### Table 8: FG676/FGG676 BGA — XC2V1500, XC2V2000, and XC2V3000

| Bank | Pin Description | Pin Number | No Connect in XC2V1500 | No Connect in XC2V2000 |

|------|-----------------|------------|------------------------|------------------------|

| NA   | VCCINT          | H19        |                        |                        |

| NA   | VCCINT          | H8         |                        |                        |

| NA   | GND             | AF26       |                        |                        |

| NA   | GND             | AF1        |                        |                        |

| NA   | GND             | AE25       |                        |                        |

| NA   | GND             | AE14       |                        |                        |

| NA   | GND             | AE13       |                        |                        |

| NA   | GND             | AE2        |                        |                        |

| NA   | GND             | AD24       |                        |                        |

| NA   | GND             | AD3        |                        |                        |

| NA   | GND             | AC23       |                        |                        |

| NA   | GND             | AC4        |                        |                        |

| NA   | GND             | AB22       |                        |                        |

| NA   | GND             | AB5        |                        |                        |

| NA   | GND             | AA21       |                        |                        |

| NA   | GND             | AA6        |                        |                        |

| NA   | GND             | U17        |                        |                        |

| NA   | GND             | U16        |                        |                        |

| NA   | GND             | U15        |                        |                        |

| NA   | GND             | U14        |                        |                        |

| NA   | GND             | U13        |                        |                        |

| NA   | GND             | U12        |                        |                        |

| NA   | GND             | U11        |                        |                        |

| NA   | GND             | U10        |                        |                        |

| NA   | GND             | T17        |                        |                        |

| NA   | GND             | T16        |                        |                        |

| NA   | GND             | T15        |                        |                        |

| NA   | GND             | T14        |                        |                        |

| NA   | GND             | T13        |                        |                        |

| NA   | GND             | T12        |                        |                        |

| NA   | GND             | T11        |                        |                        |

| NA   | GND             | T10        |                        |                        |

| NA   | GND             | R17        |                        |                        |

| NA   | GND             | R16        |                        |                        |

| NA   | GND             | R15        |                        |                        |

| NA   | GND             | R14        |                        |                        |

| NA   | GND             | R13        |                        |                        |

#### Table 9: BG575/BGG575 BGA — XC2V1000, XC2V1500, and XC2V2000

| Bank | Pin Description        | Pin Number | No Connect in XC2V1000 | No Connect in XC2V1500 |

|------|------------------------|------------|------------------------|------------------------|

| 4    | IO_L02P_4/D1           | AB20       |                        |                        |

| 4    | IO_L03N_4/D2/ALT_VRP_4 | Y19        |                        |                        |

| 4    | IO_L03P_4/D3/ALT_VRN_4 | AA19       |                        |                        |

| 4    | IO_L04N_4/VREF_4       | W18        |                        |                        |

| 4    | IO_L04P_4              | Y18        |                        |                        |

| 4    | IO_L05N_4/VRP_4        | U16        |                        |                        |

| 4    | IO_L05P_4/VRN_4        | V17        |                        |                        |

| 4    | IO_L06N_4              | AD20       |                        |                        |

| 4    | IO_L06P_4              | AD19       |                        |                        |

| 4    | IO_L19N_4              | AC20       |                        |                        |

| 4    | IO_L19P_4              | AC19       |                        |                        |

| 4    | IO_L21N_4              | AA18       |                        |                        |

| 4    | IO_L21P_4/VREF_4       | AB18       |                        |                        |

| 4    | IO_L22N_4              | AC18       |                        |                        |

| 4    | IO_L22P_4              | AC17       |                        |                        |

| 4    | IO_L24N_4              | AA17       |                        |                        |

| 4    | IO_L24P_4              | AB17       |                        |                        |

| 4    | IO_L49N_4              | Y17        |                        |                        |

| 4    | IO_L49P_4              | W17        |                        |                        |

| 4    | IO_L51N_4              | V16        |                        |                        |

| 4    | IO_L51P_4/VREF_4       | W16        |                        |                        |

| 4    | IO_L52N_4              | AD17       |                        |                        |

| 4    | IO_L52P_4              | AD16       |                        |                        |

| 4    | IO_L54N_4              | AB16       |                        |                        |

| 4    | IO_L54P_4              | AC16       |                        |                        |

| 4    | IO_L67N_4              | Y16        | NC                     |                        |

| 4    | IO_L67P_4              | AA16       | NC                     |                        |

| 4    | IO_L69N_4              | W15        | NC                     |                        |

| 4    | IO_L69P_4/VREF_4       | Y15        | NC                     |                        |

| 4    | IO_L70N_4              | U15        | NC                     |                        |

| 4    | IO_L70P_4              | V15        | NC                     |                        |

| 4    | IO_L72N_4              | AD15       | NC                     |                        |

| 4    | IO_L72P_4              | AD14       | NC                     |                        |

| 4    | IO_L73N_4              | AB15       | NC                     | NC                     |

| 4    | IO_L73P_4              | AC15       | NC                     | NC                     |

| 4    | IO_L91N_4/VREF_4       | AA14       |                        |                        |

#### *Table 9:* BG575/BGG575 BGA — XC2V1000, XC2V1500, and XC2V2000

| Bank | Pin Description | Pin Number | No Connect in XC2V1000 | No Connect in XC2V1500 |

|------|-----------------|------------|------------------------|------------------------|

| NA   | GND             | D15        |                        |                        |

| NA   | GND             | D10        |                        |                        |

| NA   | GND             | D4         |                        |                        |

| NA   | GND             | C22        |                        |                        |

| NA   | GND             | C3         |                        |                        |

| NA   | GND             | B24        |                        |                        |

| NA   | GND             | B23        |                        |                        |

| NA   | GND             | B2         |                        |                        |

| NA   | GND             | B1         |                        |                        |

| NA   | GND             | A24        |                        |                        |

| NA   | GND             | A23        |                        |                        |

| NA   | GND             | A18        |                        |                        |

| NA   | GND             | A7         |                        |                        |

| NA   | GND             | A2         |                        |                        |

#### Notes:

1. See Table 4 for an explanation of the signals available on this pin.

#### Table 10: BG728 BGA — XC2V3000

| Bank | Pin Description | Pin Number |

|------|-----------------|------------|

| NA   | VCCINT          | K10        |

| NA   | GND             | AG27       |

| NA   | GND             | AG26       |

| NA   | GND             | AG14       |

| NA   | GND             | AG2        |

| NA   | GND             | AG1        |

| NA   | GND             | AF27       |

| NA   | GND             | AF26       |

| NA   | GND             | AF20       |

| NA   | GND             | AF8        |

| NA   | GND             | AF2        |

| NA   | GND             | AF1        |

| NA   | GND             | AE25       |

| NA   | GND             | AE3        |

| NA   | GND             | AD24       |

| NA   | GND             | AD14       |

| NA   | GND             | AD4        |

| NA   | GND             | AC23       |

| NA   | GND             | AC17       |

| NA   | GND             | AC11       |

| NA   | GND             | AC5        |

| NA   | GND             | AB22       |

| NA   | GND             | AB6        |

| NA   | GND             | AA21       |

| NA   | GND             | AA7        |

| NA   | GND             | Y26        |

| NA   | GND             | Y20        |

| NA   | GND             | Y8         |

| NA   | GND             | Y2         |

| NA   | GND             | W14        |

| NA   | GND             | U23        |

| NA   | GND             | U5         |

| NA   | GND             | T16        |

| NA   | GND             | T15        |

| NA   | GND             | T14        |

| NA   | GND             | T13        |

| Bank | Pin Description  | Pin Number | No Connect in the XC2V1000 | No Connect in the XC2V1500 |

|------|------------------|------------|----------------------------|----------------------------|

| 6    | IO_L68N_6        | Y26        | NC                         |                            |

| 6    | IO_L69P_6        | AA30       | NC                         |                            |

| 6    | IO_L69N_6/VREF_6 | Y30        | NC                         |                            |

| 6    | IO_L70P_6        | W24        | NC                         |                            |

| 6    | IO_L70N_6        | V24        | NC                         |                            |

| 6    | IO_L71P_6        | Y27        | NC                         |                            |

| 6    | IO_L71N_6        | W27        | NC                         |                            |

| 6    | IO_L72P_6        | W28        | NC                         |                            |

| 6    | IO_L72N_6        | Y28        | NC                         |                            |

| 6    | IO_L73P_6        | V25        | NC                         | NC                         |

| 6    | IO_L73N_6        | U25        | NC                         | NC                         |

| 6    | IO_L74P_6        | V26        | NC                         | NC                         |

| 6    | IO_L74N_6        | V27        | NC                         | NC                         |

| 6    | IO_L75P_6        | Y29        | NC                         | NC                         |

| 6    | IO_L75N_6/VREF_6 | W29        | NC                         | NC                         |

| 6    | IO_L76P_6        | U22        | NC                         | NC                         |

| 6    | IO_L76N_6        | T22        | NC                         | NC                         |

| 6    | IO_L77P_6        | U26        | NC                         | NC                         |

| 6    | IO_L77N_6        | T26        | NC                         | NC                         |

| 6    | IO_L78P_6        | V30        | NC                         | NC                         |

| 6    | IO_L78N_6        | W30        | NC                         | NC                         |

| 6    | IO_L91P_6        | U23        |                            |                            |

| 6    | IO_L91N_6        | T23        |                            |                            |

| 6    | IO_L92P_6        | U27        |                            |                            |

| 6    | IO_L92N_6        | T27        |                            |                            |

| 6    | IO_L93P_6        | V29        |                            |                            |

| 6    | IO_L93N_6/VREF_6 | U29        |                            |                            |

| 6    | IO_L94P_6        | T24        |                            |                            |

| 6    | IO_L94N_6        | T25        |                            |                            |

| 6    | IO_L95P_6        | U28        |                            |                            |

| 6    | IO_L95N_6        | T28        |                            |                            |

| 6    | IO_L96P_6        | T30        |                            |                            |

| 6    | IO_L96N_6        | U30        |                            |                            |

|      |                  |            | ·                          |                            |

| 7    | IO_L96P_7        | P28        |                            |                            |

| 7    | IO_L96N_7        | R28        |                            |                            |

| 7    | IO_L95P_7        | R25        |                            |                            |

Table 11: FF896 BGA — XC2V1000, XC2V1500, and XC2V2000

| Bank | Pin Description  | Pin Number | No Connect in the XC2V3000 |

|------|------------------|------------|----------------------------|

| 3    | IO_L83P_3        | Y4         | NC                         |

| 3    | IO_L82N_3        | W11        | NC                         |

| 3    | IO_L82P_3        | V11        | NC                         |

| 3    | IO_L81N_3/VREF_3 | W8         | NC                         |

| 3    | IO_L81P_3        | Y8         | NC                         |

| 3    | IO_L80N_3        | W2         | NC                         |

| 3    | IO_L80P_3        | Y1         | NC                         |

| 3    | IO_L79N_3        | AA3        | NC                         |

| 3    | IO_L79P_3        | AB3        | NC                         |

| 3    | IO_L78N_3        | Y6         |                            |

| 3    | IO_L78P_3        | AA6        |                            |

| 3    | IO_L77N_3        | AA4        |                            |

| 3    | IO_L77P_3        | AB4        |                            |

| 3    | IO_L76N_3        | Y7         |                            |

| 3    | IO_L76P_3        | AA8        |                            |

| 3    | IO_L75N_3/VREF_3 | Y10        |                            |

| 3    | IO_L75P_3        | AA10       |                            |

| 3    | IO_L74N_3        | AA1        |                            |

| 3    | IO_L74P_3        | AB1        |                            |

| 3    | IO_L73N_3        | AA5        |                            |

| 3    | IO_L73P_3        | AB5        |                            |

| 3    | IO_L72N_3        | AA9        |                            |

| 3    | IO_L72P_3        | Y9         |                            |

| 3    | IO_L71N_3        | AA2        |                            |

| 3    | IO_L71P_3        | AB2        |                            |

| 3    | IO_L70N_3        | AB6        |                            |

| 3    | IO_L70P_3        | AC6        |                            |

| 3    | IO_L69N_3/VREF_3 | AD1        |                            |

| 3    | IO_L69P_3        | AC1        |                            |

| 3    | IO_L68N_3        | AC3        |                            |

| 3    | IO_L68P_3        | AD3        |                            |

| 3    | IO_L67N_3        | AC4        |                            |

| 3    | IO_L67P_3        | AD4        |                            |

| 3    | IO_L54N_3        | AB7        |                            |

| 3    | IO_L54P_3        | AC7        |                            |

| 3    | IO_L53N_3        | AC2        |                            |

#### Table 12: FF1152 BGA — XC2V3000, XC2V4000, XC2V6000, and XC2V8000

#### Bank **Pin Description Pin Number** No Connect in the XC2V3000 7 IO L03N 7 F30 7 IO\_L02P\_7/VRN\_7 K25 7 IO\_L02N\_7/VRP\_7 J25 7 IO\_L01P\_7 D33 7 IO L01N 7 E33 0 VCCO\_0 M22 0 VCCO\_0 M21 0 VCCO 0 M20 0 VCCO\_0 M19 0 VCCO\_0 M18 VCCO\_0 L23 0 VCCO\_0 L22 0 0 VCCO\_0 L21 VCCO\_0 0 L20 0 VCCO 0 E20 0 VCCO\_0 D28 0 VCCO\_0 A25 VCCO\_0 A19 0 1 VCCO\_1 M17 1 VCCO\_1 M16 1 VCCO\_1 M15 1 VCCO\_1 M14 VCCO\_1 1 M13 1 VCCO\_1 L15 1 VCCO\_1 L14 1 VCCO 1 L13 1 VCCO\_1 L12 1 VCCO\_1 E15 1 VCCO\_1 D7 1 VCCO\_1 A16 1 VCCO\_1 A10 2 VCCO 2 U12 2 VCCO\_2 T12 2 VCCO 2 T1 2 VCCO\_2 R12

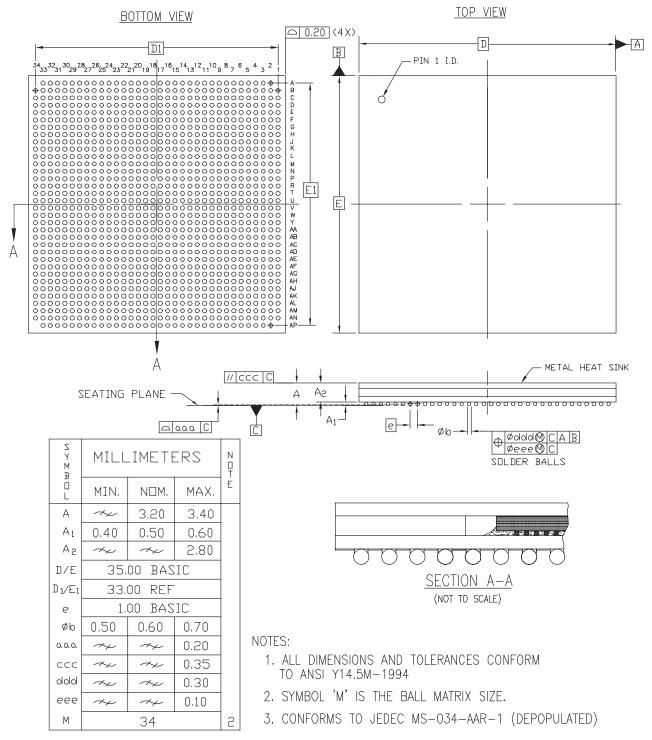

## FF1152 Flip-Chip Fine-Pitch BGA Package Specifications (1.00mm pitch)

Figure 8: FF1152 Flip-Chip Fine-Pitch BGA Package Specifications

| Bank | Pin Description  | Pin Number | No Connect in the XC2V4000 | No Connect in the XC2V6000 |

|------|------------------|------------|----------------------------|----------------------------|

| 3    | IO_L58N_3        | AD5        |                            |                            |

| 3    | IO_L58P_3        | AE5        |                            |                            |

| 3    | IO_L57N_3/VREF_3 | AE11       |                            |                            |

| 3    | IO_L57P_3        | AD11       |                            |                            |

| 3    | IO_L56N_3        | AG1        |                            |                            |

| 3    | IO_L56P_3        | AH1        |                            |                            |

| 3    | IO_L55N_3        | AD6        |                            |                            |

| 3    | IO_L55P_3        | AE6        |                            |                            |

| 3    | IO_L54N_3        | AF10       |                            |                            |

| 3    | IO_L54P_3        | AE10       |                            |                            |

| 3    | IO_L53N_3        | AG2        |                            |                            |

| 3    | IO_L53P_3        | AH2        |                            |                            |

| 3    | IO_L52N_3        | AF4        |                            |                            |

| 3    | IO_L52P_3        | AG4        |                            |                            |

| 3    | IO_L51N_3/VREF_3 | AG8        |                            |                            |

| 3    | IO_L51P_3        | AF8        |                            |                            |

| 3    | IO_L50N_3        | AH3        |                            |                            |

| 3    | IO_L50P_3        | AJ3        |                            |                            |

| 3    | IO_L49N_3        | AE7        |                            |                            |

| 3    | IO_L49P_3        | AF7        |                            |                            |

| 3    | IO_L48N_3        | AG9        |                            |                            |

| 3    | IO_L48P_3        | AF9        |                            |                            |

| 3    | IO_L47N_3        | AF6        |                            |                            |

| 3    | IO_L47P_3        | AG6        |                            |                            |

| 3    | IO_L46N_3        | AG5        |                            |                            |

| 3    | IO_L46P_3        | AH5        |                            |                            |

| 3    | IO_L45N_3/VREF_3 | AF12       |                            |                            |

| 3    | IO_L45P_3        | AE12       |                            |                            |

| 3    | IO_L44N_3        | AJ1        |                            |                            |

| 3    | IO_L44P_3        | AK1        |                            |                            |

| 3    | IO_L43N_3        | AH4        |                            |                            |

| 3    | IO_L43P_3        | AJ4        |                            |                            |

| 3    | IO_L36N_3        | AG11       | NC                         |                            |

| 3    | IO_L36P_3        | AF11       | NC                         |                            |

| 3    | IO_L35N_3        | AK2        | NC                         |                            |

| 3    | IO_L35P_3        | AL2        | NC                         |                            |

Table 13: FF1517 BGA — XC2V4000, XC2V6000, and XC2V8000

| Bank | Pin Description  | Pin Number | No Connect in XC2V2000 |

|------|------------------|------------|------------------------|

| 7    | IO_L96N_7        | R27        |                        |

| 7    | IO_L95P_7        | R24        |                        |

| 7    | IO_L95N_7        | N24        |                        |

| 7    | IO_L94P_7        | T29        |                        |

| 7    | IO_L94N_7        | R29        |                        |

| 7    | IO_L93P_7/VREF_7 | R31        |                        |

| 7    | IO_L93N_7        | P31        |                        |

| 7    | IO_L92P_7        | R26        |                        |

| 7    | IO_L92N_7        | P26        |                        |

| 7    | IO_L91P_7        | R30        |                        |

| 7    | IO_L91N_7        | P30        |                        |

| 7    | IO_L78P_7        | R25        |                        |

| 7    | IO_L78N_7        | P25        |                        |

| 7    | IO_L77P_7        | R28        |                        |

| 7    | IO_L77N_7        | P28        |                        |

| 7    | IO_L76P_7        | N31        |                        |

| 7    | IO_L76N_7        | M31        |                        |

| 7    | IO_L75P_7/VREF_7 | R23        |                        |

| 7    | IO_L75N_7        | P23        |                        |

| 7    | IO_L74P_7        | N30        |                        |

| 7    | IO_L74N_7        | M30        |                        |

| 7    | IO_L73P_7        | P27        |                        |

| 7    | IO_L73N_7        | N27        |                        |

| 7    | IO_L72P_7        | P22        |                        |

| 7    | IO_L72N_7        | N22        |                        |

| 7    | IO_L71P_7        | N29        |                        |

| 7    | IO_L71N_7        | M29        |                        |

| 7    | IO_L70P_7        | N28        |                        |

| 7    | IO_L70N_7        | M28        |                        |

| 7    | IO_L69P_7/VREF_7 | N26        |                        |

| 7    | IO_L69N_7        | M26        |                        |

| 7    | IO_L68P_7        | L31        |                        |

| 7    | IO_L68N_7        | K31        |                        |

| 7    | IO_L67P_7        | M27        |                        |

| 7    | IO_L67N_7        | L27        |                        |

| 7    | <br>IO_L54P_7    | N23        |                        |

| 7    | <br>IO_L54N_7    | M23        |                        |

| 7    | <br>IO_L53P_7    | L30        |                        |

Table 14: BF957 — XC2V2000, XC2V3000, XC2V4000, and XC2V6000