Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                     |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 30/20MHz                                                                  |

| Connectivity               | UART/USART                                                                |

| Peripherals                | POR                                                                       |

| Number of I/O              | 32                                                                        |

| Program Memory Size        | -                                                                         |

| Program Memory Type        | ROMIess                                                                   |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-LCC (J-Lead)                                                           |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at80c31x2-slsul |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4. SFR Mapping

The Special Function Registers (SFRs) of the TS80C31X2 fall into the following categories:

- C51 core registers: ACC, B, DPH, DPL, PSW, SP, AUXR1

- I/O port registers: P0, P1, P2, P3

- Timer registers: TCON, TH0, TH1, TMOD, TL0, TL1

- Serial I/O port registers: SADDR, SADEN, SBUF, SCON

- Power and clock control registers: PCON

- Interrupt system registers: IE, IP, IPH

- Others: CKCON

Table 4-1.

All SFRs with their address and their reset value

|     | Bit<br>addressable |                    | Non Bit addressable |                  |                  |                  |     |                    |     |

|-----|--------------------|--------------------|---------------------|------------------|------------------|------------------|-----|--------------------|-----|

|     | 0/8                | 1/9                | 2/A                 | 3/B              | 4/C              | 5/D              | 6/E | 7/F                |     |

| F8h |                    |                    |                     |                  |                  |                  |     |                    | FFh |

| F0h | B<br>0000 0000     |                    |                     |                  |                  |                  |     |                    | F7h |

| E8h |                    |                    |                     |                  |                  |                  |     |                    | EFh |

| E0h | ACC<br>0000 0000   |                    |                     |                  |                  |                  |     |                    | E7h |

| D8h |                    |                    |                     |                  |                  |                  |     |                    | DFh |

| D0h | PSW<br>0000 0000   |                    |                     |                  |                  |                  |     |                    | D7h |

| C8h |                    |                    |                     |                  |                  |                  |     |                    | CFh |

| C0h |                    |                    |                     |                  |                  |                  |     |                    | C7h |

| B8h | IP<br>XXX0 0000    | SADEN<br>0000 0000 |                     |                  |                  |                  |     |                    | BFh |

| B0h | P3<br>1111 1111    |                    |                     |                  |                  |                  |     | IPH<br>XXX0 0000   | B7h |

| A8h | IE<br>0XX0 0000    | SADDR<br>0000 0000 |                     |                  |                  |                  |     |                    | AFh |

| A0h | P2<br>1111 1111    |                    | AUXR1<br>XXXX XXX0  |                  |                  |                  |     |                    | A7h |

| 98h | SCON<br>0000 0000  | SBUF<br>XXXX XXXX  |                     |                  |                  |                  |     |                    | 9Fh |

| 90h | P1<br>1111 1111    |                    |                     |                  |                  |                  |     |                    | 97h |

| 88h | TCON<br>0000 0000  | TMOD<br>0000 0000  | TL0<br>0000 0000    | TL1<br>0000 0000 | TH0<br>0000 0000 | TH1<br>0000 0000 |     | CKCON<br>XXXX XXX0 | 8Fh |

| 80h | P0<br>1111 1111    | SP<br>0000 0111    | DPL<br>0000 0000    | DPH<br>0000 0000 |                  |                  |     | PCON<br>00X1 0000  | 87h |

|     | 0/8                | 1/9                | 2/A                 | 3/B              | 4/C              | 5/D              | 6/E | 7/F                |     |

Reserved

### 6. TS80C31X2 Enhanced Features

In comparison to the original 80C31, the TS80C31X2 implements some new features, which are:

- The X2 option.

- The Dual Data Pointer.

- The 4 level interrupt priority system.

- The power-off flag.

- The ONCE mode.

- Enhanced UART

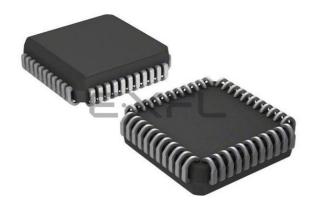

### 6.1 X2 Feature

The TS80C31X2 core needs only 6 clock periods per machine cycle. This feature called "X2" provides the following advantages:

- Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power.

- Save power consumption while keeping same CPU power (oscillator power saving).

- Save power consumption by dividing dynamically operating frequency by 2 in operating and idle modes.

- Increase CPU power by 2 while keeping same crystal frequency.

In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by software.

### 6.1.1 Description

The clock for the whole circuit and peripheral is first divided by two before being used by the CPU core and peripherals. This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%. Figure 6-1. shows the clock generation block diagram. X2 bit is validated on XTAL1÷2 rising edge to avoid glitches when switching from X2 to STD mode. Figure 6-2. shows the mode switching waveforms.

### Figure 6-1. Clock Generation Diagram

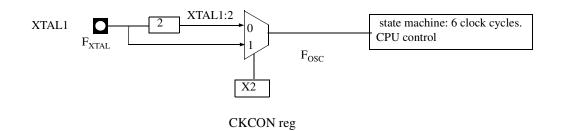

#### **Dual Data Pointer Register Ddptr** 7.

The additional data pointer can be used to speed up code execution and reduce code size in a number of ways.

The dual DPTR structure is a way by which the chip will specify the address of an external data memory location. There are two 16-bit DPTR registers that address the external memory, and a single bit called

DPS = AUXR1/bit0 (See Table 5.) that allows the program code to switch between them (Refer to Figure 7-1).

#### Figure 7-1. Use of Dual Pointer

| Table 7-1. | AUXR1: Auxiliary Register 1 |

|------------|-----------------------------|

|            |                             |

| Table 7-1.    | AUXR1: Au       | xiliary                                                                                | y Register 1                                                                    |                        |                        |      |   |     |

|---------------|-----------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------|------------------------|------|---|-----|

| 7             | 6               |                                                                                        | 5                                                                               | 4                      | 3                      | 2    | 1 | 0   |

| -             | -3              |                                                                                        | -                                                                               | -                      | -                      | -    | - | DPS |

| Bit<br>Number | Bit<br>Mnemonic |                                                                                        | Description                                                                     |                        |                        |      |   |     |

| 7             | -               |                                                                                        | <b>erved</b><br>value read from tl                                              | nis bit is indetermina | ate. Do not set this b | pit. |   |     |

| 6             | -               | Reserved           The value read from this bit is indeterminate. Do not set this bit. |                                                                                 |                        |                        |      |   |     |

| 5             | -               |                                                                                        | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                        |                        |      |   |     |

| 4             | -               |                                                                                        | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                        |                        |      |   |     |

| 3             | -               |                                                                                        | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                        |                        |      |   |     |

| 2             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.        |                                                                                 |                        |                        |      |   |     |

| 1             | -               |                                                                                        | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                        |                        |      |   |     |

| 0             | DPS             | Clea                                                                                   | Data Pointer Selection<br>Clear to select DPTR0.<br>Set to select DPTR1.        |                        |                        |      |   |     |

Reset Value = XXXX XXX0 Not bit addressable

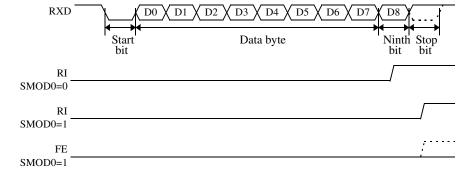

### Figure 9-3. UART Timings in Modes 2 and 3

### 9.2 Automatic Address Recognition

The automatic address recognition feature is enabled when the multiprocessor communication feature is enabled (SM2 bit in SCON register is set).

Implemented in hardware, automatic address recognition enhances the multiprocessor communication feature by allowing the serial port to examine the address of each incoming command frame. Only when the serial port recognizes its own address, the receiver sets RI bit in SCON register to generate an interrupt. This ensures that the CPU is not interrupted by command frames addressed to other devices.

If desired, you may enable the automatic address recognition feature in mode 1. In this configuration, the stop bit takes the place of the ninth data bit. Bit RI is set only when the received command frame address matches the device's address and is terminated by a valid stop bit.

To support automatic address recognition, a device is identified by a given address and a broadcast address.

NOTE: The multiprocessor communication and automatic address recognition features cannot be enabled in mode 0 (i.e. setting SM2 bit in SCON register in mode 0 has no effect).

### 9.3 Given Address

Each device has an individual address that is specified in SADDR register; the SADEN register is a mask byte that contains don't-care bits (defined by zeros) to form the device's given address. The don't-care bits provide the flexibility to address one or more slaves at a time. The following example illustrates how a given address is formed.

To address a device by its individual address, the SADEN mask byte must be 1111 1111b. For example:

| SADDR | 0101 0110b        |

|-------|-------------------|

| SADEN | <u>1111 1100b</u> |

| Given | 0101 01XXb        |

The following is an example of how to use given addresses to address different slaves:

| Slave A: | SADDR<br><u>SADEN</u><br>Given | 1111 0001b<br><u>1111 1010b</u><br>1111 0X0Xb |

|----------|--------------------------------|-----------------------------------------------|

| Slave B: | SADDR<br><u>SADEN</u><br>Given | 1111 0011b<br><u>1111 1001b</u><br>1111 0XX1b |

| Slave C: | SADDR | 1111 0010b        |

|----------|-------|-------------------|

|          | SADEN | <u>1111 1101b</u> |

|          | Given | 1111 00X1b        |

The SADEN byte is selected so that each slave may be addressed separately.

For slave A, bit 0 (the LSB) is a don't-care bit; for slaves B and C, bit 0 is a 1. To communicate with slave A only, the master must send an address where bit 0 is clear (e.g. 1111 0000b). For slave A, bit 1 is a 1; for slaves B and C, bit 1 is a don't care bit. To communicate with slaves

B and C, but not slave A, the master must send an address with bits 0 and 1 both set (e.g. 1111 0011b).

To communicate with slaves A, B and C, the master must send an address with bit 0 set, bit 1 clear, and bit 2 clear (e.g. 1111 0001b).

### 9.4 Broadcast Address

A broadcast address is formed from the logical OR of the SADDR and SADEN registers with zeros defined as don't-care bits, e.g.:

SADDR

0101 0110b

SADEN

1111 1100b

Broadcast = SADDR OR SADEN

1111 111Xb

The use of don't-care bits provides flexibility in defining the broadcast address, however in most applications, a broadcast address is FFh. The following is an example of using broadcast addresses:

| Slave A: | SADDR<br><u>SADEN</u><br>Broadcast  | 1111 0001b<br><u>1111 1010b</u><br>1111 1X11b, |

|----------|-------------------------------------|------------------------------------------------|

| Slave B: | SADDR<br><u>SADEN</u><br>Broadcast  | 1111 0011b<br><u>1111 1001b</u><br>1111 1X11B, |

| Slave C: | SADDR=<br><u>SADEN</u><br>Broadcast | 1111 0010b<br><u>1111 1101b</u><br>1111 1111b  |

For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.

### 9.5 Reset Addresses

On reset, the SADDR and SADEN registers are initialized to 00h, i.e. the given and broadcast addresses are XXXX XXXb (all don't-care bits). This ensures that the serial port will reply to any address, and so, that it is backwards compatible with the 80C51 microcontrollers that do not support automatic address recognition.

Table 9-1. SADEN - Slave Address Mask Register (B9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

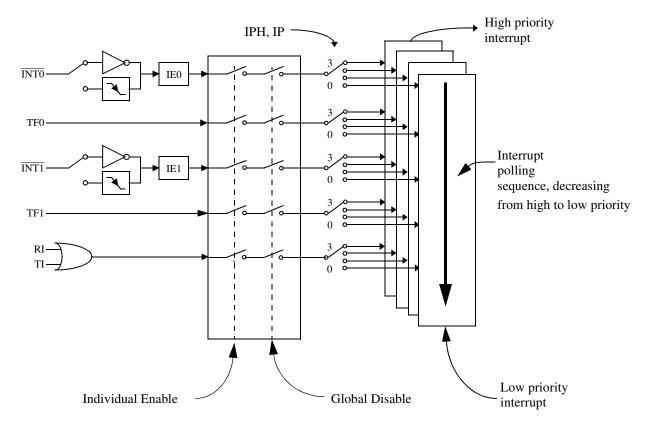

### 10. Interrupt System

The TS80C31X2 has a total of 5 interrupt vectors: two external interrupts (INT0 and INT1), two timer interrupts (timers 0 and 1) and the serial port interrupt. These interrupts are shown in Figure 10-1.

Figure 10-1. Interrupt Control System

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register (See Table 10-2.Table 10-3.). This register also contains a global disable bit, which must be cleared to disable all interrupts at once.

Each interrupt source can also be individually programmed to one out of four priority levels by setting or clearing a bit in the Interrupt Priority register (See Table 10-3.) and in the Interrupt Priority High register (See Table 10-4.). shows the bit values and priority levels associated with each combination.

| IPH.x | IP.x | Interrupt Level Priority |

|-------|------|--------------------------|

| 0     | 0    | 0 (Lowest)               |

| 0     | 1    | 1                        |

| 1     | 0    | 2                        |

| 1     | 1    | 3 (Highest)              |

Table 10-1.

Priority Level Bit Values

# AT/TS80C31X2

| 7      | 6        | 5                                      | 4                                                                               | 3               | 2                  | 1   | 0   |  |

|--------|----------|----------------------------------------|---------------------------------------------------------------------------------|-----------------|--------------------|-----|-----|--|

| -      | -        | -                                      | PS                                                                              | PT1             | PX1                | PT0 | PX0 |  |

| Bit    | Bit      |                                        |                                                                                 |                 |                    |     |     |  |

| Number | Mnemonic |                                        |                                                                                 | Descrip         | ption              |     |     |  |

| 7      | -        | <b>Reserved</b><br>The value read fro  | om this bit is in                                                               | determinate. Do | o not set this bit |     |     |  |

| 6      | -        | <b>Reserved</b><br>The value read fro  | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                    |     |     |  |

| 5      | -        | <b>Reserved</b><br>The value read fro  | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                    |     |     |  |

| 4      | PS       |                                        | Serial port Priority bit<br>Refer to PSH for priority level.                    |                 |                    |     |     |  |

| 3      | PT1      |                                        | Fimer 1 overflow interrupt Priority bit<br>Refer to PT1H for priority level.    |                 |                    |     |     |  |

| 2      | PX1      |                                        | External interrupt 1 Priority bit<br>Refer to PX1H for priority level.          |                 |                    |     |     |  |

| 1      | PT0      |                                        | Fimer 0 overflow interrupt Priority bit<br>Refer to PT0H for priority level.    |                 |                    |     |     |  |

| 0      | PX0      | External interrup<br>Refer to PX0H for |                                                                                 | t               |                    |     |     |  |

Table 10-3 IP Register -- IP - Interrupt Priority Register (B8h)

Reset Value = XXX0 0000b Bit addressable

### 11. Idle mode

An instruction that sets PCON.0 causes that to be the last instruction executed before going into the Idle mode. In the Idle mode, the internal clock signal is gated off to the CPU, but not to the interrupt, Timer, and Serial Port functions. The CPU status is preserved in its entirely : the Stack Pointer, Program Counter, Program Status Word, Accumulator and all other registers maintain their data during Idle. The port pins hold the logical states they had at the time Idle was activated. ALE and PSEN hold at logic high levels.

There are two ways to terminate the Idle. Activation of any enabled interrupt will cause PCON.0 to be cleared by hardware, terminating the Idle mode. The interrupt will be serviced, and following RETI the next instruction to be executed will be the one following the instruction that put the device into idle.

The flag bits GF0 and GF1 can be used to give and indication if an interrupt occured during normal operation or during an Idle. For example, an instruction that activates Idle can also set one or both flag bits. When Idle is terminated by an interrupt, the interrupt service routine can examine the flag bits.

The over way of terminating the Idle mode is with a hardware reset. Since the clock oscillator is still running, the hardware reset needs to be held active for only two machine cycles (24 oscillator periods) to complete the reset.

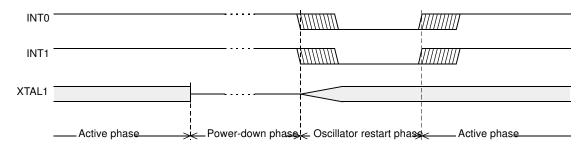

### 11.1 Power-Down Mode

To save maximum power, a power-down mode can be invoked by software (Refer to Table 9-4., PCON register).

In power-down mode, the oscillator is stopped and the instruction that invoked power-down mode is the last instruction executed. The internal RAM and SFRs retain their value until the power-down mode is terminated.  $V_{CC}$  can be lowered to save further power. Either a hardware reset or an external interrupt can cause an exit from power-down. To properly terminate power-down, the reset or external interrupt should not be executed before  $V_{CC}$  is restored to its normal operating level and must be held active long enough for the oscillator to restart and stabilize.

Only external interrupts INT0 and INT1 are useful to exit from power-down. For that, interrupt must be enabled and configured as level or edge sensitive interrupt input.

Holding the pin low restarts the oscillator but bringing the pin high completes the exit as detailed in Figure 11-1. When both interrupts are enabled, the oscillator restarts as soon as one of the two inputs is held low and power down exit will be completed when the first input will be released. In this case the higher priority interrupt service routine is executed.

Once the interrupt is serviced, the next instruction to be executed after RETI will be the one following the instruction that put TS80C31X2 into power-down mode.

### Figure 11-1. Power-Down Exit Waveform

Exit from power-down by reset redefines all the SFRs, exit from power-down by external interrupt does no affect the SFRs.

Exit from power-down by either reset or external interrupt does not affect the internal RAM content.

Note: NOTE: If idle mode is activated with power-down mode (IDL and PD bits set), the exit sequence is unchanged, when execution is vectored to interrupt, PD and IDL bits are cleared and idle mode is not entered.

| Mode       | Program<br>Memory | ALE | PSEN | PORT0    | PORT1     | PORT2     | PORT3     |

|------------|-------------------|-----|------|----------|-----------|-----------|-----------|

| Idle       | External          | 1   | 1    | Floating | Port Data | Address   | Port Data |

| Power Down | External          | 0   | 0    | Floating | Port Data | Port Data | Port Data |

Table 11-1.

The state of ports during idle and power-down modes

## 12. ONCE<sup>™</sup> Mode (ON Chip Emulation)

The ONCE mode facilitates testing and debugging of systems using TS80C31X2 without removing the circuit from the board. The ONCE mode is invoked by driving certain pins of the TS80C31X2; the following sequence must be exercised:

- Pull ALE low while the device is in reset (RST high) and PSEN is high.

- Hold ALE low as RST is deactivated.

While the TS80C31X2 is in ONCE mode, an emulator or test CPU can be used to drive the circuit Table 26. shows the status of the port pins during ONCE mode.

Normal operation is restored when normal reset is applied.

Table 12-1. External Pin Status during ONCE Mode

| ALE          | PSEN         | Port 0 | Port 1       | Port 2       | Port 3       | XTAL1/2 |

|--------------|--------------|--------|--------------|--------------|--------------|---------|

| Weak pull-up | Weak pull-up | Float  | Weak pull-up | Weak pull-up | Weak pull-up | Active  |

### 13. Power-Off Flag

The power-off flag allows the user to distinguish between a "cold start" reset and a "warm start" reset.

A cold start reset is the one induced by  $V_{CC}$  switch-on. A warm start reset occurs while  $V_{CC}$  is still applied to the device and could be generated for example by an exit from power-down.

The power-off flag (POF) is located in PCON register (See Table 13-1.). POF is set by hardware when  $V_{CC}$  rises from 0 to its nominal voltage. The POF can be set or cleared by software allowing the user to determine the type of reset.

The POF value is only relevant with a Vcc range from 4.5V to 5.5V. For lower Vcc value, reading POF bit will return indeterminate value.

| Table 13-1. | PCON Register | PCON - Power | Control | Register ( | (87h) |  |

|-------------|---------------|--------------|---------|------------|-------|--|

|             |               |              |         |            |       |  |

| 7             | 6               | 5                                     | 2                                                                                                                                                                      | 1                | 0     |    |     |  |  |

|---------------|-----------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|----|-----|--|--|

| SMOD1         | SMOD            | ) -                                   | POF                                                                                                                                                                    | GF1              | GF0   | PD | IDL |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                                       |                                                                                                                                                                        | Descrip          | otion |    |     |  |  |

| 7             | SMOD1           | Serial port Mode<br>Set to select dou |                                                                                                                                                                        | n mode 1, 2 or : | 3.    |    |     |  |  |

| 6             | SMOD0           | Clear to select SI                    | Gerial port Mode bit 0<br>Clear to select SM0 bit in SCON register.<br>Set to to select FE bit in SCON register.                                                       |                  |       |    |     |  |  |

| 5             | -               | <b>Reserved</b><br>The value read fr  | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                        |                  |       |    |     |  |  |

| 4             | POF             | Ŭ                                     | <b>Power-Off Flag</b><br>Clear to recognize next reset type.<br>Set by hardware when V <sub>CC</sub> rises from 0 to its nominal voltage. Can also be set by software. |                  |       |    |     |  |  |

| 3             | GF1             | Cleared by user f                     | General purpose Flag<br>Cleared by user for general purpose usage.<br>Set by user for general purpose usage.                                                           |                  |       |    |     |  |  |

| 2             | GF0             | Cleared by user f                     | <b>General purpose Flag</b><br>Cleared by user for general purpose usage.<br>Set by user for general purpose usage.                                                    |                  |       |    |     |  |  |

| 1             | PD              | Cleared by hardw                      | Power-Down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                                                                         |                  |       |    |     |  |  |

| 0             | IDL             |                                       | <b>Idle mode bit</b><br>Clear by hardware when interrupt or reset occurs.<br>Set to enter idle mode.                                                                   |                  |       |    |     |  |  |

Reset Value = 00X1 0000b Not bit addressable

### 14. Electrical Characteristics

### 14.1 Absolute Maximum Ratings <sup>(1)</sup>

Ambiant Temperature Under Bias: C = commercial0°C to 70°C I = industrial -40°C to 85°C Storage Temperature-65°C to + 150°C Voltage on  $V_{CC}$  to  $V_{SS}$ -0.5 V to + 7 V Voltage on  $V_{PP}$  to  $V_{SS}$ -0.5 V to + 13 V Voltage on Any Pin to  $V_{SS}$ -0.5 V to  $V_{CC}$  + 0.5 V Power Dissipation1 W<sup>(2)</sup>

- Note: 1. Stresses at or above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- 2. This value is based on the maximum allowable die temperature and the thermal resistance of the package.

### 14.2 Power consumption measurement

Since the introduction of the first C51 devices, every manufacturer made operating lcc measurements under reset, which made sense for the designs were the CPU was running under reset. In Atmel Wireless & Microcontrollers new devices, the CPU is no more active during reset, so the power consumption is very low but is not really representative of what will happen in the customer system. That's why, while keeping measurements under Reset, Atmel Wireless & Microcontrollers presents a new way to measure the operating lcc:

Using an internal test ROM, the following code is executed:

Label:

SJMP Label (80 FE)

Ports 1, 2, 3 are disconnected, Port 0 is tied to FFh, EA = Vcc, RST = Vss, XTAL2 is not connected and XTAL1 is driven by the clock.

This is much more representative of the real operating lcc.

### 14.3 DC Parameters for Standard Voltage

$\begin{array}{l} T_{A}=0^{\circ}C \text{ to } +70^{\circ}C; \ V_{SS}=0 \ V; \ V_{CC}=5 \ V\pm10\%; \ F=0 \ \text{to } 40 \ \text{MHz}. \\ T_{A}=-40^{\circ}C \ \text{to } +85^{\circ}C; \ V_{SS}=0 \ V; \ V_{CC}=5 \ V\pm10\%; \ F=0 \ \text{to } 40 \ \text{MHz}. \end{array}$

| Symbol                            | Parameter                                                    | Min                                                                     | Тур    | Max                                                 | Unit        | Test Conditions                                                                                                    |

|-----------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------|--------|-----------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>                   | Input Low Voltage                                            | -0.5                                                                    |        | 0.2 V <sub>CC</sub> - 0.1                           | V           |                                                                                                                    |

| V <sub>IH</sub>                   | Input High Voltage except XTAL1, RST                         | 0.2 V <sub>CC</sub> + 0.9                                               |        | V <sub>CC</sub> + 0.5                               | V           |                                                                                                                    |

| V <sub>IH1</sub>                  | Input High Voltage, XTAL1, RST                               | 0.7 V <sub>CC</sub>                                                     |        | V <sub>CC</sub> + 0.5                               | V           |                                                                                                                    |

| V <sub>OL</sub>                   | Output Low Voltage, ports 1, 2, 3 <sup>(6)</sup>             |                                                                         |        | 0.3<br>0.45<br>1.0                                  | V<br>V<br>V | $I_{OL} = 100 \ \mu A^{(4)}$ $I_{OL} = 1.6 \ m A^{(4)}$ $I_{OL} = 3.5 \ m A^{(4)}$                                 |

| V <sub>OL1</sub>                  | Output Low Voltage, port 0 <sup>(6)</sup>                    |                                                                         |        | 0.3<br>0.45<br>1.0                                  | V<br>V<br>V | $I_{OL} = 200 \ \mu A^{(4)}$ $I_{OL} = 3.2 \ m A^{(4)}$ $I_{OL} = 7.0 \ m A^{(4)}$                                 |

| V <sub>OL2</sub>                  | Output Low Voltage, ALE, PSEN                                |                                                                         |        | 0.3<br>0.45<br>1.0                                  | V<br>V<br>V | $\begin{split} I_{OL} &= 100 \ \mu A^{(4)} \\ I_{OL} &= 1.6 \ m A^{(4)} \\ I_{OL} &= 3.5 \ m A^{(4)} \end{split}$  |

| V <sub>OH</sub>                   | Output High Voltage, ports 1, 2, 3                           | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |        |                                                     | V<br>V<br>V | I <sub>OH</sub> = -10 μA<br>I <sub>OH</sub> = -30 μA<br>I <sub>OH</sub> = -60 μA<br>V <sub>CC</sub> = 5 V ± 10%    |

| V <sub>OH1</sub>                  | Output High Voltage, port 0                                  | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |        |                                                     | V<br>V<br>V | I <sub>OH</sub> = -200 μA<br>I <sub>OH</sub> = -3.2 mA<br>I <sub>OH</sub> = -7.0 mA<br>V <sub>CC</sub> = 5 V ± 10% |

| V <sub>OH2</sub>                  | Output High Voltage,ALE, PSEN                                | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |        |                                                     | V<br>V<br>V | I <sub>OH</sub> = -100 μA<br>I <sub>OH</sub> = -1.6 mA<br>I <sub>OH</sub> = -3.5 mA<br>V <sub>CC</sub> = 5 V ± 10% |

| R <sub>RST</sub>                  | RST Pulldown Resistor                                        | 50                                                                      | 90 (5) | 200                                                 | kΩ          |                                                                                                                    |

| I <sub>IL</sub>                   | Logical 0 Input Current ports 1, 2 and 3                     |                                                                         |        | -50                                                 | μA          | Vin = 0.45 V                                                                                                       |

| I <sub>LI</sub>                   | Input Leakage Current                                        |                                                                         |        | ±10                                                 | μA          | 0.45 V < Vin < V <sub>CC</sub>                                                                                     |

| I <sub>TL</sub>                   | Logical 1 to 0 Transition Current, ports 1, 2, 3             |                                                                         |        | -650                                                | μA          | Vin = 2.0 V                                                                                                        |

| C <sub>IO</sub>                   | Capacitance of I/O Buffer                                    |                                                                         |        | 10                                                  | pF          | Fc = 1 MHz<br>Ta = 25°C                                                                                            |

| I <sub>PD</sub>                   | Power Down Current                                           |                                                                         | 20 (5) | 50                                                  | μA          | $2.0 \text{ V} < \text{V}_{\text{CC}} < 5.5 \text{ V}^{(3)}$                                                       |

| I <sub>CC</sub><br>under<br>RESET | Power Supply Current Maximum values, X1 mode: <sup>(7)</sup> |                                                                         |        | 1 + 0.4 Freq<br>(MHz)<br>@12MHz 5.8<br>@16MHz 7.4   | mA          | $V_{\rm CC} = 5.5 \ V^{(1)}$                                                                                       |

| I <sub>CC</sub><br>operating      | Power Supply Current Maximum values, X1 mode: (7)            |                                                                         |        | 3 + 0.6 Freq<br>(MHz)<br>@12MHz 10.2<br>@16MHz 12.6 | mA          | V <sub>CC</sub> = 5.5 V <sup>(8)</sup>                                                                             |

$V_{IH} = V_{CC} - 0.5V$ ; XTAL2 N.C.;  $\overline{EA} = RST = Port 0 = V_{CC}$ .  $I_{CC}$  would be slightly higher if a crystal oscillator used..

- 2. Idle I<sub>CC</sub> is measured with all output pins disconnected; XTAL1 driven with T<sub>CLCH</sub>, T<sub>CHCL</sub> = 5 ns,  $V_{IL} = V_{SS} + 0.5 V$ ,  $V_{IH} = V_{CC} 0.5 V$ ; XTAL2 N.C; Port 0 =  $V_{CC}$ ; EA = RST =  $V_{SS}$  (see Figure 14-3.).

- Power Down I<sub>CC</sub> is measured with all output pins disconnected; EA = V<sub>SS</sub>, PORT 0 = V<sub>CC</sub>; XTAL2 NC.; RST = V<sub>SS</sub> (see Figure 14-4.).

- 4. Capacitance loading on Ports 0 and 2 may cause spurious noise pulses to be superimposed on the V<sub>OL</sub>s of ALE and Ports 1 and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins make 1 to 0 transitions during bus operation. In the worst cases (capacitive loading 100pF), the noise pulse on the ALE line may exceed 0.45V with maxi V<sub>OL</sub> peak 0.6V. A Schmitt Trigger use is not necessary.

- Typicals are based on a limited number of samples and are not guaranteed. The values listed are at room temperature and 5V.

- 6. Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows: Maximum I<sub>OL</sub> per port pin: 10 mA Maximum I<sub>OL</sub> per 8-bit port: Port 0: 26 mA Ports 1, 2 and 3: 15 mA Maximum total I<sub>OL</sub> for all output pins: 71 mA If I<sub>OL</sub> exceeds the test condition, V<sub>OL</sub> may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 7. For other values, please contact your sales office.

- Operating I<sub>CC</sub> is measured with all output pins disconnected; XTAL1 driven with T<sub>CLCH</sub>, T<sub>CHCL</sub> = 5 ns (see Figure 14-5.), V<sub>IL</sub> = V<sub>SS</sub> + 0.5 V,

$V_{IH} = V_{CC} - 0.5V$ ; XTAL2 N.C.;  $\overrightarrow{EA} = Port 0 = V_{CC}$ ; RST =  $V_{SS}$ . The internal ROM runs the code 80 FE (label: SJMP label). I<sub>CC</sub> would be slightly higher if a crystal oscillator is used. Measurements are made with OTP products when possible, which is the worst case.

All other pins are disconnected.

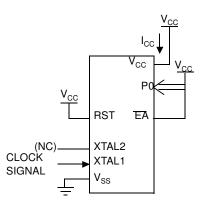

Figure 14-1. I<sub>CC</sub> Test Condition, under reset

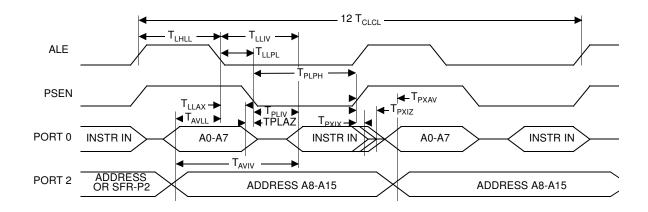

### 14.5.2 External Program Memory Read Cycle

Figure 14-6. External Program Memory Read Cycle

| Table 14-8. | External Data Me | emory Characteristics |

|-------------|------------------|-----------------------|

|-------------|------------------|-----------------------|

| Symbol            | Parameter                   |

|-------------------|-----------------------------|

| T <sub>RLRH</sub> | RD Pulse Width              |

| T <sub>WLWH</sub> | WR Pulse Width              |

| T <sub>RLDV</sub> | RD to Valid Data In         |

| T <sub>RHDX</sub> | Data Hold After RD          |

| T <sub>RHDZ</sub> | Data Float After RD         |

| T <sub>LLDV</sub> | ALE to Valid Data In        |

| T <sub>AVDV</sub> | Address to Valid Data In    |

| T <sub>LLWL</sub> | ALE to WR or RD             |

| T <sub>AVWL</sub> | Address to WR or RD         |

| T <sub>QVWX</sub> | Data Valid to WR Transition |

| T <sub>QVWH</sub> | Data set-up to WR High      |

| T <sub>WHQX</sub> | Data Hold After WR          |

| T <sub>RLAZ</sub> | RD Low to Address Float     |

| T <sub>WHLH</sub> | RD or WR High to ALE high   |

| Table 14-9. | AC Parameters for a Fix Clock |

|-------------|-------------------------------|

|             |                               |

| Speed             |     | M<br>MHz | X2 n<br>30 l | V<br>node<br>MHz<br>z equiv. | standard | V<br>  mode 40<br>Hz | X2 r<br>20 | L<br>node<br>MHz<br>z equiv. | standa | L<br>′d mode<br>MHz | Units |

|-------------------|-----|----------|--------------|------------------------------|----------|----------------------|------------|------------------------------|--------|---------------------|-------|

| Symbol            | Min | Max      | Min          | Max                          | Min      | Max                  | Min        | Max                          | Min    | Max                 |       |

| T <sub>RLRH</sub> | 130 |          | 85           |                              | 135      |                      | 125        |                              | 175    |                     | ns    |

| T <sub>WLWH</sub> | 130 |          | 85           |                              | 135      |                      | 125        |                              | 175    |                     | ns    |

| T <sub>RLDV</sub> |     | 100      |              | 60                           |          | 102                  |            | 95                           |        | 137                 | ns    |

| T <sub>RHDX</sub> | 0   |          | 0            |                              | 0        |                      | 0          |                              | 0      |                     | ns    |

| T <sub>RHDZ</sub> |     | 30       |              | 18                           |          | 35                   |            | 25                           |        | 42                  | ns    |

| T <sub>LLDV</sub> |     | 160      |              | 98                           |          | 165                  |            | 155                          |        | 222                 | ns    |

| T <sub>AVDV</sub> |     | 165      |              | 100                          |          | 175                  |            | 160                          |        | 235                 | ns    |

| T <sub>LLWL</sub> | 50  | 100      | 30           | 70                           | 55       | 95                   | 45         | 105                          | 70     | 130                 | ns    |

| T <sub>AVWL</sub> | 75  |          | 47           |                              | 80       |                      | 70         |                              | 103    |                     | ns    |

| T <sub>QVWX</sub> | 10  |          | 7            |                              | 15       |                      | 5          |                              | 13     |                     | ns    |

| T <sub>QVWH</sub> | 160 |          | 107          |                              | 165      |                      | 155        |                              | 213    |                     | ns    |

| T <sub>WHQX</sub> | 15  |          | 9            |                              | 17       |                      | 10         |                              | 18     |                     | ns    |

| T <sub>RLAZ</sub> |     | 0        |              | 0                            |          | 0                    |            | 0                            |        | 0                   | ns    |

| T <sub>WHLH</sub> | 10  | 40       | 7            | 27                           | 15       | 35                   | 5          | 45                           | 13     | 53                  | ns    |

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | -М | -V | -L | Units |

|-------------------|------|-------------------|-----------|----|----|----|-------|

| T <sub>RLRH</sub> | Min  | 6 T - x           | 3 T - x   | 20 | 15 | 25 | ns    |

| T <sub>WLWH</sub> | Min  | 6 T - x           | 3 T - x   | 20 | 15 | 25 | ns    |

| T <sub>RLDV</sub> | Мах  | 5 T - x           | 2.5 T - x | 25 | 23 | 30 | ns    |

| T <sub>RHDX</sub> | Min  | х                 | х         | 0  | 0  | 0  | ns    |

| T <sub>RHDZ</sub> | Мах  | 2 T - x           | T - x     | 20 | 15 | 25 | ns    |

| T <sub>LLDV</sub> | Мах  | 8 T - x           | 4T -x     | 40 | 35 | 45 | ns    |

| T <sub>AVDV</sub> | Мах  | 9 T - x           | 4.5 T - x | 60 | 50 | 65 | ns    |

| T <sub>LLWL</sub> | Min  | 3 T - x           | 1.5 T - x | 25 | 20 | 30 | ns    |

| T <sub>LLWL</sub> | Мах  | 3 T + x           | 1.5 T + x | 25 | 20 | 30 | ns    |

| T <sub>AVWL</sub> | Min  | 4 T - x           | 2 T - x   | 25 | 20 | 30 | ns    |

| T <sub>QVWX</sub> | Min  | T - x             | 0.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>QVWH</sub> | Min  | 7 T - x           | 3.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>WHQX</sub> | Min  | T - x             | 0.5 T - x | 10 | 8  | 15 | ns    |

| T <sub>RLAZ</sub> | Мах  | x                 | х         | 0  | 0  | 0  | ns    |

| T <sub>WHLH</sub> | Min  | T - x             | 0.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>WHLH</sub> | Max  | T + x             | 0.5 T + x | 15 | 10 | 20 | ns    |

Table 14-10. AC Parameters for a Variable Clock: derating formula

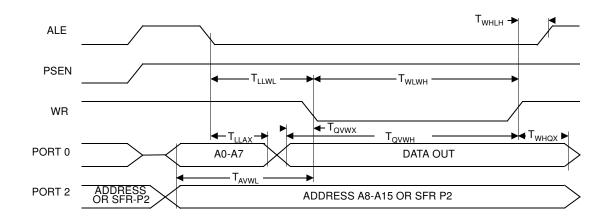

### 14.5.3 External Data Memory Write Cycle

Figure 14-7. External Data Memory Write Cycle

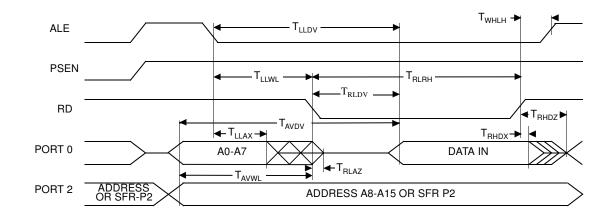

### 14.5.4 External Data Memory Read Cycle

Figure 14-8. External Data Memory Read Cycle

| Table 14-11. | Serial Port Timing - | Shift Register Mode |

|--------------|----------------------|---------------------|

|--------------|----------------------|---------------------|

| Symbol            | Parameter                                |

|-------------------|------------------------------------------|

| T <sub>XLXL</sub> | Serial port clock cycle time             |

| T <sub>QVHX</sub> | Output data set-up to clock rising edge  |

| T <sub>XHQX</sub> | Output data hold after clock rising edge |

| T <sub>XHDX</sub> | Input data hold after clock rising edge  |

| T <sub>XHDV</sub> | Clock rising edge to input data valid    |

Table 14-12. AC Parameters for a Fix Clock

| Speed             | -M<br>40 MHz |     | -V<br>X2 mode<br>30 MHz<br>60 MHz equiv. |     | -V<br>standard mode 40<br>MHz |     | -L<br>X2 mode<br>20 MHz<br>40 MHz equiv. |     | -L<br>standard mode<br>30 MHz |     | Units |

|-------------------|--------------|-----|------------------------------------------|-----|-------------------------------|-----|------------------------------------------|-----|-------------------------------|-----|-------|

| Symbol            | Min          | Max | Min                                      | Max | Min                           | Max | Min                                      | Max | Min                           | Max |       |

| T <sub>XLXL</sub> | 300          |     | 200                                      |     | 300                           |     | 300                                      |     | 400                           |     | ns    |

| Т <sub>QVHX</sub> | 200          |     | 117                                      |     | 200                           |     | 200                                      |     | 283                           |     | ns    |

| T <sub>XHQX</sub> | 30           |     | 13                                       |     | 30                            |     | 30                                       |     | 47                            |     | ns    |

| T <sub>XHDX</sub> | 0            |     | 0                                        |     | 0                             |     | 0                                        |     | 0                             |     | ns    |

| T <sub>XHDV</sub> |              | 117 |                                          | 34  |                               | 117 |                                          | 117 |                               | 200 | ns    |

# AT/TS80C31X2

| Part Number <sup>(3)</sup> | Memory Size | Supply Voltage | Temperature<br>Range | Max Frequency         | Package | Packing |

|----------------------------|-------------|----------------|----------------------|-----------------------|---------|---------|

| AT80C31X2-3CSUV            | ROMLess     | 5V ±10%        | Industrial & Green   | 60 MHz <sup>(3)</sup> | PDIL40  | Stick   |

| AT80C31X2-SLSUV            | ROMLess     | 5V ±10%        | Industrial & Green   | 60 MHz <sup>(3)</sup> | PLCC44  | Stick   |

| AT80C31X2-RLTUV            | ROMLess     | 5V ±10%        | Industrial & Green   | 60 MHz <sup>(3)</sup> | VQFP44  | Tray    |

Notes: 1. 20 MHz in X2 Mode.

2. Tape and Reel available for SL, PQFP and RL packages.

3. 30 MHz in X2 Mode.

### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

### **Atmel Operations**

Memory

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

### **Microcontrollers**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

### Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

*Literature Requests* www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically providedotherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, or warranted for use as components in applications intended to support or sustain life.

© Atmel Corporation 2008. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, are registered trademarks, and Everywhere You Are<sup>®</sup> are the trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.