Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | 8051                                                                      |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 18MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 2KB (2K x 8)                                                              |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                               |

| Data Converters            | A/D 4x8b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                           |

| Supplier Device Package    | 14-TSSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p89lpc9151fdh-129 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

8-bit microcontroller with 8-bit ADC

### 3. Ordering information

### Table 1. Ordering information

|               | ·<br>   |                                                                        |          |  |  |  |  |  |

|---------------|---------|------------------------------------------------------------------------|----------|--|--|--|--|--|

| Type number   | Package | Package                                                                |          |  |  |  |  |  |

|               | Name    | Description                                                            | Version  |  |  |  |  |  |

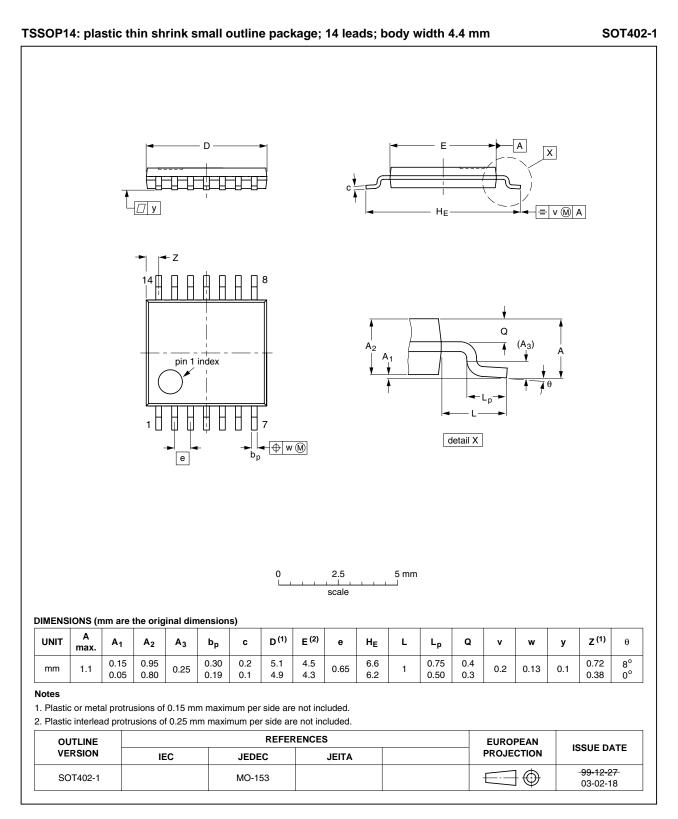

| P89LPC9151FDH | TSSOP14 | plastic thin shrink small outline package; 14 leads; body width 4.4 mm | SOT402-1 |  |  |  |  |  |

| P89LPC9161FDH | TSSOP16 | plastic thin shrink small outline package; 16 leads; body width 4.4 mm | SOT403-1 |  |  |  |  |  |

| P89LPC9171FDH | TSSOP16 | plastic thin shrink small outline package; 16 leads; body width 4.4 mm | SOT403-1 |  |  |  |  |  |

### 3.1 Ordering options

### Table 2. Ordering options

| Type number   | Flash memory | Temperature range | Frequency       |

|---------------|--------------|-------------------|-----------------|

| P89LPC9151FDH | 2 kB         | –40 °C to +85 °C  | 0 MHz to 18 MHz |

| P89LPC9161FDH | 2 kB         | –40 °C to +85 °C  | 0 MHz to 18 MHz |

| P89LPC9171FDH | 2 kB         | –40 °C to +85 °C  | 0 MHz to 18 MHz |

P89LPC9151\_61\_71\_2

8-bit microcontroller with 8-bit ADC

P89LPC9151\_61\_71\_2

8-bit microcontroller with 8-bit ADC

### 6.2 Pin description

| Symbol             | Pin     | Туре                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------|---------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | TSSOP14 | -                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| P0.0 to P0.5       |         | I/O                   | <b>Port 0:</b> Port 0 is an 6-bit I/O port with a user-configurable output type. During reset Port 0 latches are configured in the input only mode with the internal pull-up disabled. The operation of Port 0 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to <u>Section 7.15.1 "Port configurations"</u> and <u>Table 16 "Static characteristics"</u> for details.                                                                                                                                                                            |

|                    |         |                       | The Keypad Interrupt feature operates with Port 0 pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                    |         |                       | All pins have Schmitt trigger inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                    |         |                       | Port 0 also provides various special functions as described below:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| P0.0/CMP2/         | 2       | I/O                   | <b>P0.0</b> — Port 0 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| KBI0               |         | 0                     | CMP2 — Comparator 2 output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                    |         | Ι                     | KBI0 — Keyboard input 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P0.1/CIN2B/        | 1       | I/O                   | <b>P0.1</b> — Port 0 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| KBI1/AD10          |         | I                     | CIN2B — Comparator 2 positive input B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    |         | I                     | KBI1 — Keyboard input 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    |         | I                     | AD10 — ADC1 channel 0 analog input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P0.2/CIN2A/        | 14      | I/O                   | <b>P0.2</b> — Port 0 bit 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| KBI2/AD11          |         | I                     | CIN2A — Comparator 2 positive input A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    |         | I                     | KBI2 — Keyboard input 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    |         | I                     | AD11 — ADC1 channel 1 analog input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P0.3/CIN1B/        | 13      | I/O                   | P0.3 — Port 0 bit 3. High current source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| KBI3/AD12          |         | I                     | CIN1B — Comparator 1 positive input B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    |         | I                     | KBI3 — Keyboard input 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    |         | I                     | AD12 — ADC1 channel 2 analog input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P0.4/CIN1A/        | 12      | I/O                   | P0.4 — Port 0 bit 4. High current source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| KBI4/DAC1/AD13     |         | I                     | CIN1A — Comparator 1 positive input A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    |         | I                     | KBI4 — Keyboard input 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    |         | 0                     | DAC1 — Digital-to-analog converter output 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                    |         | I                     | AD13 — ADC1 channel 3 analog input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P0.5/CMPREF/       | 11      | I/O                   | P0.5 — Port 0 bit 5. High current source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| KBI5               |         | I                     | CMPREF — Comparator reference (negative) input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                    |         | I                     | KBI5 — Keyboard input 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    |         | I                     | CLKIN — External clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| P1.0 to P1.5       |         | I/O, I<br>[ <u>1]</u> | <b>Port 1:</b> Port 1 is an 6-bit I/O port with a user-configurable output type, except for three pins as noted below. During reset Port 1 latches are configured in the input only mode with the internal pull-up disabled. The operation of the configurable Port 1 pins as inputs and outputs depends upon the port configuration selected. Each of the configurable port pins are programmed independently. Refer to Section 7.15.1 "Port configurations" and Table 16 "Static characteristics" for details. P1.2 to P1.3 are open drain when used as outputs. P1.5 is input only. All pins have Schmitt trigger inputs. |

|                    |         |                       | Port 1 also provides various special functions as described below:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| P89LPC9151_61_71_2 |         |                       | © NXP B.V. 2010. All rights reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| NXP   |

|-------|

| Semic |

| onduc |

| ctors |

| œ        |  |

|----------|--|

| -<br>bit |  |

| З        |  |

| icro     |  |

| ocor     |  |

| ₹        |  |

| olle     |  |

| erv      |  |

| vith     |  |

| œ        |  |

| bit      |  |

| ADC      |  |

#### Extended special function registers - P89LPC9161[1] Table 9.

| Name    | Description                              | SFR   | Bit functions | s and add | esses |   |        |       |         |         | Rese | t value   |

|---------|------------------------------------------|-------|---------------|-----------|-------|---|--------|-------|---------|---------|------|-----------|

| Name    |                                          | addr. | MSB           |           |       |   |        |       |         | LSB     | Hex  | Binary    |

| BODCFG  | BOD<br>configuration<br>register         | FFC8H | -             | -         | -     | - | -      | -     | BOICFG1 | BOICFG0 | [2]  |           |

| CLKCON  | CLOCK Control<br>register                | FFDEH | CLKOK         | -         | -     | - | CLKDBL | FOSC2 | FOSC1   | FOSC0   | [3]  |           |

| RTCDATH | Real-time clock<br>data register<br>high | FFBFH |               |           |       |   |        |       |         |         | 00   | 0000 0000 |

| RTCDATL | Real-time clock data register low        | FFBEH |               |           |       |   |        |       |         |         | 00   | 0000 0000 |

[1] Extended SFRs are physically located on-chip but logically located in external data memory address space (XDATA). The MOVX A, @DPTR and MOVX @DPTR, A instructions are used to access these extended SFRs.

[2] The BOICFG1/0 will be copied from UCFG1.5 and UCFG1.3 when power-on reset.

[3] CLKCON register reset value comes from UCFG1 and UCFG2. The reset value of CLKCON.2 to CLKCON.0 come from UCFG1.2 to UCFG1.0 and reset value of CLKDBL bit comes from UCFG2.7.

Product data sheet

#### 8-bit microcontroller with 8-bit ADC

### 7.15 I/O ports

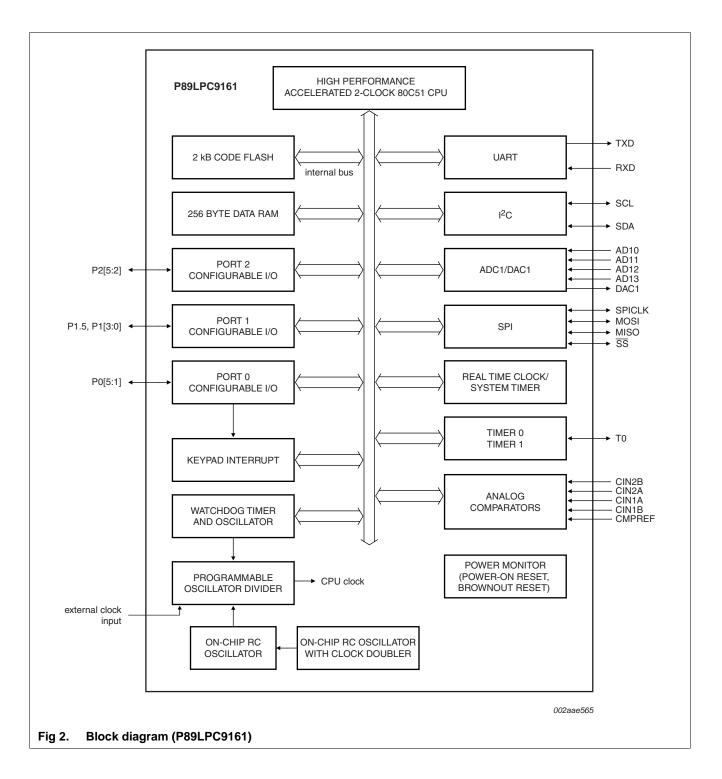

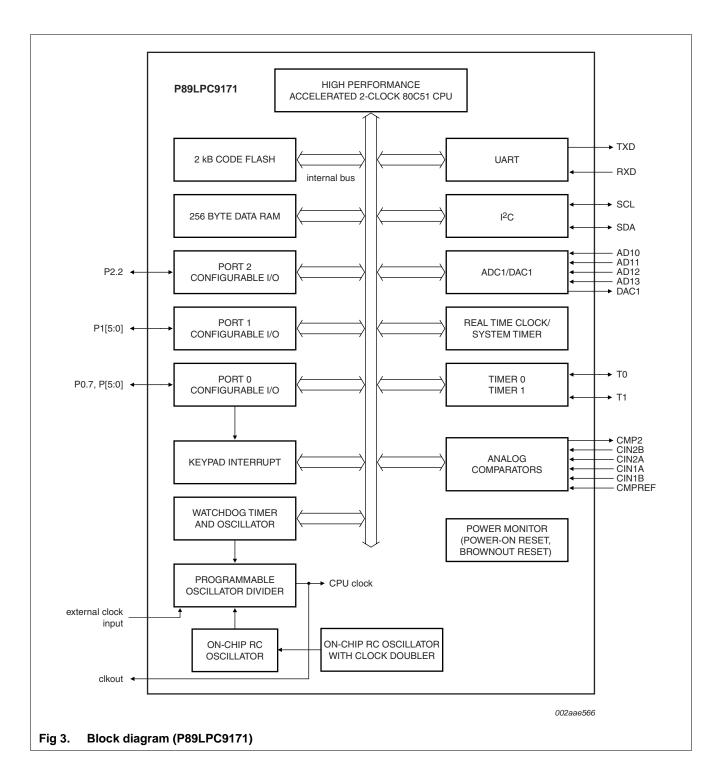

The P89LPC9151 has two I/O ports: Port 0 and Port 1. Ports 0 and 1 are both 6-bit ports. The P89LPC9161/9171 has three I/O ports: Port 0, Port 1 and Port 2. Ports 0 is 5-bit ports in the P89LPC9161 and 7-bit ports in the P89LPC9171, Port 1 is 5-bit ports in the P89LPC9161 and 6-bit ports in the P89LPC9171, Port 2 is 4-bit ports in the P89LPC9161 and 1-bit port in the P89LPC9171. The exact number of I/O pins available depends upon the clock and reset options chosen, as shown in Table 13 and Table 14

| Clock source                         | Reset option                                  | Number of I/O<br>pins (14-pin<br>package) |

|--------------------------------------|-----------------------------------------------|-------------------------------------------|

| RC oscillator or watchdog oscillator | No external reset (except during<br>power-up) | 12                                        |

|                                      | External RST pin supported                    | 11                                        |

| External clock input                 | No external reset (except during<br>power-up) | 11                                        |

|                                      | External RST pin supported <sup>[1]</sup>     | 10                                        |

### Table 13. Number of I/O pins available (P89LPC9151)

[1] Required for operation above 12 MHz.

| Clock source                         | Reset option                               | Number of I/O<br>pins (16-pin<br>package) |

|--------------------------------------|--------------------------------------------|-------------------------------------------|

| RC oscillator or watchdog oscillator | No external reset (except during power-up) | 14                                        |

|                                      | External RST pin supported                 | 13                                        |

| External clock input                 | No external reset (except during power-up) | 13                                        |

|                                      | External RST pin supported <sup>[1]</sup>  | 12                                        |

#### Table 14. Number of I/O pins available (P89LPC9161 and P89LPC9171)

[1] Required for operation above 12 MHz.

#### 7.15.1 Port configurations

All but three I/O port pins on the P89LPC9151/9161/9171 may be configured by software to one of four types on a bit-by-bit basis. These are: quasi-bidirectional (standard 80C51 port outputs), push-pull, open drain, and input-only. Two configuration registers for each port select the output type for each port pin.

- 1. P1.5 ( $\overline{RST}$ ) can only be an input and cannot be configured.

- P1.2 (SCL/T0) and P1.3 (SDA/INT0) may only be configured to be either input-only or open-drain.

#### 7.15.1.1 Quasi-bidirectional output configuration

Quasi-bidirectional output type can be used as both an input and output without the need to reconfigure the port. This is possible because when the port outputs a logic HIGH, it is weakly driven, allowing an external device to pull the pin LOW. When the pin is driven

8-bit microcontroller with 8-bit ADC

### 7.17.2 Power-down mode

The Power-down mode stops the oscillator in order to minimize power consumption. The P89LPC9151/9161/9171 exits Power-down mode via any reset, or certain interrupts. In Power-down mode, the power supply voltage may be reduced to the data retention supply voltage  $V_{DDR}$ . This retains the RAM contents at the point where Power-down mode was entered. SFR contents are not guaranteed after  $V_{DD}$  has been lowered to  $V_{DDR}$ , therefore it is highly recommended to wake-up the processor via reset in this case.  $V_{DD}$  must be raised to within the operating range before the Power-down mode is exited.

Some chip functions continue to operate and draw power during Power-down mode, increasing the total power used during power-down. These include: Brownout detect, watchdog timer, comparators (note that comparators can be powered down separately), and RTC/system timer. The internal RC oscillator is disabled unless both the RC oscillator has been selected as the system clock and the RTC is enabled.

### 7.17.3 Total Power-down mode

This is the same as Power-down mode except that the brownout detection circuitry and the voltage comparators are also disabled to conserve additional power. The internal RC oscillator is disabled unless both the RC oscillator has been selected as the system clock **and** the RTC is enabled. If the internal RC oscillator is used to clock the RTC during power-down, there will be high power consumption. Please use an external low frequency clock to achieve low power with the RTC running during power-down.

### 7.18 Reset

The P1.5/RST pin can function as either a LOW-active reset input or as a digital input, P1.5. The Reset Pin Enable (RPE) bit in UCFG1, when set to logic 1, enables the external reset input function on P1.5. When cleared, P1.5 may be used as an input pin.

**Remark:** During a power-up sequence, the RPE selection is overridden and this pin always functions as a reset input. **An external circuit connected to this pin should not hold this pin LOW during a power-on sequence as this will keep the device in reset.** After power-up this pin will function as defined by the RPE bit. Only a power-up reset will temporarily override the selection defined by RPE bit. Other sources of reset will not override the RPE bit.

**Note:** During a power cycle,  $V_{DD}$  must fall below  $V_{POR}$  before power is reapplied, in order to ensure a power-on reset (see <u>Table 16 "Static characteristics</u>").

Reset can be triggered from the following sources:

- External reset pin (during power-up or if user configured via UCFG1)

- Power-on detect

- Brownout detect

- Watchdog timer

- Software reset

- UART break character detect reset

For every reset source, there is a flag in the Reset Register, RSTSRC. The user can read this register to determine the most recent reset source. These flag bits can be cleared in software by writing a logic 0 to the corresponding bit. More than one flag bit may be set:

8-bit microcontroller with 8-bit ADC

### 7.19.6 Timer overflow toggle output

Timer 0 (and Timer 1 on the P89LPC9171) can be configured to automatically toggle a port output whenever a timer overflow occurs. The same device pins that are used for the T0 and T1 count inputs are also used for the timer toggle outputs. The port outputs will be a logic 1 prior to the first timer overflow when this mode is turned on.

### 7.20 RTC/system timer

The P89LPC9151/9161/9171 has a simple RTC that allows a user to continue running an accurate timer while the rest of the device is powered down. The RTC can be a wake-up or an interrupt source. The RTC is a 23-bit down counter comprised of a 7-bit prescaler and a 16-bit loadable down counter. When it reaches all logic 0s, the counter will be reloaded again and the RTCF flag will be set.

The clock source for this counter can be either the CPU clock (CCLK) or the external clock input, provided that the external clock input is not being used as the CPU clock. If the external clock input is used as the CPU clock, then the RTC will use CCLK as its clock source. Only power-on reset will reset the RTC and its associated SFRs to the default state.

The 16-bit loadable counter portion of the RTC is readable by reading the RTCDATL and RTCDATH registers.

### 7.21 UART

The P89LPC9151/9161/9171 has an enhanced UART that is compatible with the conventional 80C51 UART except that Timer 2 overflow cannot be used as a baud rate source. The P89LPC9151/9161/9171 does include an independent baud rate generator. The baud rate can be selected from the oscillator (divided by a constant), Timer 1 overflow, or the independent baud rate generator. In addition to the baud rate generation, enhancements over the standard 80C51 UART include Framing Error detection, automatic address recognition, selectable double buffering and several interrupt options. The UART can be operated in four modes: shift register, 8-bit UART, 9-bit UART, and CPU clock/32 or CPU clock/16.

#### 7.21.1 Mode 0

Serial data enters and exits through RXD. TXD outputs the shift clock. 8 bits are transmitted or received, LSB first. The baud rate is fixed at  $1_{16}$  of the CPU clock frequency.

#### 7.21.2 Mode 1

10 bits are transmitted (through TXD) or received (through RXD): a start bit (logic 0), 8 data bits (LSB first), and a stop bit (logic 1). When data is received, the stop bit is stored in RB8 in special function register SCON. The baud rate is variable and is determined by the Timer 1 overflow rate or the baud rate generator (described in <u>Section 7.21.5 "Baud</u> rate generator and selection").

### 7.21.3 Mode 2

11 bits are transmitted (through TXD) or received (through RXD): start bit (logic 0), 8 data bits (LSB first), a programmable 9<sup>th</sup> data bit, and a stop bit (logic 1). When data is transmitted, the 9<sup>th</sup> data bit (TB8 in SCON) can be assigned the value of logic 0 or logic 1.

#### 8-bit microcontroller with 8-bit ADC

Double buffering can be disabled. If disabled (DBMOD, i.e., SSTAT.7 = 0), the UART is compatible with the conventional 80C51 UART. If enabled, the UART allows writing to SBUF while the previous data is being shifted out. Double buffering is only allowed in Modes 1, 2 and 3. When operated in Mode 0, double buffering must be disabled (DBMOD = 0).

### 7.21.9 Transmit interrupts with double buffering enabled (modes 1, 2 and 3)

Unlike the conventional UART, in double buffering mode, the TI interrupt is generated when the double buffer is ready to receive new data.

### 7.21.10 The 9<sup>th</sup> bit (bit 8) in double buffering (modes 1, 2 and 3)

If double buffering is disabled TB8 can be written before or after SBUF is written, as long as TB8 is updated some time before that bit is shifted out. TB8 must not be changed until the bit is shifted out, as indicated by the TI interrupt.

If double buffering is enabled, TB **must** be updated before SBUF is written, as TB8 will be double-buffered together with SBUF data.

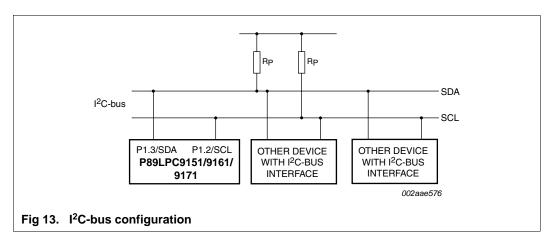

### 7.22 I<sup>2</sup>C-bus serial interface

The I<sup>2</sup>C-bus uses two wires (SDA and SCL) to transfer information between devices connected to the bus, and it has the following features:

- · Bidirectional data transfer between masters and slaves

- Multi master bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer

- The I<sup>2</sup>C-bus may be used for test and diagnostic purposes.

A typical I<sup>2</sup>C-bus configuration is shown in <u>Figure 13</u>. The P89LPC9151/9161/9171 device provides a byte-oriented I<sup>2</sup>C-bus interface that supports data transfers up to 400 kHz.

8-bit microcontroller with 8-bit ADC

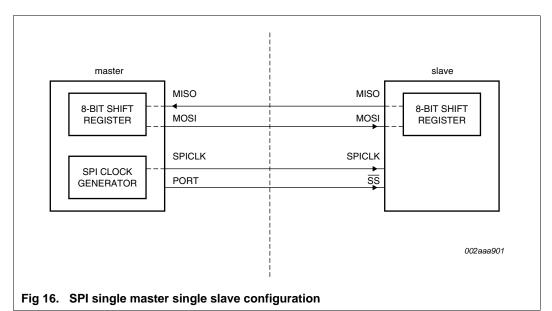

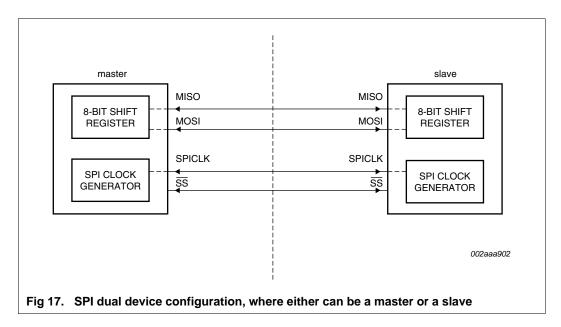

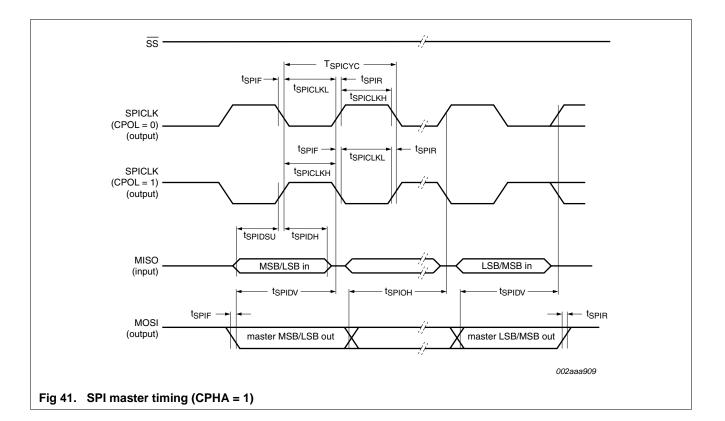

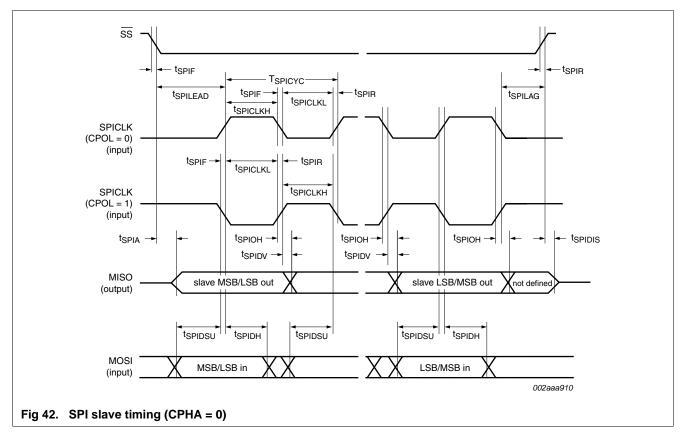

### 7.23.1 Typical SPI configurations

### **NXP Semiconductors**

### P89LPC9151/9161/9171

8-bit microcontroller with 8-bit ADC

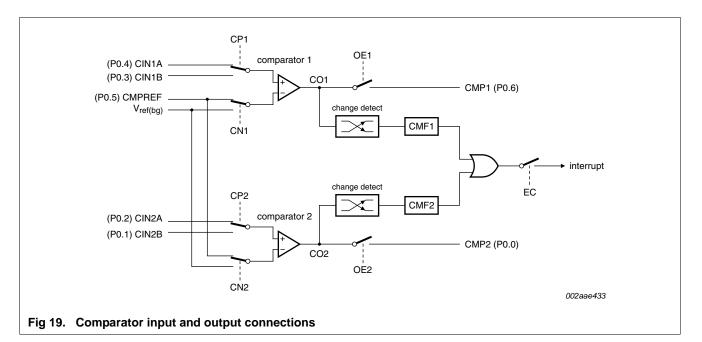

### 7.24.1 Internal reference voltage

An internal reference voltage generator may supply a default reference when a single comparator input pin is used. The value of the internal reference voltage, referred to as  $V_{ref(bg)}$ , is 1.23 V ± 10 %.

### 7.24.2 Comparator interrupt

Each comparator has an interrupt flag contained in its configuration register. This flag is set whenever the comparator output changes state. The flag may be polled by software or may be used to generate an interrupt. The two comparators use one common interrupt vector. If both comparators enable interrupts, after entering the interrupt service routine, the user needs to read the flags to determine which comparator caused the interrupt.

### 7.24.3 Comparators and power reduction modes

Either or both comparators may remain enabled when Power-down or Idle mode is activated, but both comparators are disabled automatically in Total Power-down mode.

If a comparator interrupt is enabled (except in Total Power-down mode), a change of the comparator output state will generate an interrupt and wake-up the processor. If the comparator output to a pin is enabled, the pin should be configured in the push-pull mode in order to obtain fast switching times while in Power-down mode. The reason is that with the **oscillator** stopped, the temporary strong pull-up that normally occurs during switching on a quasi-bidirectional port pin does not take place.

Comparators consume power in Power-down and Idle modes, as well as in the normal operating mode. This fact should be taken into account when system power consumption is an issue. To minimize power consumption, the user can disable the comparators via PCONA.5, or put the device in Total Power-down mode.

### 8-bit microcontroller with 8-bit ADC

P89LPC9151/9161/9171 uses  $V_{DD}$  as the supply voltage to perform the Program/Erase algorithms. When voltage supply is lower than 2.4 V, the BOD FLASH is tripped and flash erase/program is blocked.

### 7.28.2 Features

- Programming and erase over the full operating voltage range.

- Byte erase allows code memory to be used for data storage.

- Read/Programming/Erase using ICP.

- Any flash program/erase operation in 2 ms.

- Programming with industry-standard commercial programmers.

- Programmable security for the code in the flash for each sector.

- 100,000 typical erase/program cycles for each byte.

- 10 year minimum data retention.

### 7.28.3 Flash organization

The program memory consists of eight 256-byte sectors on the P89LPC9151/9161/9171 devices. Each sector can be further divided into 16-byte pages. In addition to sector erase, page erase, and byte erase, a 16-byte page register is included which allows from 1 byte to 16 bytes of a given page to be programmed at the same time, substantially reducing overall programming time. In addition, erasing and reprogramming of user-programmable configuration bytes including UCFG1, the Boot Status Bit, and the Boot Vector is supported.

#### 7.28.4 Using flash as data storage

The flash code memory array of this device supports individual byte erasing and programming. Any byte in the code memory array may be read using the MOVC instruction, provided that the sector containing the byte has not been secured (a MOVC instruction is not allowed to read code memory contents of a secured sector). Thus any byte in a non-secured sector may be used for non-volatile data storage.

### 7.28.5 Flash programming and erasing

Two different methods of erasing or programming of the flash are available. The flash may be programmed or erased in the end-user application (IA-Lite) under control of the application's firmware. Another option is to use the ICP mechanism. This ICP system provides for programming through a serial clock/serial data interface. This device does not provide for direct verification of code memory contents. Instead, this device provides a 32-bit CRC result on either a sector or the entire user code space.

**Remark:** When voltage supply is lower than 2.4 V, the BOD FLASH is tripped and flash erase/program is blocked.

### 7.28.6 ICP

ICP is performed without removing the microcontroller from the system. The ICP facility consists of internal hardware resources to facilitate remote programming of the P89LPC9151/9161/9171 through a two-wire serial interface. The NXP ICP facility has made in-circuit programming in an embedded application - using commercially available programmers - possible with a minimum of additional expense in components and circuit

8-bit microcontroller with 8-bit ADC

### 10. Static characteristics

#### Table 16. Static characteristics

$V_{DD}$  = 2.4 V to 3.6 V unless otherwise specified.

$T_{amb} = -40$  °C to +85 °C for industrial applications, unless otherwise specified.

| Symbol                | Parameter                               | Conditions                                                                                          |      | Min            | Typ <u>[1]</u>     | Max         | Unit |

|-----------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------|------|----------------|--------------------|-------------|------|

| DD(oper)              | operating supply current                | $V_{DD}$ = 3.6 V; $f_{osc}$ = 12 MHz                                                                | [2]  | -              | 10                 | 15          | mA   |

|                       |                                         | V <sub>DD</sub> = 3.6 V; f <sub>osc</sub> = 18 MHz                                                  | [2]  | -              | 14                 | 23          | mA   |

| I <sub>DD(idle)</sub> | Idle mode supply current                | $V_{DD}$ = 3.6 V; f <sub>osc</sub> = 12 MHz                                                         | [3]  | -              | 3.25               | 5           | mA   |

|                       |                                         | V <sub>DD</sub> = 3.6 V; f <sub>osc</sub> = 18 MHz                                                  | [3]  | -              | 5                  | 7           | mA   |

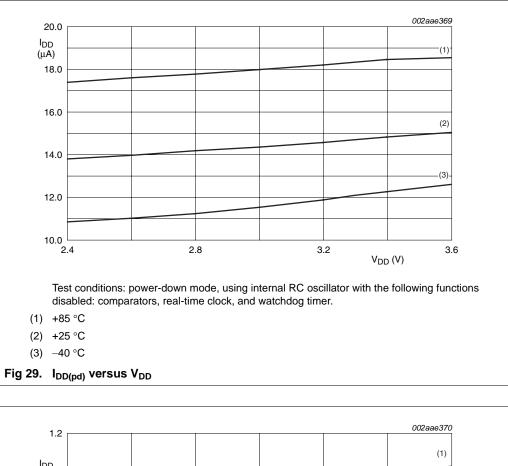

| I <sub>DD(pd)</sub>   | Power-down mode supply current          | V <sub>DD</sub> = 3.6 V; voltage comparators powered down                                           | [4]  | -              | 20                 | 40          | μA   |

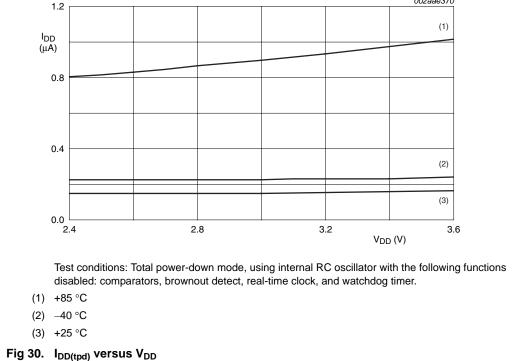

| I <sub>DD(tpd)</sub>  | total Power-down mode<br>supply current | V <sub>DD</sub> = 3.6 V                                                                             | [5]  | -              | 1                  | 5           | μA   |

| (dV/dt) <sub>r</sub>  | rise rate                               | of $V_{DD}$ ; to ensure POR signal                                                                  |      | 5              | -                  | 5000        | V/S  |

| V <sub>DDR</sub>      | data retention supply voltage           |                                                                                                     |      | 1.5            | -                  | -           | V    |

| V <sub>th(HL)</sub>   | HIGH-LOW threshold voltage              | except SCL, SDA                                                                                     |      | $0.22V_{DD}$   | $0.4V_{DD}$        | -           | V    |

| V <sub>IL</sub>       | LOW-level input voltage                 | SCL, SDA only                                                                                       |      | -0.5           | -                  | $0.3V_{DD}$ | V    |

| V <sub>th(LH)</sub>   | LOW-HIGH threshold voltage              | except SCL, SDA                                                                                     |      | -              | 0.6V <sub>DD</sub> | $0.7V_{DD}$ | V    |

| VIH                   | HIGH-level input voltage                | SCL, SDA only                                                                                       |      | $0.7V_{DD}$    | -                  | 5.5         | V    |

| V <sub>hys</sub>      | hysteresis voltage                      | port 1                                                                                              |      | -              | $0.2V_{DD}$        | -           | V    |

| V <sub>OL</sub>       | LOW-level output voltage                | $I_{OL}$ = 20 mA; $V_{DD}$ = 2.4 V to<br>3.6 V all ports, all modes<br>except high-Z                | [6]  | -              | 0.6                | 1.0         | V    |

|                       |                                         | $I_{OL}$ = 3.2 mA; $V_{DD}$ = 2.4 V to<br>3.6 V all ports, all modes<br>except high-Z               | [6]  | -              | 0.2                | 0.3         | V    |

| V <sub>OH</sub>       | HIGH-level output voltage               | $I_{OH} = -20 \ \mu$ A;<br>V <sub>DD</sub> = 2.4 V to 3.6 V; all ports,<br>quasi-bidirectional mode |      | $V_{DD} - 0.3$ | $V_{DD} - 0.2$     | -           | V    |

|                       |                                         | $I_{OH} = -3.2$ mA;<br>$V_{DD} = 2.4$ V to 3.6 V; all ports,<br>push-pull mode                      |      | $V_{DD}-0.7$   | $V_{DD}-0.4$       | -           | V    |

|                       |                                         | $I_{OH} = -10$ mA;<br>$V_{DD} = 2.4$ V to 3.6 V; all ports,<br>push-pull mode                       |      | -              | 3.2                | -           | V    |

| Vn                    | voltage on any other pin                | except $V_{\text{DD}};$ with respect to $V_{\text{SS}}$                                             | [7]  | -0.5           | -                  | +5.5        | V    |

| C <sub>iss</sub>      | input capacitance                       |                                                                                                     | [8]  | -              | -                  | 15          | pF   |

| IIL                   | LOW-level input current                 | $V_{I} = 0.4 V$                                                                                     | [9]  | -              | -                  | -80         | μA   |

| ILI                   | input leakage current                   | $V_I = V_{IL}, V_{IH}, \text{ or } V_{th(HL)}$                                                      | [10] | -              | -                  | ±1          | μA   |

| I <sub>THL</sub>      | HIGH-LOW transition<br>current          | all ports; V <sub>I</sub> = 1.5 V at $V_{DD}$ = 3.6 V                                               | [11] | -30            | -                  | -450        | μA   |

8-bit microcontroller with 8-bit ADC

### Table 16. Static characteristics ... continued

$V_{DD} = 2.4$  V to 3.6 V unless otherwise specified.

$T_{amb} = -40 \text{ }^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$  for industrial applications, unless otherwise specified.

| Symbol                  | Parameter                                          | Conditions | Min  | Typ <u>[1]</u> | Max  | Unit       |

|-------------------------|----------------------------------------------------|------------|------|----------------|------|------------|

| R <sub>RST_N(int)</sub> | interna <u>l pull</u> -up resistance<br>on pin RST | pin RST    | 10   | -              | 30   | kΩ         |

| V <sub>ref(bg)</sub>    | band gap reference voltage                         |            | 1.11 | 1.23           | 1.34 | V          |

| TC <sub>bg</sub>        | band gap temperature coefficient                   |            | -    | 10             | 20   | ppm/<br>°C |

[1] Typical ratings are not guaranteed. The values listed are at room temperature, 3 V.

[2] The IDD(oper) specification is measured using an external clock with code while(1) {} executed from on-chip flash.

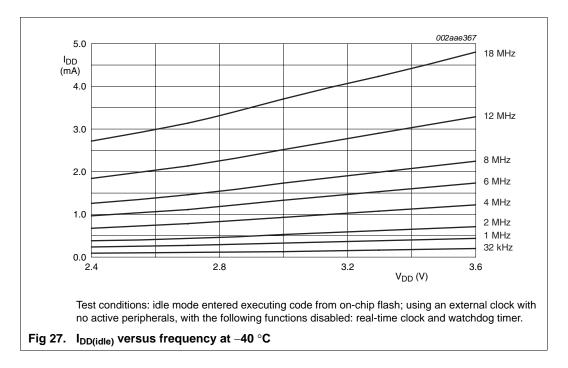

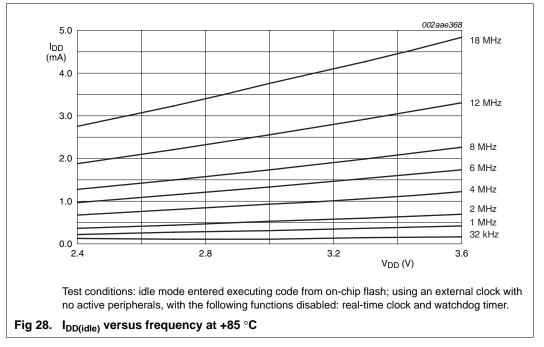

[3] The I<sub>DD(idle)</sub> specification is measured using an external clock with no active peripherals, with the following functions disabled: real-time clock and watchdog timer.

[4] The I<sub>DD(pd)</sub> specification is measured using internal RC oscillator with the following functions disabled: comparators, real-time clock, and watchdog timer.

- [5] The I<sub>DD(tpd)</sub> specification is measured using an external clock with the following functions disabled: comparators, real-time clock, brownout detect, and watchdog timer.

- [6] See Section 9 "Limiting values" for steady state (non-transient) limits on I<sub>OL</sub> or I<sub>OH</sub>. If I<sub>OL</sub>/I<sub>OH</sub> exceeds the test condition, V<sub>OL</sub>/V<sub>OH</sub> may exceed the related specification.

- [7] This specification can be applied to pins which have A/D input or analog comparator input functions when the pin is not being used for those analog functions. When the pin is being used as an analog input pin, the maximum voltage on the pin must be limited to 4.0 V with respect to V<sub>SS</sub>.

- [8] Pin capacitance is characterized but not tested.

- [9] Measured with port in quasi-bidirectional mode.

- [10] Measured with port in high-impedance mode.

- [11] Port pins source a transition current when used in quasi-bidirectional mode and externally driven from logic 1 to logic 0. This current is highest when V<sub>1</sub> is approximately 2 V.

### **NXP Semiconductors**

### P89LPC9151/9161/9171

8-bit microcontroller with 8-bit ADC

### 13. Package outline

Fig 46. TSSOP14 package outline (SOT402-1)

P89LPC9151\_61\_71\_2

8-bit microcontroller with 8-bit ADC

| 8.4.2<br>8.4.3<br>8.4.4<br>8.4.5<br>8.4.6<br>8.5<br>8.5.1<br>8.5.2<br>8.5.3<br>8.6<br>8.7 | Fixed channel, continuous conversion mode .61Auto scan, single conversion mode .61Auto scan, continuous conversion mode .61Dual channel, continuous conversion mode .62Single step mode .62Conversion start modes .62Timer triggered start .62Start immediately .62Edge triggered .62Boundary limits interrupt .62DAC output to a port pin with high output |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                           | impedance                                                                                                                                                                                                                                                                                                                                                   |

| 8.8                                                                                       | Clock divider                                                                                                                                                                                                                                                                                                                                               |

| 8.9                                                                                       | Power-down and Idle mode                                                                                                                                                                                                                                                                                                                                    |

| 9                                                                                         | Limiting values 64                                                                                                                                                                                                                                                                                                                                          |

| 10                                                                                        | Static characteristics 65                                                                                                                                                                                                                                                                                                                                   |

| 10.1                                                                                      | Current characteristics 67                                                                                                                                                                                                                                                                                                                                  |

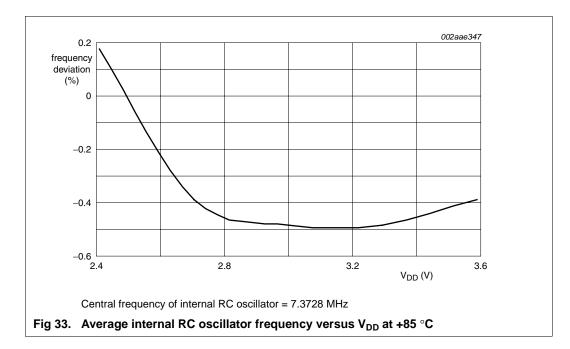

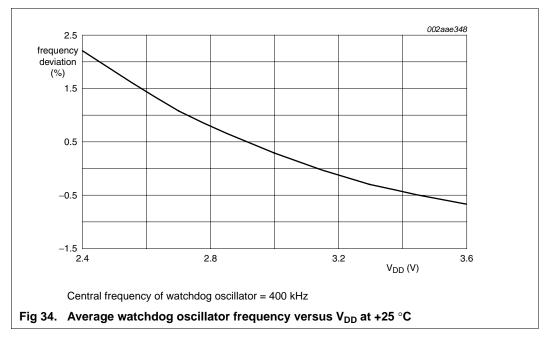

| 10.2                                                                                      | Internal RC/watchdog oscillator characteristics 71                                                                                                                                                                                                                                                                                                          |

| 10.3                                                                                      | BOD characteristics 74                                                                                                                                                                                                                                                                                                                                      |

| 11                                                                                        | Dynamic characteristics 75                                                                                                                                                                                                                                                                                                                                  |

| 11.1                                                                                      | Waveforms 79                                                                                                                                                                                                                                                                                                                                                |

| 12                                                                                        | Other characteristics 81                                                                                                                                                                                                                                                                                                                                    |

| 12.1                                                                                      | Comparator electrical characteristics 81                                                                                                                                                                                                                                                                                                                    |

| 12.2                                                                                      | ADC electrical characteristics                                                                                                                                                                                                                                                                                                                              |

| 13                                                                                        | Package outline 84                                                                                                                                                                                                                                                                                                                                          |

| 14                                                                                        | Abbreviations                                                                                                                                                                                                                                                                                                                                               |

| 15                                                                                        | Revision history 87                                                                                                                                                                                                                                                                                                                                         |

| 16                                                                                        | Legal information 88                                                                                                                                                                                                                                                                                                                                        |

| 16.1                                                                                      | Data sheet status 88                                                                                                                                                                                                                                                                                                                                        |

| 16.2                                                                                      | Definitions                                                                                                                                                                                                                                                                                                                                                 |

| 16.3                                                                                      | Disclaimers                                                                                                                                                                                                                                                                                                                                                 |

| 16.4                                                                                      | Trademarks 89                                                                                                                                                                                                                                                                                                                                               |

| 17                                                                                        | Contact information 89                                                                                                                                                                                                                                                                                                                                      |

| 18                                                                                        | Contents 90                                                                                                                                                                                                                                                                                                                                                 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2010.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 9 February 2010 Document identifier: P89LPC9151\_61\_71\_2