Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M0                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 50MHz                                                                      |

| Connectivity               | I²C, SPI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 28                                                                         |

| Program Memory Size        | 8KB (8K x 8)                                                               |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 32-HVQFN (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1111fhn33-202-5 |

|                            |                                                                            |

Table 1.

Ordering information ...continued

| Type number      | Package |                                                                                                  |           |  |  |  |  |  |  |

|------------------|---------|--------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|--|

|                  | Name    | Description                                                                                      | Version   |  |  |  |  |  |  |

| LPC1115JBD48/303 | LQFP48  | LQFP48: plastic low profile quad flat package; 48 leads; body 7 $\times$ 7 $\times$ 1.4 mm       | SOT313-2  |  |  |  |  |  |  |

| LPC1115FET48/303 | TFBGA48 | plastic thin fine-pitch ball grid array package; 48 balls; body 4.5 $\times$ 4.5 $\times$ 0.7 mm | SOT1155-2 |  |  |  |  |  |  |

| LPC1115JET48/303 | TFBGA48 | plastic thin fine-pitch ball grid array package; 48 balls; body 4.5 $\times$ 4.5 $\times$ 0.7 mm | SOT1155-2 |  |  |  |  |  |  |

## 4.1 Ordering options

Table 2. Ordering options

| Type number      | Series    | Flash | Total<br>SRAM | Power profiles | UART | I <sup>2</sup> C/<br>Fast+ | SPI | ADC channel | GPIO | Package | Temp <sup>[1]</sup> |

|------------------|-----------|-------|---------------|----------------|------|----------------------------|-----|-------------|------|---------|---------------------|

| LPC1110          |           |       |               |                |      |                            |     |             |      | 1       |                     |

| LPC1110FD20      | LPC1100L  | 4 kB  | 1 kB          | yes            | 1    | 1                          | 1   | 5           | 16   | SO20    | F                   |

| LPC1111          |           |       |               |                |      |                            |     |             |      |         |                     |

| LPC1111FDH20/002 | LPC1100L  | 8 kB  | 2 kB          | yes            | 1    | 1                          | 1   | 5           | 16   | TSSOP20 | F                   |

| LPC1111FHN33/101 | LPC1100   | 8 kB  | 2 kB          | no             | 1    | 1                          | 1   | 8           | 28   | HVQFN33 | F                   |

| LPC1111FHN33/102 | LPC1100L  | 8 kB  | 2 kB          | yes            | 1    | 1                          | 1   | 8           | 28   | HVQFN33 | F                   |

| LPC1111FHN33/103 | LPC1100XL | 8 kB  | 2 kB          | yes            | 1    | 1                          | 2   | 8           | 28   | HVQFN33 | F                   |

| LPC1111JHN33/103 | LPC1100XL | 8 kB  | 2 kB          | yes            | 1    | 1                          | 2   | 8           | 28   | HVQFN33 | J                   |

| LPC1111FHN33/201 | LPC1100   | 8 kB  | 4 kB          | no             | 1    | 1                          | 1   | 8           | 28   | HVQFN33 | F                   |

| LPC1111FHN33/202 | LPC1100L  | 8 kB  | 4 kB          | yes            | 1    | 1                          | 1   | 8           | 28   | HVQFN33 | F                   |

| LPC1111FHN33/203 | LPC1100XL | 8 kB  | 4 kB          | yes            | 1    | 1                          | 2   | 8           | 28   | HVQFN33 | F                   |

| LPC1111JHN33/203 | LPC1100XL | 8 kB  | 4 kB          | yes            | 1    | 1                          | 2   | 8           | 28   | HVQFN33 | J                   |

| LPC1112          | 1         | •     | 1             |                |      |                            |     | 1           |      |         |                     |

| LPC1112FD20/102  | LPC1100L  | 16 kB | 4 kB          | yes            | 1    | 1                          | 1   | 5           | 16   | SO20    | F                   |

| LPC1112FDH20/102 | LPC1100L  | 16 kB | 4 kB          | yes            | 1    | -                          | 1   | 5           | 14   | TSSOP20 | F                   |

| LPC1112FDH28/102 | LPC1100L  | 16 kB | 4 kB          | yes            | 1    | 1                          | 1   | 6           | 22   | TSSOP28 | F                   |

| LPC1112FHN24/202 | LPC1100L  | 16 kB | 4 kB          | yes            | 1    | 1                          | 1   | 6           | 19   | HVQFN24 | F                   |

| LPC1112FHN33/101 | LPC1100   | 16 kB | 2 kB          | no             | 1    | 1                          | 1   | 8           | 28   | HVQFN33 | F                   |

| LPC1112FHN33/102 | LPC1100L  | 16 kB | 2 kB          | yes            | 1    | 1                          | 1   | 8           | 28   | HVQFN33 | F                   |

| LPC1112FHN33/103 | LPC1100XL | 16 kB | 2 kB          | yes            | 1    | 1                          | 2   | 8           | 28   | HVQFN33 | F                   |

| LPC1112JHN33/103 | LPC1100XL | 16 kB | 2 kB          | yes            | 1    | 1                          | 2   | 8           | 28   | HVQFN33 | J                   |

| LPC1112FHN33/201 | LPC1100   | 16 kB | 4 kB          | no             | 1    | 1                          | 1   | 8           | 28   | HVQFN33 | F                   |

| LPC1112FHN33/202 | LPC1100L  | 16 kB | 4 kB          | yes            | 1    | 1                          | 1   | 8           | 28   | HVQFN33 | F                   |

| LPC1112FHN33/203 | LPC1100XL | 16 kB | 4 kB          | yes            | 1    | 1                          | 2   | 8           | 28   | HVQFN33 | F                   |

| LPC1112JHN33/203 | LPC1100XL | 16 kB | 4 kB          | yes            | 1    | 1                          | 2   | 8           | 28   | HVQFN33 | J                   |

| LPC1112FHI33/102 | LPC1100L  | 16 kB | 2 kB          | yes            | 1    | 1                          | 1   | 8           | 28   | HVQFN33 | F                   |

| LPC1112FHI33/202 | LPC1100L  | 16 kB | 4 kB          | yes            | 1    | 1                          | 1   | 8           | 28   | HVQFN33 | F                   |

| LPC1112FHI33/203 | LPC1100XL | 16 kB | 4 kB          | yes            | 1    | 1                          | 2   | 8           | 28   | HVQFN33 | F                   |

| LPC1112JHI33/203 | LPC1100XL | 16 kB | 4 kB          | yes            | 1    | 1                          | 2   | 8           | 28   | HVQFN33 | J                   |

LPC111X

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2014. All rights reserved.

# 6. Pinning information

## 6.1 Pinning

Table 3. Pin description overview

| Part             | Pin description table | Pinning diagram |

|------------------|-----------------------|-----------------|

| LPC1110FD20      | Table 4               | Figure 8        |

| LPC1111FDH20/002 | Table 4               | Figure 9        |

| LPC1112FD20/102  | Table 4               | Figure 10       |

| LPC1112FDH20/102 | Table 5               | Figure 9        |

| LPC1112FHN24/202 | Table 6               | Figure 11       |

| LPC1112FDH28/102 | Table 7               | Figure 12       |

| LPC1114FDH28/102 | Table 7               | Figure 13       |

| LPC1114FN28/102  | Table 7               | Figure 13       |

| LPC1111FHN33/101 | Table 9               | Figure 6        |

| LPC1111FHN33/102 | Table 9               | Figure 6        |

| LPC1111JHN33/103 | Table 11              | Figure 7        |

| LPC1111FHN33/103 | Table 11              | Figure 7        |

| LPC1111FHN33/201 | Table 9               | Figure 6        |

| LPC1111FHN33/202 | Table 9               | Figure 6        |

| LPC1111FHN33/203 | Table 11              | Figure 7        |

| LPC1111JHN33/203 | Table 11              | Figure 7        |

| LPC1112FHN33/101 | Table 9               | Figure 6        |

| LPC1112FHN33/102 | Table 9               | Figure 6        |

| LPC1112FHN33/103 | Table 11              | Figure 7        |

| LPC1112JHN33/103 | Table 11              | Figure 7        |

| LPC1112FHN33/201 | Table 9               | Figure 6        |

| LPC1112FHN33/202 | Table 9               | Figure 6        |

| LPC1112FHN33/203 | Table 11              | Figure 7        |

| LPC1112JHN33/203 | Table 11              | Figure 7        |

| LPC1112FHI33/202 | Table 9               | Figure 6        |

| LPC1112FHI33/203 | Table 11              | Figure 7        |

| LPC1112JHI33/203 | Table 11              | Figure 7        |

| LPC1113FHN33/201 | Table 9               | Figure 6        |

| LPC1113FHN33/202 | Table 9               | Figure 6        |

| LPC1113FHN33/203 | Table 11              | Figure 7        |

| LPC1113JHN33/203 | Table 11              | Figure 7        |

| LPC1113FHN33/301 | Table 9               | Figure 6        |

| LPC1113FHN33/302 | Table 9               | Figure 6        |

| LPC1113FHN33/303 | Table 11              | Figure 7        |

| LPC1113JHN33/303 | Table 11              | Figure 7        |

| LPC1114FHN33/201 | Table 9               | Figure 6        |

| LPC1114FHN33/202 | Table 9               | Figure 6        |

Table 4. LPC1100L series: LPC1110/11/12 pin description table (SO20 and TSSOP20 package with I<sup>2</sup>C-bus pins) ...continued

| Symbol                        | Pin SO20/<br>TSSOP20 |            | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | Description                                                                                                                                                                                                  |  |  |  |

|-------------------------------|----------------------|------------|-------------------------|------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| R/PIO0_11/<br>AD0/CT32B0_MAT3 | 4                    | <u>[5]</u> | yes                     | I    | I; PU                 | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                              |  |  |  |

|                               |                      |            |                         | I/O  | -                     | PIO0_11 — General purpose digital input/output pin.                                                                                                                                                          |  |  |  |

|                               |                      |            |                         | I    | -                     | AD0 — A/D converter, input 0.                                                                                                                                                                                |  |  |  |

|                               |                      |            |                         | 0    | -                     | CT32B0_MAT3 — Match output 3 for 32-bit timer 0.                                                                                                                                                             |  |  |  |

| PIO1_0 to PIO1_7              |                      |            |                         | I/O  |                       | <b>Port 1</b> — Port 1 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 1 pins depends on the function selected through the IOCONFIG register block. |  |  |  |

| R/PIO1_0/<br>AD1/CT32B1_CAP0  | 7                    | <u>[5]</u> | yes                     | I    | I; PU                 | <ul> <li>R — Reserved. Configure for an alternate function in the IOCONFIG block.</li> </ul>                                                                                                                 |  |  |  |

|                               |                      |            |                         | I/O  | -                     | PIO1_0 — General purpose digital input/output pin.                                                                                                                                                           |  |  |  |

|                               |                      |            |                         | I    | -                     | AD1 — A/D converter, input 1.                                                                                                                                                                                |  |  |  |

|                               |                      |            |                         | I    | -                     | CT32B1_CAP0 — Capture input 0 for 32-bit timer 1.                                                                                                                                                            |  |  |  |

| R/PIO1_1/<br>AD2/CT32B1_MAT0  | 8                    | [5]        | no                      | 0    | I; PU                 | R — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                     |  |  |  |

|                               |                      |            |                         | I/O  | -                     | PIO1_1 — General purpose digital input/output pin.                                                                                                                                                           |  |  |  |

|                               |                      |            |                         | I    | -                     | AD2 — A/D converter, input 2.                                                                                                                                                                                |  |  |  |

|                               |                      |            |                         | 0    | -                     | CT32B1_MAT0 — Match output 0 for 32-bit timer 1.                                                                                                                                                             |  |  |  |

| R/PIO1_2/<br>AD3/CT32B1_MAT1  | 9                    | [5]        | no                      | I    | I; PU                 | R — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                     |  |  |  |

|                               |                      |            |                         | I/O  | -                     | PIO1_2 — General purpose digital input/output pin.                                                                                                                                                           |  |  |  |

|                               |                      |            |                         | I    | -                     | AD3 — A/D converter, input 3.                                                                                                                                                                                |  |  |  |

|                               |                      |            |                         | 0    | -                     | CT32B1_MAT1 — Match output 1 for 32-bit timer 1.                                                                                                                                                             |  |  |  |

| SWDIO/PIO1_3/                 | 10                   | [5]        | no                      | I/O  | I; PU                 | SWDIO — Serial wire debug input/output.                                                                                                                                                                      |  |  |  |

| AD4/CT32B1_MAT2               |                      |            |                         | I/O  | -                     | PIO1_3 — General purpose digital input/output pin.                                                                                                                                                           |  |  |  |

|                               |                      |            |                         | I    | -                     | AD4 — A/D converter, input 4.                                                                                                                                                                                |  |  |  |

|                               |                      |            |                         | 0    | -                     | CT32B1_MAT2 — Match output 2 for 32-bit timer 1.                                                                                                                                                             |  |  |  |

| PIO1_6/RXD/                   | 11                   | [3]        | no                      | I/O  | I; PU                 | PIO1_6 — General purpose digital input/output pin.                                                                                                                                                           |  |  |  |

| CT32B0_MAT0                   |                      |            |                         | I    | -                     | RXD — Receiver input for UART.                                                                                                                                                                               |  |  |  |

|                               |                      |            |                         | 0    | -                     | CT32B0_MAT0 — Match output 0 for 32-bit timer 0.                                                                                                                                                             |  |  |  |

| PIO1_7/TXD/                   | 12                   | [3]        | no                      | I/O  | I; PU                 | PIO1_7 — General purpose digital input/output pin.                                                                                                                                                           |  |  |  |

| CT32B0_MAT1                   |                      |            |                         | 0    | -                     | TXD — Transmitter output for UART.                                                                                                                                                                           |  |  |  |

|                               |                      |            |                         | 0    | -                     | CT32B0_MAT1 — Match output 1 for 32-bit timer 0.                                                                                                                                                             |  |  |  |

| $V_{DD}$                      | 15                   |            | -                       |      | -                     | 3.3 V supply voltage to the internal regulator, the external rail, and the ADC. Also used as the ADC reference voltage.                                                                                      |  |  |  |

| XTALIN                        | 14                   | [6]        | -                       | I    | -                     | Input to the oscillator circuit and internal clock generator circuits. Input voltage must not exceed 1.8 V.                                                                                                  |  |  |  |

| XTALOUT                       | 13                   | [6]        | -                       | 0    | -                     | Output from the oscillator amplifier.                                                                                                                                                                        |  |  |  |

| V <sub>SS</sub>               | 16                   |            | -                       |      | -                     | Ground.                                                                                                                                                                                                      |  |  |  |

Table 5. LPC1100L series: LPC1112 pin description table (TSSOP20 with V<sub>DDA</sub> and V<sub>SSA</sub> pins) ...continued

| Symbol           | Pin TSSOP20   | Start<br>logic<br>input | Type | Reset<br>state<br>[1] | Description                                                                                                 |

|------------------|---------------|-------------------------|------|-----------------------|-------------------------------------------------------------------------------------------------------------|

| $V_{DDA}$        | 5             | -                       | I    | -                     | 3.3 V supply voltage to the ADC. Also used as the ADC reference voltage.                                    |

| XTALIN           | 14 <u>[5]</u> | -                       | I    | -                     | Input to the oscillator circuit and internal clock generator circuits. Input voltage must not exceed 1.8 V. |

| XTALOUT          | 13 <u>[5]</u> | -                       | 0    | -                     | Output from the oscillator amplifier.                                                                       |

| V <sub>SS</sub>  | 16            | -                       | I    | -                     | Ground.                                                                                                     |

| V <sub>SSA</sub> | 6             | -                       | I    | -                     | Analog ground.                                                                                              |

- [1] Pin state at reset for default function: I = Input; O = Output; PU = internal pull-up enabled (pins pulled up to full V<sub>DD</sub> level ); IA = inactive, no pull-up/down enabled.

- [2] 5 V tolerant pad. RESET functionality is not available in Deep power-down mode.

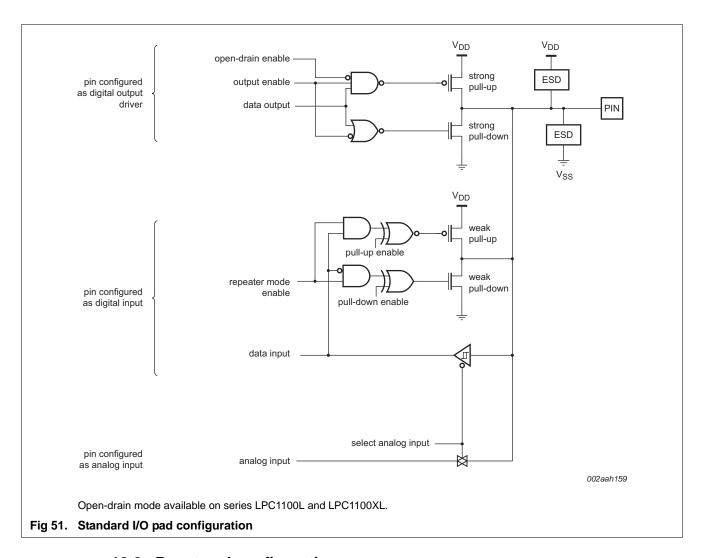

- [3] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors and configurable hysteresis (see Figure 51).

- [4] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors, configurable hysteresis, and analog input. When configured as a ADC input, digital section of the pad is disabled and the pin is not 5 V tolerant (see Figure 51).

- [5] When the system oscillator is not used, connect XTALIN and XTALOUT as follows: XTALIN can be left floating or can be grounded (grounding is preferred to reduce susceptibility to noise). XTALOUT should be left floating.

Table 6. LPC1100L series: LPC1112 (HVQFN24 package)

| Symbol                        | HVQFN<br>pin | Start<br>logic<br>input | Туре          | Reset state | Description                                                                                                                                                                                                                                        |                                                                 |  |  |  |

|-------------------------------|--------------|-------------------------|---------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|

| RESET/PIO0_0                  | 1[2]         | yes                     | I             | I; PU       | <b>RESET</b> — External reset input with 20 ns glitch filter. A LOW-going pulse as short as 50 ns on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. |                                                                 |  |  |  |

|                               |              |                         |               |             | In deep power-down mode, this pin must be pulled HIGH externally. The RESET pin can be left unconnected or be used as a GPIO pin if an external RESET function is not needed and Deep power-down mode is not used.                                 |                                                                 |  |  |  |

|                               |              |                         | I/O           | -           | <b>PIO0_0</b> — General purpose digital input/output pin with 10 ns glitch filter.                                                                                                                                                                 |                                                                 |  |  |  |

| PIO0_1/CLKOUT/<br>CT32B0_MAT2 | 2[3]         | yes                     | I/O           | I; PU       | PIO0_1 — General purpose digital input/output pin. A LOW level on this pin during reset starts the ISP command handler.                                                                                                                            |                                                                 |  |  |  |

|                               |              |                         | 0             | -           | CLKOUT — Clockout pin.                                                                                                                                                                                                                             |                                                                 |  |  |  |

|                               |              |                         | 0             | -           | CT32B0_MAT2 — Match output 2 for 32-bit timer 0.                                                                                                                                                                                                   |                                                                 |  |  |  |

| PIO0_2/SSEL0/                 | 7 <u>[3]</u> | yes                     | I/O           | I; PU       | PIO0_2 — General purpose digital input/output pin.                                                                                                                                                                                                 |                                                                 |  |  |  |

| CT16B0_CAP0                   |              |                         | I/O           | -           | SSEL0 — Slave Select for SPI0.                                                                                                                                                                                                                     |                                                                 |  |  |  |

|                               |              |                         | I             | -           | CT16B0_CAP0 — Capture input 0 for 16-bit timer 0.                                                                                                                                                                                                  |                                                                 |  |  |  |

| PIO0_4/SCL                    | 8[4]         | yes yes                 | yes I/O I; IA |             | I; IA                                                                                                                                                                                                                                              | PIO0_4 — General purpose digital input/output pin (open-drain). |  |  |  |

|                               |              |                         | I/O           | -           | <b>SCL</b> — I <sup>2</sup> C-bus, open-drain clock input/output. High-current sink only if I <sup>2</sup> C Fast-mode Plus is selected in the I/O configuration register.                                                                         |                                                                 |  |  |  |

Table 9. LPC1100 and LPC1100L series: LPC1111/12/13/14 pin description table (HVQFN33 package)

| Symbol               |         | Pin               | Start<br>logic<br>input | Туре |      | Description                                                                                                                                                                                                                                       |

|----------------------|---------|-------------------|-------------------------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO0_0 to            |         |                   |                         |      |      | <b>Port 0</b> — Port 0 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 0 pins depends on the function selected through the IOCONFIG register block.                                      |

| RESET/PI             | O0_0    | 2[2]              | yes                     | I    | I;PU | <b>RESET</b> — External reset input with 20 ns glitch filter. A LOW-going pulse as short as 50 ns on this pin resets the device, causing I/O ports and peripherals to take on their default states and processor execution to begin at address 0. |

|                      |         |                   |                         |      |      | In deep power-down mode, this pin must be pulled HIGH externally. The RESET pin can be left unconnected or be used as a GPIO pin if an external RESET function is not needed and Deep power-down mode is not used.                                |

|                      |         |                   |                         | I/O  | -    | PIO0_0 — General purpose digital input/output pin with 10 ns glitch filter.                                                                                                                                                                       |

| PIO0_1/C<br>CT32B0_I |         | 3[3]              | yes                     | I/O  | I;PU | <b>PIOO_1</b> — General purpose digital input/output pin. A LOW level on this pin during reset starts the ISP command handler.                                                                                                                    |

|                      |         |                   |                         | 0    | -    | CLKOUT — Clock out pin.                                                                                                                                                                                                                           |

|                      |         |                   |                         | 0    | -    | CT32B0_MAT2 — Match output 2 for 32-bit timer 0.                                                                                                                                                                                                  |

| PIO0_2/S             |         | 8 <u>[3]</u>      | yes                     | I/O  | I;PU | PIO0_2 — General purpose digital input/output pin.                                                                                                                                                                                                |

| CT16B0_0             | CAP0    |                   |                         | I/O  | -    | SSEL0 — Slave select for SPI0.                                                                                                                                                                                                                    |

|                      |         |                   |                         | I    | -    | CT16B0_CAP0 — Capture input 0 for 16-bit timer 0.                                                                                                                                                                                                 |

| PIO0_3               |         | 9 <u>[3]</u>      | yes                     | I/O  | I;PU | PIO0_3 — General purpose digital input/output pin.                                                                                                                                                                                                |

| PIO0_4/S             | CL      | 10 <sup>[4]</sup> | yes                     | I/O  | I;IA | PIO0_4 — General purpose digital input/output pin (open-drain).                                                                                                                                                                                   |

|                      |         |                   |                         | I/O  | -    | <b>SCL</b> — I <sup>2</sup> C-bus, open-drain clock input/output. High-current sink only if I <sup>2</sup> C Fast-mode Plus is selected in the I/O configuration register.                                                                        |

| PIO0_5/SI            | DA      | 11 <sup>[4]</sup> | yes                     | I/O  | I;IA | PIO0_5 — General purpose digital input/output pin (open-drain).                                                                                                                                                                                   |

|                      |         |                   |                         | I/O  | -    | <b>SDA</b> — $I^2C$ -bus, open-drain data input/output. High-current sink only if $I^2C$ Fast-mode Plus is selected in the I/O configuration register.                                                                                            |

| PIO0_6/S             | CK0     | 15 <u>[3]</u>     | yes                     | I/O  | I;PU | PIO0_6 — General purpose digital input/output pin.                                                                                                                                                                                                |

|                      |         |                   |                         | I/O  | -    | SCK0 — Serial clock for SPI0.                                                                                                                                                                                                                     |

| PIO0_7/C             | TS      | 16 <sup>[3]</sup> | yes                     | I/O  | I;PU | PIO0_7 — General purpose digital input/output pin (high-current output driver).                                                                                                                                                                   |

|                      |         |                   |                         | I    | -    | CTS — Clear To Send input for UART.                                                                                                                                                                                                               |

| PIO0_8/M             |         | 17 <sup>[3]</sup> | yes                     | I/O  | I;PU | PIO0_8 — General purpose digital input/output pin.                                                                                                                                                                                                |

| CT16B0_I             | MAT0    |                   |                         | I/O  | -    | MISO0 — Master In Slave Out for SPI0.                                                                                                                                                                                                             |

|                      |         |                   |                         | 0    | -    | CT16B0_MAT0 — Match output 0 for 16-bit timer 0.                                                                                                                                                                                                  |

| PIO0_9/M             | OSI0/   | 18 <sup>[3]</sup> | yes                     | I/O  | I;PU | PIO0_9 — General purpose digital input/output pin.                                                                                                                                                                                                |

| CT16B0_I             | MAT1    |                   |                         | I/O  | -    | MOSI0 — Master Out Slave In for SPI0.                                                                                                                                                                                                             |

|                      |         |                   |                         | 0    | -    | CT16B0_MAT1 — Match output 1 for 16-bit timer 0.                                                                                                                                                                                                  |

| SWCLK/P              | IO0_10/ | 19 <sup>[3]</sup> | yes                     | I    | I;PU | SWCLK — Serial wire clock.                                                                                                                                                                                                                        |

| SCK0/                | MATO    |                   |                         | I/O  | -    | PIO0_10 — General purpose digital input/output pin.                                                                                                                                                                                               |

| CT16B0_I             | viA I Z |                   |                         | I/O  | -    | SCK0 — Serial clock for SPI0.                                                                                                                                                                                                                     |

|                      |         |                   |                         | 0    | -    | CT16B0_MAT2 — Match output 2 for 16-bit timer 0.                                                                                                                                                                                                  |

- Enabled by software but requires a hardware reset or a watchdog reset/interrupt to be disabled.

- Incorrect/Incomplete feed sequence causes reset/interrupt if enabled.

- Flag to indicate watchdog reset.

- Programmable 24-bit timer with internal prescaler.

- Selectable time period from (T<sub>cy(WDCLK)</sub> × 256 × 4) to (T<sub>cy(WDCLK)</sub> × 2<sup>24</sup> × 4) in multiples of T<sub>cy(WDCLK)</sub> × 4.

- The Watchdog Clock (WDCLK) source can be selected from the Internal RC oscillator (IRC), the Watchdog oscillator, or the main clock. This gives a wide range of potential timing choices of Watchdog operation under different power reduction conditions. It also provides the ability to run the WDT from an entirely internal source that is not dependent on an external crystal and its associated components and wiring for increased reliability.

## 7.15 Windowed WatchDog Timer (LPC1100L and LPC1100XL series)

**Remark:** The windowed watchdog timer is available on the LPC1100L and LPC1100XL series only.

The purpose of the watchdog is to reset the controller if software fails to periodically service it within a programmable time window.

### 7.15.1 Features

- Internally resets chip if not periodically reloaded during the programmable time-out period.

- Optional windowed operation requires reload to occur between a minimum and maximum time period, both programmable.

- Optional warning interrupt can be generated at a programmable time prior to watchdog time-out.

- Enabled by software but requires a hardware reset or a watchdog reset/interrupt to be disabled.

- Incorrect feed sequence causes reset or interrupt if enabled.

- · Flag to indicate watchdog reset.

- Programmable 24-bit timer with internal prescaler.

- Selectable time period from (T<sub>cy(WDCLK)</sub>  $\times$  256  $\times$  4) to (T<sub>cy(WDCLK)</sub>  $\times$  2<sup>24</sup>  $\times$  4) in multiples of T<sub>cv(WDCLK)</sub>  $\times$  4.

- The Watchdog Clock (WDCLK) source can be selected from the IRC or the dedicated watchdog oscillator (WDO). This gives a wide range of potential timing choices of watchdog operation under different power conditions.

## 7.16 Clocking and power control

#### 7.16.1 Crystal oscillators

The LPC1110/11/12/13/14/15 include three independent oscillators. These are the system oscillator, the Internal RC oscillator (IRC), and the Watchdog oscillator. Each oscillator can be used for more than one purpose as required in a particular application.

LPC111X

## 10. Static characteristics

## 10.1 LPC1100, LPC1100L series

Table 16. Static characteristics (LPC1100, LPC1100L series)

$T_{amb} = -40 \, ^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$ , unless otherwise specified.

| Symbol          | Parameter                               | Conditions                                       |               | Min      | Typ[1]  | Max | Unit |

|-----------------|-----------------------------------------|--------------------------------------------------|---------------|----------|---------|-----|------|

| $V_{DD}$        | supply voltage (core and external rail) |                                                  |               | 1.8      | 3.3     | 3.6 | V    |

| LPC1100 se      | ries (LPC111x/101/201/301               | ) power consumption                              |               |          | ·       |     |      |

| I <sub>DD</sub> | supply current                          | Active mode; code                                |               |          |         |     |      |

|                 |                                         | while(1){}                                       |               |          |         |     |      |

|                 |                                         | executed from flash                              |               |          |         |     |      |

|                 |                                         | system clock = 12 MHz                            | [2][3][4]     | -        | 3       | -   | mA   |

|                 |                                         | $V_{DD} = 3.3 \text{ V}$                         | <u>[5][6]</u> |          |         |     |      |

|                 |                                         | system clock = 50 MHz                            | [2][3][5]     | -        | 9       | -   | mA   |

|                 |                                         | $V_{DD} = 3.3 \text{ V}$                         | [6][7]        |          |         |     |      |

|                 |                                         | Sleep mode;                                      | [2][3][4]     | -        | 2       | -   | mA   |

|                 |                                         | system clock = 12 MHz                            | <u>[5][6]</u> |          |         |     |      |

|                 |                                         | $V_{DD} = 3.3 \text{ V}$                         |               |          |         |     |      |

|                 |                                         | Deep-sleep mode;<br>V <sub>DD</sub> = 3.3 V      | [2][3][8]     | -        | 6       | -   | μΑ   |

|                 |                                         | Deep power-down mode;<br>V <sub>DD</sub> = 3.3 V | [2][9]        | -        | 220     | -   | nA   |

| LPC1100L s      | eries (LPC111x/002/102/20               | 2/302) power consumption                         | in low-c      | urrent m | ode[11] |     |      |

| I <sub>DD</sub> | supply current                          | Active mode; code                                |               |          |         |     |      |

|                 |                                         | while(1){}                                       |               |          |         |     |      |

|                 |                                         | executed from flash                              |               |          |         |     |      |

|                 |                                         | system clock = 1 MHz                             | [2][3][5]     | -        | 840     | -   | μА   |

|                 |                                         | V <sub>DD</sub> = 3.3 V                          | [6][10]       |          |         |     |      |

|                 |                                         | system clock = 6 MHz                             | [2][3][5]     | -        | 1       | -   | mA   |

|                 |                                         | V <sub>DD</sub> = 3.3 V                          | [6][10]       |          |         |     |      |

|                 |                                         | system clock = 12 MHz                            | [2][3][4]     | -        | 2       | -   | mA   |

|                 |                                         | V <sub>DD</sub> = 3.3 V                          | [5][6]        |          |         |     |      |

|                 |                                         | system clock = 50 MHz                            | [2][3][5]     | -        | 7       | -   | mA   |

|                 |                                         | $V_{DD} = 3.3 \text{ V}$                         | [6][7]        |          |         |     |      |

|                 |                                         | Sleep mode;                                      | [2][3][4]     | -        | 1       | -   | mA   |

|                 |                                         | system clock = 12 MHz                            | <u>[5][6]</u> |          |         |     |      |

|                 |                                         | $V_{DD} = 3.3 \text{ V}$                         |               |          |         |     |      |

|                 |                                         | system clock = 50 MHz                            | [2][3][4]     | -        | 5       | -   | mA   |

|                 |                                         | $V_{DD} = 3.3 \text{ V}$                         | [5][6]        |          |         |     |      |

|                 |                                         | Deep-sleep mode;<br>V <sub>DD</sub> = 3.3 V      | [2][3][8]     | -        | 2       | -   | μΑ   |

|                 |                                         | Deep power-down mode;<br>V <sub>DD</sub> = 3.3 V | [2][9]        | -        | 220     | -   | nA   |

LPC111X

Table 17. Static characteristics (LPC1100XL series) ...continued  $T_{amb} = -40$  °C to +105 °C, unless otherwise specified.

| Symbol                                   | Parameter                              | Conditions                                                                                 | Min                   | Typ[1]              | Max                | Unit |

|------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------|-----------------------|---------------------|--------------------|------|

| V <sub>OH</sub>                          | HIGH-level output voltage              | $2.5 \text{ V} \leq \text{V}_{DD} \leq 3.6 \text{ V};$ $\text{I}_{OH} = -20 \text{ mA}$    | V <sub>DD</sub> - 0.4 | -                   | -                  | V    |

|                                          |                                        | $1.8 \text{ V} \le \text{V}_{DD} < 2.5 \text{ V};$<br>$\text{I}_{OH} = -12 \text{ mA}$     | $V_{DD} - 0.4$        | -                   | -                  | V    |

| V <sub>OL</sub>                          | LOW-level output voltage               | $2.5 \text{ V} \leq \text{V}_{DD} \leq 3.6 \text{ V};$ $\text{I}_{OL} = 4 \text{ mA}$      | -                     | -                   | 0.4                | V    |

|                                          |                                        | $1.8 \text{ V} \le \text{V}_{DD} < 2.5 \text{ V};$<br>$\text{I}_{OL} = 3 \text{ mA}$       | -                     | -                   | 0.4                | V    |

| I <sub>OH</sub>                          | HIGH-level output current              | $V_{OH} = V_{DD} - 0.4 \text{ V};$<br>2.5 V \le V_{DD} \le 3.6 V                           | 20                    | -                   | -                  | mA   |

|                                          |                                        | 1.8 V ≤ V <sub>DD</sub> < 2.5 V                                                            | 12                    | -                   | -                  | mA   |

| I <sub>OL</sub>                          | LOW-level output current               | $V_{OL} = 0.4 \text{ V}$<br>2.5 V \le V_{DD} \le 3.6 V                                     | 4                     | -                   | -                  | mA   |

|                                          |                                        | 1.8 V ≤ V <sub>DD</sub> < 2.5 V                                                            | 3                     | -                   | -                  | mA   |

| I <sub>OLS</sub>                         | LOW-level short-circuit output current | $V_{OL} = V_{DD}$ [16]                                                                     | -                     | -                   | 50                 | mA   |

| I <sub>pd</sub>                          | pull-down current                      | V <sub>I</sub> = 5 V                                                                       | 10                    | 50                  | 150                | μΑ   |

|                                          | pull-up current                        | $V_{I} = 0 \text{ V}$ $2.0 \text{ V} \le V_{DD} \le 3.6 \text{ V}$                         | -15                   | -50                 | -85                | μА   |

|                                          |                                        | 1.8 V ≤ V <sub>DD</sub> < 2.0 V                                                            | -10                   | -50                 | -85                | μΑ   |

|                                          |                                        | V <sub>DD</sub> < V <sub>I</sub> < 5 V                                                     | 0                     | 0                   | 0                  | μΑ   |

| I <sup>2</sup> C-bus pins                | s (PIO0_4 and PIO0_5)                  |                                                                                            |                       |                     |                    |      |

| V <sub>IH</sub>                          | HIGH-level input voltage               |                                                                                            | 0.7V <sub>DD</sub>    | -                   | -                  | V    |

| V <sub>IL</sub>                          | LOW-level input voltage                |                                                                                            | -                     | -                   | 0.3V <sub>DD</sub> | V    |

| $V_{hys}$                                | hysteresis voltage                     |                                                                                            | -                     | 0.05V <sub>DD</sub> | -                  | V    |

| I <sub>OL</sub>                          | LOW-level output current               | V <sub>OL</sub> = 0.4 V; I <sup>2</sup> C-bus pins<br>configured as standard<br>mode pins  | 3.5                   | -                   | -                  | mA   |

|                                          |                                        | $2.5 \text{ V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V}$                               |                       |                     |                    |      |

| _                                        |                                        | 1.8 V ≤ V <sub>DD</sub> < 2.5 V                                                            | 3                     | -                   | -                  |      |

| I <sub>OL</sub> LOW-level output current |                                        | V <sub>OL</sub> = 0.4 V; I <sup>2</sup> C-bus pins<br>configured as Fast-mode<br>Plus pins | 20                    | -                   | -                  | mA   |

|                                          |                                        | $2.5 \text{ V} \leq \text{V}_{DD} \leq 3.6 \text{ V}$                                      |                       |                     |                    |      |

|                                          |                                        | 1.8 V ≤ V <sub>DD</sub> < 2.5 V                                                            | 16                    | -                   | -                  |      |

| I <sub>LI</sub>                          | input leakage current                  | $V_I = V_{DD}$ [17]                                                                        | -                     | 2                   | 4                  | μΑ   |

|                                          |                                        | $V_I = 5 V$                                                                                | -                     | 10                  | 22                 | μΑ   |

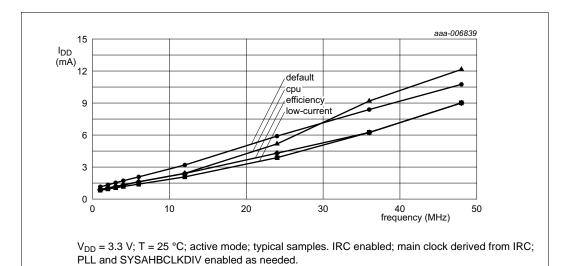

Fig 35. CoreMark current consumption for different power modes using IRC

## 10.9 Peripheral power consumption

The supply current per peripheral is measured as the difference in supply current between the peripheral block enabled and the peripheral block disabled in the SYSAHBCLKCFG and PDRUNCFG (for analog blocks) registers. All other blocks are disabled in both registers and no code is executed. Measured on a typical sample at  $T_{amb} = 25 \, ^{\circ}C$ . Unless noted otherwise, the system oscillator and PLL are running in both measurements.

The supply currents are shown for system clock frequencies of 12 MHz and 48 MHz.

Table 21. Power consumption for individual analog and digital blocks

| Peripheral                             | Typical mA | supply cu | rrent in | Notes                                                                                                                                        |  |  |  |

|----------------------------------------|------------|-----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                        | n/a        | 12 MHz    | 48 MHz   |                                                                                                                                              |  |  |  |

| IRC                                    | 0.27       | -         | -        | System oscillator running; PLL off; independent of main clock frequency.                                                                     |  |  |  |

| System oscillator at 12 MHz            | 0.22       | -         | -        | IRC running; PLL off; independent of main clock frequency.                                                                                   |  |  |  |

| Watchdog<br>oscillator at<br>500 kHz/2 | 0.004      | -         | -        | System oscillator running; PLL off; independent of main clock frequency.                                                                     |  |  |  |

| BOD                                    | 0.051      | -         | -        | Independent of main clock frequency.                                                                                                         |  |  |  |

| Main PLL                               | -          | 0.21      | -        |                                                                                                                                              |  |  |  |

| ADC                                    | -          | 0.08      | 0.29     |                                                                                                                                              |  |  |  |

| CLKOUT                                 | -          | 0.12      | 0.47     | Main clock divided by 4 in the CLKOUTDIV register.                                                                                           |  |  |  |

| CT16B0                                 | -          | 0.02      | 0.06     |                                                                                                                                              |  |  |  |

| CT16B1                                 | -          | 0.02      | 0.06     |                                                                                                                                              |  |  |  |

| CT32B0                                 | -          | 0.02      | 0.07     |                                                                                                                                              |  |  |  |

| CT32B1                                 | -          | 0.02      | 0.06     |                                                                                                                                              |  |  |  |

| GPIO                                   | -          | 0.23      | 0.88     | GPIO pins configured as outputs and set to LOW. Direction and pin state are maintained if the GPIO is disabled in the SYSAHBCLKCFG register. |  |  |  |

| IOCONFIG                               | -          | 0.03      | 0.10     |                                                                                                                                              |  |  |  |

| I2C                                    | -          | 0.04      | 0.13     |                                                                                                                                              |  |  |  |

| ROM                                    | -          | 0.04      | 0.15     |                                                                                                                                              |  |  |  |

| SPI0                                   | -          | 0.12      | 0.45     |                                                                                                                                              |  |  |  |

| SPI1                                   | -          | 0.12      | 0.45     |                                                                                                                                              |  |  |  |

| UART                                   | -          | 0.22      | 0.82     |                                                                                                                                              |  |  |  |

| WDT/WWDT                               | -          | 0.02      | 0.06     | Main clock selected as clock source for the WDT.                                                                                             |  |  |  |

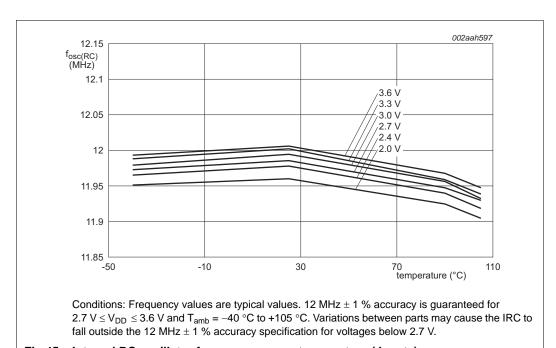

Fig 45. Internal RC oscillator frequency versus temperature (J parts)

Table 26. Dynamic characteristics: Watchdog oscillator

| Symbol    | Parameter                     | Conditions                                                 |        | Min | Typ[1] | Max | Unit |

|-----------|-------------------------------|------------------------------------------------------------|--------|-----|--------|-----|------|

| 030(1111) | internal oscillator frequency | DIVSEL = 0x1F, FREQSEL = 0x1 I in the WDTOSCCTRL register; | [2][3] | -   | 9.4    | -   | kHz  |

|           |                               | DIVSEL = 0x00, FREQSEL = 0xF I in the WDTOSCCTRL register  | [2][3] | -   | 2300   | -   | kHz  |

- [1] Typical ratings are not guaranteed. The values listed are at room temperature (25  $^{\circ}$ C), nominal supply voltages.

- [2] The typical frequency spread over processing and temperature ( $T_{amb}$  = -40 °C to +105 °C) is  $\pm$ 40 %.

- [3] See the LPC111x user manual.

## 11.5 I/O pins

Table 27. Dynamic characteristic: I/O pins[1]

$T_{amb} = -40 \, ^{\circ}\text{C} \text{ to } +105 \, ^{\circ}\text{C}; 3.0 \, \text{V} \leq V_{DD} \leq 3.6 \, \text{V}.$

| Symbol         | Parameter | Conditions                     | Min | Тур | Max | Unit |

|----------------|-----------|--------------------------------|-----|-----|-----|------|

| t <sub>r</sub> | rise time | pin<br>configured as<br>output | 3.0 | -   | 5.0 | ns   |

| t <sub>f</sub> | fall time | pin<br>configured as<br>output | 2.5 | -   | 5.0 | ns   |

[1] Applies to standard port pins and  $\overline{RESET}$  pin.

## 12.4 XTAL Printed Circuit Board (PCB) layout guidelines

The crystal should be connected on the PCB as close as possible to the oscillator input and output pins of the chip. Take care that the load capacitors  $C_{X1}$ ,  $C_{X2}$ , and  $C_{X3}$  in case of third overtone crystal usage have a common ground plane. The external components must also be connected to the ground plain. Loops must be made as small as possible in order to keep the noise coupled in via the PCB as small as possible. Also parasitics should stay as small as possible. Values of  $C_{X1}$  and  $C_{X2}$  should be chosen smaller accordingly to the increase in parasitics of the PCB layout.

## 12.5 Standard I/O pad configuration

Figure 51 shows the possible pin modes for standard I/O pins with analog input function:

- Digital output driver

- Digital input: Pull-up enabled/disabled

- Digital input: Pull-down enabled/disabled

- Digital input: Repeater mode enabled/disabled

- Digital output: Pseudo open-drain mode enable/disabled

- Analog input

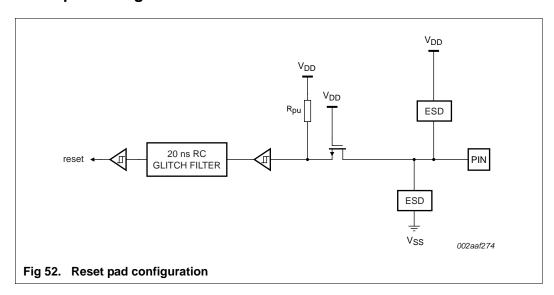

## 12.6 Reset pad configuration

LPC111X

## 12.7 ElectroMagnetic Compatibility (EMC)

Radiated emission measurements according to the IEC61967-2 standard using the TEM-cell method are shown for the LPC1114FBD48/302 in Table 32.

Table 32. ElectroMagnetic Compatibility (EMC) for part LPC1114FBD48/302 (TEM-cell method)

$V_{DD}=3.3~V;~T_{amb}=25~^{\circ}\mathrm{C}.$

| Parameter             | Frequency band           | System clo | Unit     |        |      |

|-----------------------|--------------------------|------------|----------|--------|------|

|                       |                          | 12 MHz     | 24 MHz   | 48 MHz |      |

| Input clock:          | IRC (12 MHz)             |            | <u>'</u> | ,      |      |

| maximum<br>peak level | 150 kHz to 30 MHz        | -7         | -5       | -7     | dBμV |

|                       | 30 MHz to 150 MHz        | -2         | 1        | 10     | dBμV |

|                       | 150 MHz to 1 GHz         | 4          | 8        | 16     | dBμV |

| IEC level[1]          | -                        | 0          | N        | М      | -    |

| Input clock:          | crystal oscillator (12 l | VIHz)      | <u>'</u> | ,      | "    |

| maximum<br>peak level | 150 kHz to 30 MHz        | -7         | -7       | -7     | dBμV |

|                       | 30 MHz to 150 MHz        | -2         | 1        | 8      | dBμV |

|                       | 150 MHz to 1 GHz         | 4          | 7        | 14     | dBμV |

| IEC level[1]          | -                        | 0          | N        | М      | -    |

<sup>[1]</sup> IEC levels refer to Appendix D in the IEC61967-2 Specification.

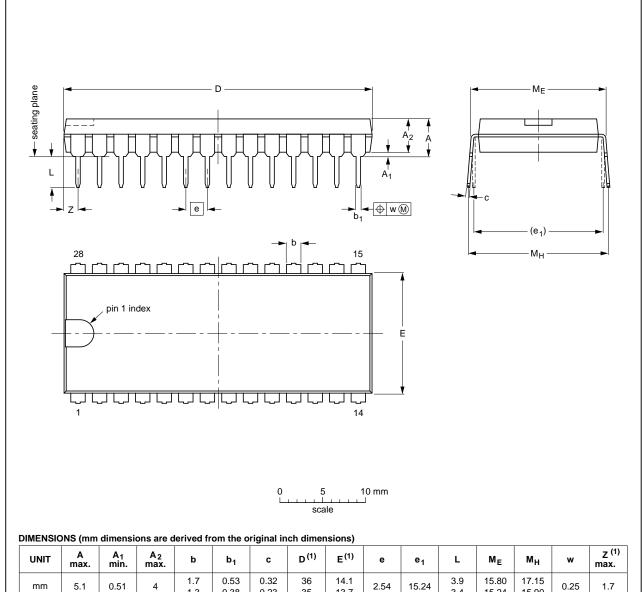

## DIP28: plastic dual in-line package; 28 leads (600 mil)

SOT117-1

| UNIT   | A<br>max. | A <sub>1</sub><br>min. | A <sub>2</sub><br>max. | b              | b <sub>1</sub> | С              | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | e <sub>1</sub> | L            | ME             | Мн             | w    | Z <sup>(1)</sup><br>max. |

|--------|-----------|------------------------|------------------------|----------------|----------------|----------------|------------------|------------------|------|----------------|--------------|----------------|----------------|------|--------------------------|

| mm     | 5.1       | 0.51                   | 4                      | 1.7<br>1.3     | 0.53<br>0.38   | 0.32<br>0.23   | 36<br>35         | 14.1<br>13.7     | 2.54 | 15.24          | 3.9<br>3.4   | 15.80<br>15.24 | 17.15<br>15.90 | 0.25 | 1.7                      |

| inches | 0.2       | 0.02                   | 0.16                   | 0.066<br>0.051 | 0.020<br>0.014 | 0.013<br>0.009 | 1.41<br>1.34     | 0.56<br>0.54     | 0.1  | 0.6            | 0.15<br>0.13 | 0.62<br>0.60   | 0.68<br>0.63   | 0.01 | 0.067                    |

1. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

| OUTLINE  |        | REFERENCES EUROPEAN |           |  |            |                                 |  |

|----------|--------|---------------------|-----------|--|------------|---------------------------------|--|

| VERSION  | IEC    | JEDEC               | JEITA     |  | PROJECTION | ISSUE DATE                      |  |

| SOT117-1 | 051G05 | MO-015              | SC-510-28 |  |            | <del>99-12-27</del><br>03-02-13 |  |

Fig 57. Package outline SOT117-1 (DIP28)

All information provided in this document is subject to legal disclaimers.

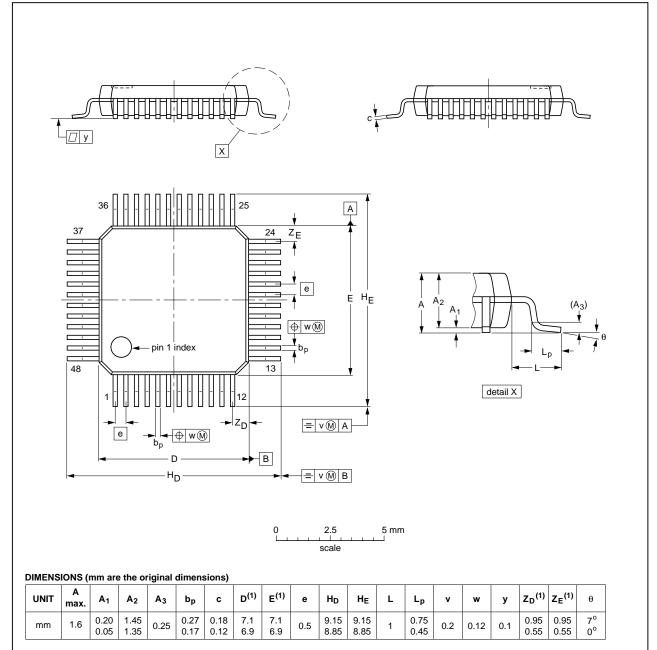

LQFP48: plastic low profile quad flat package; 48 leads; body 7 x 7 x 1.4 mm

SOT313-2

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

|        | REFER  | EUROPEAN  | ISSUE DATE |                 |                                 |

|--------|--------|-----------|------------|-----------------|---------------------------------|

| IEC    | JEDEC  | JEITA     |            | PROJECTION      | ISSUE DATE                      |

| 136E05 | MS-026 |           |            |                 | <del>00-01-19</del><br>03-02-25 |

|        |        | IEC JEDEC |            | IEC JEDEC JEITA | IEC JEDEC JEITA PROJECTION      |

Fig 60. Package outline SOT313-2 (LQFP48)

C111X All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2014. All rights reserved.

LPC111X

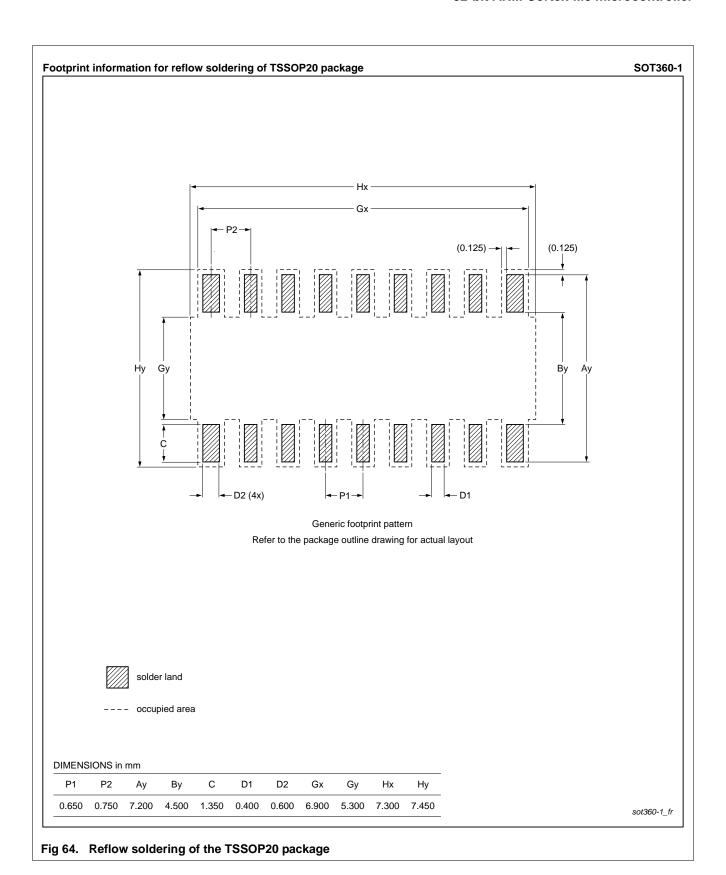

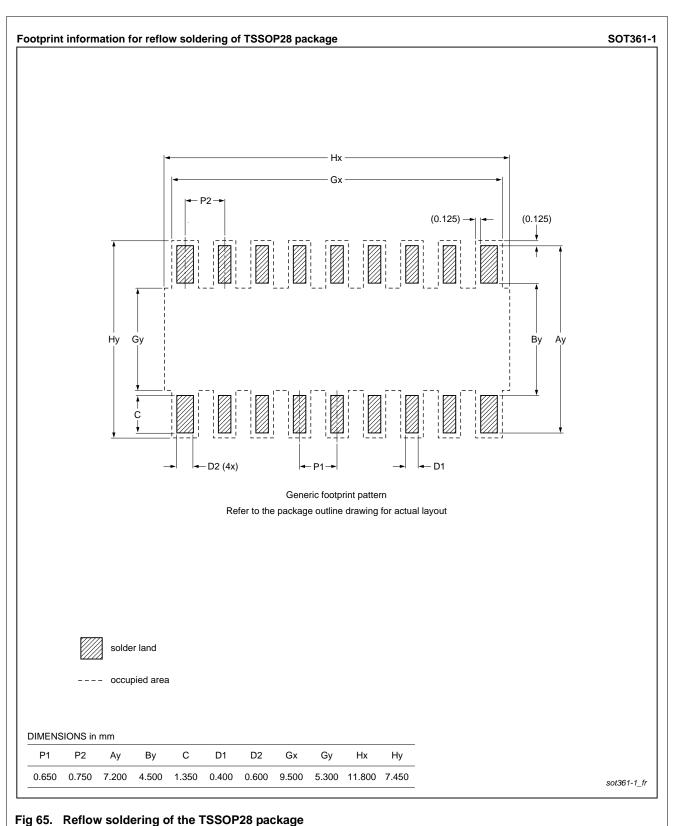

1 ig 00. Renow soldering of the 10001 20 packag