# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 50MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 16KB (16K × 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 6x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-TSSOP (0.173", 4.40mm Width)                                            |

| Supplier Device Package    | 28-TSSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1112fdh28-102-5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 32-bit ARM Cortex-M0 microcontroller

| Type number      | Package |                                                                                                  |           |  |  |  |  |  |  |

|------------------|---------|--------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|--|

|                  | Name    | Description                                                                                      | Version   |  |  |  |  |  |  |

| LPC1115JBD48/303 | LQFP48  | LQFP48: plastic low profile quad flat package; 48 leads; body 7 $\times$ 7 $\times$ 1.4 mm       | SOT313-2  |  |  |  |  |  |  |

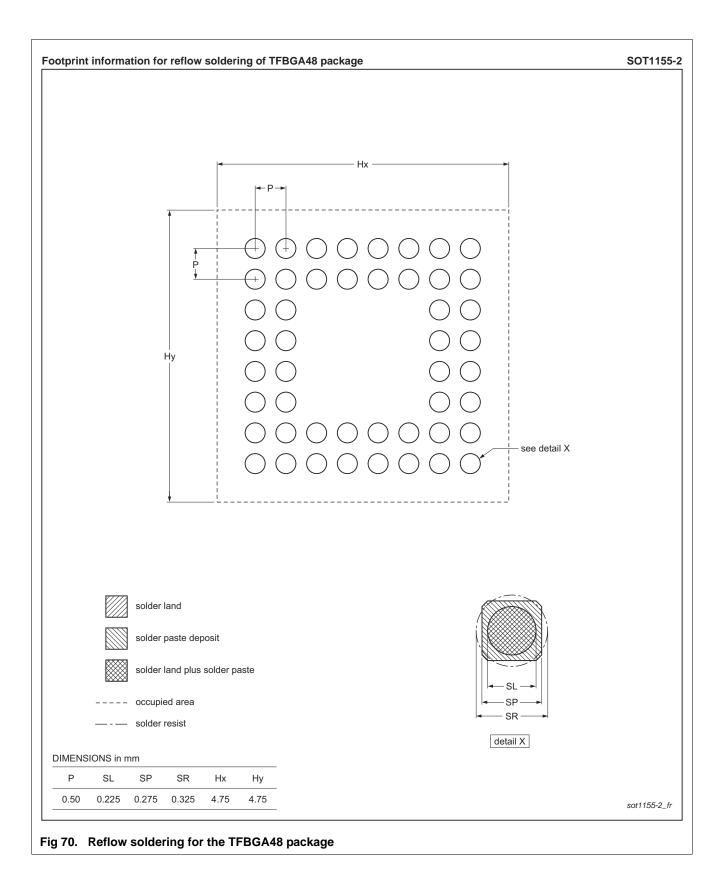

| LPC1115FET48/303 | TFBGA48 | plastic thin fine-pitch ball grid array package; 48 balls; body 4.5 $\times$ 4.5 $\times$ 0.7 mm | SOT1155-2 |  |  |  |  |  |  |

| LPC1115JET48/303 | TFBGA48 | plastic thin fine-pitch ball grid array package; 48 balls; body 4.5 $\times$ 4.5 $\times$ 0.7 mm | SOT1155-2 |  |  |  |  |  |  |

#### Table 1. Ordering information ... continued

### 4.1 Ordering options

#### Table 2. Ordering options

| Type number      | Series    | Flash | Total<br>SRAM | Power<br>profiles | UART | l <sup>2</sup> C/<br>Fast+ | SPI | ADC<br>channel | GPIO | Package | Temp <u><sup>[1]</sup></u> |

|------------------|-----------|-------|---------------|-------------------|------|----------------------------|-----|----------------|------|---------|----------------------------|

| LPC1110          |           |       |               |                   |      |                            |     |                |      |         |                            |

| LPC1110FD20      | LPC1100L  | 4 kB  | 1 kB          | 100               | 1    | 1                          | 1   | 5              | 16   | SO20    | F                          |

| LPC1111          | LFCIIUUL  | 4 KD  | IKD           | yes               | I    | I                          | I   | 5              | 10   | 3020    | Г                          |

|                  | LPC1100L  | 0.1-D |               |                   | 4    | 4                          | 4   | 5              | 40   | TSSOP20 | F                          |

| LPC1111FDH20/002 |           | 8 kB  | 2 kB          | yes               | 1    | 1                          | 1   |                | 16   |         |                            |

| LPC1111FHN33/101 | LPC1100   | 8 kB  | 2 kB          | no                | 1    | 1                          | 1   | 8              | 28   |         | F                          |

| LPC1111FHN33/102 | LPC1100L  | 8 kB  | 2 kB          | yes               | 1    | 1                          | 1   | 8              | 28   | HVQFN33 |                            |

| LPC1111FHN33/103 | LPC1100XL | 8 kB  | 2 kB          | yes               | 1    | 1                          | 2   | 8              | 28   | HVQFN33 |                            |

| LPC1111JHN33/103 | LPC1100XL | 8 kB  | 2 kB          | yes               | 1    | 1                          | 2   | 8              | 28   | HVQFN33 | J                          |

| LPC1111FHN33/201 | LPC1100   | 8 kB  | 4 kB          | no                | 1    | 1                          | 1   | 8              | 28   | HVQFN33 |                            |

| LPC1111FHN33/202 | LPC1100L  | 8 kB  | 4 kB          | yes               | 1    | 1                          | 1   | 8              | 28   | HVQFN33 | F                          |

| LPC1111FHN33/203 | LPC1100XL | 8 kB  | 4 kB          | yes               | 1    | 1                          | 2   | 8              | 28   | HVQFN33 | F                          |

| LPC1111JHN33/203 | LPC1100XL | 8 kB  | 4 kB          | yes               | 1    | 1                          | 2   | 8              | 28   | HVQFN33 | J                          |

| LPC1112          |           |       |               |                   |      |                            |     |                |      |         |                            |

| LPC1112FD20/102  | LPC1100L  | 16 kB | 4 kB          | yes               | 1    | 1                          | 1   | 5              | 16   | SO20    | F                          |

| LPC1112FDH20/102 | LPC1100L  | 16 kB | 4 kB          | yes               | 1    | -                          | 1   | 5              | 14   | TSSOP20 | F                          |

| LPC1112FDH28/102 | LPC1100L  | 16 kB | 4 kB          | yes               | 1    | 1                          | 1   | 6              | 22   | TSSOP28 | F                          |

| LPC1112FHN24/202 | LPC1100L  | 16 kB | 4 kB          | yes               | 1    | 1                          | 1   | 6              | 19   | HVQFN24 | F                          |

| LPC1112FHN33/101 | LPC1100   | 16 kB | 2 kB          | no                | 1    | 1                          | 1   | 8              | 28   | HVQFN33 | F                          |

| LPC1112FHN33/102 | LPC1100L  | 16 kB | 2 kB          | yes               | 1    | 1                          | 1   | 8              | 28   | HVQFN33 | F                          |

| LPC1112FHN33/103 | LPC1100XL | 16 kB | 2 kB          | yes               | 1    | 1                          | 2   | 8              | 28   | HVQFN33 | F                          |

| LPC1112JHN33/103 | LPC1100XL | 16 kB | 2 kB          | yes               | 1    | 1                          | 2   | 8              | 28   | HVQFN33 | J                          |

| LPC1112FHN33/201 | LPC1100   | 16 kB | 4 kB          | no                | 1    | 1                          | 1   | 8              | 28   | HVQFN33 | F                          |

| LPC1112FHN33/202 | LPC1100L  | 16 kB | 4 kB          | yes               | 1    | 1                          | 1   | 8              | 28   | HVQFN33 | F                          |

| LPC1112FHN33/203 | LPC1100XL | 16 kB | 4 kB          | yes               | 1    | 1                          | 2   | 8              | 28   | HVQFN33 | F                          |

| LPC1112JHN33/203 | LPC1100XL | 16 kB | 4 kB          | yes               | 1    | 1                          | 2   | 8              | 28   | HVQFN33 | J                          |

| LPC1112FHI33/102 | LPC1100L  | 16 kB | 2 kB          | yes               | 1    | 1                          | 1   | 8              | 28   | HVQFN33 | F                          |

| LPC1112FHI33/202 | LPC1100L  | 16 kB | 4 kB          | yes               | 1    | 1                          | 1   | 8              | 28   | HVQFN33 | F                          |

| LPC1112FHI33/203 | LPC1100XL | 16 kB | 4 kB          | yes               | 1    | 1                          | 2   | 8              | 28   | HVQFN33 | F                          |

| LPC1112JHI33/203 | LPC1100XL | 16 kB | 4 kB          | yes               | 1    | 1                          | 2   | 8              | 28   | HVQFN33 | J                          |

#### 32-bit ARM Cortex-M0 microcontroller

- [1] Pin state at reset for default function: I = Input; O = Output; PU = internal pull-up enabled (pins pulled up to full V<sub>DD</sub> level ); IA = inactive, no pull-up/down enabled.

- [2] 5 V tolerant pad. RESET functionality is not available in Deep power-down mode.

- [3] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors and configurable hysteresis (see Figure 51).

- [4] I<sup>2</sup>C-bus pin compliant with the I<sup>2</sup>C-bus specification for I<sup>2</sup>C standard mode and I<sup>2</sup>C Fast-mode Plus. The pin requires an external pull-up to provide output functionality. When power is switched off, this pin is floating and does not disturb the I2C lines. Open-drain configuration applies to all functions on this pin.

- [5] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors, configurable hysteresis, and analog input. When configured as a ADC input, digital section of the pad is disabled and the pin is not 5 V tolerant (see Figure 51).

- [6] When the system oscillator is not used, connect XTALIN and XTALOUT as follows: XTALIN can be left floating or can be grounded (grounding is preferred to reduce susceptibility to noise). XTALOUT should be left floating.

Table 5. LPC1100L series: LPC1112 pin description table (TSSOP20 with V<sub>DDA</sub> and V<sub>SSA</sub> pins)

| Symbol                        | Pin TSSOP20 |     | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------|-------------|-----|-------------------------|------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO0_0 to PIO0_11             |             |     |                         | I/O  |                       | <b>Port 0</b> — Port 0 is a 12-bit I/O port with individual direction<br>and function controls for each bit. The operation of port 0 pins<br>depends on the function selected through the IOCONFIG<br>register block.                                                                                                                                                                                                                                                 |

| RESET/PIO0_0                  | 17          | [2] | yes                     | 1    | I; PU                 | <b>RESET</b> — External reset input with 20 ns glitch filter. A LOW-going pulse as short as 50 ns on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. In deep power-down mode, this pin must be pulled HIGH externally. The RESET pin can be left unconnected or be used as a GPIO pin if an external RESET function is not needed and Deep power-down mode is not used. |

|                               |             |     |                         | I/O  | -                     | <b>PIO0_0</b> — General purpose digital input/output pin with 10 ns glitch filter.                                                                                                                                                                                                                                                                                                                                                                                    |

| PIO0_1/CLKOUT/<br>CT32B0_MAT2 | 18          | [3] | yes                     | I/O  | I; PU                 | <b>PIO0_1</b> — General purpose digital input/output pin. A LOW level on this pin during reset starts the ISP command handler.                                                                                                                                                                                                                                                                                                                                        |

|                               |             |     |                         | 0    | -                     | CLKOUT — Clockout pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                               |             |     |                         | 0    | -                     | CT32B0_MAT2 — Match output 2 for 32-bit timer 0.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PIO0_2/SSEL0/                 | 19          | [3] | yes                     | I/O  | I; PU                 | PIO0_2 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CT16B0_CAP0                   |             |     |                         | I/O  | -                     | SSEL0 — Slave Select for SPI0.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                               |             |     |                         | I    | -                     | CT16B0_CAP0 — Capture input 0 for 16-bit timer 0.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PIO0_3                        | 20          | [3] | yes                     | I/O  | I; PU                 | PIO0_3 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PIO0_8/MISO0/                 | 1           | [3] | yes                     | I/O  | I; PU                 | PIO0_8 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CT16B0_MAT0                   |             |     |                         | I/O  | -                     | MISO0 — Master In Slave Out for SPI0.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                               |             |     |                         | 0    | -                     | CT16B0_MAT0 — Match output 0 for 16-bit timer 0.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PIO0_9/MOSI0/                 | 2           | [3] | yes                     | I/O  | I; PU                 | PIO0_9 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CT16B0_MAT1                   |             |     |                         | I/O  | -                     | MOSI0 — Master Out Slave In for SPI0.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                               |             |     |                         | 0    | -                     | CT16B0_MAT1 — Match output 1 for 16-bit timer 0.                                                                                                                                                                                                                                                                                                                                                                                                                      |

### 32-bit ARM Cortex-M0 microcontroller

| Symbol           | Pin TSSOP20   | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | Description                                                                                                 |

|------------------|---------------|-------------------------|------|-----------------------|-------------------------------------------------------------------------------------------------------------|

| V <sub>DDA</sub> | 5             | -                       | I    | -                     | 3.3 V supply voltage to the ADC. Also used as the ADC reference voltage.                                    |

| XTALIN           | 14 <u>[5]</u> | -                       | I    | -                     | Input to the oscillator circuit and internal clock generator circuits. Input voltage must not exceed 1.8 V. |

| XTALOUT          | 13 <u>[5]</u> | -                       | 0    | -                     | Output from the oscillator amplifier.                                                                       |

| V <sub>SS</sub>  | 16            | -                       | I    | -                     | Ground.                                                                                                     |

| V <sub>SSA</sub> | 6             | -                       | I    | -                     | Analog ground.                                                                                              |

#### Table 5. LPC1100L series: LPC1112 pin description table (TSSOP20 with VDDA and VSSA pins) ... continued

[1] Pin state at reset for default function: I = Input; O = Output; PU = internal pull-up enabled (pins pulled up to full V<sub>DD</sub> level ); IA = inactive, no pull-up/down enabled.

[2] 5 V tolerant pad. RESET functionality is not available in Deep power-down mode.

[3] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors and configurable hysteresis (see Figure 51).

[4] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors, configurable hysteresis, and analog input. When configured as a ADC input, digital section of the pad is disabled and the pin is not 5 V tolerant (see Figure 51).

[5] When the system oscillator is not used, connect XTALIN and XTALOUT as follows: XTALIN can be left floating or can be grounded (grounding is preferred to reduce susceptibility to noise). XTALOUT should be left floating.

| Symbol                        | HVQFN<br>pin | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | Description                                                                                                                                                                                                                                        |

|-------------------------------|--------------|-------------------------|------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET/PIO0_0                  | 1[2]         | yes                     | I    | I; PU                 | <b>RESET</b> — External reset input with 20 ns glitch filter. A LOW-going pulse as short as 50 ns on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. |

|                               |              |                         |      |                       | In deep power- <u>down mode</u> , this pin must be pulled HIGH<br>externally. The RESET pin can be left unconnected or be used<br>as a GPIO pin if an external RESET function is not needed and<br>Deep power-down mode is not used.               |

|                               |              |                         | I/O  | -                     | <b>PIO0_0</b> — General purpose digital input/output pin with 10 ns glitch filter.                                                                                                                                                                 |

| PIO0_1/CLKOUT/<br>CT32B0_MAT2 | 2 <u>[3]</u> | yes                     | I/O  | I; PU                 | <b>PIO0_1</b> — General purpose digital input/output pin. A LOW level on this pin during reset starts the ISP command handler.                                                                                                                     |

|                               |              |                         | 0    | -                     | CLKOUT — Clockout pin.                                                                                                                                                                                                                             |

|                               |              |                         | 0    | -                     | CT32B0_MAT2 — Match output 2 for 32-bit timer 0.                                                                                                                                                                                                   |

| PIO0_2/SSEL0/                 | 7 <u>[3]</u> | yes                     | I/O  | I; PU                 | PIO0_2 — General purpose digital input/output pin.                                                                                                                                                                                                 |

| CT16B0_CAP0                   |              |                         | I/O  | -                     | SSEL0 — Slave Select for SPI0.                                                                                                                                                                                                                     |

|                               |              |                         | I    | -                     | CT16B0_CAP0 — Capture input 0 for 16-bit timer 0.                                                                                                                                                                                                  |

| PIO0_4/SCL                    | 8 <u>[4]</u> | yes                     | I/O  | I; IA                 | <b>PIO0_4</b> — General purpose digital input/output pin (open-drain).                                                                                                                                                                             |

|                               |              |                         | I/O  | -                     | <b>SCL</b> — I <sup>2</sup> C-bus, open-drain clock input/output. High-current sink only if I <sup>2</sup> C Fast-mode Plus is selected in the I/O configuration register.                                                                         |

#### Table 6. LPC1100L series: LPC1112 (HVQFN24 package)

Product data sheet

© NXP Semiconductors N.V. 2014. All rights reserved.

### 32-bit ARM Cortex-M0 microcontroller

| Symbol                        | Pin                      | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | Description                                                                                                                                                                                                                                        |

|-------------------------------|--------------------------|-------------------------|------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO0_0 to PIO0_11             |                          |                         | I/O  |                       | <b>Port 0</b> — Port 0 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 0 pins depends on the function selected through the IOCONFIG register block.                                       |

| RESET/PIO0_0                  | 3 <u>[2]</u>             | yes                     | 1    | I; PU                 | <b>RESET</b> — External reset input with 20 ns glitch filter. A LOW-going pulse as short as 50 ns on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. |

|                               |                          |                         |      |                       | In deep power-down mode, this pin must be pulled HIGH externally. The RESET pin can be left unconnected or be used as a GPIO pin if an external RESET function is not needed and Deep power-down mode is not used.                                 |

|                               |                          |                         | I/O  | -                     | <b>PIO0_0</b> — General purpose digital input/output pin with 10 ns glitch filter.                                                                                                                                                                 |

| PIO0_1/CLKOUT/<br>CT32B0_MAT2 | 4 <u>[3]</u>             | yes                     | I/O  | I; PU                 | <b>PIO0_1</b> — General purpose digital input/output pin. A LOW level on this pin during reset starts the ISP command handler.                                                                                                                     |

|                               |                          |                         | 0    | -                     | CLKOUT — Clockout pin.                                                                                                                                                                                                                             |

|                               |                          |                         | 0    | -                     | CT32B0_MAT2 — Match output 2 for 32-bit timer 0.                                                                                                                                                                                                   |

| PIO0_2/SSEL0/                 | 10 <u>[3]</u>            | yes                     | I/O  | I; PU                 | PIO0_2 — General purpose digital input/output pin.                                                                                                                                                                                                 |

| CT16B0_CAP0                   |                          |                         | I/O  | -                     | SSEL0 — Slave Select for SPI0.                                                                                                                                                                                                                     |

|                               |                          |                         | I    | -                     | CT16B0_CAP0 — Capture input 0 for 16-bit timer 0.                                                                                                                                                                                                  |

| PIO0_3                        | 14 <u>[3]</u>            | yes                     | I/O  | I; PU                 | PIO0_3 — General purpose digital input/output pin.                                                                                                                                                                                                 |

| PIO0_4/SCL                    | 15 <u><sup>[4]</sup></u> | yes                     | I/O  | I; IA                 | <b>PIO0_4</b> — General purpose digital input/output pin (open-drain).                                                                                                                                                                             |

|                               |                          |                         | I/O  | -                     | <b>SCL</b> — I <sup>2</sup> C-bus, open-drain clock input/output. High-current sink only if I <sup>2</sup> C Fast-mode Plus is selected in the I/O configuration register.                                                                         |

| PIO0_5/SDA                    | 16 <u><sup>[4]</sup></u> | yes                     | I/O  | I; IA                 | <b>PIO0_5</b> — General purpose digital input/output pin (open-drain).                                                                                                                                                                             |

|                               |                          |                         | I/O  | -                     | <b>SDA</b> — I <sup>2</sup> C-bus, open-drain data input/output. High-current sink only if I <sup>2</sup> C Fast-mode Plus is selected in the I/O configuration register.                                                                          |

| PIO0_6/SCK0                   | 22 <u>[3]</u>            | yes                     | I/O  | I; PU                 | PIO0_6 — General purpose digital input/output pin.                                                                                                                                                                                                 |

|                               |                          |                         | I/O  | -                     | SCK0 — Serial clock for SPI0.                                                                                                                                                                                                                      |

| PIO0_7/CTS                    | 23 <u>[3]</u>            | yes                     | I/O  | I; PU                 | <b>PIO0_7</b> — General purpose digital input/output pin (high-current output driver).                                                                                                                                                             |

|                               |                          |                         | I    | -                     | CTS — Clear To Send input for UART.                                                                                                                                                                                                                |

| PIO0_8/MISO0/                 | 27 <u>[3]</u>            | yes                     | I/O  | I; PU                 | PIO0_8 — General purpose digital input/output pin.                                                                                                                                                                                                 |

| CT16B0_MAT0                   |                          |                         | I/O  | -                     | MISO0 — Master In Slave Out for SPI0.                                                                                                                                                                                                              |

|                               |                          |                         | 0    | -                     | CT16B0_MAT0 — Match output 0 for 16-bit timer 0.                                                                                                                                                                                                   |

| PIO0_9/MOSI0/                 | 28 <u>[3]</u>            | yes                     | I/O  | I; PU                 | PIO0_9 — General purpose digital input/output pin.                                                                                                                                                                                                 |

| CT16B0_MAT1                   |                          |                         | I/O  | -                     | MOSI0 — Master Out Slave In for SPI0.                                                                                                                                                                                                              |

|                               |                          |                         | 0    | -                     | CT16B0_MAT1 — Match output 1 for 16-bit timer 0.                                                                                                                                                                                                   |

### Table 8. LPC1100 and LPC1100L series: LPC1113/14 pin description table (LQFP48 package)

#### 32-bit ARM Cortex-M0 microcontroller

| Symbol           | Pin                      | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | et Description<br>e                                                                                                                                                                                                                                    |  |  |  |  |  |

|------------------|--------------------------|-------------------------|------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PIO3_0 to PIO3_5 |                          |                         | I/O  |                       | <b>Port 3</b> — Port 3 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 3 pins depends on the function selected through the IOCONFIG register block. Pins PIO3_6 to PIO3_11 are not available. |  |  |  |  |  |

| PIO3_0/DTR       | 36 <u>[3]</u>            | no                      | I/O  | I; PU                 | PIO3_0 — General purpose digital input/output pin.                                                                                                                                                                                                     |  |  |  |  |  |

|                  |                          |                         | 0    | -                     | DTR — Data Terminal Ready output for UART.                                                                                                                                                                                                             |  |  |  |  |  |

| PIO3_1/DSR       | 37 <u>[3]</u>            | no                      | I/O  | I; PU                 | PIO3_1 — General purpose digital input/output pin.                                                                                                                                                                                                     |  |  |  |  |  |

|                  |                          |                         | I    | -                     | DSR — Data Set Ready input for UART.                                                                                                                                                                                                                   |  |  |  |  |  |

| PIO3_2/DCD       | 43 <u>[3]</u>            | no                      | I/O  | I; PU                 | PIO3_2 — General purpose digital input/output pin.                                                                                                                                                                                                     |  |  |  |  |  |

|                  |                          |                         | I    | -                     | DCD — Data Carrier Detect input for UART.                                                                                                                                                                                                              |  |  |  |  |  |

| PIO3_3/RI        | 48 <u>[3]</u>            | no                      | I/O  | I; PU                 | PIO3_3 — General purpose digital input/output pin.                                                                                                                                                                                                     |  |  |  |  |  |

|                  |                          |                         | I    | -                     | RI — Ring Indicator input for UART.                                                                                                                                                                                                                    |  |  |  |  |  |

| PIO3_4           | 18 <u><sup>[3]</sup></u> | no                      | I/O  | I; PU                 | PIO3_4 — General purpose digital input/output pin.                                                                                                                                                                                                     |  |  |  |  |  |

| PIO3_5           | 21 <u>[3]</u>            | no                      | I/O  | I; PU                 | PIO3_5 — General purpose digital input/output pin.                                                                                                                                                                                                     |  |  |  |  |  |

| V <sub>DD</sub>  | 8; 44                    | -                       | I    | -                     | 3.3 V supply voltage to the internal regulator, the external rail, and the ADC. Also used as the ADC reference voltage.                                                                                                                                |  |  |  |  |  |

| XTALIN           | 6 <u>[6]</u>             | -                       | I    | -                     | Input to the oscillator circuit and internal clock generator circuits.<br>Input voltage must not exceed 1.8 V.                                                                                                                                         |  |  |  |  |  |

| XTALOUT          | 7 <u>[6]</u>             | -                       | 0    | -                     | Output from the oscillator amplifier.                                                                                                                                                                                                                  |  |  |  |  |  |

| V <sub>SS</sub>  | 5; 41                    | -                       | I    | -                     | Ground.                                                                                                                                                                                                                                                |  |  |  |  |  |

#### Table 8. LPC1100 and LPC1100L series: LPC1113/14 pin description table (LQFP48 package) ...continued

[1] Pin state at reset for default function: I = Input; O = Output; PU = internal pull-up enabled (pins pulled up to 2.6 V for LPC111x/101/201/301, pins pulled up to full V<sub>DD</sub> level on LPC111x/002/102/202/302 (V<sub>DD</sub> = 3.3 V)); IA = inactive, no pull-up/down enabled.

[2] 5 V tolerant pad. RESET functionality is not available in Deep power-down mode. Use the WAKEUP pin to reset the chip and wake up from Deep power-down mode. An external pull-up resistor is required on this pin for the Deep power-down mode. See <u>Figure 52</u> for the reset pad configuration.

[3] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors and configurable hysteresis (see Figure 51).

[4] I<sup>2</sup>C-bus pads compliant with the I<sup>2</sup>C-bus specification for I<sup>2</sup>C standard mode and I<sup>2</sup>C Fast-mode Plus. The pin requires an external pull-up to provide output functionality. When power is switched off, this pin is floating and does not disturb the I2C lines. Open-drain configuration applies to all functions on this pin.

[5] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors, configurable hysteresis, and analog input. When configured as a ADC input, digital section of the pad is disabled and the pin is not 5 V tolerant (see <u>Figure 51</u>).

[6] When the system oscillator is not used, connect XTALIN and XTALOUT as follows: XTALIN can be left floating or can be grounded (grounding is preferred to reduce susceptibility to noise). XTALOUT should be left floating.

LPC111X

32 of 127

### 32-bit ARM Cortex-M0 microcontroller

| Symbol                                   | Pin                      | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | Description                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|------------------------------------------|--------------------------|-------------------------|------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| R/PIO0_11/AD0/<br>CT32B0_MAT3            | 21 <u>5</u>              | yes                     | -    | I;PU                  | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                          |  |  |  |

|                                          |                          |                         | I/O  | -                     | PIO0_11 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                          |                          |                         | I    | -                     | AD0 — A/D converter, input 0.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                          |                          |                         | 0    | -                     | CT32B0_MAT3 — Match output 3 for 32-bit timer 0.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| PIO1_0 to PIO1_11                        |                          |                         |      |                       | <b>Port 1</b> — Port 1 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 1 pins depends on the function selected through the IOCONFIG register block.                                                                                                                                                             |  |  |  |

| R/PIO1_0/AD1/<br>CT32B1_CAP0             | 22 <u><sup>[5]</sup></u> | yes                     | -    | I;PU                  | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                          |  |  |  |

|                                          |                          |                         | I/O  | -                     | PIO1_0 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                          |                          |                         | I    | -                     | AD1 — A/D converter, input 1.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                          |                          |                         | I    | -                     | CT32B1_CAP0 — Capture input 0 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                        |  |  |  |

| R/PIO1_1/AD2/<br>CT32B1_MAT0             | 23 <u>[5]</u>            | no                      | -    | I;PU                  | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                          |  |  |  |

|                                          |                          |                         | I/O  | -                     | PIO1_1 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                          |                          |                         | I    | -                     | AD2 — A/D converter, input 2.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                          |                          |                         | 0    | -                     | CT32B1_MAT0 — Match output 0 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| R/PIO1_2/AD3/<br>CT32B1_MAT1             | 24 <u><sup>[5]</sup></u> | no                      | -    | I;PU                  | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                          |  |  |  |

|                                          |                          |                         | I/O  | -                     | PIO1_2 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                          |                          |                         | I    | -                     | AD3 — A/D converter, input 3.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                          |                          |                         | 0    | -                     | CT32B1_MAT1 — Match output 1 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| SWDIO/PIO1_3/                            | 25 <u>[5]</u>            | no                      | I/O  | I;PU                  | SWDIO — Serial wire debug input/output.                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| AD4/CT32B1_MAT2                          |                          |                         | I/O  | -                     | PIO1_3 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                          |                          |                         | I    | -                     | AD4 — A/D converter, input 4.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                          |                          |                         | 0    | -                     | CT32B1_MAT2 — Match output 2 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| PIO1_4/AD5/ 26<br>CT32B1_MAT3/<br>WAKEUP |                          | no                      | I/O  | I;PU                  | <b>PIO1_4</b> — General purpose digital input/output pin with 10 ns glitch filter. In Deep power-down mode, this pin serves as the Deep power-down mode wake-up pin with 20 ns glitch filter. Pull this pin HIGH externally before entering Deep power-down mode. Pull this pin LOW to exit Deep power-down mode. A LOW-going pulse as short as 50 ns wakes up the part. |  |  |  |

|                                          |                          |                         | I    | -                     | AD5 — A/D converter, input 5.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                          |                          |                         | 0    | -                     | CT32B1_MAT3 — Match output 3 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| PIO1_5/RTS/                              | 30 <u>[3]</u>            | no                      | I/O  | I;PU                  | PIO1_5 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |  |  |  |

| CT32B0_CAP0                              |                          |                         | 0    | -                     | RTS — Request To Send output for UART.                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                          |                          |                         | I    | -                     | CT32B0_CAP0 — Capture input 0 for 32-bit timer 0.                                                                                                                                                                                                                                                                                                                        |  |  |  |

| PIO1_6/RXD/                              | 31 <u>[3]</u>            | no                      | I/O  | I;PU                  | PIO1_6 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |  |  |  |

| CT32B0_MAT0                              |                          |                         | I    | -                     | RXD — Receiver input for UART.                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                                          |                          |                         | 0    | -                     | CT32B0_MAT0 — Match output 0 for 32-bit timer 0.                                                                                                                                                                                                                                                                                                                         |  |  |  |

#### Table 9. LPC1100 and LPC1100L series: LPC1111/12/13/14 pin description table (HVQFN33 package) ...continued

### 32-bit ARM Cortex-M0 microcontroller

### 7.5 Nested Vectored Interrupt Controller (NVIC)

The Nested Vectored Interrupt Controller (NVIC) is an integral part of the Cortex-M0. The tight coupling to the CPU allows for low interrupt latency and efficient processing of late arriving interrupts.

### 7.5.1 Features

• Controls system exceptions and peripheral interrupts.

#### 32-bit ARM Cortex-M0 microcontroller

- In the LPC1110/11/12/13/14/15, the NVIC supports 32 vectored interrupts including up to 13 inputs to the start logic from individual GPIO pins.

- Four programmable interrupt priority levels with hardware priority level masking.

- Software interrupt generation.

### 7.5.2 Interrupt sources

Each peripheral device has one interrupt line connected to the NVIC but may have several interrupt flags. Individual interrupt flags may also represent more than one interrupt source.

Any GPIO pin (total of up to 42 pins) regardless of the selected function, can be programmed to generate an interrupt on a level, or rising edge or falling edge, or both.

### 7.6 IOCONFIG block

The IOCONFIG block allows selected pins of the microcontroller to have more than one function. Configuration registers control the multiplexers to allow connection between the pin and the on-chip peripherals.

Peripherals should be connected to the appropriate pins prior to being activated and prior to any related interrupt(s) being enabled. Activity of any enabled peripheral function that is not mapped to a related pin should be considered undefined.

### 7.7 Fast general purpose parallel I/O

Device pins that are not connected to a specific peripheral function are controlled by the GPIO registers. Pins may be dynamically configured as inputs or outputs. Multiple outputs can be set or cleared in one write operation.

LPC1110/11/12/13/14/15 use accelerated GPIO functions:

- GPIO registers are a dedicated AHB peripheral so that the fastest possible I/O timing can be achieved.

- Entire port value can be written in one instruction.

Additionally, any GPIO pin (total of up to 42 pins) providing a digital function can be programmed to generate an interrupt on a level, a rising or falling edge, or both.

### 7.7.1 Features

- Bit level port registers allow a single instruction to set or clear any number of bits in one write operation.

- Direction control of individual bits.

- All I/O default to inputs with pull-ups enabled after reset with the exception of the I<sup>2</sup>C-bus pins PIO0\_4 and PIO0\_5.

- Pull-up/pull-down resistor configuration can be programmed through the IOCONFIG block for each GPIO pin (except for pins PIO0\_4 and PIO0\_5).

- On the LPC1100, all GPIO pins (except PIO0\_4 and PIO0\_5) are pulled up to 2.6 V (V<sub>DD</sub> = 3.3 V) if their pull-up resistor is enabled in the IOCONFIG block.

32-bit ARM Cortex-M0 microcontroller

### 8. Limiting values

#### Table 12. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).[1]

| Symbol                 | Parameter                               | Conditions                                                                    | Min  | Max   | Unit |

|------------------------|-----------------------------------------|-------------------------------------------------------------------------------|------|-------|------|

| V <sub>DD</sub>        | supply voltage (core and external rail) | [2]                                                                           | -0.5 | +4.6  | V    |

| VI                     | input voltage                           |                                                                               | -0.5 | +5.5  | V    |

|                        |                                         | 5 V tolerant [2][4]<br>open-drain pins<br>PIO0_4 and<br>PIO0_5                | -0.5 | +5.5  | V    |

| V <sub>IA</sub>        | analog input voltage                    | pin configured as [2][5]<br>analog input                                      | -0.5 | 4.6   | V    |

| I <sub>DD</sub>        | supply current                          | per supply pin                                                                | -    | 100   | mA   |

| I <sub>SS</sub>        | ground current                          | per ground pin                                                                | -    | 100   | mA   |

| I <sub>latch</sub>     | I/O latch-up current                    | $-(0.5V_{DD}) < V_{I} <$<br>(1.5V <sub>DD</sub> );<br>T <sub>i</sub> < 125 °C | -    | 100   | mA   |

| T <sub>stg</sub>       | storage temperature                     | non-operating [6]                                                             | -65  | +150  | °C   |

| T <sub>j(max)</sub>    | maximum junction temperature            |                                                                               | -    | 150   | °C   |

| P <sub>tot(pack)</sub> | total power dissipation (per package)   | based on package<br>heat transfer, not<br>device power<br>consumption         | -    | 1.5   | W    |

| V <sub>ESD</sub>       | electrostatic discharge voltage         | human body [7]<br>model; all pins                                             | -    | +6500 | V    |

[1] The following applies to the limiting values:

a) This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maximum.

b) Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted.

c) The limiting values are stress ratings only. Operating the part at these values is not recommended, and proper operation is not guaranteed. The conditions for functional operation are specified in <u>Table 16</u>.

[2] Maximum/minimum voltage above the maximum operating voltage (see <u>Table 16</u>) and below ground that can be applied for a short time (< 10 ms) to a device without leading to irrecoverable failure. Failure includes the loss of reliability and shorter lifetime of the device.

[3] Including voltage on outputs in 3-state mode.

[4]  $V_{DD}$  present or not present. Compliant with the I<sup>2</sup>C-bus standard. 5.5 V can be applied to this pin when  $V_{DD}$  is powered down.

[5] See <u>Table 18</u> for maximum operating voltage.

- [6] The maximum non-operating storage temperature is different than the temperature for required shelf life which should be determined based on required shelf lifetime. Please refer to the JEDEC spec (J-STD-033B.1) for further details.

- [7] Human body model: equivalent to discharging a 100 pF capacitor through a 1.5 k $\Omega$  series resistor.

32-bit ARM Cortex-M0 microcontroller

## 10. Static characteristics

### 10.1 LPC1100, LPC1100L series

#### Table 16. Static characteristics (LPC1100, LPC1100L series)

$T_{amb} = -40 \$ °C to +85 °C, unless otherwise specified.

| Symbol          | Parameter                               | Conditions                                  |                  | Min      | Typ <u>[1]</u>      | Max | Unit |

|-----------------|-----------------------------------------|---------------------------------------------|------------------|----------|---------------------|-----|------|

| V <sub>DD</sub> | supply voltage (core and external rail) |                                             |                  | 1.8      | 3.3                 | 3.6 | V    |

| LPC1100 se      | ries (LPC111x/101/201/301               | ) power consumption                         |                  |          | U                   |     |      |

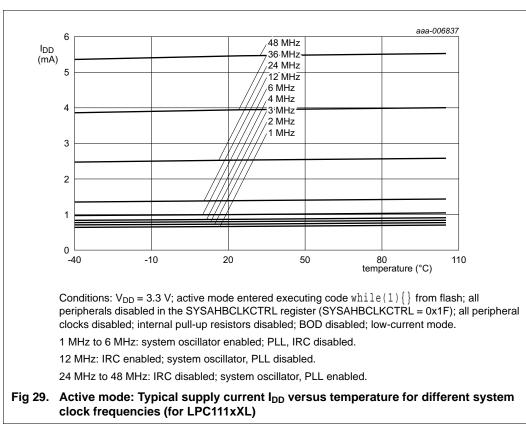

| I <sub>DD</sub> | supply current                          | Active mode; code                           |                  |          |                     |     |      |

|                 |                                         | while(1){}                                  |                  |          |                     |     |      |

|                 |                                         | executed from flash                         |                  |          |                     |     |      |

|                 |                                         | system clock = 12 MHz                       | [2][3][4]        | -        | 3                   | -   | mA   |

|                 |                                         | V <sub>DD</sub> = 3.3 V                     | [5][6]           |          |                     |     |      |

|                 |                                         | system clock = 50 MHz                       | [2][3][5]        | -        | 9                   | -   | mA   |

|                 |                                         | V <sub>DD</sub> = 3.3 V                     | <u>[6][7]</u>    |          |                     |     |      |

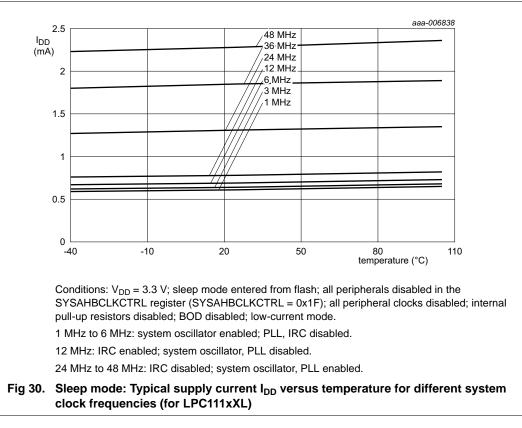

|                 |                                         | Sleep mode;                                 | [2][3][4]        | -        | 2                   | -   | mA   |

|                 |                                         | system clock = 12 MHz                       | [5][6]           |          |                     |     |      |

|                 |                                         | V <sub>DD</sub> = 3.3 V                     |                  |          |                     |     |      |

|                 |                                         | Deep-sleep mode;<br>V <sub>DD</sub> = 3.3 V | [2][3][8]        | -        | 6                   | -   | μΑ   |

|                 |                                         | Deep power-down mode;<br>$V_{DD} = 3.3 V$   | <u>[2][9]</u>    | -        | 220                 | -   | nA   |

| LPC1100L s      | eries (LPC111x/002/102/20               | 2/302) power consumption                    | in low-c         | urrent m | ode <sup>[11]</sup> |     | 4    |

| I <sub>DD</sub> | supply current                          | Active mode; code                           |                  |          |                     |     |      |

|                 |                                         | while(1){}                                  |                  |          |                     |     |      |

|                 |                                         | executed from flash                         |                  |          |                     |     |      |

|                 |                                         | system clock = 1 MHz                        | [2][3][5]        | -        | 840                 | -   | μA   |

|                 |                                         | V <sub>DD</sub> = 3.3 V                     | [6][10]          |          |                     |     |      |

|                 |                                         | system clock = 6 MHz                        | [2][3][5]        | -        | 1                   | -   | mA   |

|                 |                                         | $V_{DD} = 3.3 V$                            | <u>[6][10]</u>   |          |                     |     |      |

|                 |                                         | system clock = 12 MHz                       | [2][3][4]        | -        | 2                   | -   | mA   |

|                 |                                         | $V_{DD} = 3.3 V$                            | [5][6]           |          |                     |     |      |

|                 |                                         | system clock = 50 MHz                       | [2][3][5]        | -        | 7                   | -   | mA   |

|                 |                                         | $V_{DD} = 3.3 V$                            | [6][7]           |          |                     |     |      |

|                 |                                         | Sleep mode;                                 | [2][3][4]        | -        | 1                   | -   | mA   |

|                 |                                         | system clock = 12 MHz                       | [5][6]           |          |                     |     |      |

|                 |                                         | V <sub>DD</sub> = 3.3 V                     |                  |          |                     |     |      |

|                 |                                         | system clock = 50 MHz                       | [2][3][4]        | -        | 5                   | -   | mA   |

|                 |                                         | V <sub>DD</sub> = 3.3 V                     | [5][6]           |          |                     |     |      |

|                 |                                         | Deep-sleep mode;<br>V <sub>DD</sub> = 3.3 V | <u>[2][3][8]</u> | -        | 2                   | -   | μΑ   |

|                 |                                         | Deep power-down mode;<br>$V_{DD} = 3.3 V$   | [2][9]           | -        | 220                 | -   | nA   |

© NXP Semiconductors N.V. 2014. All rights reserved.

### **NXP Semiconductors**

# LPC1110/11/12/13/14/15

32-bit ARM Cortex-M0 microcontroller

32-bit ARM Cortex-M0 microcontroller

All information provided in this document is subject to legal disclaimers

LPC111X

© NXP Semiconductors N.V. 2014. All rights reserved.

32-bit ARM Cortex-M0 microcontroller

32-bit ARM Cortex-M0 microcontroller

Product data sheet

32-bit ARM Cortex-M0 microcontroller

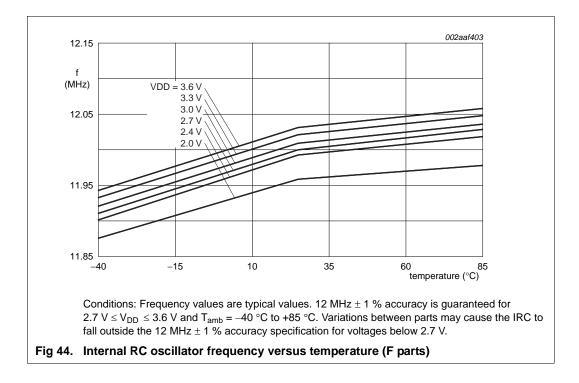

### 11.4 Internal oscillators

#### Table 25. Dynamic characteristic: internal oscillators

$T_{amb} = -40 \ ^{\circ}C \ to +105 \ ^{\circ}C; 2.7 \ V \le V_{DD} \le 3.6 \ V.[1]$

| Symbol               | Parameter                        | Conditions | Min   | Typ <u>[2]</u> | Max   | Unit |

|----------------------|----------------------------------|------------|-------|----------------|-------|------|

| f <sub>osc(RC)</sub> | internal RC oscillator frequency | -          | 11.88 | 12             | 12.12 | MHz  |

[1] Parameters are valid over operating temperature range unless otherwise specified.

[2] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

32-bit ARM Cortex-M0 microcontroller

#### Fig 55. Package outline SOT360-1 (TSSOP20)

32-bit ARM Cortex-M0 microcontroller

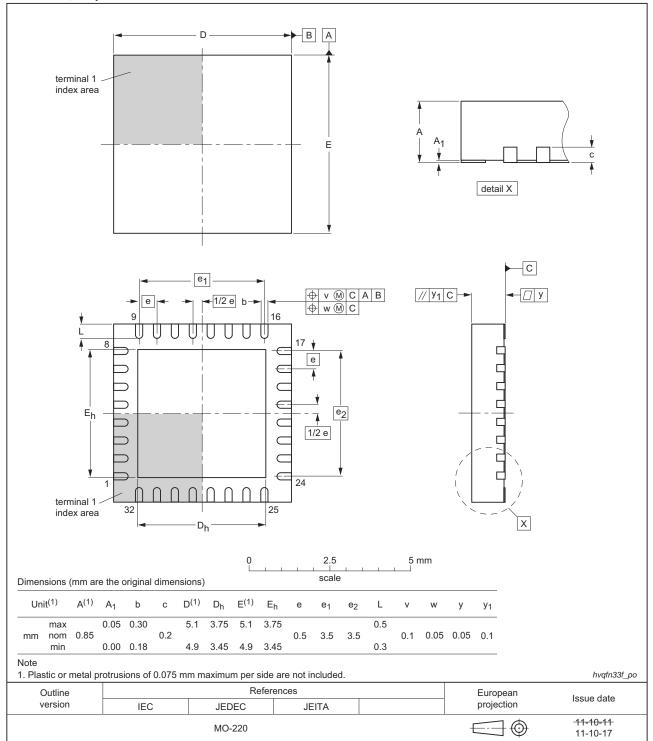

HVQFN33: plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; body 5 x 5 x 0.85 mm

Fig 58. Package outline (HVQFN33 5x5)

All information provided in this document is subject to legal disclaimers.

32-bit ARM Cortex-M0 microcontroller

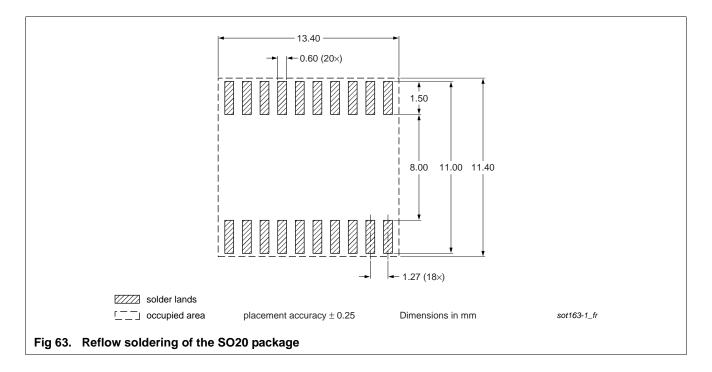

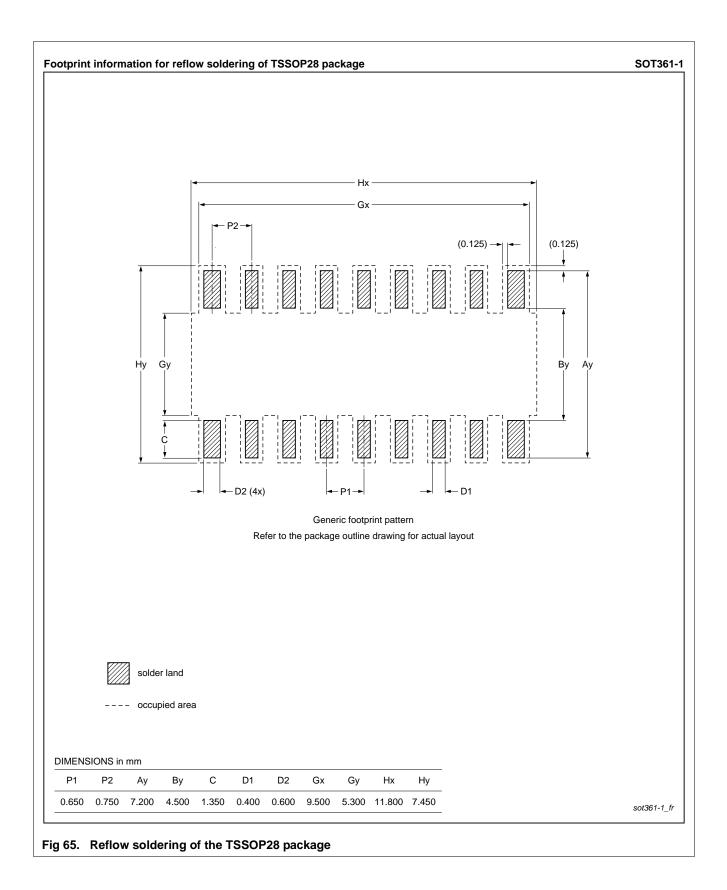

## 14. Soldering

### **NXP Semiconductors**

# LPC1110/11/12/13/14/15

### 32-bit ARM Cortex-M0 microcontroller

32-bit ARM Cortex-M0 microcontroller