Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 50MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 28                                                                         |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 32-HVQFN (5x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1112fhi33-102-5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

32-bit ARM Cortex-M0 microcontroller

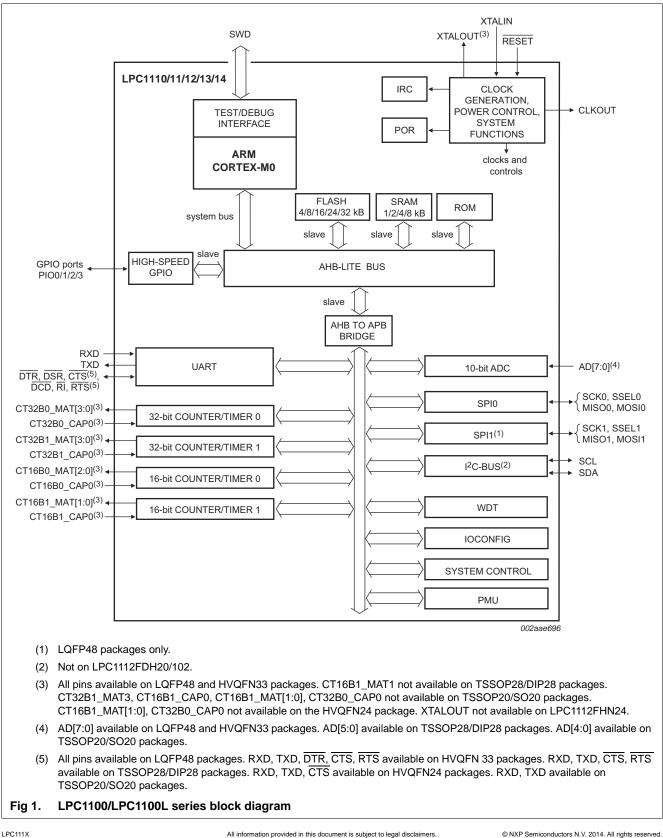

### 5. Block diagram

### 32-bit ARM Cortex-M0 microcontroller

| PIO0_0 to PIO0_11       I/O       Port 0 — Port 0 is a 12-bit I/O port with individual dire function controls for each bit. The operation of port 0 p on the function selected through the IOCONFIG registion on the function on the function selected through the IOCONFIG registion on the function on the function to begin at address 0. In deep power-down mode, this pin must be pulled HIV externally. The RESET pin can be left unconnected or GPIO pin if an external RESET function is not needed power-down mode is not used.         I/O       -       PIO0_0 — General purpose digital input/output pin wit glitch filter.         PIO0_1/CLKOUT/       24       I/O       I; PU       PIO0_1 — General purpose digital input/output pin. A | pins depends<br>ster block.<br>A LOW-going<br>, causing I/O<br>and processor<br>HIGH<br>r be used as a<br>ed and Deep |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| pulse as short as 50 ns on this pin resets the device, or<br>ports and peripherals to take on their default states, ar<br>execution to begin at address 0.<br>In deep power-down mode, this pin must be pulled Hile<br>externally. The RESET pin can be left unconnected or<br>GPIO pin if an external RESET function is not needed<br>power-down mode is not used.<br>I/O - PIO0_0 — General purpose digital input/output pin wit<br>glitch filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | , causing I/O<br>and processor<br>IIGH<br>r be used as a<br>ed and Deep                                               |

| externally. The RESET pin can be left unconnected or GPIO pin if an external RESET function is not needed power-down mode is not used.         I/O       -       PIO0_0 — General purpose digital input/output pin wit glitch filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | r be used as a<br>ed and Deep                                                                                         |

| glitch filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | vith 10 ns                                                                                                            |

| PIO0_1/CLKOUT/ 24 [3] yes I/O I; PU PIO0_1 — General purpose digital input/output pin. A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                       |

| CT32B0_MAT2 on this pin during reset starts the ISP command handl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                       |

| O - CLKOUT — Clockout pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                       |

| O - CT32B0_MAT2 — Match output 2 for 32-bit timer 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                       |

| PIO0_2/SSEL0/ 25 3 yes I/O I; PU PIO0_2 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                       |

| CT16B0_CAP0 I/O - SSEL0 — Slave Select for SPI0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                       |

| I - CT16B0_CAP0 — Capture input 0 for 16-bit timer 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                       |

| PIO0_3 26 3 yes I/O I; PU PIO0_3 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                       |

| PIO0_4/SCL 27 4 yes I/O I; IA PIO0_4 — General purpose digital input/output pin (op                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | open-drain).                                                                                                          |

| I/O     -     SCL — I <sup>2</sup> C-bus, open-drain clock input/output. High-constrainty only if I <sup>2</sup> C Fast-mode Plus is selected in the I/O configuregister.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                       |

| PIO0_5/SDA 5 4 yes I/O I; IA PIO0_5 — General purpose digital input/output pin (op                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | open-drain).                                                                                                          |

| I/O       -       SDA — I <sup>2</sup> C-bus, open-drain data input/output. High-cu         only if I <sup>2</sup> C Fast-mode Plus is selected in the I/O config         register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                       |

| PIO0_6/SCK0 6 [3] yes I/O I; PU <b>PIO0_6</b> — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                       |

| I/O - Scko — Serial clock for SPI0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                       |

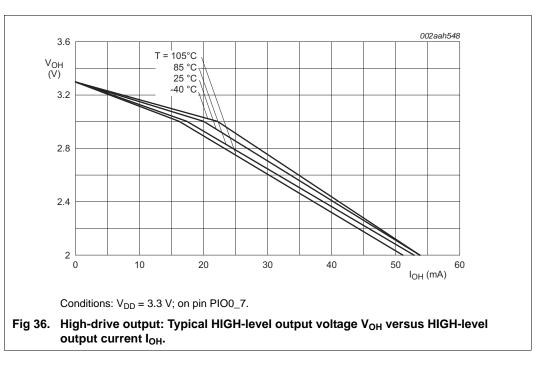

| PIO0_7/CTS       28       3       yes       I/O       I; PU       PIO0_7 — General purpose digital input/output pin (hi output driver).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | nigh-current                                                                                                          |

| I - Clear To Send input for UART.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                       |

| PIO0_8/MISO0/ 1 (3) yes I/O I; PU PIO0_8 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                       |

| CT16B0_MAT0 I/O - MISO0 — Master In Slave Out for SPI0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                       |

| O - CT16B0_MAT0 — Match output 0 for 16-bit timer 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                       |

| PIO0_9/MOSI0/ 2 <sup>[3]</sup> yes I/O I; PU <b>PIO0_9</b> — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                       |

| CT16B0_MAT1 I/O - MOSIO — Master Out Slave In for SPI0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                       |

| O - CT16B0_MAT1 — Match output 1 for 16-bit timer 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                       |

#### Table 7. LPC1100L series: LPC1112/14 pin description table (TSSOP28 and DIP28 packages)

### 32-bit ARM Cortex-M0 microcontroller

| Symbol                                | Pin TSSOP28/<br>DIP28 |            | Start<br>logic<br>input | Туре | state<br>[1] | Description                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------|-----------------------|------------|-------------------------|------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SWCLK/PIO0_10/                        | 3                     | [3]        | yes                     | I    | I; PU        | SWCLK — Serial wire clock.                                                                                                                                                                                                                                                                                                                                               |

| SCK0/<br>CT16B0_MAT2                  |                       |            |                         | I/O  | -            | PIO0_10 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                      |

|                                       |                       |            |                         | I/O  | -            | SCK0 — Serial clock for SPI0.                                                                                                                                                                                                                                                                                                                                            |

|                                       |                       |            |                         | 0    | -            | CT16B0_MAT2 — Match output 2 for 16-bit timer 0.                                                                                                                                                                                                                                                                                                                         |

| R/PIO0_11/<br>AD0/CT32B0_MAT3         | 4                     | <u>[5]</u> | yes                     | I    | I; PU        | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                          |

|                                       |                       |            |                         | I/O  | -            | PIO0_11 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                      |

|                                       |                       |            |                         | I    | -            | AD0 — A/D converter, input 0.                                                                                                                                                                                                                                                                                                                                            |

|                                       |                       |            |                         | 0    | -            | CT32B0_MAT3 — Match output 3 for 32-bit timer 0.                                                                                                                                                                                                                                                                                                                         |

| PIO1_0 to PIO1_9                      |                       |            |                         | I/O  |              | <b>Port 1</b> — Port 1 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 1 pins depends on the function selected through the IOCONFIG register block.                                                                                                                                                             |

| R/PIO1_0/<br>AD1/CT32B1_CAP0          | 9                     | [5]        | yes                     | I    | I; PU        | <ul> <li>R — Reserved. Configure for an alternate function in the IOCONFIG block.</li> </ul>                                                                                                                                                                                                                                                                             |

|                                       |                       |            |                         | I/O  | -            | PIO1_0 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |

|                                       |                       |            |                         | I    | -            | AD1 — A/D converter, input 1.                                                                                                                                                                                                                                                                                                                                            |

|                                       |                       |            |                         | I    | -            | CT32B1_CAP0 — Capture input 0 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                        |

| R/PIO1_1/<br>AD2/CT32B1_MAT0          | 10                    | [5]        | no                      | 0    | I; PU        | <ul> <li>R — Reserved. Configure for an alternate function in the IOCONFIG block.</li> </ul>                                                                                                                                                                                                                                                                             |

|                                       |                       |            |                         | I/O  | -            | PIO1_1 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |

|                                       |                       |            |                         | I    | -            | AD2 — A/D converter, input 2.                                                                                                                                                                                                                                                                                                                                            |

|                                       |                       |            |                         | 0    | -            | CT32B1_MAT0 — Match output 0 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |

| R/PIO1_2/<br>AD3/CT32B1_MAT1          | 11                    | [5]        | no                      | I    | I; PU        | R — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                                 |

|                                       |                       |            |                         | I/O  | -            | PIO1_2 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |

|                                       |                       |            |                         | I    | -            | AD3 — A/D converter, input 3.                                                                                                                                                                                                                                                                                                                                            |

|                                       |                       |            |                         | 0    | -            | CT32B1_MAT1 — Match output 1 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |

| SWDIO/PIO1_3/                         | 12                    | [5]        | no                      | I/O  | I; PU        | SWDIO — Serial wire debug input/output.                                                                                                                                                                                                                                                                                                                                  |

| AD4/CT32B1_MAT2                       |                       |            |                         | I/O  | -            | PIO1_3 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |

|                                       |                       |            |                         | I    | -            | AD4 — A/D converter, input 4.                                                                                                                                                                                                                                                                                                                                            |

|                                       |                       |            |                         | 0    | -            | CT32B1_MAT2 — Match output 2 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |

| PIO1_4/AD5/<br>CT32B1_MAT3/<br>WAKEUP | 13                    | [5]        | no                      | I/O  | I; PU        | <b>PIO1_4</b> — General purpose digital input/output pin with 10 ns glitch filter. In Deep power-down mode, this pin serves as the Deep power-down mode wake-up pin with 20 ns glitch filter. Pull this pin HIGH externally before entering Deep power-down mode. Pull this pin LOW to exit Deep power-down mode. A LOW-going pulse as short as 50 ns wakes up the part. |

|                                       |                       |            |                         | I    | -            | AD5 — A/D converter, input 5.                                                                                                                                                                                                                                                                                                                                            |

|                                       |                       |            |                         | 0    | -            | CT32B1_MAT3 — Match output 3 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |

#### Table 7. LPC1100L series: LPC1112/14 pin description table (TSSOP28 and DIP28 packages) ... continued

#### 32-bit ARM Cortex-M0 microcontroller

### 7.5 Nested Vectored Interrupt Controller (NVIC)

The Nested Vectored Interrupt Controller (NVIC) is an integral part of the Cortex-M0. The tight coupling to the CPU allows for low interrupt latency and efficient processing of late arriving interrupts.

#### 7.5.1 Features

• Controls system exceptions and peripheral interrupts.

32-bit ARM Cortex-M0 microcontroller

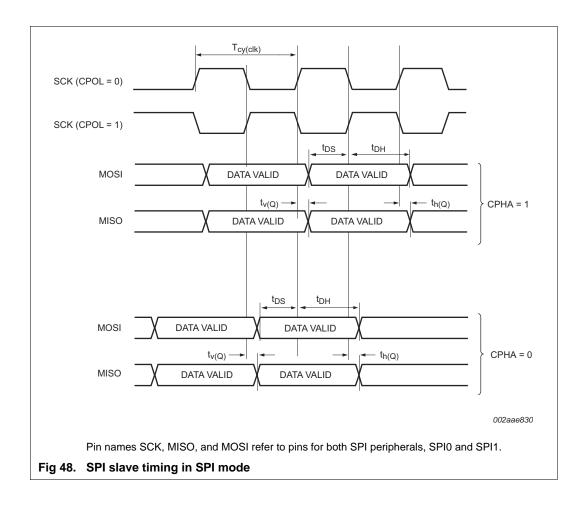

- Master or slave operation

- 8-frame FIFOs for both transmit and receive

- 4-bit to 16-bit frame

### 7.10 I<sup>2</sup>C-bus serial I/O controller

The LPC1110/11/12/13/14/15 contain one I<sup>2</sup>C-bus controller.

Remark: Part LPC1112FDH20/102 does not contain the I<sup>2</sup>C-bus controller.

The I<sup>2</sup>C-bus is bidirectional for inter-IC control using only two wires: a Serial Clock Line (SCL) and a Serial DAta line (SDA). Each device is recognized by a unique address and can operate as either a receiver-only device (e.g., an LCD driver) or a transmitter with the capability to both receive and send information (such as memory). Transmitters and/or receivers can operate in either master or slave mode, depending on whether the chip has to initiate a data transfer or is only addressed. The I<sup>2</sup>C is a multi-master bus and can be controlled by more than one bus master connected to it.

#### 7.10.1 Features

- The I<sup>2</sup>C-interface is a standard I<sup>2</sup>C-bus compliant interface with open-drain pins. The I<sup>2</sup>C-bus interface also supports Fast-mode Plus with bit rates up to 1 Mbit/s.

- Easy to configure as master, slave, or master/slave.

- Programmable clocks allow versatile rate control.

- Bidirectional data transfer between masters and slaves.

- Multi-master bus (no central master).

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus.

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus.

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer.

- The I<sup>2</sup>C-bus can be used for test and diagnostic purposes.

- The I<sup>2</sup>C-bus controller supports multiple address recognition and a bus monitor mode.

#### 7.11 10-bit ADC

The LPC1110/11/12/13/14/15 contain one ADC. It is a single 10-bit successive approximation ADC with eight channels.

#### 7.11.1 Features

- 10-bit successive approximation ADC.

- Input multiplexing among 8 pins.

- Power-down mode.

- Measurement range 0 V to V<sub>DD</sub>.

- 10-bit conversion time  $\ge$  2.44  $\mu$ s (up to 400 kSamples/s).

- Burst conversion mode for single or multiple inputs.

32-bit ARM Cortex-M0 microcontroller

### 10. Static characteristics

### 10.1 LPC1100, LPC1100L series

#### Table 16. Static characteristics (LPC1100, LPC1100L series)

$T_{amb} = -40 \$ °C to +85 °C, unless otherwise specified.

| Symbol          | Parameter                               | Conditions                                  |                  | Min      | Typ <u>[1]</u>      | Max | Unit |

|-----------------|-----------------------------------------|---------------------------------------------|------------------|----------|---------------------|-----|------|

| V <sub>DD</sub> | supply voltage (core and external rail) |                                             |                  | 1.8      | 3.3                 | 3.6 | V    |

| LPC1100 se      | ries (LPC111x/101/201/301               | ) power consumption                         |                  |          | U                   |     |      |

| I <sub>DD</sub> | supply current                          | Active mode; code                           |                  |          |                     |     |      |

|                 |                                         | while(1){}                                  |                  |          |                     |     |      |

|                 |                                         | executed from flash                         |                  |          |                     |     |      |

|                 |                                         | system clock = 12 MHz                       | [2][3][4]        | -        | 3                   | -   | mA   |

|                 |                                         | V <sub>DD</sub> = 3.3 V                     | [5][6]           |          |                     |     |      |

|                 |                                         | system clock = 50 MHz                       | [2][3][5]        | -        | 9                   | -   | mA   |

|                 |                                         | V <sub>DD</sub> = 3.3 V                     | <u>[6][7]</u>    |          |                     |     |      |

|                 |                                         | Sleep mode;                                 | [2][3][4]        | -        | 2                   | -   | mA   |

|                 |                                         | system clock = 12 MHz                       | [5][6]           |          |                     |     |      |

|                 |                                         | V <sub>DD</sub> = 3.3 V                     |                  |          |                     |     |      |

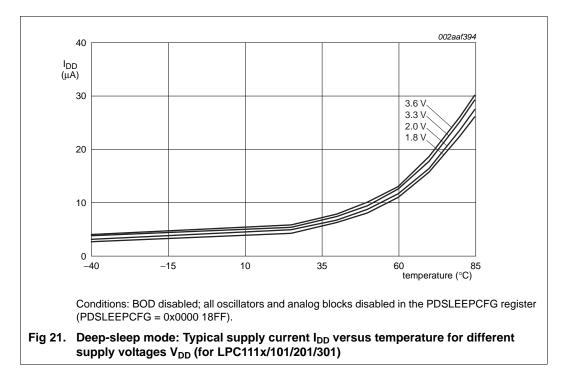

|                 |                                         | Deep-sleep mode;<br>V <sub>DD</sub> = 3.3 V | [2][3][8]        | -        | 6                   | -   | μΑ   |

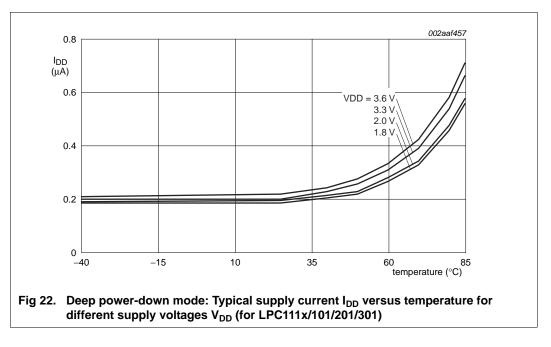

|                 |                                         | Deep power-down mode;<br>$V_{DD} = 3.3 V$   | <u>[2][9]</u>    | -        | 220                 | -   | nA   |

| LPC1100L s      | eries (LPC111x/002/102/20               | 2/302) power consumption                    | in low-c         | urrent m | ode <sup>[11]</sup> |     | 4    |

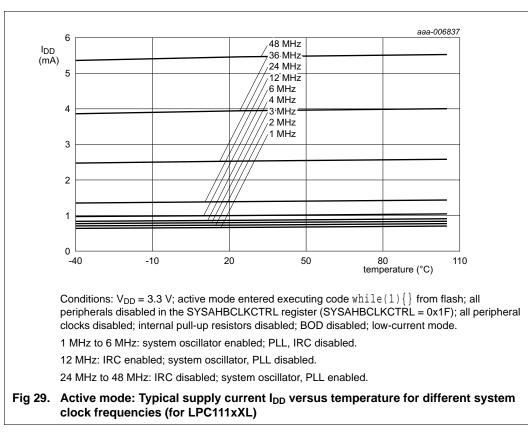

| I <sub>DD</sub> | supply current                          | Active mode; code                           |                  |          |                     |     |      |

|                 |                                         | while(1){}                                  |                  |          |                     |     |      |

|                 |                                         | executed from flash                         |                  |          |                     |     |      |

|                 |                                         | system clock = 1 MHz                        | [2][3][5]        | -        | 840                 | -   | μA   |

|                 |                                         | V <sub>DD</sub> = 3.3 V                     | [6][10]          |          |                     |     |      |

|                 |                                         | system clock = 6 MHz                        | [2][3][5]        | -        | 1                   | -   | mA   |

|                 |                                         | $V_{DD} = 3.3 V$                            | <u>[6][10]</u>   |          |                     |     |      |

|                 |                                         | system clock = 12 MHz                       | [2][3][4]        | -        | 2                   | -   | mA   |

|                 |                                         | $V_{DD} = 3.3 V$                            | [5][6]           |          |                     |     |      |

|                 |                                         | system clock = 50 MHz                       | [2][3][5]        | -        | 7                   | -   | mA   |

|                 |                                         | $V_{DD} = 3.3 V$                            | [6][7]           |          |                     |     |      |

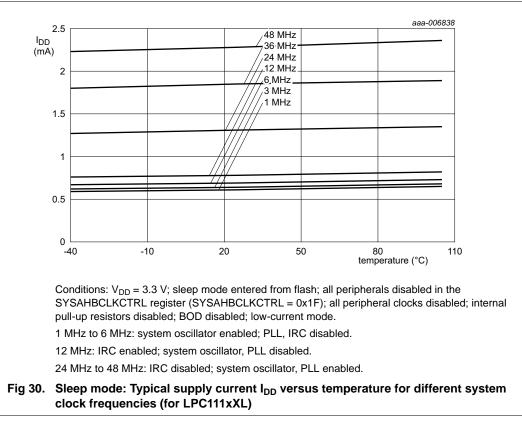

|                 |                                         | Sleep mode;                                 | [2][3][4]        | -        | 1                   | -   | mA   |

|                 |                                         | system clock = 12 MHz                       | [5][6]           |          |                     |     |      |

|                 |                                         | V <sub>DD</sub> = 3.3 V                     |                  |          |                     |     |      |

|                 |                                         | system clock = 50 MHz                       | [2][3][4]        | -        | 5                   | -   | mA   |

|                 |                                         | V <sub>DD</sub> = 3.3 V                     | [5][6]           |          |                     |     |      |

|                 |                                         | Deep-sleep mode;<br>V <sub>DD</sub> = 3.3 V | <u>[2][3][8]</u> | -        | 2                   | -   | μΑ   |

|                 |                                         | Deep power-down mode;<br>$V_{DD} = 3.3 V$   | [2][9]           | -        | 220                 | -   | nA   |