# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 50MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 28                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | ·                                                                          |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 32-HVQFN (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1114fhn33-201-5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

32-bit ARM Cortex-M0 microcontroller

#### **Pinning information** 6.

#### 6.1 Pinning

#### Table 3. Pin description overview Part Pin description table **Pinning diagram** LPC1110FD20 Table 4 Figure 8 LPC1111FDH20/002 Table 4 Figure 9 LPC1112FD20/102 Table 4 Figure 10 LPC1112FDH20/102 Table 5 Figure 9 LPC1112FHN24/202 Table 6 Figure 11 LPC1112FDH28/102 Table 7 Figure 12 LPC1114FDH28/102 Table 7 Figure 13 LPC1114FN28/102 Table 7 Figure 13 LPC1111FHN33/101 Table 9 Figure 6 LPC1111FHN33/102 Table 9 Figure 6 LPC1111JHN33/103 Table 11 Figure 7 LPC1111FHN33/103 Figure 7 Table 11 LPC1111FHN33/201 Table 9 Figure 6 LPC1111FHN33/202 Table 9 Figure 6 LPC1111FHN33/203 Table 11 Figure 7 LPC1111JHN33/203 Table 11 Figure 7 LPC1112FHN33/101 Table 9 Figure 6 LPC1112FHN33/102 Table 9 Figure 6 LPC1112FHN33/103 Table 11 Figure 7 LPC1112JHN33/103 Table 11 Figure 7 LPC1112FHN33/201 Table 9 Figure 6 LPC1112FHN33/202 Table 9 Figure 6 LPC1112FHN33/203 Table 11 Figure 7 LPC1112JHN33/203 Table 11 Figure 7 LPC1112FHI33/202 Table 9 Figure 6 LPC1112FHI33/203 Table 11 Figure 7 LPC1112JHI33/203 Table 11 Figure 7 LPC1113FHN33/201 Table 9 Figure 6 LPC1113FHN33/202 Table 9 Figure 6 LPC1113FHN33/203 Table 11 Figure 7 LPC1113JHN33/203 Table 11 Figure 7 LPC1113FHN33/301 Table 9 Figure 6 LPC1113FHN33/302 Table 9 Figure 6 LPC1113FHN33/303 Table 11 Figure 7 LPC1113JHN33/303 Table 11 Figure 7 LPC1114FHN33/201 Table 9 Figure 6 LPC1114FHN33/202 Table 9 Figure 6

#### 32-bit ARM Cortex-M0 microcontroller

| Symbol                                | Pin                      | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | Description                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|---------------------------------------|--------------------------|-------------------------|------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| R/PIO0_11/AD0/<br>CT32B0_MAT3         | 21 <u>5</u>              | yes                     | -    | I;PU                  | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                          |  |  |  |

|                                       |                          |                         | I/O  | -                     | PIO0_11 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                       |                          |                         | I    | -                     | AD0 — A/D converter, input 0.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                       |                          |                         | 0    | -                     | CT32B0_MAT3 — Match output 3 for 32-bit timer 0.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| PIO1_0 to PIO1_11                     |                          |                         |      |                       | <b>Port 1</b> — Port 1 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 1 pins depends on the function selected through the IOCONFIG register block.                                                                                                                                                             |  |  |  |

| R/PIO1_0/AD1/<br>CT32B1_CAP0          | 22 <u><sup>[5]</sup></u> | yes                     | -    | I;PU                  | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                          |  |  |  |

|                                       |                          |                         | I/O  | -                     | PIO1_0 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                       |                          |                         | I    | -                     | AD1 — A/D converter, input 1.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                       |                          |                         | I    | -                     | CT32B1_CAP0 — Capture input 0 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                        |  |  |  |

| R/PIO1_1/AD2/<br>CT32B1_MAT0          | 23 <u>[5]</u>            | no                      | -    | I;PU                  | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                          |  |  |  |

|                                       |                          |                         | I/O  | -                     | PIO1_1 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                       |                          |                         | I    | -                     | AD2 — A/D converter, input 2.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                       |                          |                         | 0    | -                     | CT32B1_MAT0 — Match output 0 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| R/PIO1_2/AD3/<br>CT32B1_MAT1          | 24 <u><sup>[5]</sup></u> | no                      | -    | I;PU                  | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                          |  |  |  |

|                                       |                          |                         | I/O  | -                     | PIO1_2 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                       |                          |                         | I    | -                     | AD3 — A/D converter, input 3.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                       |                          |                         | 0    | -                     | CT32B1_MAT1 — Match output 1 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| SWDIO/PIO1_3/                         | 25 <u>[5]</u>            | no                      | I/O  | I;PU                  | SWDIO — Serial wire debug input/output.                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| AD4/CT32B1_MAT2                       |                          |                         | I/O  | -                     | PIO1_3 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                       |                          |                         | I    | -                     | AD4 — A/D converter, input 4.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                       |                          |                         | 0    | -                     | CT32B1_MAT2 — Match output 2 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| PIO1_4/AD5/<br>CT32B1_MAT3/<br>WAKEUP | 26 <sup>[5]</sup>        | no                      | I/O  | I;PU                  | <b>PIO1_4</b> — General purpose digital input/output pin with 10 ns glitch filter. In Deep power-down mode, this pin serves as the Deep power-down mode wake-up pin with 20 ns glitch filter. Pull this pin HIGH externally before entering Deep power-down mode. Pull this pin LOW to exit Deep power-down mode. A LOW-going pulse as short as 50 ns wakes up the part. |  |  |  |

|                                       |                          |                         | I    | -                     | AD5 — A/D converter, input 5.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                       |                          |                         | 0    | -                     | CT32B1_MAT3 — Match output 3 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| PIO1_5/RTS/                           | 30 <u>[3]</u>            | no                      | I/O  | I;PU                  | PIO1_5 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |  |  |  |

| CT32B0_CAP0                           |                          |                         | 0    | -                     | RTS — Request To Send output for UART.                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                       |                          |                         | I    | -                     | CT32B0_CAP0 — Capture input 0 for 32-bit timer 0.                                                                                                                                                                                                                                                                                                                        |  |  |  |

| PIO1_6/RXD/                           | 31 <u>[3]</u>            | no                      | I/O  | I;PU                  | PIO1_6 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |  |  |  |

| CT32B0_MAT0                           |                          |                         | I    | -                     | RXD — Receiver input for UART.                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                                       |                          |                         | 0    | -                     | CT32B0_MAT0 — Match output 0 for 32-bit timer 0.                                                                                                                                                                                                                                                                                                                         |  |  |  |

#### Table 9. LPC1100 and LPC1100L series: LPC1111/12/13/14 pin description table (HVQFN33 package) ...continued

#### 32-bit ARM Cortex-M0 microcontroller

| Symbol           | Pin           | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | Description                                                                                                                                                                                                                                                                       |  |  |  |

|------------------|---------------|-------------------------|------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIO1_7/TXD/      | 32 <u>[3]</u> | no                      | I/O  | I;PU                  | PIO1_7 — General purpose digital input/output pin.                                                                                                                                                                                                                                |  |  |  |

| CT32B0_MAT1      |               |                         | 0    | -                     | TXD — Transmitter output for UART.                                                                                                                                                                                                                                                |  |  |  |

|                  |               |                         | 0    | -                     | CT32B0_MAT1 — Match output 1 for 32-bit timer 0.                                                                                                                                                                                                                                  |  |  |  |

| PIO1_8/          | 7 <u>[3]</u>  | no                      | I/O  | I;PU                  | PIO1_8 — General purpose digital input/output pin.                                                                                                                                                                                                                                |  |  |  |

| CT16B1_CAP0      |               |                         | I    | -                     | CT16B1_CAP0 — Capture input 0 for 16-bit timer 1.                                                                                                                                                                                                                                 |  |  |  |

| PIO1_9/          | 12 <u>[3]</u> | no                      | I/O  | I;PU                  | PIO1_9 — General purpose digital input/output pin.                                                                                                                                                                                                                                |  |  |  |

| CT16B1_MAT0      |               |                         | 0    | -                     | CT16B1_MAT0 — Match output 0 for 16-bit timer 1.                                                                                                                                                                                                                                  |  |  |  |

| PIO1_10/AD6/     | 20 <u>[5]</u> | no                      | I/O  | I;PU                  | PIO1_10 — General purpose digital input/output pin.                                                                                                                                                                                                                               |  |  |  |

| CT16B1_MAT1      |               |                         | I    | -                     | AD6 — A/D converter, input 6.                                                                                                                                                                                                                                                     |  |  |  |

|                  |               |                         | 0    | -                     | CT16B1_MAT1 — Match output 1 for 16-bit timer 1.                                                                                                                                                                                                                                  |  |  |  |

| PIO1_11/AD7      | 27 <u>[5]</u> | no                      | I/O  | I;PU                  | PIO1_11 — General purpose digital input/output pin.                                                                                                                                                                                                                               |  |  |  |

|                  |               |                         | I    | -                     | AD7 — A/D converter, input 7.                                                                                                                                                                                                                                                     |  |  |  |

| PIO2_0           |               |                         |      |                       | <b>Port 2</b> — Port 2 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 2 pins depends on the function selected through the IOCONFIG register block. Pins PIO2_1 to PIO2_11 are not available.                            |  |  |  |

| PIO2_0/DTR       | 1 <u>[3]</u>  | no                      | I/O  | I;PU                  | PIO2_0 — General purpose digital input/output pin.                                                                                                                                                                                                                                |  |  |  |

|                  |               |                         | 0    | -                     | DTR — Data Terminal Ready output for UART.                                                                                                                                                                                                                                        |  |  |  |

| PIO3_0 to PIO3_5 |               |                         |      |                       | <b>Port 3</b> — Port 3 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 3 pins depends on the function selected through the IOCONFIG register block. Pins PIO3_0, PIO3_1, PIO3_3 and PIO3_6 to PIO3_11 are not available. |  |  |  |

| PIO3_2           | 28 <u>[3]</u> | no                      | I/O  | I;PU                  | PIO3_2 — General purpose digital input/output pin.                                                                                                                                                                                                                                |  |  |  |

| PIO3_4           | 13 <u>[3]</u> | no                      | I/O  | I;PU                  | PIO3_4 — General purpose digital input/output pin.                                                                                                                                                                                                                                |  |  |  |

| PIO3_5           | 14 <u>[3]</u> | no                      | I/O  | I;PU                  | PIO3_5 — General purpose digital input/output pin.                                                                                                                                                                                                                                |  |  |  |

| V <sub>DD</sub>  | 6; 29         | -                       | I    | -                     | 3.3 V supply voltage to the internal regulator, the external rail, and the ADC. Also used as the ADC reference voltage.                                                                                                                                                           |  |  |  |

| XTALIN           | 4 <u>[6]</u>  | -                       | I    | -                     | Input to the oscillator circuit and internal clock generator circuits. Input voltage must not exceed 1.8 V.                                                                                                                                                                       |  |  |  |

| XTALOUT          | 5 <u>[6]</u>  | -                       | 0    | -                     | Output from the oscillator amplifier.                                                                                                                                                                                                                                             |  |  |  |

| V <sub>SS</sub>  | 33            | -                       | -    | -                     | Thermal pad. Connect to ground.                                                                                                                                                                                                                                                   |  |  |  |

#### Table 9. LPC1100 and LPC1100L series: LPC1111/12/13/14 pin description table (HVQFN33 package) ...continued

[1] Pin state at reset for default function: I = Input; O = Output; PU = internal pull-up enabled (pins pulled up to 2.6 V for LPC111x/101/201/301, pins pulled up to full V<sub>DD</sub> level on LPC111x/002/102/202/302 (V<sub>DD</sub> = 3.3 V)); IA = inactive, no pull-up/down enabled.

[2] 5 V tolerant pad. RESET functionality is not available in Deep power-down mode. Use the WAKEUP pin to reset the chip and wake up from Deep power-down mode. An external pull-up resistor is required on this pin for the Deep power-down mode. See <u>Figure 52</u> for the reset pad configuration.

[3] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors and configurable hysteresis (see Figure 51).

[4] I<sup>2</sup>C-bus pads compliant with the I<sup>2</sup>C-bus specification for I<sup>2</sup>C standard mode and I<sup>2</sup>C Fast-mode Plus. The pin requires an external pull-up to provide output functionality. When power is switched off, this pin is floating and does not disturb the I2C lines. Open-drain configuration applies to all functions on this pin.

[5] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors, configurable hysteresis, and analog input. When configured as a ADC input, digital section of the pad is disabled, and the pin is not 5 V tolerant (see Figure 51).

#### 32-bit ARM Cortex-M0 microcontroller

| Symbol                        | LQFP48                   | TFBGA48                  | Start<br>logic<br>input                            | Туре | Reset<br>state<br>[1] | Description                                                                                                                                                                                                  |

|-------------------------------|--------------------------|--------------------------|----------------------------------------------------|------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO0_8/MISO0/                 | 27 <u>[3]</u>            | F8 <u>[3]</u>            | yes                                                | I/O  | I; PU                 | PIO0_8 — General purpose digital input/output pin.                                                                                                                                                           |

| CT16B0_MAT0                   |                          |                          |                                                    | I/O  | -                     | MISO0 — Master In Slave Out for SPI0.                                                                                                                                                                        |

|                               |                          |                          |                                                    | 0    | -                     | CT16B0_MAT0 — Match output 0 for 16-bit timer 0.                                                                                                                                                             |

| PIO0_9/MOSI0/                 | 28 <u>[3]</u>            | F7 <u>[3]</u>            | yes                                                | I/O  | I; PU                 | PIO0_9 — General purpose digital input/output pin.                                                                                                                                                           |

| CT16B0_MAT1                   |                          |                          |                                                    | I/O  | -                     | MOSI0 — Master Out Slave In for SPI0.                                                                                                                                                                        |

|                               |                          |                          |                                                    | 0    | -                     | CT16B0_MAT1 — Match output 1 for 16-bit timer 0.                                                                                                                                                             |

| SWCLK/PIO0_10/                | 29 <u>[3]</u>            | E7 <u>[3]</u>            | yes                                                | I    | I; PU                 | SWCLK — Serial wire clock.                                                                                                                                                                                   |

| I/O<br>I/16B0_MAT2            |                          | -                        | PIO0_10 — General purpose digital input/output pir |      |                       |                                                                                                                                                                                                              |

| CT16B0_MAT2                   |                          |                          |                                                    | I/O  | -                     | SCK0 — Serial clock for SPI0.                                                                                                                                                                                |

|                               |                          |                          |                                                    | 0    | -                     | CT16B0_MAT2 — Match output 2 for 16-bit timer 0.                                                                                                                                                             |

| R/PIO0_11/<br>AD0/CT32B0_MAT3 | 32 <u>[5]</u>            | D8 <u>[5]</u>            | yes                                                | I    | I; PU                 | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                              |

|                               |                          |                          |                                                    | I/O  | -                     | <b>PIO0_11</b> — General purpose digital input/output pin.                                                                                                                                                   |

|                               |                          |                          |                                                    | I    | -                     | AD0 — A/D converter, input 0.                                                                                                                                                                                |

|                               |                          |                          |                                                    | 0    | -                     | CT32B0_MAT3 — Match output 3 for 32-bit timer 0.                                                                                                                                                             |

| PIO1_0 to PIO1_11             |                          |                          |                                                    | I/O  |                       | <b>Port 1</b> — Port 1 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 1 pins depends on the function selected through the IOCONFIG register block. |

| R/PIO1_0/<br>AD1/CT32B1_CAP0  | 33 <u>[5]</u>            | C7 <u><sup>[5]</sup></u> | yes                                                | 1    | I; PU                 | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                              |

|                               |                          |                          |                                                    | I/O  | -                     | <b>PIO1_0</b> — General purpose digital input/output pin.                                                                                                                                                    |

|                               |                          |                          |                                                    | I    | -                     | AD1 — A/D converter, input 1.                                                                                                                                                                                |

|                               |                          |                          |                                                    | I    | -                     | CT32B1_CAP0 — Capture input 0 for 32-bit timer 1.                                                                                                                                                            |

| R/PIO1_1/<br>AD2/CT32B1_MAT0  | 34 <u><sup>[5]</sup></u> | C8[5]                    | no                                                 | 0    | I; PU                 | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                              |

|                               |                          |                          |                                                    | I/O  | -                     | <b>PIO1_1</b> — General purpose digital input/output pin.                                                                                                                                                    |

|                               |                          |                          |                                                    | I    | -                     | AD2 — A/D converter, input 2.                                                                                                                                                                                |

|                               |                          |                          |                                                    | 0    | -                     | CT32B1_MAT0 — Match output 0 for 32-bit timer 1.                                                                                                                                                             |

| R/PIO1_2/<br>AD3/CT32B1_MAT1  | 35 <u>[5]</u>            | B7 <u>[5]</u>            | no                                                 | I    | I; PU                 | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                              |

|                               |                          |                          |                                                    | I/O  | -                     | PIO1_2 — General purpose digital input/output pin.                                                                                                                                                           |

|                               |                          |                          |                                                    | I    | -                     | AD3 — A/D converter, input 3.                                                                                                                                                                                |

|                               |                          |                          |                                                    | 0    | -                     | CT32B1_MAT1 — Match output 1 for 32-bit timer 1.                                                                                                                                                             |

| SWDIO/PIO1_3/                 | 39 <u>[5]</u>            | B6[5]                    | no                                                 | I/O  | I; PU                 | SWDIO — Serial wire debug input/output.                                                                                                                                                                      |

| AD4/CT32B1_MAT2               |                          |                          |                                                    | I/O  | -                     | PIO1_3 — General purpose digital input/output pin.                                                                                                                                                           |

|                               |                          |                          |                                                    | I    | -                     | AD4 — A/D converter, input 4.                                                                                                                                                                                |

|                               |                          |                          |                                                    | 0    | -                     | CT32B1_MAT2 — Match output 2 for 32-bit timer 1.                                                                                                                                                             |

#### Table 10. LPC1100XL series: LPC1113/14/15 pin description table (LQFP48 and TFBGA48 package) ... continued

#### 32-bit ARM Cortex-M0 microcontroller

| Symbol               | LQFP48        | TFBGA48       | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | Description                                                                                                             |

|----------------------|---------------|---------------|-------------------------|------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| PIO3_2/DCD/          | 43 <u>[3]</u> | A4 <u>[3]</u> | no                      | I/O  | I; PU                 | PIO3_2 — General purpose digital input/output pin.                                                                      |

| CT16B0_MAT2/<br>SCK1 |               |               |                         | I    | -                     | <b>DCD</b> — Data Carrier Detect input for UART.                                                                        |

| 00111                |               |               |                         | 0    | -                     | CT16B0_MAT2 — Match output 2 for 16-bit timer 0.                                                                        |

|                      |               |               |                         | I/O  | -                     | SCK1 — Serial clock for SPI1.                                                                                           |

| PIO3_3/RI/           | 48 <u>[3]</u> | A2[3]         | no                      | I/O  | I; PU                 | PIO3_3 — General purpose digital input/output pin.                                                                      |

| CT16B0_CAP0          |               |               |                         | I    | -                     | <b>RI</b> — Ring Indicator input for UART.                                                                              |

|                      |               |               |                         | I    | -                     | CT16B0_CAP0 — Capture input 0 for 16-bit timer 0.                                                                       |

| PIO3_4/              | 18 <u>[3]</u> | H4 <u>[3]</u> | no                      | I/O  | I; PU                 | PIO3_4 — General purpose digital input/output pin.                                                                      |

| CT16B0_CAP1/RXD      |               |               |                         | I    | -                     | CT16B0_CAP1 — Capture input 1 for 16-bit timer 0.                                                                       |

|                      |               |               |                         | I    | -                     | RXD — Receiver input for UART                                                                                           |

| PIO3_5/              | 21 <u>[3]</u> | G6 <u>[3]</u> | no                      | I/O  | I; PU                 | PIO3_5 — General purpose digital input/output pin.                                                                      |

| CT16B1_CAP1/TXD      |               |               |                         | I    | -                     | CT16B1_CAP1 — Capture input 1 for 16-bit timer 1.                                                                       |

|                      |               |               |                         | 0    | -                     | TXD — Transmitter output for UART                                                                                       |

| V <sub>DD</sub>      | 8; 44         | E2;<br>B4     | -                       | I    | -                     | 3.3 V supply voltage to the internal regulator, the external rail, and the ADC. Also used as the ADC reference voltage. |

| XTALIN               | 6 <u>[6]</u>  | D1 <u>6</u>   | -                       | I    | -                     | Input to the oscillator circuit and internal clock generator circuits. Input voltage must not exceed 1.8 V.             |

| XTALOUT              | 7 <u>[6]</u>  | E1 <u>[6]</u> | -                       | 0    | -                     | Output from the oscillator amplifier.                                                                                   |

| V <sub>SS</sub>      | 5; 41         | D2;<br>B5     | -                       | 1    | -                     | Ground.                                                                                                                 |

#### Table 10. LPC1100XL series: LPC1113/14/15 pin description table (LQFP48 and TFBGA48 package) ... continued

[1] Pin state at reset for default function: I = Input; O = Output; PU = internal pull-up enabled (pins pulled up to full  $V_{DD}$  level ( $V_{DD}$  = 3.3 V)); IA = inactive, no pull-up/down enabled.

[2] 5 V tolerant pad. RESET functionality is not available in Deep power-down mode. Use the WAKEUP pin to reset the chip and wake up from Deep power-down mode. An external pull-up resistor is required on this pin for the Deep power-down mode. See <u>Figure 52</u> for the reset pad configuration.

[3] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors and configurable hysteresis (see Figure 51).

[4] I<sup>2</sup>C-bus pads compliant with the I<sup>2</sup>C-bus specification for I<sup>2</sup>C standard mode and I<sup>2</sup>C Fast-mode Plus. The pin requires an external pull-up to provide output functionality. When power is switched off, this pin is floating and does not disturb the I2C lines. Open-drain configuration applies to all functions on this pin.

[5] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors, configurable hysteresis, and analog input. When configured as a ADC input, digital section of the pad is disabled and the pin is not 5 V tolerant (see Figure 51).

[6] When the system oscillator is not used, connect XTALIN and XTALOUT as follows: XTALIN can be left floating or can be grounded (grounding is preferred to reduce susceptibility to noise). XTALOUT should be left floating.

LPC111X

40 of 127

#### 32-bit ARM Cortex-M0 microcontroller

### 7.5 Nested Vectored Interrupt Controller (NVIC)

The Nested Vectored Interrupt Controller (NVIC) is an integral part of the Cortex-M0. The tight coupling to the CPU allows for low interrupt latency and efficient processing of late arriving interrupts.

#### 7.5.1 Features

• Controls system exceptions and peripheral interrupts.

#### 32-bit ARM Cortex-M0 microcontroller

- On the LPC1100L and LPC1100XL series, all GPIO pins (except PIO0\_4 and PIO0\_5) are pulled up to 3.3 V (V<sub>DD</sub> = 3.3 V) if their pull-up resistor is enabled in the IOCONFIG block.

- Programmable open-drain mode for series LPC1100L and LPC1100XL.

#### 7.8 UART

The LPC1110/11/12/13/14/15 contain one UART.

Support for RS-485/9-bit mode allows both software address detection and automatic address detection using 9-bit mode.

The UART includes a fractional baud rate generator. Standard baud rates such as 115200 Bd can be achieved with any crystal frequency above 2 MHz.

#### 7.8.1 Features

- Maximum UART data bit rate of 3.125 MBit/s.

- 16 Byte Receive and Transmit FIFOs.

- Register locations conform to 16C550 industry standard.

- Receiver FIFO trigger points at 1 B, 4 B, 8 B, and 14 B.

- Built-in fractional baud rate generator covering wide range of baud rates without a need for external crystals of particular values.

- FIFO control mechanism that enables software flow control implementation.

- Support for RS-485/9-bit mode.

- Support for modem control.

### 7.9 SPI serial I/O controller

The LPC1100 and LPC1100L series contain two SPI controllers on the LQFP48 package and one SPI controller on the HVQFN33/TSSOP28/DIP28/TSSOP20/SO20 packages (SPI0).

The LPC1100XL series contain two SPI controllers.

Both SPI controllers support SSP features.

The SPI controller is capable of operation on a SSP, 4-wire SSI, or Microwire bus. It can interact with multiple masters and slaves on the bus. Only a single master and a single slave can communicate on the bus during a given data transfer. The SPI supports full duplex transfers, with frames of 4 bits to 16 bits of data flowing from the master to the slave and from the slave to the master. In practice, often only one of these data flows carries meaningful data.

#### 7.9.1 Features

- Maximum SPI speed of 25 Mbit/s (master) or 4.17 Mbit/s (slave) (in SSP mode)

- Compatible with Motorola SPI, 4-wire Texas Instruments SSI, and National Semiconductor Microwire buses

- Synchronous serial communication

32-bit ARM Cortex-M0 microcontroller

The system oscillator operates at frequencies of 1 MHz to 25 MHz. This frequency can be boosted to a higher frequency, up to the maximum CPU operating frequency, by the system PLL.

#### 7.16.1.3 Watchdog oscillator

The watchdog oscillator can be used as a clock source that directly drives the CPU, the watchdog timer, or the CLKOUT pin. The watchdog oscillator nominal frequency is programmable between 9.4 kHz and 2.3 MHz. The frequency spread over processing and temperature is  $\pm$ 40 %.

#### 7.16.2 System PLL

The PLL accepts an input clock frequency in the range of 10 MHz to 25 MHz. The input frequency is multiplied up to a high frequency with a Current Controlled Oscillator (CCO). The multiplier can be an integer value from 1 to 32. The CCO operates in the range of 156 MHz to 320 MHz, so there is an additional divider in the loop to keep the CCO within its frequency range while the PLL is providing the desired output frequency. The PLL output frequency must be lower than 100 MHz. The output divider may be set to divide by 2, 4, 8, or 16 to produce the output clock. Since the minimum output divider value is 2, it is insured that the PLL output has a 50 % duty cycle. The PLL is turned off and bypassed following a chip reset and may be enabled by software. The program must configure and activate the PLL, wait for the PLL to lock, and then connect to the PLL as a clock source. The PLL settling time is 100  $\mu$ s.

#### 7.16.3 Clock output

The LPC1110/11/12/13/14/15 features a clock output function that routes the IRC oscillator, the system oscillator, the watchdog oscillator, or the main clock to an output pin.

#### 7.16.4 Wake-up process

The LPC1110/11/12/13/14/15 begin operation at power-up and when awakened from Deep power-down mode by using the 12 MHz IRC oscillator as the clock source. This allows chip operation to resume quickly. If the system oscillator or the PLL is needed by the application, software will need to enable these features and wait for them to stabilize before they are used as a clock source.

#### 7.16.5 Power control

The LPC1110/11/12/13/14/15 support a variety of power control features. There are three special modes of processor power reduction: Sleep mode, Deep-sleep mode, and Deep power-down mode. The CPU clock rate may also be controlled as needed by changing clock sources, reconfiguring PLL values, and/or altering the CPU clock divider value. This allows a trade-off of power versus processing speed based on application requirements. In addition, a register is provided for shutting down the clocks to individual on-chip peripherals, allowing fine tuning of power consumption by eliminating all dynamic power use in any peripherals that are not required for the application. Selected peripherals have their own clock divider which provides even better power control.

#### 7.16.5.1 Power profiles (LPC1100L and LPC1100XL series only)

The power consumption in Active and Sleep modes can be optimized for the application through simple calls to the power profile. The power configuration routine configures the LPC1110/11/12/13/14/15 for one of the following power modes:

32-bit ARM Cortex-M0 microcontroller

The start logic must be configured in the system configuration block and in the NVIC before being used.

#### 7.17.2 Reset

Reset has four sources on the LPC1110/11/12/13/14/15: the RESET pin, the Watchdog reset, Power-On Reset (POR), and the BrownOut Detection (BOD) circuit. The RESET pin is a Schmitt trigger input pin. Assertion of chip reset by any source, once the operating voltage attains a usable level, starts the IRC and initializes the flash controller.

A LOW-going pulse as short as 50 ns resets the part.

When the internal Reset is removed, the processor begins executing at address 0, which is initially the Reset vector mapped from the boot block. At that point, all of the processor and peripheral registers have been initialized to predetermined values.

An external pull-up resistor is required on the RESET pin if Deep power-down mode is used.

#### 7.17.3 Brownout detection

The LPC1110/11/12/13/14/15 includes up to four levels for monitoring the voltage on the  $V_{DD}$  pin. If this voltage falls below one of the selected levels, the BOD asserts an interrupt signal to the NVIC. This signal can be enabled for interrupt in the Interrupt Enable Register in the NVIC in order to cause a CPU interrupt; if not, software can monitor the signal by reading a dedicated status register. Four threshold levels can be selected to cause a forced reset of the chip.

#### 7.17.4 Code security (Code Read Protection - CRP)

This feature of the LPC1110/11/12/13/14/15 allows user to enable different levels of security in the system so that access to the on-chip flash and use of the Serial Wire Debugger (SWD) and In-System Programming (ISP) can be restricted. When needed, CRP is invoked by programming a specific pattern into a dedicated flash location. IAP commands are not affected by the CRP.

In addition, ISP entry via the PIO0\_1 pin can be disabled without enabling CRP. For details see the *LPC111x user manual*.

There are three levels of Code Read Protection:

- CRP1 disables access to the chip via the SWD and allows partial flash update (excluding flash sector 0) using a limited set of the ISP commands. This mode is useful when CRP is required and flash field updates are needed but all sectors can not be erased.

- 2. CRP2 disables access to the chip via the SWD and only allows full flash erase and update using a reduced set of the ISP commands.

- 3. Running an application with level CRP3 selected fully disables any access to the chip via the SWD pins and the ISP. This mode effectively disables ISP override using PIO0\_1 pin, too. It is up to the user's application to provide (if needed) flash update mechanism using IAP calls or call reinvoke ISP command to enable flash update via the UART.

32-bit ARM Cortex-M0 microcontroller

#### Table 17. Static characteristics (LPC1100XL series) ... continued

#### $T_{amb} = -40$ °C to +105 °C, unless otherwise specified.

| Symbol               | Parameter                   | Conditions                                    | Min  | Typ[1] | Max  | Unit |

|----------------------|-----------------------------|-----------------------------------------------|------|--------|------|------|

| Oscillator p         | ins                         |                                               |      | U      |      |      |

| V <sub>i(xtal)</sub> | crystal input voltage       |                                               | -0.5 | 1.8    | 1.95 | V    |

| V <sub>o(xtal)</sub> | crystal output voltage      |                                               | -0.5 | 1.8    | 1.95 | V    |

| Pin capacita         | ance                        |                                               |      | L      |      |      |

| C <sub>io</sub>      | input/output<br>capacitance | pins configured for analog function           | -    | -      | 7.1  | pF   |

|                      |                             | I <sup>2</sup> C-bus pins (PIO0_4 and PIO0_5) | -    | -      | 2.5  | pF   |

|                      |                             | pins configured as GPIO                       | -    | -      | 2.8  | pF   |

[1] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

[2] Low-current mode PWR\_LOW\_CURRENT selected when running the set\_power routine in the power profiles.

[3]  $T_{amb} = 25 \ ^{\circ}C.$

[4] I<sub>DD</sub> measurements were performed with all pins configured as GPIO outputs driven LOW and pull-up resistors disabled.

[5] System oscillator enabled; IRC disabled; system PLL disabled.

[6] BOD disabled.

[7] All peripherals disabled in the SYSAHBCLKCTRL register. Peripheral clocks to UART and SPI0/1 disabled in system configuration block.

[8] IRC enabled; system oscillator disabled; system PLL disabled.

[9] IRC disabled; system oscillator enabled; system PLL enabled.

[10] All oscillators and analog blocks turned off in the PDSLEEPCFG register; PDSLEEPCFG = 0x0000 18FF.

[11] 105 °C spec applies only to parts with the J designator (e.g. LPC1115JET48).

- [12] WAKEUP pin and RESET pin are pulled HIGH externally.

- [13] Including voltage on outputs in 3-state mode.

- [14] V<sub>DD</sub> supply voltage must be present.

- [15] 3-state outputs go into 3-state mode in Deep power-down mode.

- [16] Allowed as long as the current limit does not exceed the maximum current allowed by the device.

[17] To V<sub>SS</sub>.

32-bit ARM Cortex-M0 microcontroller

### **10.3 ADC static characteristics**

#### Table 18. ADC static characteristics

$T_{amb} = -40 \text{ }^{\circ}\text{C}$  to +105  $\text{ }^{\circ}\text{C}$  unless otherwise specified; ADC frequency 4.5 MHz,  $V_{DD} = 2.5 \text{ V}$  to 3.6 V.

| Symbol              | Parameter                           | Conditions | Min | Тур | Max             | Unit |

|---------------------|-------------------------------------|------------|-----|-----|-----------------|------|

| V <sub>IA</sub>     | analog input voltage                |            | 0   | -   | V <sub>DD</sub> | V    |

| C <sub>ia</sub>     | analog input capacitance            |            | -   | -   | 1               | pF   |

| E <sub>D</sub>      | differential linearity error        | [1][2]     | -   | -   | ± 1             | LSB  |

| E <sub>L(adj)</sub> | integral non-linearity              | [3]        | -   | -   | ± 1.5           | LSB  |

| E <sub>O</sub>      | offset error                        | [4]        | -   | -   | ± 3.5           | LSB  |

| E <sub>G</sub>      | gain error                          | [5]        | -   | -   | 0.6             | %    |

| E <sub>T</sub>      | absolute error                      | [6]        | -   | -   | ± 4             | LSB  |

| R <sub>vsi</sub>    | voltage source interface resistance |            | -   | -   | 40              | kΩ   |

| R <sub>i</sub>      | input resistance                    | [7][8]     | -   | -   | 2.5             | MΩ   |

[1] The ADC is monotonic, there are no missing codes.

[2] The differential linearity error (E<sub>D</sub>) is the difference between the actual step width and the ideal step width. See Figure 17.

[3] The integral non-linearity (E<sub>L(adj)</sub>) is the peak difference between the center of the steps of the actual and the ideal transfer curve after appropriate adjustment of gain and offset errors. See Figure 17.

[4] The offset error (E<sub>O</sub>) is the absolute difference between the straight line which fits the actual curve and the straight line which fits the ideal curve. See <u>Figure 17</u>.

[5] The gain error (E<sub>G</sub>) is the relative difference in percent between the straight line fitting the actual transfer curve after removing offset error, and the straight line which fits the ideal transfer curve. See <u>Figure 17</u>.

[6] The absolute error ( $E_T$ ) is the maximum difference between the center of the steps of the actual transfer curve of the non-calibrated ADC and the ideal transfer curve. See Figure 17.

[7]  $T_{amb} = 25 \text{ °C}$ ; maximum sampling frequency  $f_s = 400 \text{ kSamples/s}$  and analog input capacitance  $C_{ia} = 1 \text{ pF}$ .

[8] Input resistance  $R_i$  depends on the sampling frequency  $f_s$ :  $R_i = 1 / (f_s \times C_{ia})$ .

32-bit ARM Cortex-M0 microcontroller

32-bit ARM Cortex-M0 microcontroller

#### 32-bit ARM Cortex-M0 microcontroller

| Symbol                | Parameter                        | Conditions                                                                 | Min | Typ <u>[1]</u> | Max | Unit |

|-----------------------|----------------------------------|----------------------------------------------------------------------------|-----|----------------|-----|------|

| f <sub>osc(int)</sub> | internal oscillator<br>frequency | DIVSEL = 0x1F, FREQSEL = 0x1 [2][3]<br>in the WDTOSCCTRL register;         | -   | 9.4            | -   | kHz  |

|                       |                                  | DIVSEL = 0x00, FREQSEL = 0xF $\frac{[2][3]}{1}$ in the WDTOSCCTRL register | -   | 2300           | -   | kHz  |

Table 26. Dynamic characteristics: Watchdog oscillator

[1] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

- [2] The typical frequency spread over processing and temperature (T<sub>amb</sub> = -40 °C to +105 °C) is  $\pm$ 40 %.

- [3] See the LPC111x user manual.

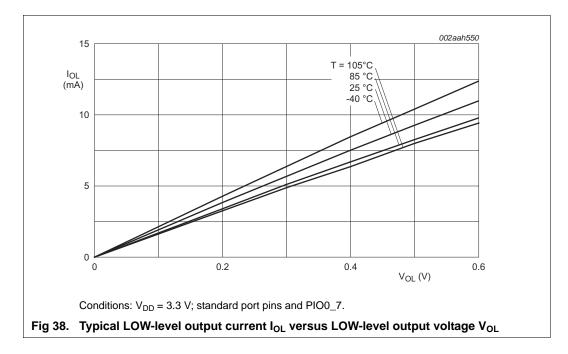

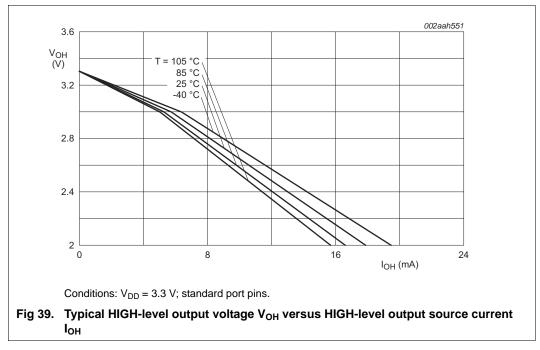

#### 11.5 I/O pins

| Table 27.       | Dynamic characteristic: I/O pins <sup>[1]</sup>           |

|-----------------|-----------------------------------------------------------|

| $T_{amb} = -40$ | °C to +105 °C; 3.0 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V. |

| amb            |           |                                |     |     |     |      |

|----------------|-----------|--------------------------------|-----|-----|-----|------|

| Symbol         | Parameter | Conditions                     | Min | Тур | Max | Unit |

| t <sub>r</sub> |           | pin<br>configured as<br>output | 3.0 | -   | 5.0 | ns   |

| t <sub>f</sub> | fall time | pin<br>configured as<br>output | 2.5 | -   | 5.0 | ns   |

[1] Applies to standard port pins and RESET pin.

#### 32-bit ARM Cortex-M0 microcontroller

### 12.4 XTAL Printed Circuit Board (PCB) layout guidelines

The crystal should be connected on the PCB as close as possible to the oscillator input and output pins of the chip. Take care that the load capacitors  $C_{X1}$ ,  $C_{X2}$ , and  $C_{X3}$  in case of third overtone crystal usage have a common ground plane. The external components must also be connected to the ground plain. Loops must be made as small as possible in order to keep the noise coupled in via the PCB as small as possible. Also parasitics should stay as small as possible. Values of  $C_{X1}$  and  $C_{X2}$  should be chosen smaller accordingly to the increase in parasitics of the PCB layout.

#### 12.5 Standard I/O pad configuration

Figure 51 shows the possible pin modes for standard I/O pins with analog input function:

- Digital output driver

- Digital input: Pull-up enabled/disabled

- Digital input: Pull-down enabled/disabled

- Digital input: Repeater mode enabled/disabled

- Digital output: Pseudo open-drain mode enable/disabled

- Analog input

32-bit ARM Cortex-M0 microcontroller

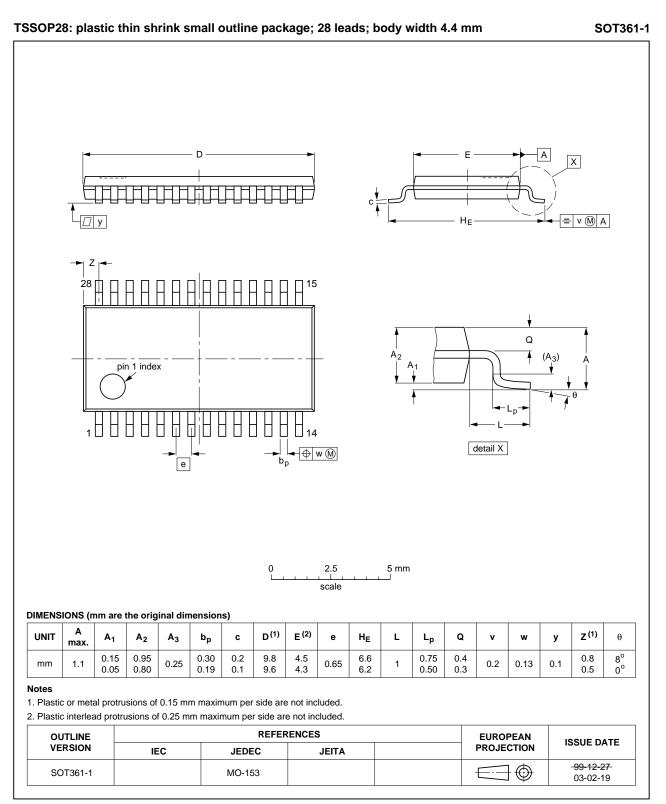

#### Fig 56. Package outline SOT361-1 (TSSOP28)

32-bit ARM Cortex-M0 microcontroller

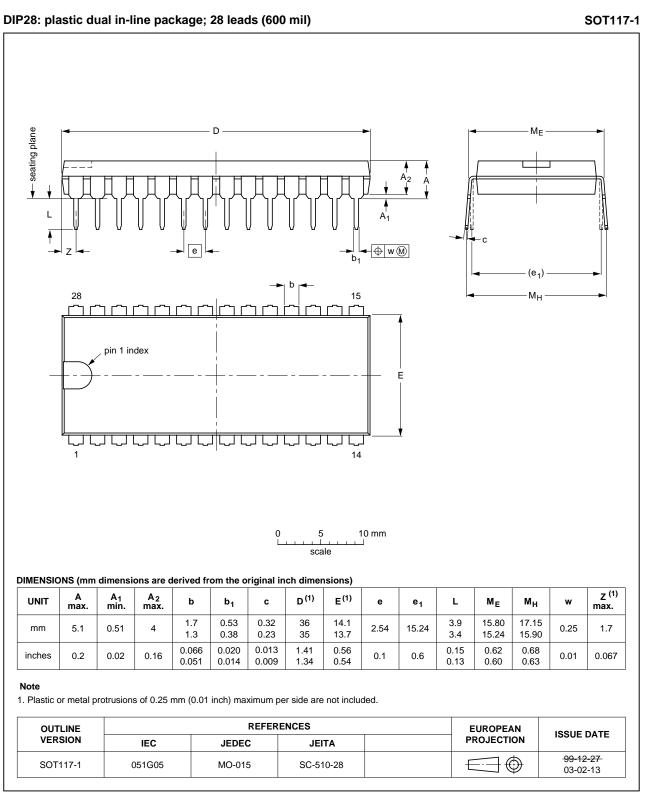

#### Fig 57. Package outline SOT117-1 (DIP28)

32-bit ARM Cortex-M0 microcontroller

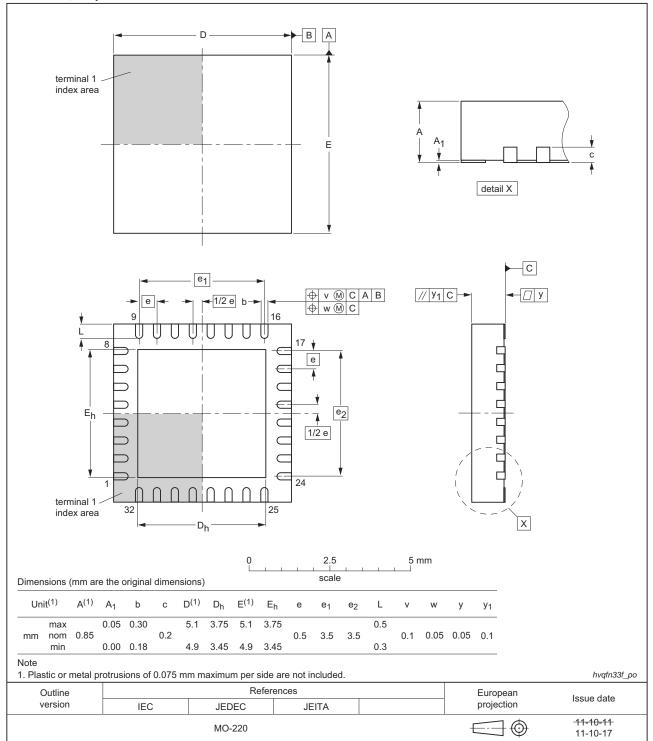

HVQFN33: plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; body 5 x 5 x 0.85 mm

Fig 58. Package outline (HVQFN33 5x5)

All information provided in this document is subject to legal disclaimers.

32-bit ARM Cortex-M0 microcontroller

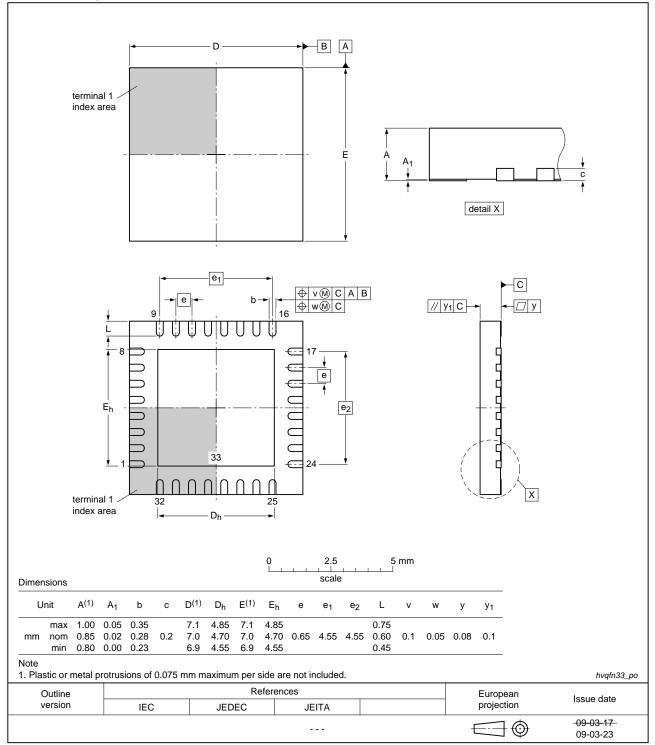

HVQFN33: plastic thermal enhanced very thin quad flat package; no leads; 33 terminals; body 7 x 7 x 0.85 mm

Fig 59. Package outline (HVQFN33 7x7)

All information provided in this document is subject to legal disclaimers

32-bit ARM Cortex-M0 microcontroller

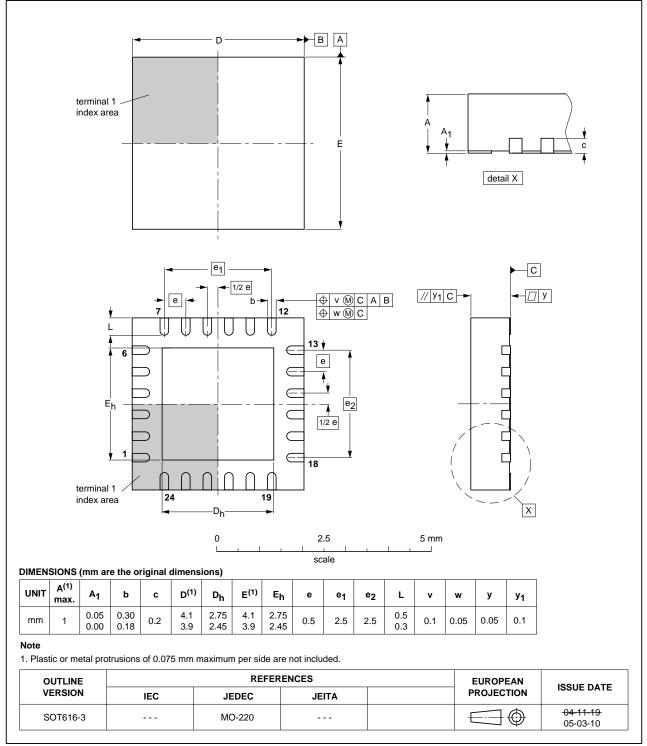

### HVQFN24: plastic thermal enhanced very thin quad flat package; no leads; 24 terminals; body 4 x 4 x 0.85 mm

SOT616-3

Fig 61. Package outline SOT616-3 (HVQFN24)