# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 50MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 28                                                                         |

| Program Memory Size        | 56KB (56K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 32-HVQFN (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1114fhn33-333-5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 32-bit ARM Cortex-M0 microcontroller

- LPC1100L series available as TSSOP28 package, DIP28 package, TSSOP20 package, and SO20 package.

- Extended temperature (-40 °C to +105 °C) for selected parts (see <u>Table 2</u>).

### 3. Applications

- eMetering

- Alarm systems

- Lighting

- White goods

### 4. Ordering information

| Type number        | Package      |                                                                                                                       |          |

|--------------------|--------------|-----------------------------------------------------------------------------------------------------------------------|----------|

|                    | Name         | Description                                                                                                           | Version  |

| SO20, TSSOP20, TSS | OP28, and DI | P28 packages                                                                                                          |          |

| LPC1110FD20        | SO20         | SO20: plastic small outline package; 20 leads; body width 7.5 mm                                                      | SOT163-1 |

| LPC1111FDH20/002   | TSSOP20      | TSSOP20: plastic thin shrink small outline package; 20 leads; body width 4.4 mm                                       | SOT360-1 |

| LPC1112FD20/102    | SO20         | SO20: plastic small outline package; 20 leads; body width 7.5 mm                                                      | SOT163-1 |

| LPC1112FDH20/102   | TSSOP20      | TSSOP20: plastic thin shrink small outline package; 20 leads; body width 4.4 mm                                       | SOT360-1 |

| LPC1112FDH28/102   | TSSOP28      | TSSOP28: plastic thin shrink small outline package; 28 leads; body width 4.4 mm                                       | SOT361-1 |

| LPC1114FDH28/102   | TSSOP28      | TSSOP28: plastic thin shrink small outline package; 28 leads; body width 4.4 mm                                       | SOT361-1 |

| LPC1114FN28/102    | DIP28        | DIP28: plastic dual in-line package; 28 leads (600 mil)                                                               | SOT117-1 |

| HVQFN24/33, LQFP48 | , and TFBGA  | 48 packages                                                                                                           |          |

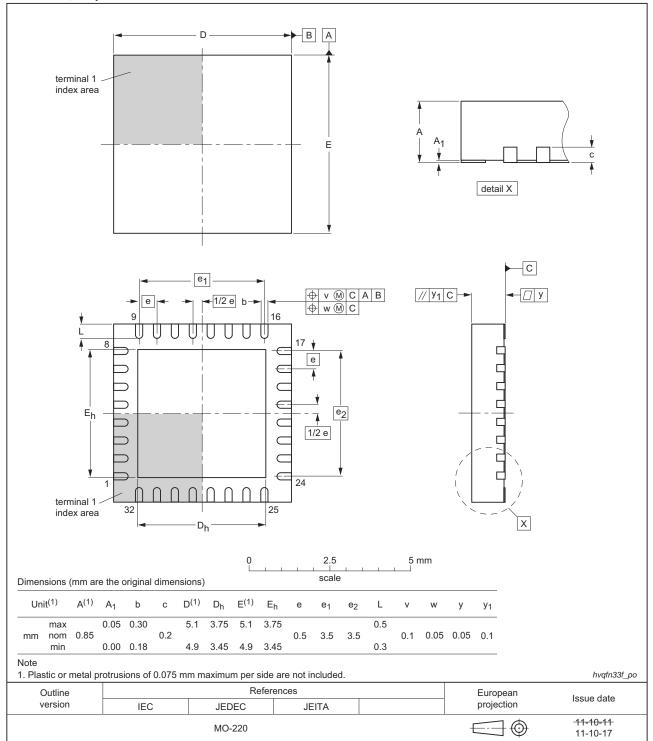

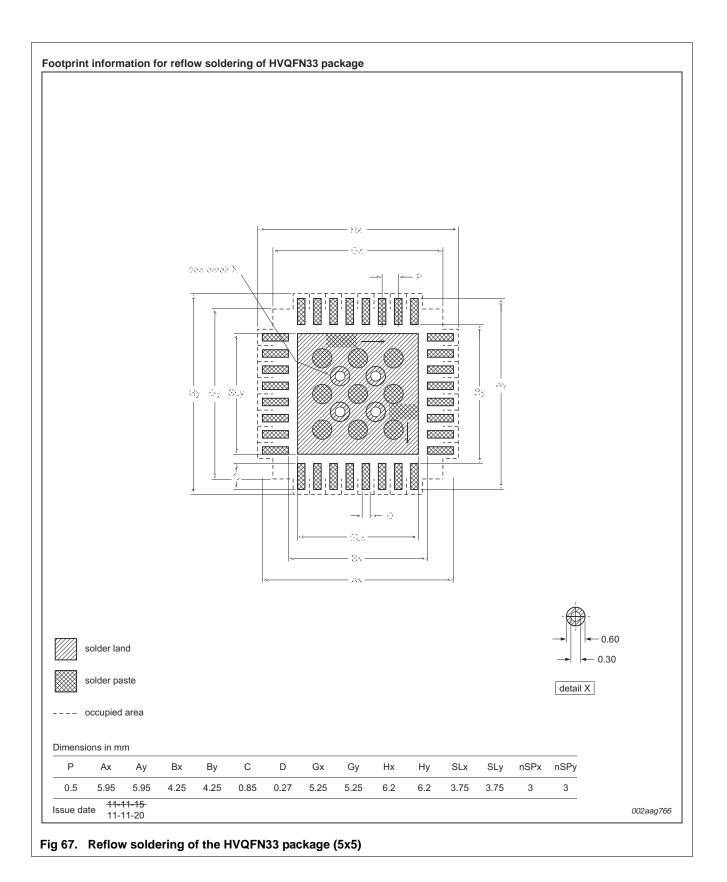

| LPC1111FHN33/101   | HVQFN33      | HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 33 terminals; body $7 \times 7 \times 0.85$ mm | n/a      |

| LPC1111FHN33/102   | HVQFN33      | HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 33 terminals; body $7 \times 7 \times 0.85$ mm | n/a      |

| LPC1111FHN33/201   | HVQFN33      | HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 33 terminals; body $7 \times 7 \times 0.85$ mm | n/a      |

| LPC1111FHN33/202   | HVQFN33      | HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 33 terminals; body $7 \times 7 \times 0.85$ mm | n/a      |

| LPC1111FHN33/103   | HVQFN33      | HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 33 terminals; body $7 \times 7 \times 0.85$ mm | n/a      |

| LPC1111JHN33/103   | HVQFN33      | HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 33 terminals; body $7 \times 7 \times 0.85$ mm | n/a      |

| LPC1111FHN33/203   | HVQFN33      | HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 33 terminals; body $7 \times 7 \times 0.85$ mm | n/a      |

| LPC1111JHN33/203   | HVQFN33      | HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 33 terminals; body $7 \times 7 \times 0.85$ mm | n/a      |

| LPC1112FHN33/101   | HVQFN33      | HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 33 terminals; body $7 \times 7 \times 0.85$ mm | n/a      |

| LPC1112FHN33/102   | HVQFN33      | HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 33 terminals; body $7 \times 7 \times 0.85$ mm | n/a      |

Product data sheet

© NXP Semiconductors N.V. 2014. All rights reserved.

#### **NXP Semiconductors**

### LPC1110/11/12/13/14/15

32-bit ARM Cortex-M0 microcontroller

### **NXP Semiconductors**

### LPC1110/11/12/13/14/15

32-bit ARM Cortex-M0 microcontroller

All information provided in this document is subject to legal disclaimers

#### 32-bit ARM Cortex-M0 microcontroller

#### LPC1100L series: LPC1110/11/12 pin description table (SO20 and TSSOP20 package with Table 4. I<sup>2</sup>C-bus pins) ... continued

| I <sup>2</sup> C-bus p        |                      | contin     |                         |      |                       |                                                                                                                                                                                                              |

|-------------------------------|----------------------|------------|-------------------------|------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                        | Pin SO20/<br>TSSOP20 |            | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | Description                                                                                                                                                                                                  |

| R/PIO0_11/<br>AD0/CT32B0_MAT3 | 4                    | <u>[5]</u> | yes                     | I    | I; PU                 | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                              |

|                               |                      |            |                         | I/O  | -                     | PIO0_11 — General purpose digital input/output pin.                                                                                                                                                          |

|                               |                      |            |                         | I    | -                     | AD0 — A/D converter, input 0.                                                                                                                                                                                |

|                               |                      |            |                         | 0    | -                     | CT32B0_MAT3 — Match output 3 for 32-bit timer 0.                                                                                                                                                             |

| PIO1_0 to PIO1_7              |                      |            |                         | I/O  |                       | <b>Port 1</b> — Port 1 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 1 pins depends on the function selected through the IOCONFIG register block. |

| R/PIO1_0/<br>AD1/CT32B1_CAP0  | 7                    | [5]        | yes                     | I    | I; PU                 | <ul> <li>R — Reserved. Configure for an alternate function in the IOCONFIG block.</li> </ul>                                                                                                                 |

|                               |                      |            |                         | I/O  | -                     | PIO1_0 — General purpose digital input/output pin.                                                                                                                                                           |

|                               |                      |            |                         | I    | -                     | AD1 — A/D converter, input 1.                                                                                                                                                                                |

|                               |                      |            |                         | I    | -                     | CT32B1_CAP0 — Capture input 0 for 32-bit timer 1.                                                                                                                                                            |

| R/PIO1_1/<br>AD2/CT32B1_MAT0  | 8                    | [5]        | no                      | 0    | I; PU                 | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                              |

|                               |                      |            |                         | I/O  | -                     | PIO1_1 — General purpose digital input/output pin.                                                                                                                                                           |

|                               |                      |            |                         | I    | -                     | AD2 — A/D converter, input 2.                                                                                                                                                                                |

|                               |                      |            |                         | 0    | -                     | CT32B1_MAT0 — Match output 0 for 32-bit timer 1.                                                                                                                                                             |

| R/PIO1_2/<br>AD3/CT32B1_MAT1  | 9                    | [5]        | no                      | I    | I; PU                 | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                              |

|                               |                      |            |                         | I/O  | -                     | PIO1_2 — General purpose digital input/output pin.                                                                                                                                                           |

|                               |                      |            |                         | I    | -                     | AD3 — A/D converter, input 3.                                                                                                                                                                                |

|                               |                      |            |                         | 0    | -                     | CT32B1_MAT1 — Match output 1 for 32-bit timer 1.                                                                                                                                                             |

| SWDIO/PIO1_3/                 | 10                   | [5]        | no                      | I/O  | I; PU                 | SWDIO — Serial wire debug input/output.                                                                                                                                                                      |

| AD4/CT32B1_MAT2               |                      |            |                         | I/O  | -                     | PIO1_3 — General purpose digital input/output pin.                                                                                                                                                           |

|                               |                      |            |                         | I    | -                     | AD4 — A/D converter, input 4.                                                                                                                                                                                |

|                               |                      |            |                         | 0    | -                     | CT32B1_MAT2 — Match output 2 for 32-bit timer 1.                                                                                                                                                             |

| PIO1_6/RXD/                   | 11                   | [3]        | no                      | I/O  | I; PU                 | PIO1_6 — General purpose digital input/output pin.                                                                                                                                                           |

| CT32B0_MAT0                   |                      |            |                         | I    | -                     | RXD — Receiver input for UART.                                                                                                                                                                               |

|                               |                      |            |                         | 0    | -                     | CT32B0_MAT0 — Match output 0 for 32-bit timer 0.                                                                                                                                                             |

| PIO1_7/TXD/                   | 12                   | [3]        | no                      | I/O  | I; PU                 | PIO1_7 — General purpose digital input/output pin.                                                                                                                                                           |

| CT32B0_MAT1                   |                      |            |                         | 0    | -                     | TXD — Transmitter output for UART.                                                                                                                                                                           |

|                               |                      |            |                         | 0    | -                     | CT32B0_MAT1 — Match output 1 for 32-bit timer 0.                                                                                                                                                             |

| V <sub>DD</sub>               | 15                   |            | -                       |      | -                     | 3.3 V supply voltage to the internal regulator, the external rail, and the ADC. Also used as the ADC reference voltage.                                                                                      |

| XTALIN                        | 14                   | [6]        | -                       | I    | -                     | Input to the oscillator circuit and internal clock generator circuits.<br>Input voltage must not exceed 1.8 V.                                                                                               |

| XTALOUT                       | 13                   | [6]        | -                       | 0    | -                     | Output from the oscillator amplifier.                                                                                                                                                                        |

| V <sub>SS</sub>               | 16                   |            | -                       |      | -                     | Ground.                                                                                                                                                                                                      |

LPC111X Product data sheet

#### 32-bit ARM Cortex-M0 microcontroller

- [1] Pin state at reset for default function: I = Input; O = Output; PU = internal pull-up enabled (pins pulled up to full V<sub>DD</sub> level ); IA = inactive, no pull-up/down enabled.

- [2] 5 V tolerant pad. RESET functionality is not available in Deep power-down mode.

- [3] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors and configurable hysteresis (see Figure 51).

- [4] I<sup>2</sup>C-bus pin compliant with the I<sup>2</sup>C-bus specification for I<sup>2</sup>C standard mode and I<sup>2</sup>C Fast-mode Plus. The pin requires an external pull-up to provide output functionality. When power is switched off, this pin is floating and does not disturb the I2C lines. Open-drain configuration applies to all functions on this pin.

- [5] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors, configurable hysteresis, and analog input. When configured as a ADC input, digital section of the pad is disabled and the pin is not 5 V tolerant (see Figure 51).

- [6] When the system oscillator is not used, connect XTALIN and XTALOUT as follows: XTALIN can be left floating or can be grounded (grounding is preferred to reduce susceptibility to noise). XTALOUT should be left floating.

Table 5. LPC1100L series: LPC1112 pin description table (TSSOP20 with V<sub>DDA</sub> and V<sub>SSA</sub> pins)

| Symbol                        | Pin TSSOP20 |     | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------|-------------|-----|-------------------------|------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO0_0 to PIO0_11             |             |     |                         | I/O  |                       | <b>Port 0</b> — Port 0 is a 12-bit I/O port with individual direction<br>and function controls for each bit. The operation of port 0 pins<br>depends on the function selected through the IOCONFIG<br>register block.                                                                                                                                                                                                                                                 |

| RESET/PIO0_0                  | 17          | [2] | yes                     | 1    | I; PU                 | <b>RESET</b> — External reset input with 20 ns glitch filter. A LOW-going pulse as short as 50 ns on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. In deep power-down mode, this pin must be pulled HIGH externally. The RESET pin can be left unconnected or be used as a GPIO pin if an external RESET function is not needed and Deep power-down mode is not used. |

|                               |             |     |                         | I/O  | -                     | <b>PIO0_0</b> — General purpose digital input/output pin with 10 ns glitch filter.                                                                                                                                                                                                                                                                                                                                                                                    |

| PIO0_1/CLKOUT/<br>CT32B0_MAT2 | 18          | [3] | yes                     | I/O  | I; PU                 | <b>PIO0_1</b> — General purpose digital input/output pin. A LOW level on this pin during reset starts the ISP command handler.                                                                                                                                                                                                                                                                                                                                        |

|                               |             |     |                         | 0    | -                     | CLKOUT — Clockout pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                               |             |     |                         | 0    | -                     | CT32B0_MAT2 — Match output 2 for 32-bit timer 0.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PIO0_2/SSEL0/                 | 19          | [3] | yes                     | I/O  | I; PU                 | PIO0_2 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CT16B0_CAP0                   |             |     |                         | I/O  | -                     | SSEL0 — Slave Select for SPI0.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                               |             |     |                         | I    | -                     | CT16B0_CAP0 — Capture input 0 for 16-bit timer 0.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PIO0_3                        | 20          | [3] | yes                     | I/O  | I; PU                 | PIO0_3 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PIO0_8/MISO0/                 | 1           | [3] | yes                     | I/O  | I; PU                 | PIO0_8 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CT16B0_MAT0                   |             |     |                         | I/O  | -                     | MISO0 — Master In Slave Out for SPI0.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                               |             |     |                         | 0    | -                     | CT16B0_MAT0 — Match output 0 for 16-bit timer 0.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PIO0_9/MOSI0/                 | 2           | [3] | yes                     | I/O  | I; PU                 | PIO0_9 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CT16B0_MAT1                   |             |     |                         | I/O  | -                     | MOSI0 — Master Out Slave In for SPI0.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                               |             |     |                         | 0    | -                     | CT16B0_MAT1 — Match output 1 for 16-bit timer 0.                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### 32-bit ARM Cortex-M0 microcontroller

| Symbol                                | Pin TSSOP28/<br>DIP28 |            | Start<br>logic<br>input | Туре | state<br>[1] | Description                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------|-----------------------|------------|-------------------------|------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SWCLK/PIO0_10/                        | 3                     | [3]        | yes                     | I    | I; PU        | SWCLK — Serial wire clock.                                                                                                                                                                                                                                                                                                                                               |

| SCK0/<br>CT16B0_MAT2                  |                       |            |                         | I/O  | -            | PIO0_10 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                      |

|                                       |                       |            |                         | I/O  | -            | SCK0 — Serial clock for SPI0.                                                                                                                                                                                                                                                                                                                                            |

|                                       |                       |            |                         | 0    | -            | CT16B0_MAT2 — Match output 2 for 16-bit timer 0.                                                                                                                                                                                                                                                                                                                         |

| R/PIO0_11/<br>AD0/CT32B0_MAT3         | 4                     | <u>[5]</u> | yes                     | I    | I; PU        | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                          |

|                                       |                       |            |                         | I/O  | -            | PIO0_11 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                      |

|                                       |                       |            |                         | I    | -            | AD0 — A/D converter, input 0.                                                                                                                                                                                                                                                                                                                                            |

|                                       |                       |            |                         | 0    | -            | CT32B0_MAT3 — Match output 3 for 32-bit timer 0.                                                                                                                                                                                                                                                                                                                         |

| PIO1_0 to PIO1_9                      |                       |            |                         | I/O  |              | <b>Port 1</b> — Port 1 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 1 pins depends on the function selected through the IOCONFIG register block.                                                                                                                                                             |

| R/PIO1_0/<br>AD1/CT32B1_CAP0          | 9                     | <u>[5]</u> | yes                     | I    | I; PU        | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                          |

|                                       |                       |            |                         | I/O  | -            | PIO1_0 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |

|                                       |                       |            |                         | I    | -            | AD1 — A/D converter, input 1.                                                                                                                                                                                                                                                                                                                                            |

|                                       |                       |            |                         | I    | -            | CT32B1_CAP0 — Capture input 0 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                        |

| R/PIO1_1/<br>AD2/CT32B1_MAT0          | 10                    | [5]        | no                      | 0    | I; PU        | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                          |

|                                       |                       |            |                         | I/O  | -            | PIO1_1 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |

|                                       |                       |            |                         | I    | -            | AD2 — A/D converter, input 2.                                                                                                                                                                                                                                                                                                                                            |

|                                       |                       |            |                         | 0    | -            | CT32B1_MAT0 — Match output 0 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |

| R/PIO1_2/<br>AD3/CT32B1_MAT1          | 11                    | [5]        | no                      | I    | I; PU        | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                          |

|                                       |                       |            |                         | I/O  | -            | PIO1_2 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |

|                                       |                       |            |                         | I    | -            | AD3 — A/D converter, input 3.                                                                                                                                                                                                                                                                                                                                            |

|                                       |                       |            |                         | 0    | -            | CT32B1_MAT1 — Match output 1 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |

| SWDIO/PIO1_3/                         | 12                    | [5]        | no                      | I/O  | I; PU        | SWDIO — Serial wire debug input/output.                                                                                                                                                                                                                                                                                                                                  |

| AD4/CT32B1_MAT2                       |                       |            |                         | I/O  | -            | PIO1_3 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |

|                                       |                       |            |                         | I    | -            | AD4 — A/D converter, input 4.                                                                                                                                                                                                                                                                                                                                            |

|                                       |                       |            |                         | 0    | -            | CT32B1_MAT2 — Match output 2 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |

| PIO1_4/AD5/<br>CT32B1_MAT3/<br>WAKEUP | 13                    | [5]        | no                      | I/O  | I; PU        | <b>PIO1_4</b> — General purpose digital input/output pin with 10 ns glitch filter. In Deep power-down mode, this pin serves as the Deep power-down mode wake-up pin with 20 ns glitch filter. Pull this pin HIGH externally before entering Deep power-down mode. Pull this pin LOW to exit Deep power-down mode. A LOW-going pulse as short as 50 ns wakes up the part. |

|                                       |                       |            |                         | 1    | -            | AD5 — A/D converter, input 5.                                                                                                                                                                                                                                                                                                                                            |

|                                       |                       |            |                         | 0    | -            | CT32B1_MAT3 — Match output 3 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |

#### Table 7. LPC1100L series: LPC1112/14 pin description table (TSSOP28 and DIP28 packages) ... continued

#### 32-bit ARM Cortex-M0 microcontroller

| Symbol                        | Pin                      | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | Description                                                                                                                                                                                                                                        |

|-------------------------------|--------------------------|-------------------------|------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO0_0 to PIO0_11             |                          |                         | I/O  |                       | <b>Port 0</b> — Port 0 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 0 pins depends on the function selected through the IOCONFIG register block.                                       |

| RESET/PIO0_0                  | 3 <u>[2]</u>             | yes                     | 1    | I; PU                 | <b>RESET</b> — External reset input with 20 ns glitch filter. A LOW-going pulse as short as 50 ns on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. |

|                               |                          |                         |      |                       | In deep power-down mode, this pin must be pulled HIGH externally. The RESET pin can be left unconnected or be used as a GPIO pin if an external RESET function is not needed and Deep power-down mode is not used.                                 |

|                               |                          |                         | I/O  | -                     | <b>PIO0_0</b> — General purpose digital input/output pin with 10 ns glitch filter.                                                                                                                                                                 |

| PIO0_1/CLKOUT/<br>CT32B0_MAT2 | 4 <u>[3]</u>             | yes                     | I/O  | I; PU                 | <b>PIO0_1</b> — General purpose digital input/output pin. A LOW level on this pin during reset starts the ISP command handler.                                                                                                                     |

|                               |                          |                         | 0    | -                     | CLKOUT — Clockout pin.                                                                                                                                                                                                                             |

|                               |                          |                         | 0    | -                     | CT32B0_MAT2 — Match output 2 for 32-bit timer 0.                                                                                                                                                                                                   |

| PIO0_2/SSEL0/<br>CT16B0_CAP0  | 10 <u>[3]</u>            | yes                     | I/O  | I; PU                 | PIO0_2 — General purpose digital input/output pin.                                                                                                                                                                                                 |

|                               |                          |                         | I/O  | -                     | SSEL0 — Slave Select for SPI0.                                                                                                                                                                                                                     |

|                               |                          |                         | I    | -                     | CT16B0_CAP0 — Capture input 0 for 16-bit timer 0.                                                                                                                                                                                                  |

| PIO0_3                        | 14 <u>[3]</u>            | yes                     | I/O  | I; PU                 | PIO0_3 — General purpose digital input/output pin.                                                                                                                                                                                                 |

| PIO0_4/SCL                    | 15 <u><sup>[4]</sup></u> | yes                     | I/O  | I; IA                 | <b>PIO0_4</b> — General purpose digital input/output pin (open-drain).                                                                                                                                                                             |

|                               |                          |                         | I/O  | -                     | <b>SCL</b> — I <sup>2</sup> C-bus, open-drain clock input/output. High-current sink only if I <sup>2</sup> C Fast-mode Plus is selected in the I/O configuration register.                                                                         |

| PIO0_5/SDA                    | 16 <u><sup>[4]</sup></u> | yes                     | I/O  | I; IA                 | <b>PIO0_5</b> — General purpose digital input/output pin (open-drain).                                                                                                                                                                             |

|                               |                          |                         | I/O  | -                     | <b>SDA</b> — I <sup>2</sup> C-bus, open-drain data input/output. High-current sink only if I <sup>2</sup> C Fast-mode Plus is selected in the I/O configuration register.                                                                          |

| PIO0_6/SCK0                   | 22 <u>[3]</u>            | yes                     | I/O  | I; PU                 | PIO0_6 — General purpose digital input/output pin.                                                                                                                                                                                                 |

|                               |                          |                         | I/O  | -                     | SCK0 — Serial clock for SPI0.                                                                                                                                                                                                                      |

| PIO0_7/CTS                    | 23 <u>[3]</u>            | yes                     | I/O  | I; PU                 | <b>PIO0_7</b> — General purpose digital input/output pin (high-current output driver).                                                                                                                                                             |

|                               |                          |                         | I    | -                     | CTS — Clear To Send input for UART.                                                                                                                                                                                                                |

| PIO0_8/MISO0/                 | 27 <u>[3]</u>            | yes                     | I/O  | I; PU                 | PIO0_8 — General purpose digital input/output pin.                                                                                                                                                                                                 |

| CT16B0_MAT0                   |                          |                         | I/O  | -                     | MISO0 — Master In Slave Out for SPI0.                                                                                                                                                                                                              |

|                               |                          |                         | 0    | -                     | CT16B0_MAT0 — Match output 0 for 16-bit timer 0.                                                                                                                                                                                                   |

| PIO0_9/MOSI0/                 | 28 <u>[3]</u>            | yes                     | I/O  | I; PU                 | PIO0_9 — General purpose digital input/output pin.                                                                                                                                                                                                 |

| CT16B0_MAT1                   |                          |                         | I/O  | -                     | MOSI0 — Master Out Slave In for SPI0.                                                                                                                                                                                                              |

|                               |                          |                         | 0    | -                     | CT16B0_MAT1 — Match output 1 for 16-bit timer 0.                                                                                                                                                                                                   |

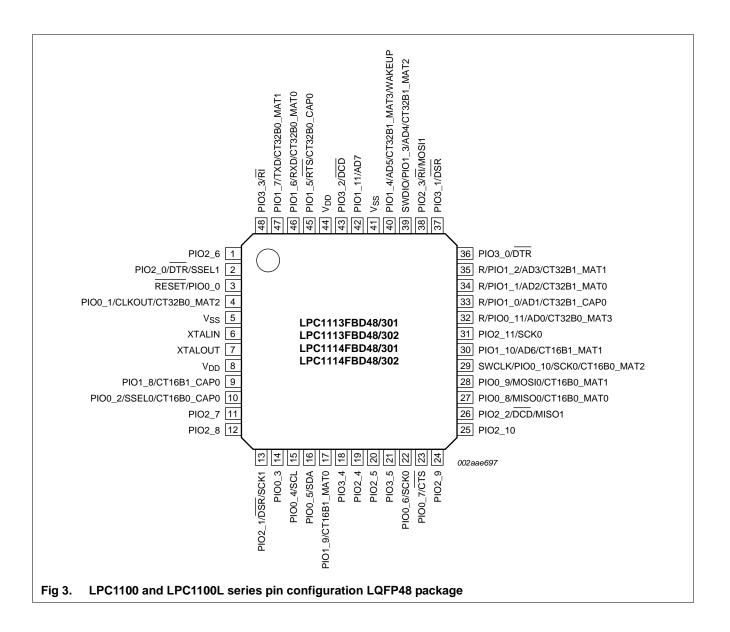

#### Table 8. LPC1100 and LPC1100L series: LPC1113/14 pin description table (LQFP48 package)

#### 32-bit ARM Cortex-M0 microcontroller

- Optional conversion on transition of input pin or timer match signal.

- Individual result registers for each ADC channel to reduce interrupt overhead.

### 7.12 General purpose external event counter/timers

The LPC1110/11/12/13/14/15 include two 32-bit counter/timers and two 16-bit counter/timers. The counter/timer is designed to count cycles of the system derived clock. It can optionally generate interrupts or perform other actions at specified timer values, based on four match registers. Each counter/timer also includes up to two capture inputs to trap the timer value when an input signal transitions, optionally generating an interrupt.

#### 7.12.1 Features

- A 32-bit/16-bit timer/counter with a programmable 32-bit/16-bit prescaler.

- Counter or timer operation.

- Up to two capture channels per timer, that can take a snapshot of the timer value when an input signal transitions. A capture event may also generate an interrupt.

- The timer and prescaler may be configured to be cleared on a designated capture event. This feature permits easy pulse width measurement by clearing the timer on the leading edge of an input pulse and capturing the timer value on the trailing edge.

- Four match registers per timer that allow:

- Continuous operation with optional interrupt generation on match.

- Stop timer on match with optional interrupt generation.

- Reset timer on match with optional interrupt generation.

- Up to four external outputs corresponding to match registers, with the following capabilities:

- Set LOW on match.

- Set HIGH on match.

- Toggle on match.

- Do nothing on match.

#### 7.13 System tick timer

The ARM Cortex-M0 includes a system tick timer (SYSTICK) that is intended to generate a dedicated SYSTICK exception at a fixed time interval (typically 10 ms).

### 7.14 Watchdog timer (LPC1100 series, LPC111x/101/201/301)

**Remark:** The watchdog timer without windowed features is available on parts LPC111x/101/201/301.

The purpose of the watchdog is to reset the microcontroller within a selectable time period.

#### 7.14.1 Features

- Internally resets chip if not periodically reloaded.

- Debug mode.

32-bit ARM Cortex-M0 microcontroller

The system oscillator operates at frequencies of 1 MHz to 25 MHz. This frequency can be boosted to a higher frequency, up to the maximum CPU operating frequency, by the system PLL.

#### 7.16.1.3 Watchdog oscillator

The watchdog oscillator can be used as a clock source that directly drives the CPU, the watchdog timer, or the CLKOUT pin. The watchdog oscillator nominal frequency is programmable between 9.4 kHz and 2.3 MHz. The frequency spread over processing and temperature is  $\pm$ 40 %.

#### 7.16.2 System PLL

The PLL accepts an input clock frequency in the range of 10 MHz to 25 MHz. The input frequency is multiplied up to a high frequency with a Current Controlled Oscillator (CCO). The multiplier can be an integer value from 1 to 32. The CCO operates in the range of 156 MHz to 320 MHz, so there is an additional divider in the loop to keep the CCO within its frequency range while the PLL is providing the desired output frequency. The PLL output frequency must be lower than 100 MHz. The output divider may be set to divide by 2, 4, 8, or 16 to produce the output clock. Since the minimum output divider value is 2, it is insured that the PLL output has a 50 % duty cycle. The PLL is turned off and bypassed following a chip reset and may be enabled by software. The program must configure and activate the PLL, wait for the PLL to lock, and then connect to the PLL as a clock source. The PLL settling time is 100  $\mu$ s.

#### 7.16.3 Clock output

The LPC1110/11/12/13/14/15 features a clock output function that routes the IRC oscillator, the system oscillator, the watchdog oscillator, or the main clock to an output pin.

#### 7.16.4 Wake-up process

The LPC1110/11/12/13/14/15 begin operation at power-up and when awakened from Deep power-down mode by using the 12 MHz IRC oscillator as the clock source. This allows chip operation to resume quickly. If the system oscillator or the PLL is needed by the application, software will need to enable these features and wait for them to stabilize before they are used as a clock source.

#### 7.16.5 Power control

The LPC1110/11/12/13/14/15 support a variety of power control features. There are three special modes of processor power reduction: Sleep mode, Deep-sleep mode, and Deep power-down mode. The CPU clock rate may also be controlled as needed by changing clock sources, reconfiguring PLL values, and/or altering the CPU clock divider value. This allows a trade-off of power versus processing speed based on application requirements. In addition, a register is provided for shutting down the clocks to individual on-chip peripherals, allowing fine tuning of power consumption by eliminating all dynamic power use in any peripherals that are not required for the application. Selected peripherals have their own clock divider which provides even better power control.

#### 7.16.5.1 Power profiles (LPC1100L and LPC1100XL series only)

The power consumption in Active and Sleep modes can be optimized for the application through simple calls to the power profile. The power configuration routine configures the LPC1110/11/12/13/14/15 for one of the following power modes:

32-bit ARM Cortex-M0 microcontroller

### 8. Limiting values

#### Table 12. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).[1]

| Symbol                 | Parameter                               | Conditions                                                                                     | Min  | Max   | Unit |

|------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------|------|-------|------|

| V <sub>DD</sub>        | supply voltage (core and external rail) | [2]                                                                                            | -0.5 | +4.6  | V    |

| VI                     | input voltage                           |                                                                                                | -0.5 | +5.5  | V    |

|                        |                                         | 5 V tolerant [2][4]<br>open-drain pins<br>PIO0_4 and<br>PIO0_5                                 | -0.5 | +5.5  | V    |

| V <sub>IA</sub>        | analog input voltage                    | pin configured as [2][5]<br>analog input                                                       | -0.5 | 4.6   | V    |

| I <sub>DD</sub>        | supply current                          | per supply pin                                                                                 | -    | 100   | mA   |

| I <sub>SS</sub>        | ground current                          | per ground pin                                                                                 | -    | 100   | mA   |

| I <sub>latch</sub>     | I/O latch-up current                    | -(0.5V <sub>DD</sub> ) < V <sub>I</sub> <<br>(1.5V <sub>DD</sub> );<br>T <sub>i</sub> < 125 °C | -    | 100   | mA   |

| T <sub>stg</sub>       | storage temperature                     | non-operating [6]                                                                              | -65  | +150  | °C   |

| T <sub>j(max)</sub>    | maximum junction temperature            |                                                                                                | -    | 150   | °C   |

| P <sub>tot(pack)</sub> | total power dissipation (per package)   | based on package<br>heat transfer, not<br>device power<br>consumption                          | -    | 1.5   | W    |

| V <sub>ESD</sub>       | electrostatic discharge voltage         | human body [7]<br>model; all pins                                                              | -    | +6500 | V    |

[1] The following applies to the limiting values:

a) This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maximum.

b) Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted.

c) The limiting values are stress ratings only. Operating the part at these values is not recommended, and proper operation is not guaranteed. The conditions for functional operation are specified in <u>Table 16</u>.

[2] Maximum/minimum voltage above the maximum operating voltage (see <u>Table 16</u>) and below ground that can be applied for a short time (< 10 ms) to a device without leading to irrecoverable failure. Failure includes the loss of reliability and shorter lifetime of the device.

[3] Including voltage on outputs in 3-state mode.

[4]  $V_{DD}$  present or not present. Compliant with the I<sup>2</sup>C-bus standard. 5.5 V can be applied to this pin when  $V_{DD}$  is powered down.

[5] See <u>Table 18</u> for maximum operating voltage.

- [6] The maximum non-operating storage temperature is different than the temperature for required shelf life which should be determined based on required shelf lifetime. Please refer to the JEDEC spec (J-STD-033B.1) for further details.

- [7] Human body model: equivalent to discharging a 100 pF capacitor through a 1.5 k $\Omega$  series resistor.

32-bit ARM Cortex-M0 microcontroller

#### Table 16. Static characteristics (LPC1100, LPC1100L series) ... continued

$T_{amb} = -40 \ ^{\circ}C$  to +85  $^{\circ}C$ , unless otherwise specified.

| Symbol                              | Parameter                                 | Conditions                                                                                                                                                                                              | Min                | Typ <u>[1]</u>      | Max                | Unit |

|-------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------|--------------------|------|

| I <sub>OZ</sub>                     | OFF-state output<br>current               | $V_O = 0 V; V_O = V_{DD};$<br>on-chip pull-up/down<br>resistors disabled                                                                                                                                | -                  | 0.5                 | 10                 | nA   |

| VI                                  | input voltage                             | pin configured to provide [12][13]<br>a digital function [14]                                                                                                                                           | 0                  | -                   | 5.0                | V    |

| Vo                                  | output voltage                            | output active                                                                                                                                                                                           | 0                  | -                   | V <sub>DD</sub>    | V    |

| V <sub>IH</sub>                     | HIGH-level input<br>voltage               |                                                                                                                                                                                                         | 0.7V <sub>DD</sub> | -                   | -                  | V    |

| V <sub>IL</sub>                     | LOW-level input voltage                   |                                                                                                                                                                                                         | -                  | -                   | $0.3V_{DD}$        | V    |

| V <sub>hys</sub>                    | hysteresis voltage                        |                                                                                                                                                                                                         | 0.4                | -                   | -                  | V    |

| V <sub>OH</sub>                     | HIGH-level output voltage                 | $\begin{array}{l} 2.5 \ V \leq V_{DD} \leq 3.6 \ V; \\ I_{OH} = -20 \ mA \end{array} \label{eq:VDD}$                                                                                                    | $V_{DD}-0.4$       | -                   | -                  | V    |

|                                     |                                           | $\begin{array}{l} 1.8 \ V \leq V_{DD} < 2.5 \ V; \\ I_{OH} = -12 \ mA \end{array} \label{eq:VDD}$                                                                                                       | $V_{DD} - 0.4$     | -                   | -                  | V    |

| V <sub>OL</sub>                     | LOW-level output voltage                  | $\begin{array}{l} 2.5 \ V \leq V_{DD} \leq 3.6 \ V; \\ I_{OL} = 4 \ mA \end{array} \label{eq:VDD}$                                                                                                      | -                  | -                   | 0.4                | V    |

|                                     |                                           | $\begin{array}{l} 1.8 \ V \leq V_{DD} < 2.5 \ V; \\ I_{OL} = 3 \ mA \end{array} \label{eq:VDD}$                                                                                                         | -                  | -                   | 0.4                | V    |

| ••••                                | HIGH-level output<br>current              | $V_{OH} = V_{DD} - 0.4 V;$<br>2.5 V $\leq V_{DD} \leq 3.6 V$                                                                                                                                            | 20                 | -                   | -                  | mA   |

|                                     |                                           | $1.8 \text{ V} \leq \text{V}_{\text{DD}} < 2.5 \text{ V}$                                                                                                                                               | 12                 | -                   | -                  | mA   |

| I <sub>OL</sub> LOW-leve<br>current | LOW-level output<br>current               | $V_{OL} = 0.4 \text{ V}$ $2.5 \text{ V} \leq V_{DD} \leq 3.6 \text{ V}$                                                                                                                                 | 4                  | -                   | -                  | mA   |

|                                     |                                           | $1.8 \text{ V} \leq \text{V}_{\text{DD}}$ < $2.5 \text{ V}$                                                                                                                                             | 3                  | -                   | -                  | mA   |

| I <sub>OLS</sub>                    | LOW-level short-circuit<br>output current | $V_{OL} = V_{DD} $ [15]                                                                                                                                                                                 | -                  | -                   | 50                 | mA   |

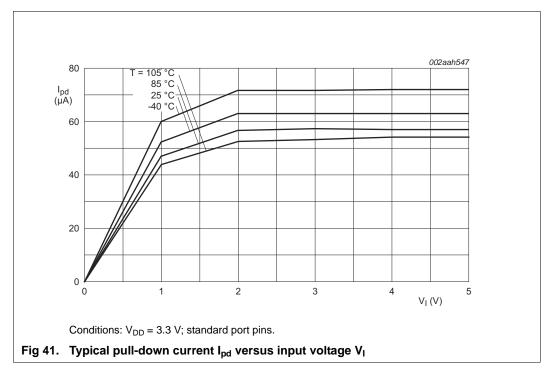

| I <sub>pd</sub>                     | pull-down current                         | V <sub>1</sub> = 5 V                                                                                                                                                                                    | 10                 | 50                  | 150                | μA   |

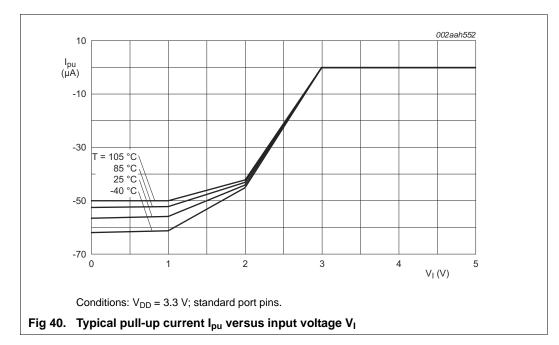

| I <sub>pu</sub>                     | pull-up current                           | $V_{I} = 0 V$ $2.0 V \le V_{DD} \le 3.6 V$                                                                                                                                                              | -15                | -50                 | -85                | μΑ   |

|                                     |                                           | $1.8 \text{ V} \le \text{V}_{\text{DD}}$ < 2.0 V                                                                                                                                                        | -10                | -50                 | -85                | μA   |

|                                     |                                           | V <sub>DD</sub> < V <sub>I</sub> < 5 V                                                                                                                                                                  | 0                  | 0                   | 0                  | μA   |

| I <sup>2</sup> C-bus pins           | s (PIO0_4 and PIO0_5)                     | L                                                                                                                                                                                                       | 1                  |                     |                    |      |

| V <sub>IH</sub>                     | HIGH-level input voltage                  |                                                                                                                                                                                                         | 0.7V <sub>DD</sub> | -                   | -                  | V    |

| V <sub>IL</sub>                     | LOW-level input voltage                   |                                                                                                                                                                                                         | -                  | -                   | 0.3V <sub>DD</sub> | V    |

| V <sub>hys</sub>                    | hysteresis voltage                        |                                                                                                                                                                                                         | -                  | 0.05V <sub>DD</sub> | -                  | V    |

| I <sub>OL</sub>                     | LOW-level output<br>current               | $\label{eq:Volume} \begin{array}{l} V_{OL} = 0.4 \ \text{V; } l^2 C\text{-bus pins} \\ \text{configured as standard} \\ \text{mode pins} \\ 2.5 \ \text{V} \leq V_{DD} \leq 3.6 \ \text{V} \end{array}$ | 3.5                | -                   | -                  | mA   |

|                                     |                                           | $1.8 \text{ V} \le \text{V}_{\text{DD}}$ < 2.5 V                                                                                                                                                        | 3                  | -                   | -                  |      |

32-bit ARM Cortex-M0 microcontroller

### 10.2 LPC1100XL series

#### Table 17. Static characteristics (LPC1100XL series)

$T_{amb} = -40 \text{ °C to } +105 \text{ °C}$ , unless otherwise specified.

| Symbol          | Parameter                               | Conditions                                              |                 | Min                | Typ <u>[1]</u>         | Max             | Unit |

|-----------------|-----------------------------------------|---------------------------------------------------------|-----------------|--------------------|------------------------|-----------------|------|

| V <sub>DD</sub> | supply voltage (core and external rail) |                                                         |                 | 1.8                | 3.3                    | 3.6             | V    |

| LPC1100XL s     | series (LPC111x/103/203/30              | 3/323/333) power consum                                 | ption in        | low-curre          | nt mode <sup>[2]</sup> |                 |      |

| I <sub>DD</sub> | supply current                          | Active mode; code                                       |                 |                    |                        |                 |      |

|                 |                                         | while(1){}                                              |                 |                    |                        |                 |      |

|                 |                                         | executed from flash                                     |                 |                    |                        |                 |      |

|                 |                                         | system clock = 3 MHz                                    | [3][4][5]       | -                  | 600                    | -               | μA   |

|                 |                                         | V <sub>DD</sub> = 3.3 V                                 | [6][7]          |                    |                        |                 |      |

|                 |                                         | system clock = 6 MHz                                    | [3][4][5]       | -                  | 850                    | -               | μA   |

|                 |                                         | V <sub>DD</sub> = 3.3 V                                 | [6][7]          |                    |                        |                 |      |

|                 |                                         | system clock = 12 MHz                                   | [3][4][6]       | -                  | 1.4                    | -               | mA   |

|                 |                                         | V <sub>DD</sub> = 3.3 V                                 | [7][8]          |                    |                        |                 |      |

|                 |                                         | system clock = 50 MHz                                   | [3][4][6]       | -                  | 5.8                    | -               | mA   |

|                 |                                         | V <sub>DD</sub> = 3.3 V                                 | [7][9]          |                    |                        |                 |      |