Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 50MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 42                                                                         |

| Program Memory Size        | 56KB (56K × 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-LQFP                                                                    |

| Supplier Device Package    | 48-LQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1114jbd48-333ql |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

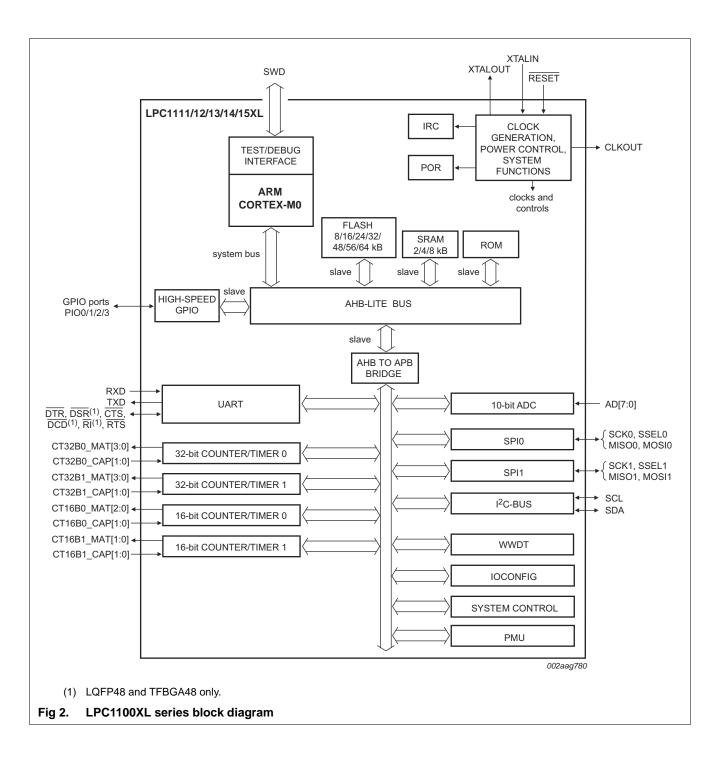

### 32-bit ARM Cortex-M0 microcontroller

- Digital peripherals:

- Up to 42 General Purpose I/O (GPIO) pins with configurable pull-up/pull-down resistors. In addition, a configurable open-drain mode is supported on the LPC1100L and LPC1100XL series.

- ♦ GPIO pins can be used as edge and level sensitive interrupt sources.

- ◆ High-current output driver (20 mA) on one pin.

- ♦ High-current sink drivers (20 mA) on two l<sup>2</sup>C-bus pins in Fast-mode Plus (not on LPC1112FDH20/102).

- Four general purpose counter/timers with up to eight capture inputs and up to 13 match outputs.

- ◆ Programmable WatchDog Timer (WDT) the LPC1100 series only.

- Programmable windowed WDT on the LPC1100L and LPC1100XL series only.

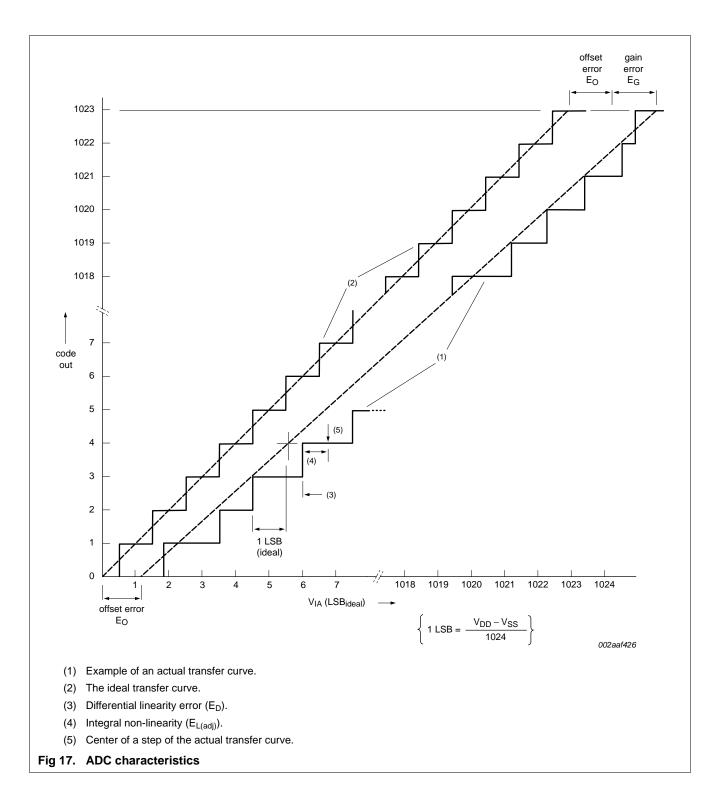

- Analog peripherals:

- ♦ 10-bit ADC with input multiplexing among 5, 6, or 8 pins depending on package size.

- Serial interfaces:

- ◆ UART with fractional baud rate generation, internal FIFO, and RS-485 support.

- Two SPI controllers with SSP features and with FIFO and multi-protocol capabilities (second SPI on LPC1100 and LPC1100L series LQFP48 package only).

- ♦ I<sup>2</sup>C-bus interface supporting full I<sup>2</sup>C-bus specification and Fast-mode Plus with a data rate of 1 Mbit/s with multiple address recognition and monitor mode (not on LPC1112FDH20/102).

- Clock generation:

- 12 MHz internal RC oscillator trimmed to 1 % accuracy that can optionally be used as a system clock.

- Crystal oscillator with an operating range of 1 MHz to 25 MHz.

- ◆ Programmable watchdog oscillator with a frequency range of 9.4 kHz to 2.3 MHz.

- PLL allows CPU operation up to the maximum CPU rate without the need for a high-frequency crystal. May be run from the system oscillator or the internal RC oscillator.

- Clock output function with divider that can reflect the system oscillator clock, IRC clock, CPU clock, and the Watchdog clock.

- Power control:

- Integrated PMU (Power Management Unit) to minimize power consumption during Sleep, Deep-sleep, and Deep power-down modes.

- Power profiles residing in boot ROM allowing to optimize performance and minimize power consumption for any given application through one simple function call. (LPC1100L and LPC1100XL series only.)

- ◆ Three reduced power modes: Sleep, Deep-sleep, and Deep power-down.

- Processor wake-up from Deep-sleep mode via a dedicated start logic using up to 13 of the functional pins.

- Power-On Reset (POR).

- Brownout detect with up to four separate thresholds for interrupt and forced reset.

- Unique device serial number for identification.

- Single power supply (1.8 V to 3.6 V).

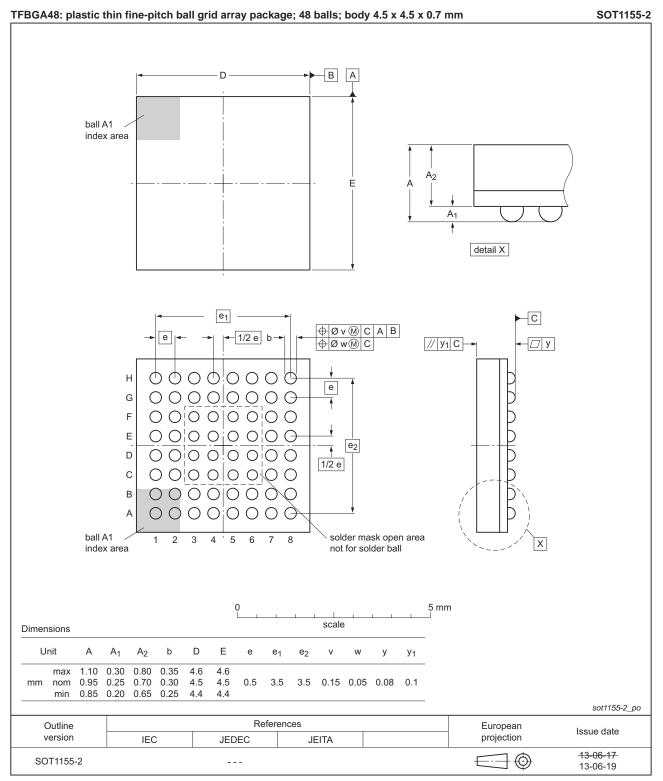

- Available as LQFP48 package, HVQFN33 package, and TFBGA48 package.

LPC111X

© NXP Semiconductors N.V. 2014. All rights reserved.

32-bit ARM Cortex-M0 microcontroller

| Type number      | Series    |       |      | Power<br>profiles | UART | I <sup>2</sup> C/<br>Fast+ |   | ADC<br>channel | GPIO | Package | Temp <u><sup>[1]</sup></u> |

|------------------|-----------|-------|------|-------------------|------|----------------------------|---|----------------|------|---------|----------------------------|

| LPC1115JBD48/303 | LPC1100XL | 64 kB | 8 kB | yes               | 1    | 1                          | 2 | 8              | 42   | LQFP48  | J                          |

| LPC1115FET48/303 | LPC1100XL | 64 kB | 8 kB | yes               | 1    | 1                          | 2 | 8              | 42   | TFBGA48 | F                          |

| LPC1115JET48/303 | LPC1100XL | 64 kB | 8 kB | yes               | 1    | 1                          | 2 | 8              | 42   | TFBGA48 | J                          |

#### Table 2. Ordering options ...continued

[1]  $F = -40 \degree C$  to +85  $\degree C$ ,  $J = -40 \degree C$  to +105  $\degree C$ .

### **NXP Semiconductors**

## LPC1110/11/12/13/14/15

32-bit ARM Cortex-M0 microcontroller

### 32-bit ARM Cortex-M0 microcontroller

| Table 8. LPC110                       | 0 and LPC                     | :1100L se               | eries: LPO     | C1113/14              | pin description table (LQFP48 package) continued                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------|-------------------------------|-------------------------|----------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                                | Pin                           | Start<br>logic<br>input | Туре           | Reset<br>state<br>[1] | Description                                                                                                                                                                                                                                                                                                                                                              |

| SWCLK/PIO0_10/                        | 29 <u>[3]</u>                 | yes                     | I              | I; PU                 | SWCLK — Serial wire clock.                                                                                                                                                                                                                                                                                                                                               |

| SCK0/<br>CT16B0_MAT2                  |                               |                         | I/O            | -                     | PIO0_10 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                      |

| CTIODU_IVIATZ                         |                               |                         | I/O            | -                     | SCK0 — Serial clock for SPI0.                                                                                                                                                                                                                                                                                                                                            |

|                                       |                               |                         | 0              | -                     | CT16B0_MAT2 — Match output 2 for 16-bit timer 0.                                                                                                                                                                                                                                                                                                                         |

| R/PIO0_11/<br>AD0/CT32B0_MAT          | 32 <u>[5]</u><br>3            | yes                     | I              | I; PU                 | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                          |

|                                       |                               |                         | I/O            | -                     | PIO0_11 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                      |

|                                       |                               |                         | I              | -                     | AD0 — A/D converter, input 0.                                                                                                                                                                                                                                                                                                                                            |

|                                       |                               |                         | 0              | -                     | CT32B0_MAT3 — Match output 3 for 32-bit timer 0.                                                                                                                                                                                                                                                                                                                         |

| PIO1_0 to PIO1_11                     |                               |                         | I/O            |                       | <b>Port 1</b> — Port 1 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 1 pins depends on the function selected through the IOCONFIG register block.                                                                                                                                                             |

| R/PIO1_0/<br>AD1/CT32B1_CAP           | 33 <u>[5]</u><br>0            | yes                     | 1              | I; PU                 | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                          |

|                                       |                               |                         | I/O            | -                     | PIO1_0 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |

|                                       |                               |                         | 1              | -                     | AD1 — A/D converter, input 1.                                                                                                                                                                                                                                                                                                                                            |

|                                       |                               |                         | I              | -                     | CT32B1_CAP0 — Capture input 0 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                        |

| R/PIO1_1/<br>AD2/CT32B1_MAT0          | 34 <u><sup>[5]</sup></u><br>0 | no                      | 0              | I; PU                 | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                          |

|                                       |                               |                         | I/O            | -                     | PIO1_1 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |

|                                       |                               |                         | I              | -                     | AD2 — A/D converter, input 2.                                                                                                                                                                                                                                                                                                                                            |

|                                       |                               |                         | 0              | -                     | CT32B1_MAT0 — Match output 0 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |

| R/PIO1_2/<br>AD3/CT32B1_MAT           | 35 <u><sup>[5]</sup></u><br>1 | no                      | 1              | I; PU                 | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                          |

|                                       |                               |                         | I/O            | -                     | PIO1_2 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |

|                                       |                               |                         | I              | -                     | AD3 — A/D converter, input 3.                                                                                                                                                                                                                                                                                                                                            |

|                                       |                               |                         | 0              | -                     | CT32B1_MAT1 — Match output 1 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |

| SWDIO/PIO1_3/                         | 39 <u>[5]</u>                 | no                      | I/O            | I; PU                 | SWDIO — Serial wire debug input/output.                                                                                                                                                                                                                                                                                                                                  |

| AD4/CT32B1_MAT                        | 2                             |                         | I/O            | -                     | PIO1_3 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |

|                                       |                               |                         | I              | -                     | AD4 — A/D converter, input 4.                                                                                                                                                                                                                                                                                                                                            |

|                                       |                               |                         | 0              | -                     | CT32B1_MAT2 — Match output 2 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |

| PIO1_4/AD5/<br>CT32B1_MAT3/<br>WAKEUP | 40 <u>[5]</u>                 | no                      | I/O            | I; PU                 | <b>PIO1_4</b> — General purpose digital input/output pin with 10 ns glitch filter. In Deep power-down mode, this pin serves as the Deep power-down mode wake-up pin with 20 ns glitch filter. Pull this pin HIGH externally before entering Deep power-down mode. Pull this pin LOW to exit Deep power-down mode. A LOW-going pulse as short as 50 ns wakes up the part. |

|                                       |                               |                         | I              | -                     | AD5 — A/D converter, input 5.                                                                                                                                                                                                                                                                                                                                            |

|                                       |                               |                         | 0              | -                     | CT32B1_MAT3 — Match output 3 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |

| PIO1_5/RTS/                           | 45 <u>[3]</u>                 | no                      | I/O            | I; PU                 | PIO1_5 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |

| CT32B0_CAP0                           |                               |                         | 0              | -                     | RTS — Request To Send output for UART.                                                                                                                                                                                                                                                                                                                                   |

|                                       |                               |                         | I              | -                     | CT32B0_CAP0 — Capture input 0 for 32-bit timer 0.                                                                                                                                                                                                                                                                                                                        |

| LPC111X                               |                               |                         | All informatio | n provided in this    | s document is subject to legal disclaimers. © NXP Semiconductors N.V. 2014. All rights reserved                                                                                                                                                                                                                                                                          |

#### Table 8. LPC1100 and LPC1100L series: LPC1113/14 pin description table (LQFP48 package) ... continued

Product data sheet

### 32-bit ARM Cortex-M0 microcontroller

| Symbol                                | Pin                      | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | Description                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|---------------------------------------|--------------------------|-------------------------|------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| R/PIO0_11/AD0/<br>CT32B0_MAT3         | 21 <u>5</u>              | yes                     | -    | I;PU                  | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                          |  |  |  |

|                                       |                          |                         | I/O  | -                     | PIO0_11 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                       |                          |                         | I    | -                     | AD0 — A/D converter, input 0.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                       |                          |                         | 0    | -                     | CT32B0_MAT3 — Match output 3 for 32-bit timer 0.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| PIO1_0 to PIO1_11                     |                          |                         |      |                       | <b>Port 1</b> — Port 1 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 1 pins depends on the function selected through the IOCONFIG register block.                                                                                                                                                             |  |  |  |

| R/PIO1_0/AD1/<br>CT32B1_CAP0          | 22 <u><sup>[5]</sup></u> | yes                     | -    | I;PU                  | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                          |  |  |  |

|                                       |                          |                         | I/O  | -                     | PIO1_0 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                       |                          |                         | I    | -                     | AD1 — A/D converter, input 1.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                       |                          |                         | I    | -                     | CT32B1_CAP0 — Capture input 0 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                        |  |  |  |

| R/PIO1_1/AD2/<br>CT32B1_MAT0          | 23 <u>[5]</u>            | no                      | -    | I;PU                  | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                          |  |  |  |

|                                       |                          |                         | I/O  | -                     | PIO1_1 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                       |                          |                         | I    | -                     | AD2 — A/D converter, input 2.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                       |                          |                         | 0    | -                     | CT32B1_MAT0 — Match output 0 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| R/PIO1_2/AD3/<br>CT32B1_MAT1          | 24 <u><sup>[5]</sup></u> | no                      | -    | I;PU                  | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                                                                                                                          |  |  |  |

|                                       |                          |                         | I/O  | -                     | PIO1_2 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                       |                          |                         | I    | -                     | AD3 — A/D converter, input 3.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                       |                          |                         | 0    | -                     | CT32B1_MAT1 — Match output 1 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| SWDIO/PIO1_3/                         | 25 <u>[5]</u>            | no                      | I/O  | I;PU                  | SWDIO — Serial wire debug input/output.                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| AD4/CT32B1_MAT2                       |                          |                         | I/O  | -                     | PIO1_3 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                       |                          |                         | I    | -                     | AD4 — A/D converter, input 4.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                       |                          |                         | 0    | -                     | CT32B1_MAT2 — Match output 2 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| PIO1_4/AD5/<br>CT32B1_MAT3/<br>WAKEUP | 26 <sup>[5]</sup>        | no l                    | I/O  | I;PU                  | <b>PIO1_4</b> — General purpose digital input/output pin with 10 ns glitch filter. In Deep power-down mode, this pin serves as the Deep power-down mode wake-up pin with 20 ns glitch filter. Pull this pin HIGH externally before entering Deep power-down mode. Pull this pin LOW to exit Deep power-down mode. A LOW-going pulse as short as 50 ns wakes up the part. |  |  |  |

|                                       |                          |                         | I    | -                     | AD5 — A/D converter, input 5.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                       |                          |                         | 0    | -                     | CT32B1_MAT3 — Match output 3 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| PIO1_5/RTS/                           | 30 <u>[3]</u>            | no                      | I/O  | I;PU                  | PIO1_5 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |  |  |  |

| CT32B0_CAP0                           |                          |                         | 0    | -                     | RTS — Request To Send output for UART.                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                       |                          |                         | I    | -                     | CT32B0_CAP0 — Capture input 0 for 32-bit timer 0.                                                                                                                                                                                                                                                                                                                        |  |  |  |

| PIO1_6/RXD/                           | 31 <u>[3]</u>            | no                      | I/O  | I;PU                  | PIO1_6 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |  |  |  |

| CT32B0_MAT0                           |                          |                         | I    | -                     | RXD — Receiver input for UART.                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                                       |                          |                         | 0    | -                     | CT32B0_MAT0 — Match output 0 for 32-bit timer 0.                                                                                                                                                                                                                                                                                                                         |  |  |  |

#### Table 9. LPC1100 and LPC1100L series: LPC1111/12/13/14 pin description table (HVQFN33 package) ...continued

### 32-bit ARM Cortex-M0 microcontroller

| Symbol                        | Pin           | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | Description                                                                                                                                                                                                                                       |

|-------------------------------|---------------|-------------------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO0_0 to PIO0_11             |               |                         |      |                       | <b>Port 0</b> — Port 0 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 0 pins depends on the function selected through the IOCONFIG register block.                                      |

| RESET/PIO0_0                  | 2 <u>[2]</u>  | yes                     | I    | I;PU                  | <b>RESET</b> — External reset input with 20 ns glitch filter. A LOW-going pulse as short as 50 ns on this pin resets the device, causing I/O ports and peripherals to take on their default states and processor execution to begin at address 0. |

|                               |               |                         |      |                       | In deep power-down mode, this pin must be pulled HIGH externally.<br>The RESET pin can be left unconnected or be used as a GPIO pin if<br>an external RESET function is not needed and Deep power-down<br>mode is not used.                       |

|                               |               |                         | I/O  | -                     | <b>PIO0_0</b> — General purpose digital input/output pin with 10 ns glitch filter.                                                                                                                                                                |

| PIO0_1/CLKOUT/<br>CT32B0_MAT2 | 3 <u>[3]</u>  | yes                     | I/O  | I;PU                  | <b>PIO0_1</b> — General purpose digital input/output pin. A LOW level on this pin during reset starts the ISP command handler.                                                                                                                    |

|                               |               |                         | 0    | -                     | CLKOUT — Clock out pin.                                                                                                                                                                                                                           |

|                               |               |                         | 0    | -                     | CT32B0_MAT2 — Match output 2 for 32-bit timer 0.                                                                                                                                                                                                  |

| PIO0_2/SSEL0/                 | 8 <u>[3]</u>  | yes                     | I/O  | I;PU                  | PIO0_2 — General purpose digital input/output pin.                                                                                                                                                                                                |

| CT16B0_CAP0                   |               |                         | I/O  | -                     | SSEL0 — Slave select for SPI0.                                                                                                                                                                                                                    |

|                               |               |                         | I    | -                     | CT16B0_CAP0 — Capture input 0 for 16-bit timer 0.                                                                                                                                                                                                 |

| PIO0_3                        | 9 <u>[3]</u>  | yes                     | I/O  | I;PU                  | PIO0_3 — General purpose digital input/output pin.                                                                                                                                                                                                |

| PIO0_4/SCL                    | 10 <u>[4]</u> | l yes                   | I/O  | I;IA                  | PIO0_4 — General purpose digital input/output pin (open-drain).                                                                                                                                                                                   |

|                               |               |                         | I/O  | -                     | <b>SCL</b> — $I^2C$ -bus, open-drain clock input/output. High-current sink only if $I^2C$ Fast-mode Plus is selected in the I/O configuration register.                                                                                           |

| PIO0_5/SDA                    | 11 <u>[4]</u> | yes                     | I/O  | I;IA                  | PIO0_5 — General purpose digital input/output pin (open-drain).                                                                                                                                                                                   |

|                               |               |                         | I/O  | -                     | <b>SDA</b> — I <sup>2</sup> C-bus, open-drain data input/output. High-current sink only if I <sup>2</sup> C Fast-mode Plus is selected in the I/O configuration register.                                                                         |

| PIO0_6/SCK0                   | 15 <u>[3]</u> | yes                     | I/O  | I;PU                  | PIO0_6 — General purpose digital input/output pin.                                                                                                                                                                                                |

|                               |               |                         | I/O  | -                     | SCK0 — Serial clock for SPI0.                                                                                                                                                                                                                     |

| PIO0_7/CTS                    | 16 <u>[3]</u> | yes                     | I/O  | I;PU                  | <b>PIO0_7</b> — General purpose digital input/output pin (high-current output driver).                                                                                                                                                            |

|                               |               |                         | I    | -                     | CTS — Clear To Send input for UART.                                                                                                                                                                                                               |

| PIO0_8/MISO0/                 | 17 <u>[3]</u> | yes                     | I/O  | I;PU                  | PIO0_8 — General purpose digital input/output pin.                                                                                                                                                                                                |

| CT16B0_MAT0                   |               |                         | I/O  | -                     | MISO0 — Master In Slave Out for SPI0.                                                                                                                                                                                                             |

|                               |               |                         | 0    | -                     | CT16B0_MAT0 — Match output 0 for 16-bit timer 0.                                                                                                                                                                                                  |

| PIO0_9/MOSI0/                 | 18 <u>[3]</u> | yes                     | I/O  | I;PU                  | PIO0_9 — General purpose digital input/output pin.                                                                                                                                                                                                |

| CT16B0_MAT1                   |               |                         | I/O  | -                     | MOSI0 — Master Out Slave In for SPI0.                                                                                                                                                                                                             |

|                               |               |                         | 0    | -                     | CT16B0_MAT1 — Match output 1 for 16-bit timer 0.                                                                                                                                                                                                  |

| SWCLK/PIO0_10/                | 19 <u>[3]</u> | yes                     | I    | I;PU                  | SWCLK — Serial wire clock.                                                                                                                                                                                                                        |

| SCK0/                         |               | ,                       | I/O  | -                     | PIO0_10 — General purpose digital input/output pin.                                                                                                                                                                                               |

| CT16B0_MAT2                   |               |                         | I/O  | -                     | SCK0 — Serial clock for SPI0.                                                                                                                                                                                                                     |

|                               |               |                         | 0    | -                     | CT16B0_MAT2 — Match output 2 for 16-bit timer 0.                                                                                                                                                                                                  |

#### Table 11. LPC1100XL series: LPC1111/12/13/14 pin description table (HVQFN33 package)

#### 32-bit ARM Cortex-M0 microcontroller

- Enabled by software but requires a hardware reset or a watchdog reset/interrupt to be disabled.

- Incorrect/Incomplete feed sequence causes reset/interrupt if enabled.

- Flag to indicate watchdog reset.

- Programmable 24-bit timer with internal prescaler.

- Selectable time period from  $(T_{cy(WDCLK)} \times 256 \times 4)$  to  $(T_{cy(WDCLK)} \times 2^{24} \times 4)$  in multiples of  $T_{cy(WDCLK)} \times 4$ .

- The Watchdog Clock (WDCLK) source can be selected from the Internal RC oscillator (IRC), the Watchdog oscillator, or the main clock. This gives a wide range of potential timing choices of Watchdog operation under different power reduction conditions. It also provides the ability to run the WDT from an entirely internal source that is not dependent on an external crystal and its associated components and wiring for increased reliability.

### 7.15 Windowed WatchDog Timer (LPC1100L and LPC1100XL series)

**Remark:** The windowed watchdog timer is available on the LPC1100L and LPC1100XL series only.

The purpose of the watchdog is to reset the controller if software fails to periodically service it within a programmable time window.

### 7.15.1 Features

- Internally resets chip if not periodically reloaded during the programmable time-out period.

- Optional windowed operation requires reload to occur between a minimum and maximum time period, both programmable.

- Optional warning interrupt can be generated at a programmable time prior to watchdog time-out.

- Enabled by software but requires a hardware reset or a watchdog reset/interrupt to be disabled.

- Incorrect feed sequence causes reset or interrupt if enabled.

- Flag to indicate watchdog reset.

- Programmable 24-bit timer with internal prescaler.

- Selectable time period from  $(T_{cy(WDCLK)} \times 256 \times 4)$  to  $(T_{cy(WDCLK)} \times 2^{24} \times 4)$  in multiples of  $T_{cy(WDCLK)} \times 4$ .

- The Watchdog Clock (WDCLK) source can be selected from the IRC or the dedicated watchdog oscillator (WDO). This gives a wide range of potential timing choices of watchdog operation under different power conditions.

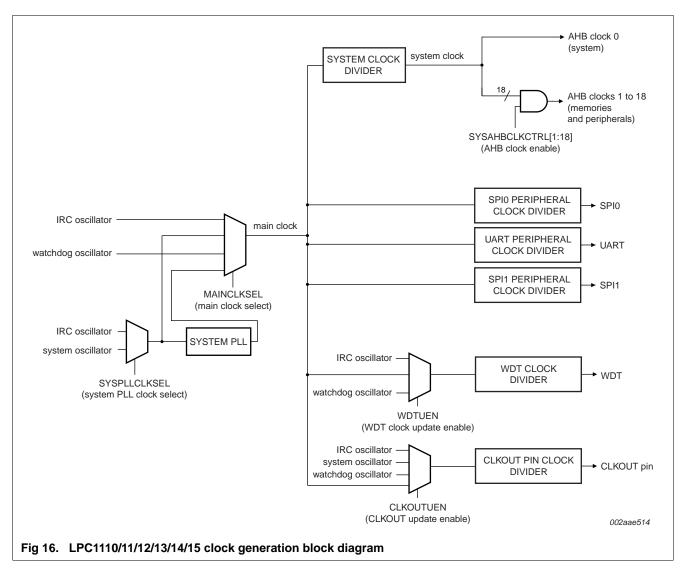

### 7.16 Clocking and power control

### 7.16.1 Crystal oscillators

The LPC1110/11/12/13/14/15 include three independent oscillators. These are the system oscillator, the Internal RC oscillator (IRC), and the Watchdog oscillator. Each oscillator can be used for more than one purpose as required in a particular application.

#### 32-bit ARM Cortex-M0 microcontroller

Following reset, the LPC1110/11/12/13/14/15 will operate from the Internal RC oscillator until switched by software. This allows systems to operate without any external crystal and the bootloader code to operate at a known frequency.

See Figure 16 for an overview of the LPC1110/11/12/13/14/15 clock generation.

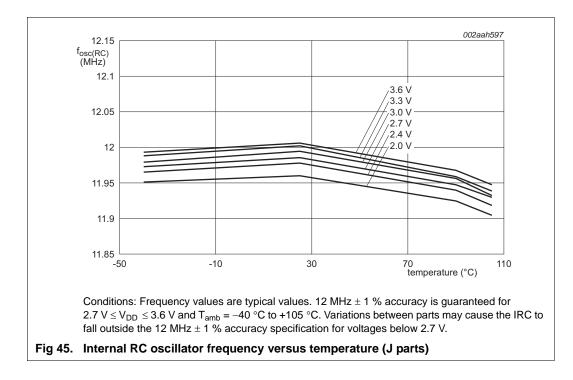

#### 7.16.1.1 Internal RC oscillator

The IRC may be used as the clock source for the WDT, and/or as the clock that drives the PLL and subsequently the CPU. The nominal IRC frequency is 12 MHz. The IRC is trimmed to 1 % accuracy over the entire voltage and temperature range.

Upon power-up or any chip reset, the LPC1110/11/12/13/14/15 use the IRC as the clock source. Software may later switch to one of the other available clock sources.

#### 7.16.1.2 System oscillator

The system oscillator can be used as the clock source for the CPU, with or without using the PLL.

#### 32-bit ARM Cortex-M0 microcontroller

- Default mode corresponding to power configuration after reset.

- CPU performance mode corresponding to optimized processing capability.

- Efficiency mode corresponding to optimized balance of current consumption and CPU performance.

- Low-current mode corresponding to lowest power consumption.

In addition, the power profile includes routines to select the optimal PLL settings for a given system clock and PLL input clock.

#### 7.16.5.2 Sleep mode

When Sleep mode is entered, the clock to the core is stopped. Resumption from the Sleep mode does not need any special sequence but re-enabling the clock to the ARM core.

In Sleep mode, execution of instructions is suspended until either a reset or interrupt occurs. Peripheral functions continue operation during Sleep mode and may generate interrupts to cause the processor to resume execution. Sleep mode eliminates dynamic power used by the processor itself, memory systems and related controllers, and internal buses.

#### 7.16.5.3 Deep-sleep mode

In Deep-sleep mode, the chip is in Sleep mode, and in addition all analog blocks are shut down. As an exception, the user has the option to keep the watchdog oscillator and the BOD circuit running for self-timed wake-up and BOD protection. Deep-sleep mode allows for additional power savings.

Up to 13 pins total serve as external wake-up pins to the start logic to wake up the chip from Deep-sleep mode.

Unless the watchdog oscillator is selected to run in Deep-sleep mode, the clock source should be switched to IRC before entering Deep-sleep mode, because the IRC can be switched on and off glitch-free.

#### 7.16.5.4 Deep power-down mode

In Deep power-down mode, power is shut off to the entire chip with the exception of the WAKEUP pin. The LPC1110/11/12/13/14/15 can wake up from Deep power-down mode via the WAKEUP pin.

A LOW-going pulse as short as 50 ns wakes up the part from Deep power-down mode.

When entering Deep power-down mode, an external pull-up resistor is required on the WAKEUP pin to hold it HIGH. The RESET pin must also be held HIGH to prevent it from floating while in Deep power-down mode.

### 7.17 System control

### 7.17.1 Start logic

The start logic connects external pins to corresponding interrupts in the NVIC. Each pin shown in <u>Table 8</u> to <u>Table 9</u> as input to the start logic has an individual interrupt in the NVIC interrupt vector table. The start logic pins can serve as external interrupt pins when the chip is running. In addition, an input signal on the start logic pins can wake up the chip from Deep-sleep mode when all clocks are shut down.

32-bit ARM Cortex-M0 microcontroller

| Symbol           | Parameter                                  | Conditions                                                                                                                                        | Min                | Typ[1] | Max                | Unit |

|------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|--------------------|------|

| V <sub>IL</sub>  | LOW-level input voltage                    |                                                                                                                                                   | -                  | -      | 0.3V <sub>DD</sub> | V    |

| V <sub>hys</sub> | hysteresis voltage                         |                                                                                                                                                   | -                  | 0.4    | -                  | V    |

| V <sub>OH</sub>  | HIGH-level output voltage                  | $\begin{array}{l} 2.5 \ V \leq V_{DD} \leq 3.6 \ V; \\ I_{OH} = -4 \ mA \end{array} \label{eq:VDD}$                                               | $V_{DD}-0.4$       | -      | -                  | V    |

|                  |                                            | $\begin{array}{l} 1.8 \ \text{V} \leq \text{V}_{\text{DD}} < 2.5 \ \text{V}; \\ \text{I}_{\text{OH}} = -3 \ \text{mA} \end{array}$                | $V_{DD}-0.4$       | -      | -                  | V    |

| V <sub>OL</sub>  | LOW-level output voltage                   | $\begin{array}{l} 2.5 \ \text{V} \leq \text{V}_{DD} \leq 3.6 \ \text{V}; \\ \text{I}_{OL} = 4 \ \text{mA} \end{array} \end{array} \label{eq:VDD}$ | -                  | -      | 0.4                | V    |

|                  |                                            | $1.8 \text{ V} \leq \text{V}_{\text{DD}} < 2.5 \text{ V}; \\ \text{I}_{\text{OL}} = 3 \text{ mA}$                                                 | -                  | -      | 0.4                | V    |

| I <sub>OH</sub>  | HIGH-level output current                  | $V_{OH} = V_{DD} - 0.4 V;$<br>2.5 V $\leq V_{DD} \leq 3.6 V$                                                                                      | -4                 | -      | -                  | mA   |

|                  |                                            | $1.8 \text{ V} \le \text{V}_{\text{DD}} < 2.5 \text{ V}$                                                                                          | -3                 | -      | -                  | mA   |

| I <sub>OL</sub>  | LOW-level output current                   | $V_{OL} = 0.4 V$<br>2.5 V $\leq V_{DD} \leq 3.6 V$                                                                                                | 4                  | -      | -                  | mA   |

|                  |                                            | $1.8 \text{ V} \le \text{V}_{\text{DD}} < 2.5 \text{ V}$                                                                                          | 3                  | -      | -                  | mA   |

| I <sub>OHS</sub> | HIGH-level short-circuit<br>output current | V <sub>OH</sub> = 0 V [16]                                                                                                                        | -                  | -      | -45                | mA   |

| I <sub>OLS</sub> | LOW-level short-circuit<br>output current  | $V_{OL} = V_{DD} $ [16]                                                                                                                           | -                  | -      | 50                 | mA   |

| I <sub>pd</sub>  | pull-down current                          | V <sub>1</sub> = 5 V                                                                                                                              | 10                 | 50     | 150                | μA   |

| I <sub>pu</sub>  | pull-up current                            | $V_{I} = 0 V;$<br>2.0 V $\leq V_{DD} \leq 3.6 V$                                                                                                  | -15                | -50    | -85                | μA   |

|                  |                                            | $1.8 \text{ V} \le \text{V}_{\text{DD}} < 2.0 \text{ V}$                                                                                          | -10                | -50    | -85                | μA   |

|                  |                                            | V <sub>DD</sub> < V <sub>I</sub> < 5 V                                                                                                            | 0                  | 0      | 0                  | μA   |

| High-drive o     | output pin (PIO0_7)                        |                                                                                                                                                   |                    |        |                    |      |

| IIL              | LOW-level input current                    | V <sub>I</sub> = 0 V; on-chip pull-up resistor disabled                                                                                           | -                  | 0.5    | 10                 | nA   |

| I <sub>IH</sub>  | HIGH-level input<br>current                | V <sub>I</sub> = V <sub>DD</sub> ; on-chip<br>pull-down resistor<br>disabled                                                                      | -                  | 0.5    | 10                 | nA   |

| I <sub>OZ</sub>  | OFF-state output<br>current                | V <sub>O</sub> = 0 V; V <sub>O</sub> = V <sub>DD</sub> ;<br>on-chip pull-up/down<br>resistors disabled                                            | -                  | 0.5    | 10                 | nA   |

| VI               | input voltage                              | pin configured to provide [13][14]<br>a digital function [15]                                                                                     | -                  | -      | 5.0                | V    |

| Vo               | output voltage                             | output active                                                                                                                                     | 0                  | -      | V <sub>DD</sub>    | V    |

| V <sub>IH</sub>  | HIGH-level input voltage                   |                                                                                                                                                   | 0.7V <sub>DD</sub> | -      | -                  | V    |

| V <sub>IL</sub>  | LOW-level input voltage                    |                                                                                                                                                   | -                  | -      | 0.3V <sub>DD</sub> | V    |

| V <sub>hys</sub> | hysteresis voltage                         |                                                                                                                                                   | 0.4                | -      | -                  | V    |

#### Table 17. Static characteristics (LPC1100XL series) ... continued $T_{amb} = -40 \ ^{\circ}C$ to +105 $^{\circ}C$ . unless otherwise specified.

### **NXP Semiconductors**

## LPC1110/11/12/13/14/15

32-bit ARM Cortex-M0 microcontroller

32-bit ARM Cortex-M0 microcontroller

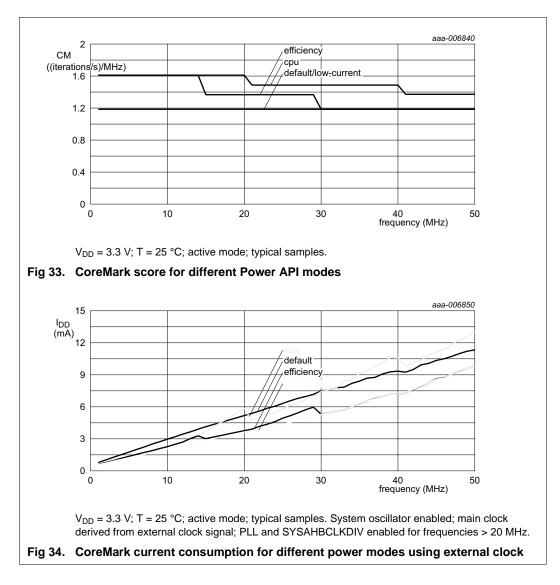

### 10.8 CoreMark data

Remark: All CoreMark data were taken with the Keil uVision v. 4.6 tool.

32-bit ARM Cortex-M0 microcontroller

32-bit ARM Cortex-M0 microcontroller

### 11.6 I<sup>2</sup>C-bus

### Table 28. Dynamic characteristic: I<sup>2</sup>C-bus pins<sup>[1]</sup>

$T_{amb} = -40 \ ^{\circ}C \ to +105 \ ^{\circ}C.$

| Symbol              | Parameter      |                          | Conditions                  | Min                   | Max | Unit |

|---------------------|----------------|--------------------------|-----------------------------|-----------------------|-----|------|

| f <sub>SCL</sub>    | SCL clock      |                          | Standard-mode               | 0                     | 100 | kHz  |

|                     | frequency      |                          | Fast-mode                   | 0                     | 400 | kHz  |

|                     |                |                          | Fast-mode Plus              | 0                     | 1   | MHz  |

| t <sub>f</sub>      | fall time      | [4][5][6][7]             | of both SDA and SCL signals | -                     | 300 | ns   |

|                     |                |                          | Standard-mode               |                       |     |      |

|                     |                |                          | Fast-mode                   | $20 + 0.1 \times C_b$ | 300 | ns   |

|                     |                |                          | Fast-mode Plus              | -                     | 120 | ns   |

| t <sub>LOW</sub>    | LOW period of  |                          | Standard-mode               | 4.7                   | -   | μS   |

|                     | the SCL clock  |                          | Fast-mode                   | 1.3                   | -   | μS   |

|                     |                |                          | Fast-mode Plus              | 0.5                   | -   | μS   |

| t <sub>HIGH</sub>   | HIGH period of |                          | Standard-mode               | 4.0                   | -   | μS   |

|                     | the SCL clock  |                          | Fast-mode                   | 0.6                   | -   | μS   |

|                     |                |                          | Fast-mode Plus              | 0.26                  | -   | μS   |

| t <sub>HD;DAT</sub> | data hold time | d time [ <u>3][4][8]</u> | Standard-mode               | 0                     | -   | μS   |

|                     |                |                          | Fast-mode                   | 0                     | -   | μS   |

|                     |                |                          | Fast-mode Plus              | 0                     | -   | μS   |

| t <sub>SU;DAT</sub> | data set-up    | <u>[9][10]</u>           | Standard-mode               | 250                   | -   | ns   |

|                     | time           |                          | Fast-mode                   | 100                   | -   | ns   |

|                     |                |                          | Fast-mode Plus              | 50                    | -   | ns   |

[1] See the I<sup>2</sup>C-bus specification UM10204 for details.

[2] Parameters are valid over operating temperature range unless otherwise specified.

- [3] t<sub>HD;DAT</sub> is the data hold time that is measured from the falling edge of SCL; applies to data in transmission and the acknowledge.

- [5]  $C_b$  = total capacitance of one bus line in pF.

- [6] The maximum t<sub>f</sub> for the SDA and SCL bus lines is specified at 300 ns. The maximum fall time for the SDA output stage t<sub>f</sub> is specified at 250 ns. This allows series protection resistors to be connected in between the SDA and the SCL pins and the SDA/SCL bus lines without exceeding the maximum specified t<sub>f</sub>.

- [7] In Fast-mode Plus, fall time is specified the same for both output stage and bus timing. If series resistors are used, designers should allow for this when considering bus timing.

- [8] The maximum  $t_{HD;DAT}$  could be 3.45  $\mu$ s and 0.9  $\mu$ s for Standard-mode and Fast-mode but must be less than the maximum of  $t_{VD;DAT}$  or  $t_{VD;ACK}$  by a transition time (see *UM10204*). This maximum must only be met if the device does not stretch the LOW period ( $t_{LOW}$ ) of the SCL signal. If the clock stretches the SCL, the data must be valid by the set-up time before it releases the clock.

- [9] t<sub>SU;DAT</sub> is the data set-up time that is measured with respect to the rising edge of SCL; applies to data in transmission and the acknowledge.

- [10] A Fast-mode I<sup>2</sup>C-bus device can be used in a Standard-mode I<sup>2</sup>C-bus system but the requirement  $t_{SU;DAT} = 250$  ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line  $t_{r(max)} + t_{SU;DAT} = 1000 + 250 = 1250$  ns (according to the Standard-mode I<sup>2</sup>C-bus specification) before the SCL line is released. Also the acknowledge timing must meet this set-up time.

32-bit ARM Cortex-M0 microcontroller

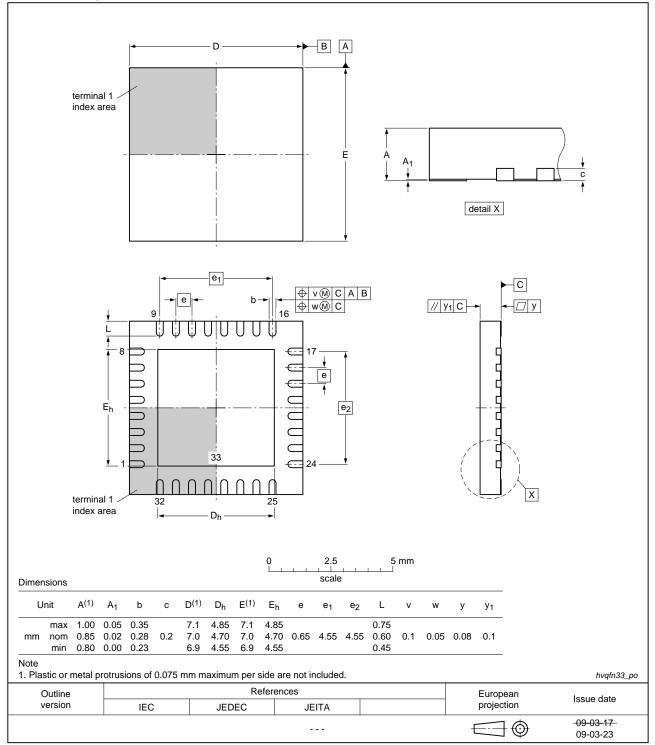

HVQFN33: plastic thermal enhanced very thin quad flat package; no leads; 33 terminals; body 7 x 7 x 0.85 mm

Fig 59. Package outline (HVQFN33 7x7)

All information provided in this document is subject to legal disclaimers

32-bit ARM Cortex-M0 microcontroller

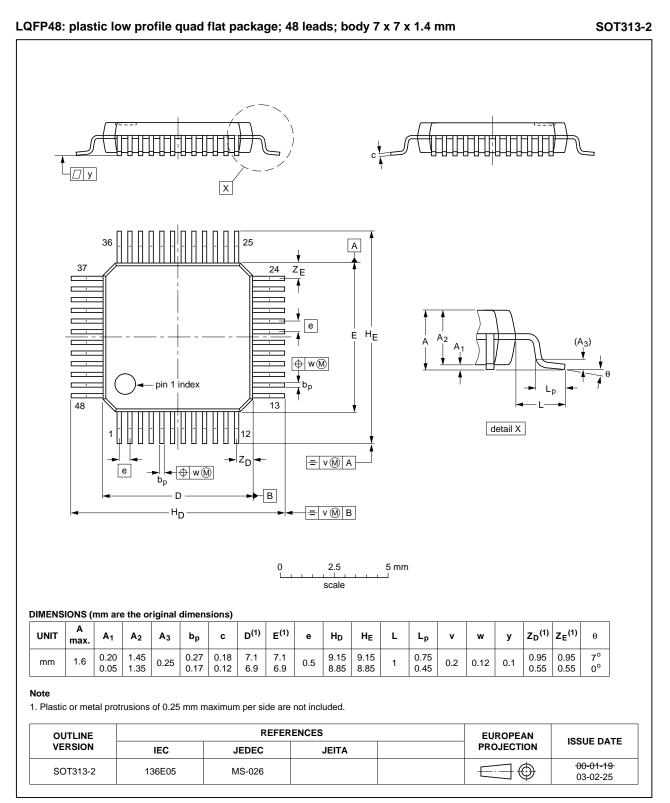

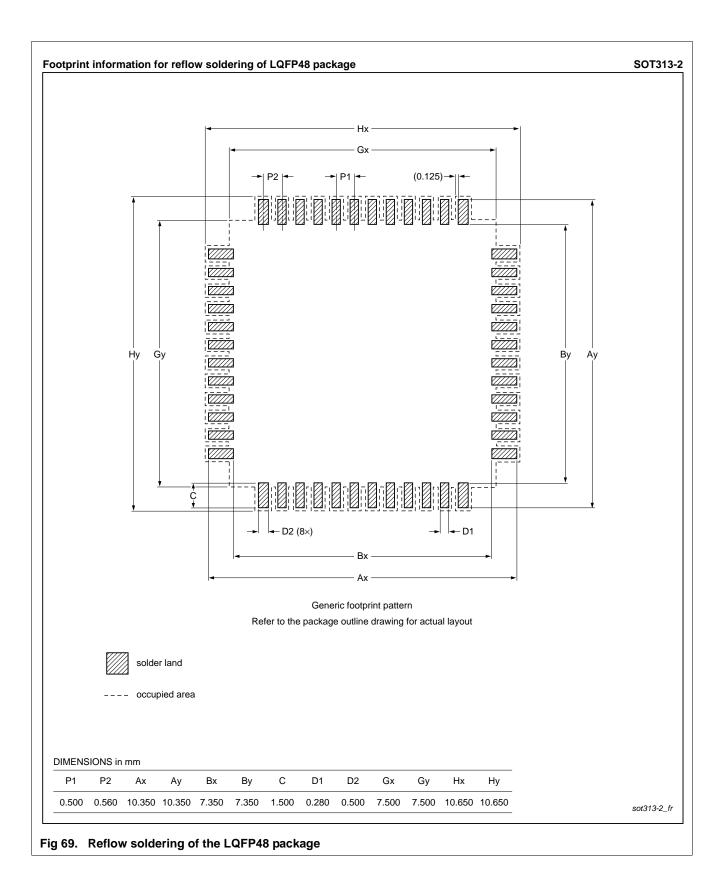

#### Fig 60. Package outline SOT313-2 (LQFP48)

LPC111X Product data sheet © NXP Semiconductors N.V. 2014. All rights reserved.

32-bit ARM Cortex-M0 microcontroller

Fig 62. Package outline TFBGA48 (SOT1155-2)

All information provided in this document is subject to legal disclaimers.

32-bit ARM Cortex-M0 microcontroller

32-bit ARM Cortex-M0 microcontroller

### 15. Abbreviations

| Table 33. Abbre                   | Table 33. Abbreviations                     |  |  |  |  |  |  |  |  |

|-----------------------------------|---------------------------------------------|--|--|--|--|--|--|--|--|

| Acronym                           | Description                                 |  |  |  |  |  |  |  |  |

| ADC                               | Analog-to-Digital Converter                 |  |  |  |  |  |  |  |  |

| AHB                               | Advanced High-performance Bus               |  |  |  |  |  |  |  |  |

| APB                               | Advanced Peripheral Bus                     |  |  |  |  |  |  |  |  |

| BOD                               | BrownOut Detection                          |  |  |  |  |  |  |  |  |

| GPIO General Purpose Input/Output |                                             |  |  |  |  |  |  |  |  |

| PLL                               | Phase-Locked Loop                           |  |  |  |  |  |  |  |  |

| RC                                | Resistor-Capacitor                          |  |  |  |  |  |  |  |  |

| SPI                               | Serial Peripheral Interface                 |  |  |  |  |  |  |  |  |

| SSI                               | Serial Synchronous Interface                |  |  |  |  |  |  |  |  |

| SSP Synchronous Serial Port       |                                             |  |  |  |  |  |  |  |  |

| TEM                               | Transverse ElectroMagnetic                  |  |  |  |  |  |  |  |  |

| UART                              | Universal Asynchronous Receiver/Transmitter |  |  |  |  |  |  |  |  |

### 16. References

| [1] | LPC111x/LPC11Cxx User manual UM10398:                |

|-----|------------------------------------------------------|

|     | http://www.nxp.com/documents/user_manual/UM10398.pdf |

[2] LPC111x Errata sheet: http://www.nxp.com/documents/errata\_sheet/ES\_LPC111X.pdf

32-bit ARM Cortex-M0 microcontroller

### 17. Revision history

| Table 34. Revision h | -                                           | Data alteration for                                                                                                                                                                                                                                    | Charrier                                                    | Sumana da -                                                                        |  |  |  |  |  |  |

|----------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Document ID          | Release date                                | Data sheet status                                                                                                                                                                                                                                      | Change notice                                               | -                                                                                  |  |  |  |  |  |  |

| LPC111X v.9.2        | 20140326                                    | Product data sheet                                                                                                                                                                                                                                     | -                                                           | LPC111X v.9.1                                                                      |  |  |  |  |  |  |

| Modifications:       | must be pu<br>as a GPIO                     | must be pulled HIGH externally. The RESET pin can be left unconnected or be used as a GPIO pin if an external RESET function is not needed. See <u>Section 6.2</u> .                                                                                   |                                                             |                                                                                    |  |  |  |  |  |  |

|                      | Section 6.2                                 | Section 6.2.                                                                                                                                                                                                                                           |                                                             |                                                                                    |  |  |  |  |  |  |

|                      | Parts adde<br>LPC1113JH<br>LPC1114JE        | d: LPC1114JHI33/303, I<br>IN33/203, LPC1114JHN                                                                                                                                                                                                         | LPC1111JHN33/103<br>133/303, LPC1114J<br>148/323, LPC1113JE | 3, LPC1112JHN33/203,<br>BD48/333, LPC1112FHI33/102,<br>BD48/303, LPC1113JHN33/303, |  |  |  |  |  |  |

| LPC111X v.9.1        | 20131213                                    | Product data sheet                                                                                                                                                                                                                                     | -                                                           | LPC111X v.9                                                                        |  |  |  |  |  |  |

| Modifications:       | <ul> <li>Table 17 "S</li> </ul>             | Static characteristics (LP                                                                                                                                                                                                                             | C1100XL series)":                                           |                                                                                    |  |  |  |  |  |  |